# תתת

Advanced Advances

The Language Book

ההההההההההההההההההההההה תתתתתתתתתתתתתתתתתתתתתת התתתתתתתתתתתתתתתתתתתת זהתהתהתהתהתהתהתהתה נהההתהתהתהתהההההההה<u>ה</u>ה תתתתתתתתתתתתתתתתתתתתת התהתהתהתהתהתהתהתה תתתתתתתתתתתתתתתתתתתת התתתתתתתתתתתתת ותתתתתתתתתתתתתתתתתתת התהתהתהתהתהתהתהתהתהתהההה ההתהתהתהתהתהתהתהתה *ההההההההההההההההההההההה* התהתהתהתהתהתהתהתהתהתהתהחה<u>ת</u> תתתתתתתתתתתתתתתתתת

# **Advanced Micro Devices**

# The Am2900 Family Data Book With Related Support Circuits

Copyright © 1979 by Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

901 Thompson Place, P.O. Box 453, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

AM-PUB003

#### **TABLE OF CONTENTS**

|     | Introduction |                                                                     | 1-1   |

|-----|--------------|---------------------------------------------------------------------|-------|

| 11. |              | A Dit Disclar Missans Clies                                         |       |

|     | Am2901/A/B   | 4-Bit Bipolar Microprocessor Slice                                  |       |

|     |              | Using the Am2901                                                    | 2-17  |

|     | Am2901C      | Improved-Speed 4-Bit Microprocessor Slice                           |       |

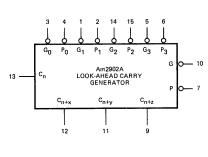

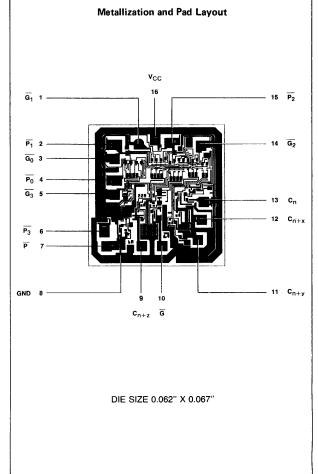

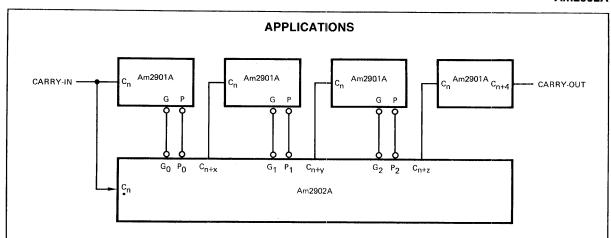

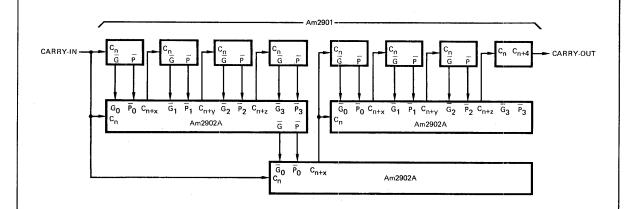

|     | Am2902A      | High-Speed Look-Ahead Carry Generator                               |       |

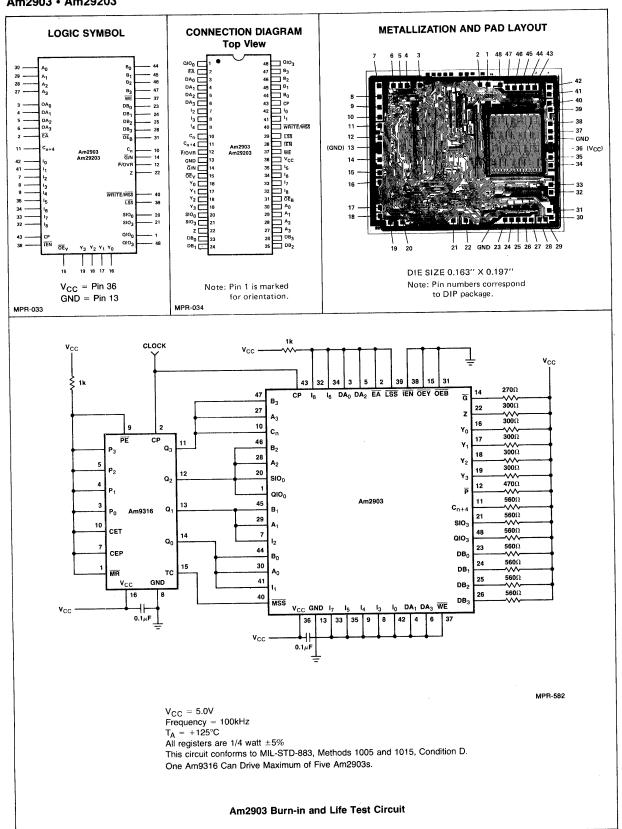

|     | Am2903/29203 | The Superslice® (Advanced 4-Bit Bipolar Microprocessor Slice)       |       |

|     |              | Using the Am2903 and Am29203                                        |       |

|     |              | Am2903 Detailed Switching Characteristics                           |       |

|     | Am2903A      | Improved Speed Superslice™                                          |       |

|     | Am2904       | Status and Shift Control Unit                                       |       |

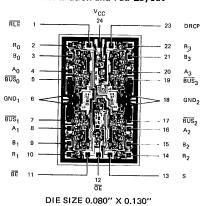

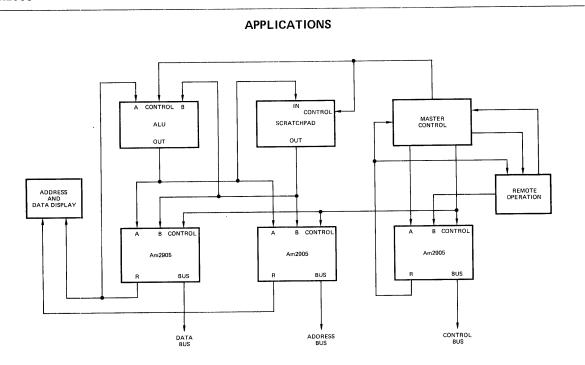

|     | Am2905       | Quad 2-Input OC Bus Transceiver with 3-State Receiver               |       |

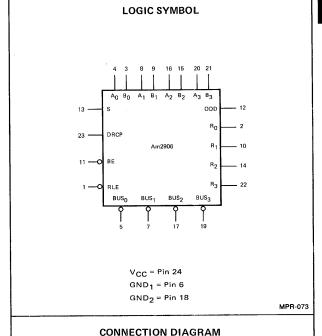

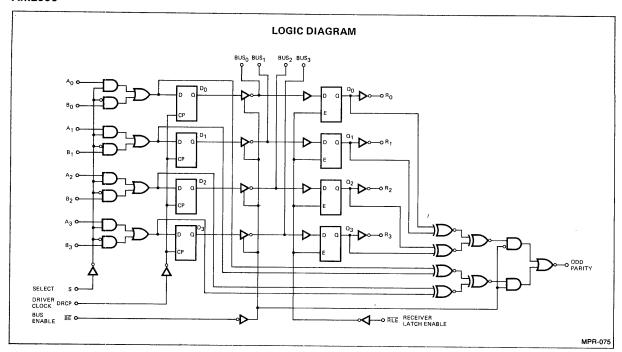

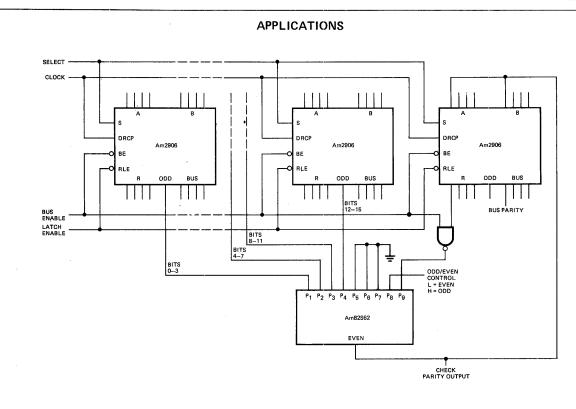

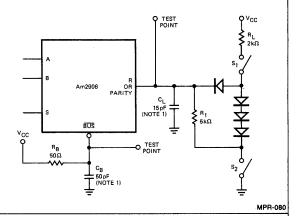

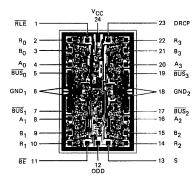

|     | Am2906       | Quad 2-Input OC Bus Transceiver with Parity                         |       |

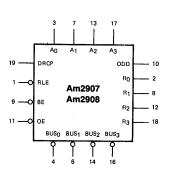

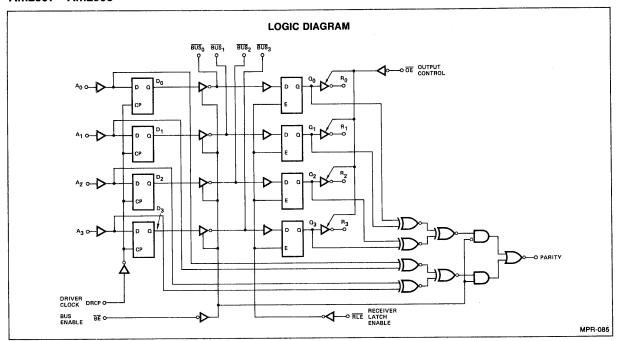

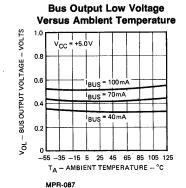

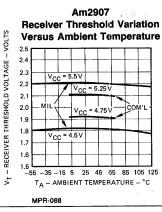

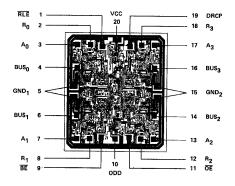

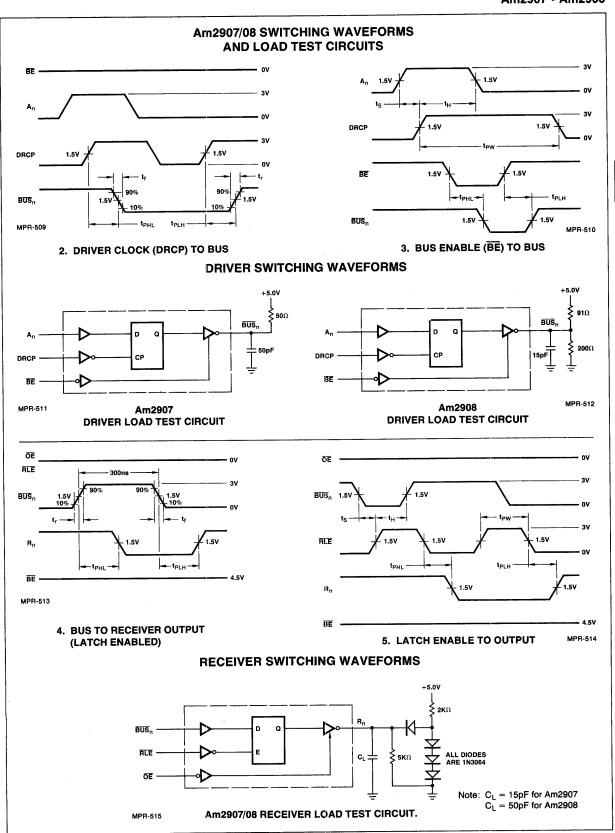

|     | Am2907/2908  | Quad Bus Transceiver with Interface Logic                           |       |

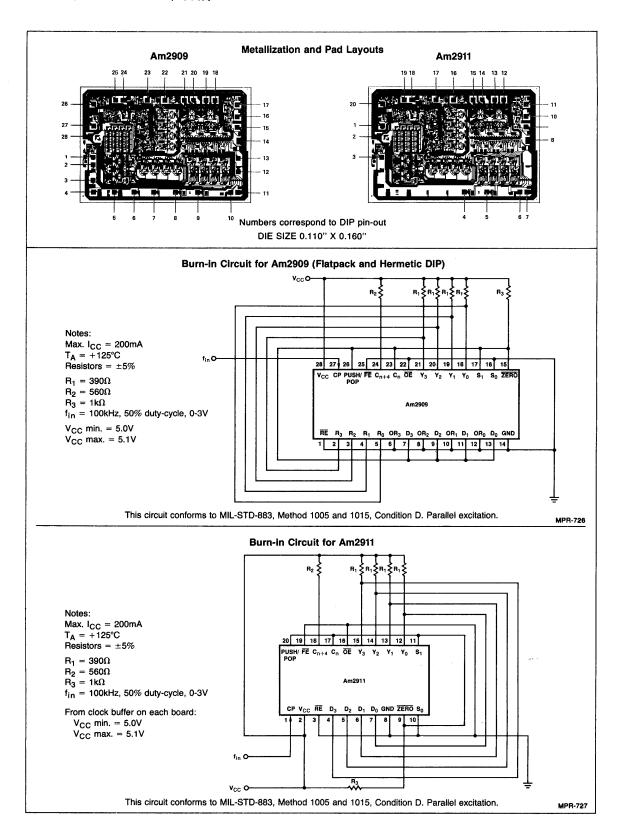

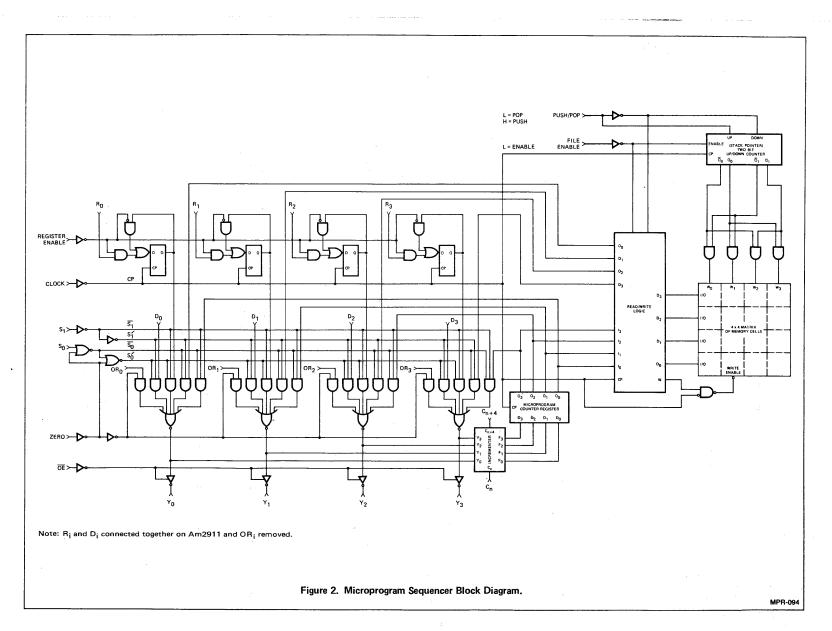

|     | Am2909/2909A | Microprogram Sequencer                                              |       |

|     | Am2910       | Microprogram Controller                                             |       |

|     | Am2911/2911A | Microprogram Sequencer                                              |       |

|     | Am2912       | Quad Bus Tranceiver                                                 |       |

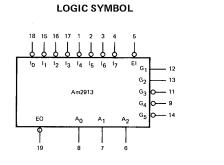

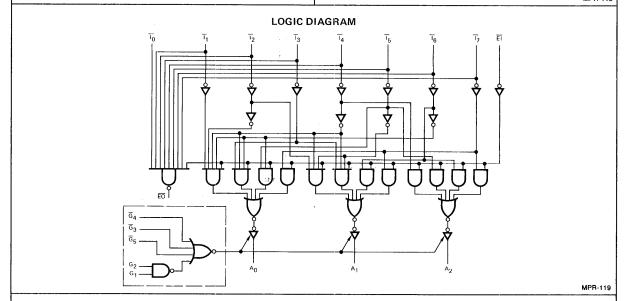

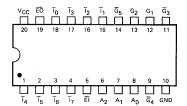

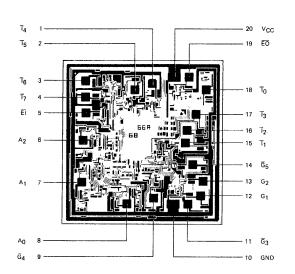

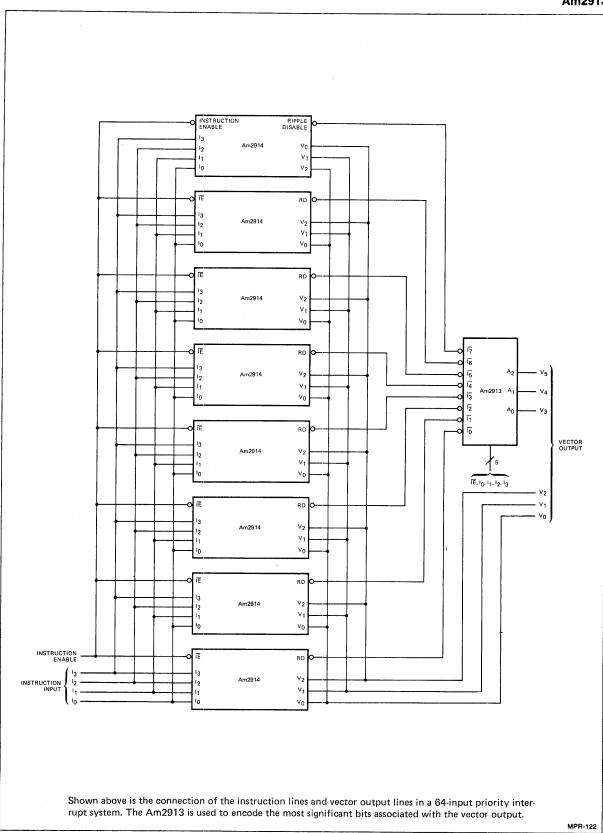

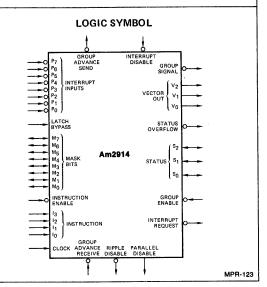

|     | Am2913       | Priority Interrupt Expander                                         |       |

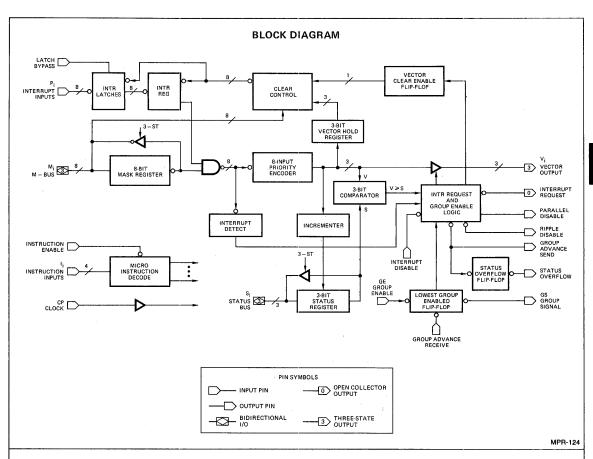

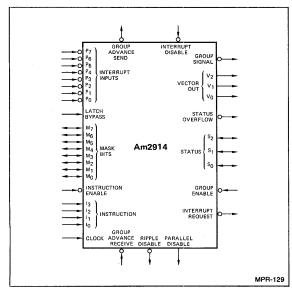

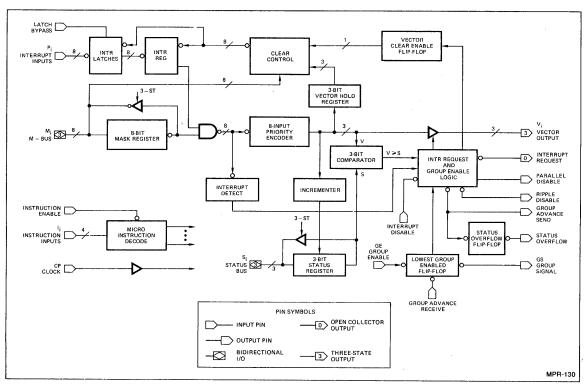

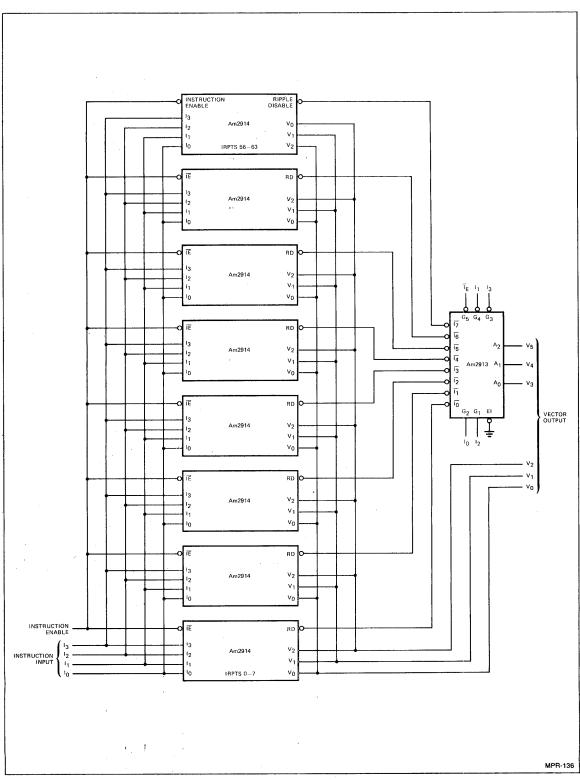

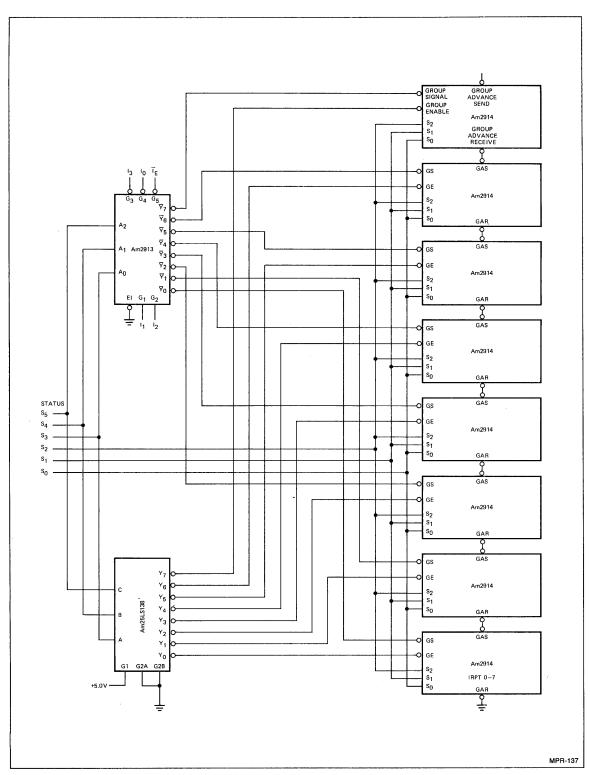

|     | Am2914       | Vectored Priority Interrupt Controller                              | 2-158 |

|     | •            | A Microprogrammable Interrupt Structure                             | 2-166 |

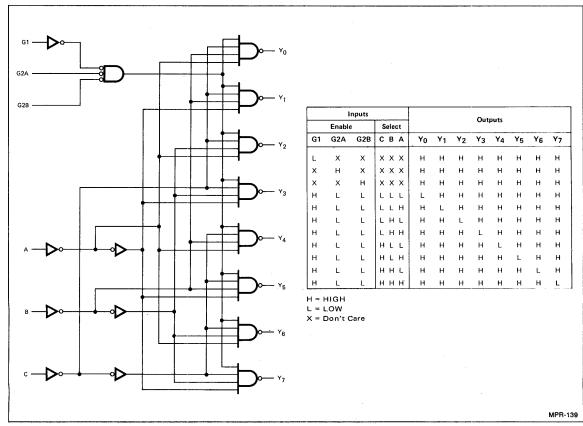

|     |              | Priority Interrupt Encoder Logic Description                        | 2-177 |

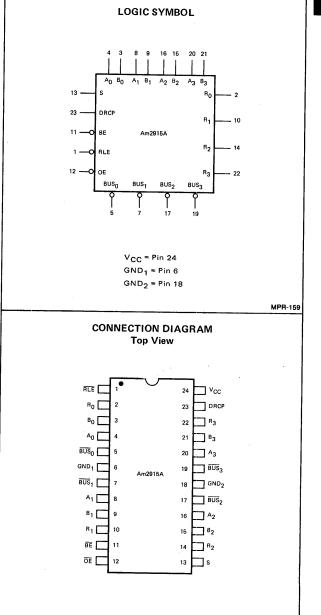

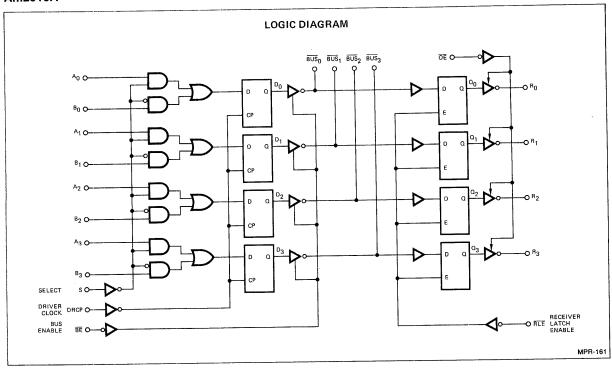

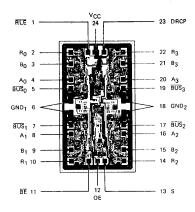

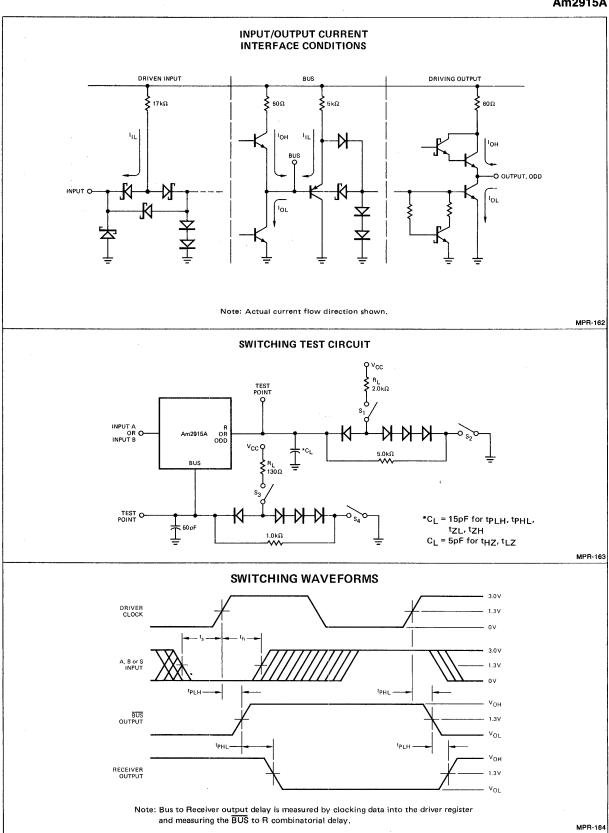

|     | Am2915A      | Quad 3-State Bus Transceiver with Interface Logic                   | 2-183 |

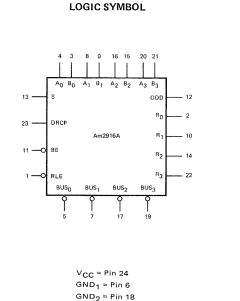

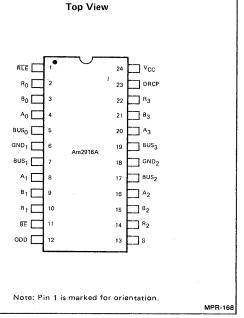

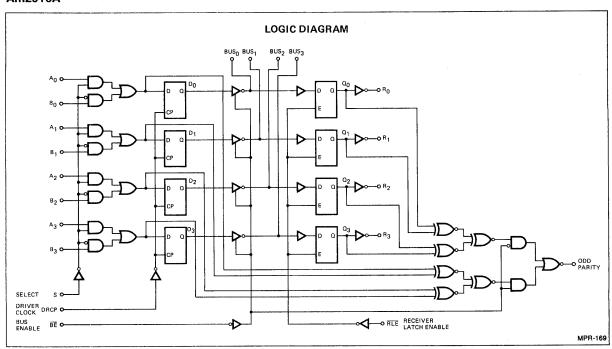

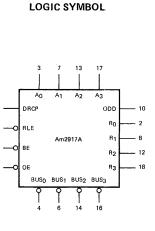

|     | Am2916A      | Quad 3-State Bus Transceiver with Interface Logic                   | 2-189 |

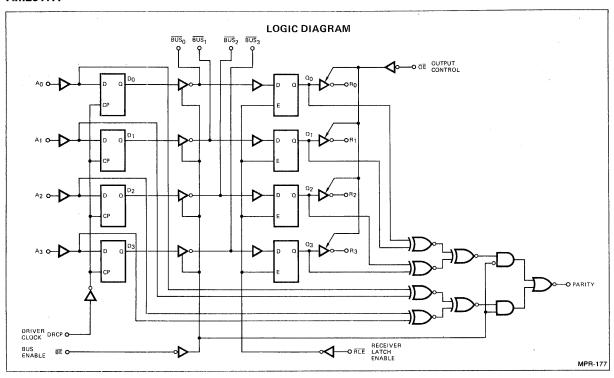

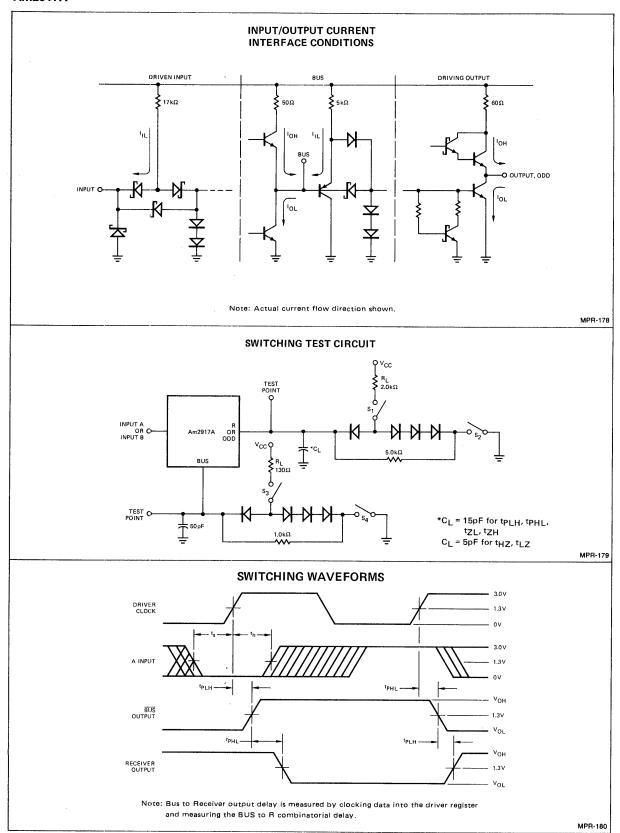

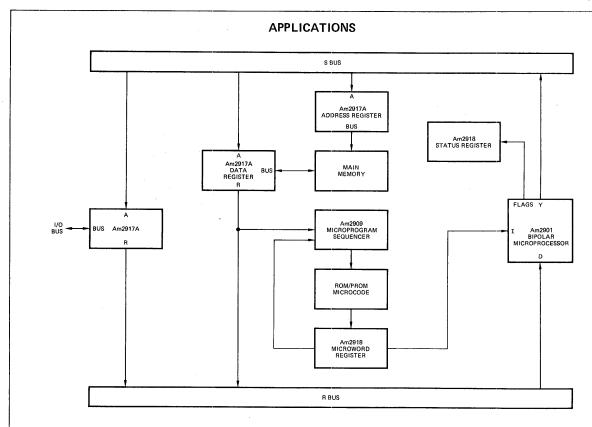

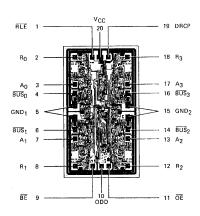

|     | Am2917A      | Quad 3-State Bus Transceiver with Interface Logic                   | 2-195 |

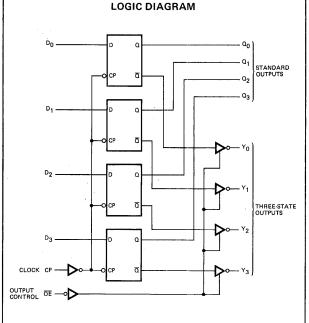

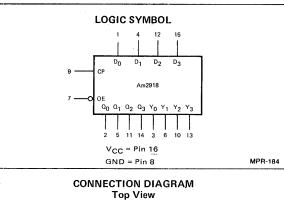

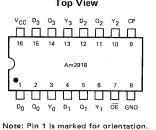

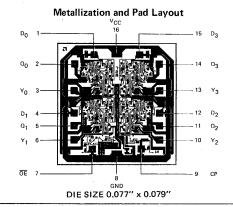

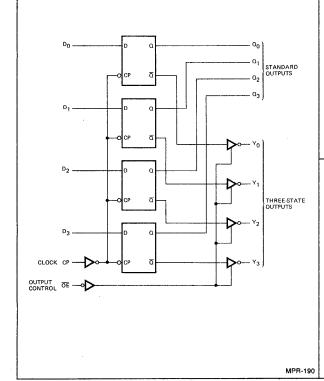

|     | Am2918       | Quad D Register with Standard and 3-State Outputs                   | 2-201 |

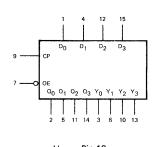

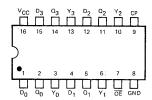

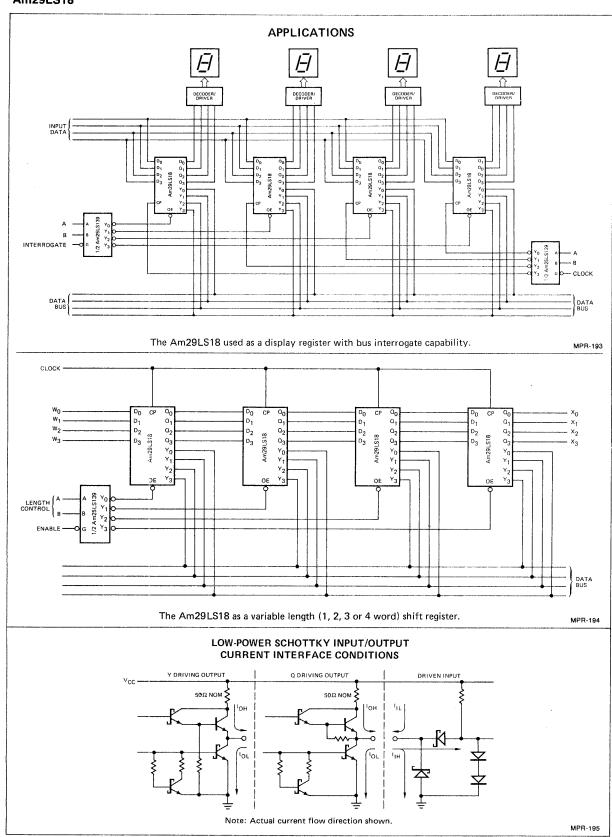

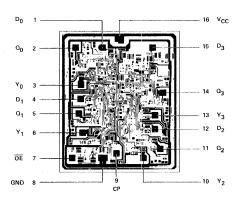

|     | Am29LS18     | Quad D Register with Standard and 3-State Outputs                   | 2-205 |

|     | Am2919       | Quad Register with Dual 3-State Outputs                             |       |

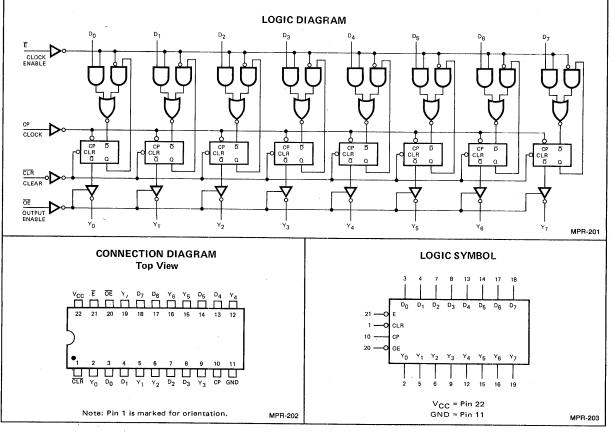

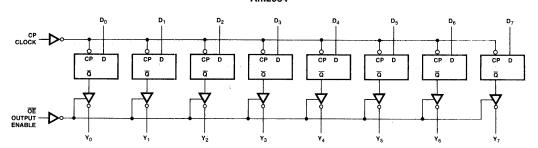

|     | Am2920       | Octal D-Type Flip-Flop with Clear, Clock Enable and 3-State Control | 2-215 |

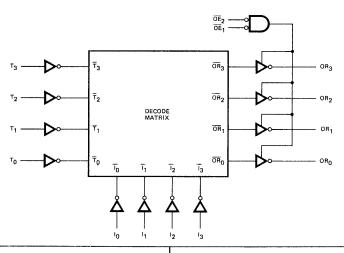

|     | Am2921       | 1-of-8 Decoder with 3-State Outputs and Polarity Control            |       |

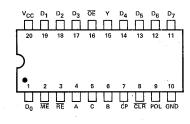

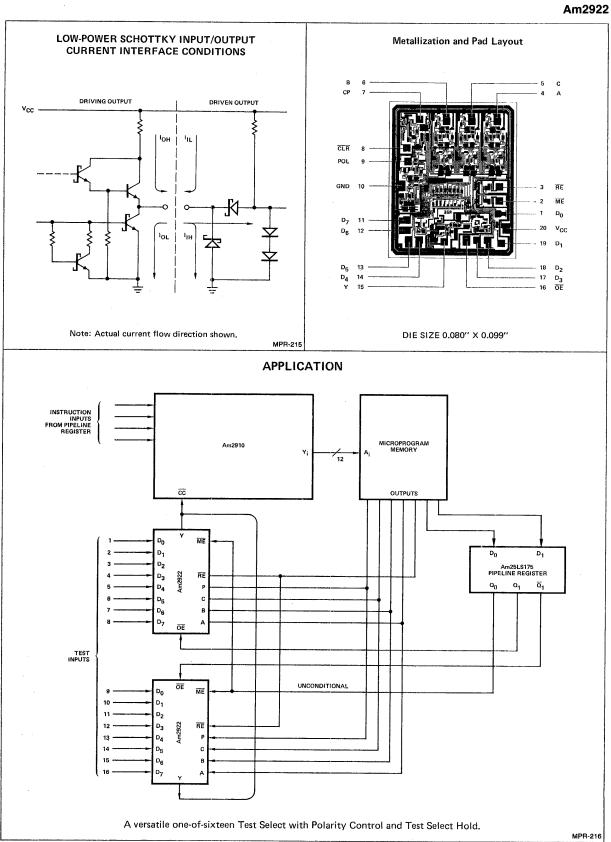

|     | Am2922       | 8-Input Multiplexer with Control Register                           |       |

|     | Am2923       | 8-Input Multiplexer                                                 |       |

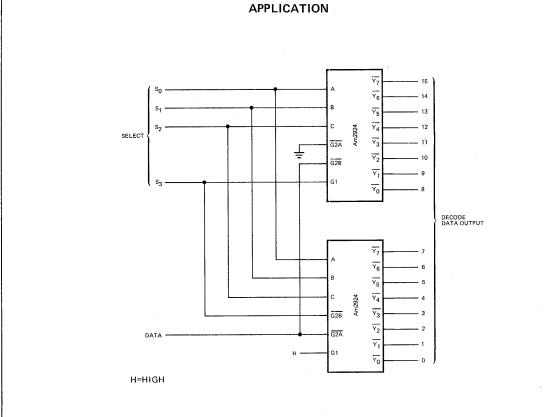

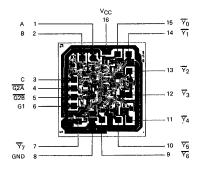

|     | Am2924       | 3-Line to 8-Line Decoder/Demultiplexer                              |       |

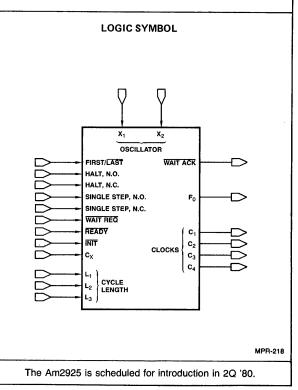

|     | Am2925       | System Clock Generator and Driver                                   |       |

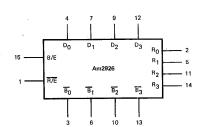

|     | Am2926       | Schottky 3-State Quad Bus Driver/Receiver                           | 2-239 |

|     | Am2927/2928  | Quad 3-State Bus Transceivers with Clock Enable                     |       |

|     | Am2929       | Schottky 3-State Quad Bus Driver/Receiver                           |       |

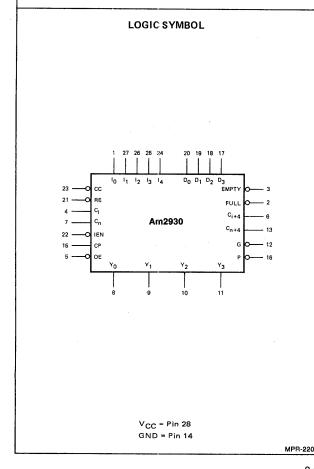

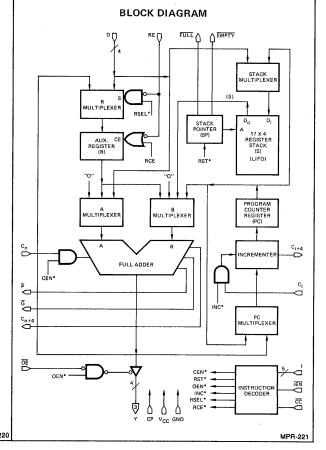

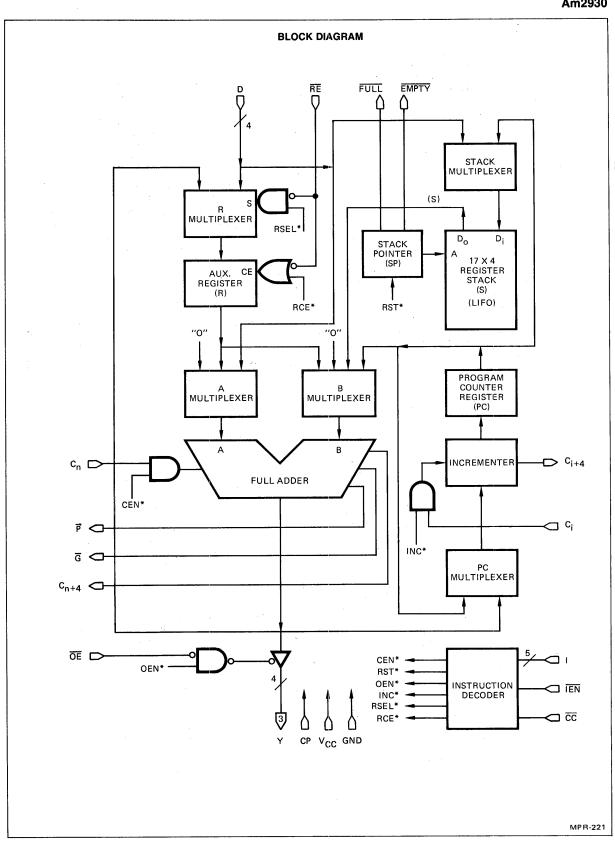

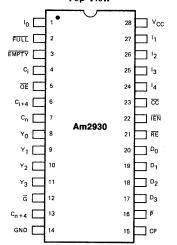

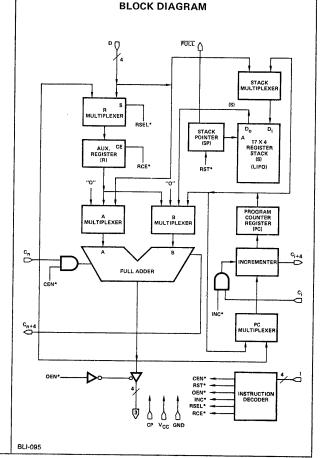

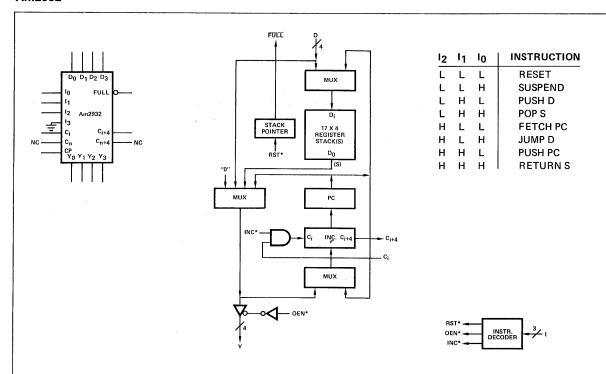

|     | Am2930       | Program Control Unit                                                |       |

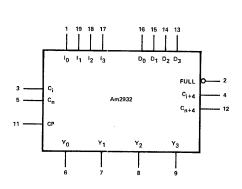

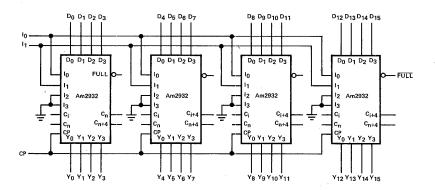

|     | Am2932       | Program Control Unit/Push-Pop Stack                                 |       |

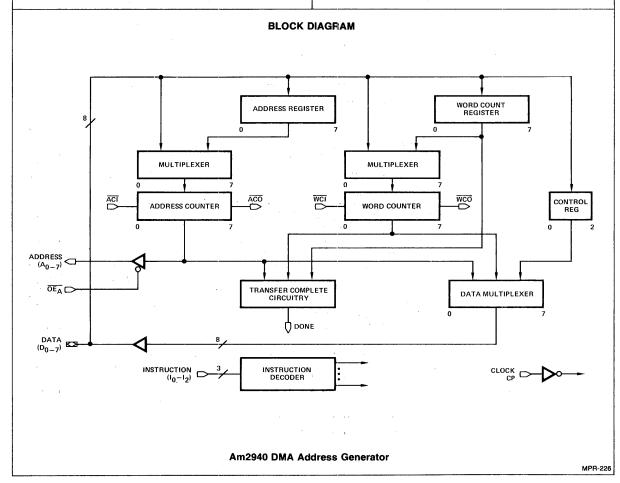

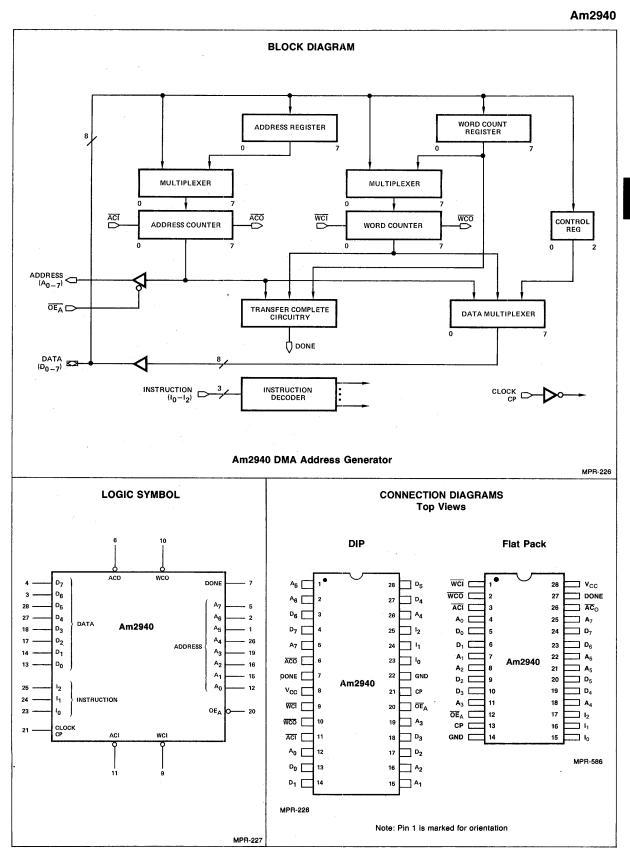

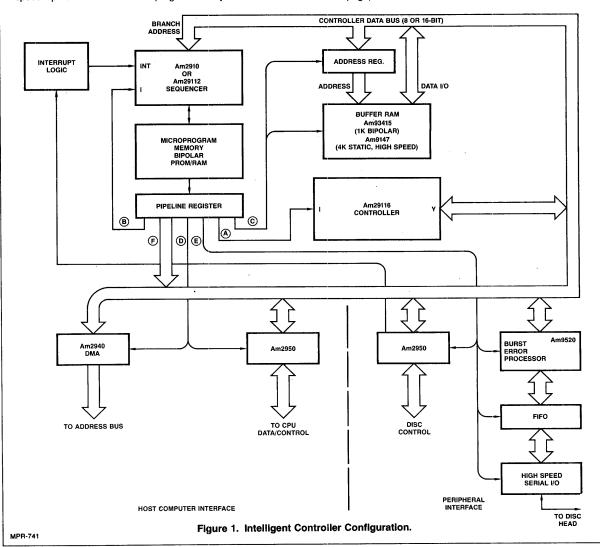

|     | Am2940       | DMA Address Generator                                               |       |

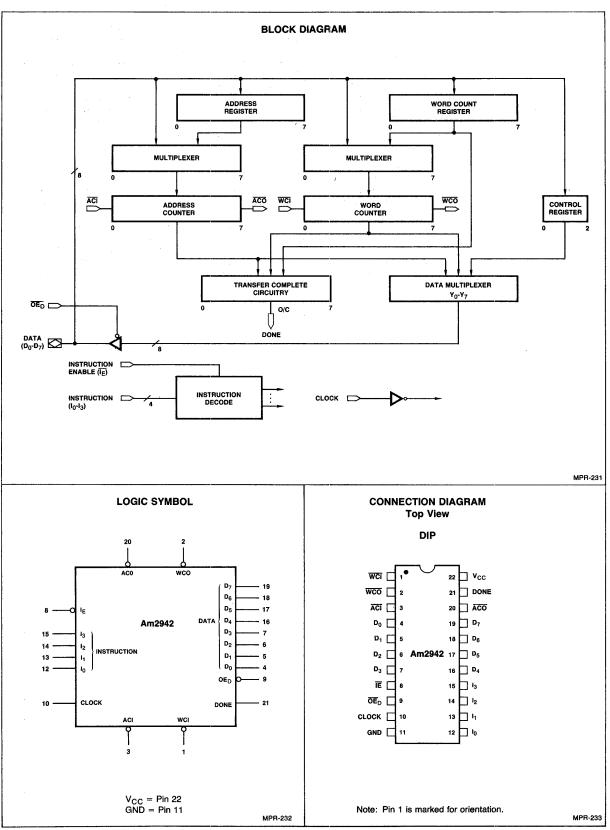

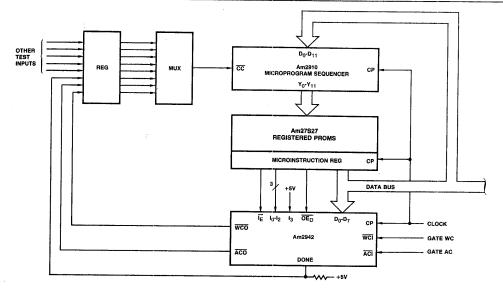

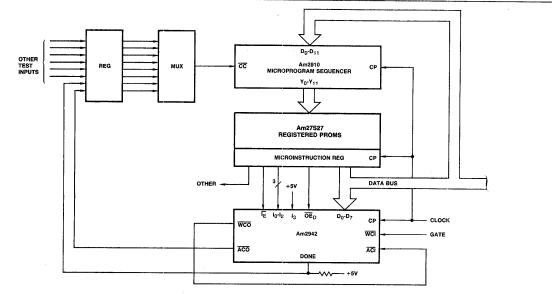

|     | Am2942       | Programmable Timer/Counter/DMA Address Generator                    |       |

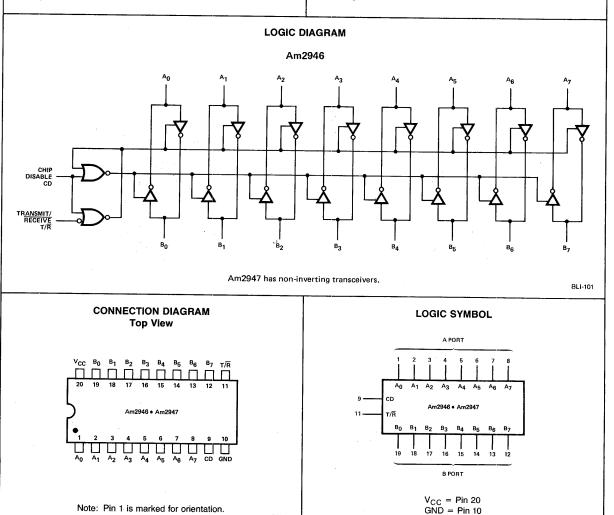

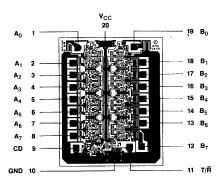

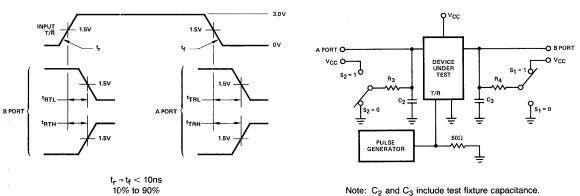

|     | Am2946/2947  | Octal 3-State Bidirectional Bus Transceivers                        |       |

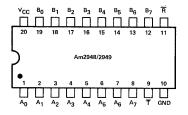

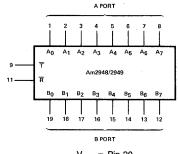

|     | Am2948/2949  | Octal 3-State Bidirectional Bus Transceivers                        |       |

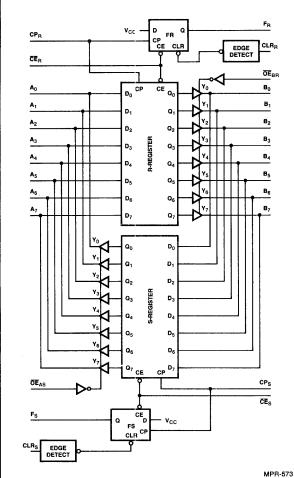

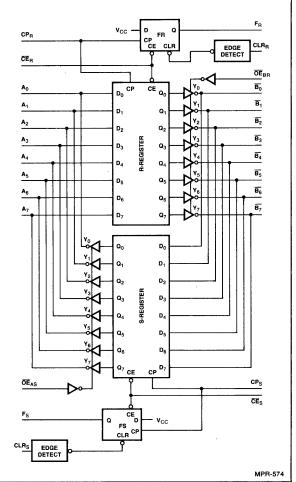

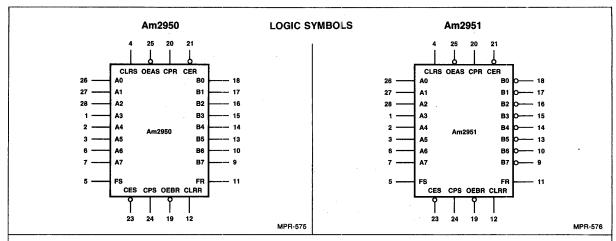

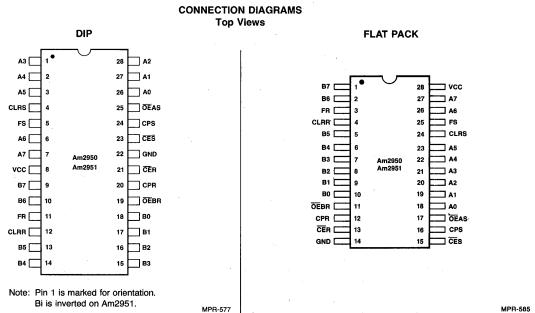

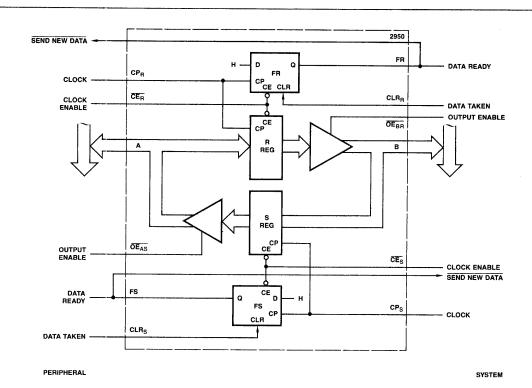

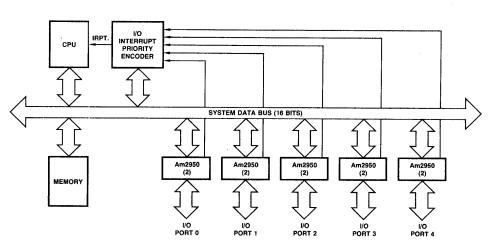

|     | Am2950/2951  | 8-Bit Bidirectional I/O Ports                                       |       |

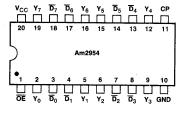

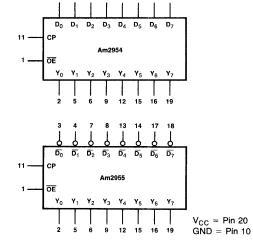

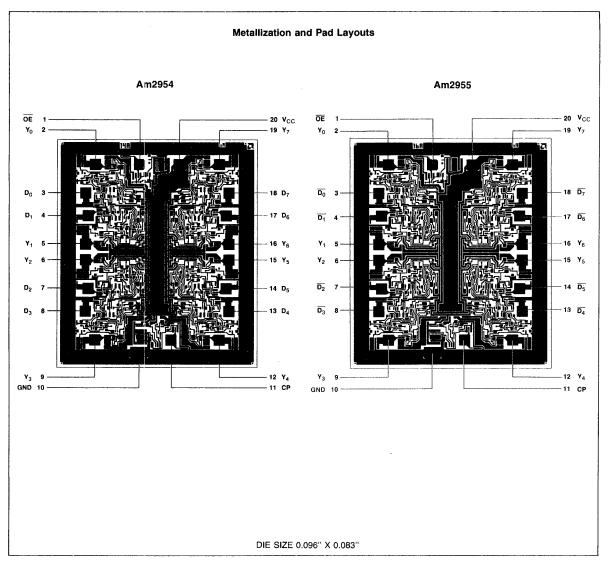

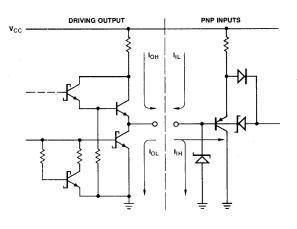

|     | Am2954/2955  | Octal Registers with 3-State Outputs                                |       |

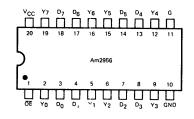

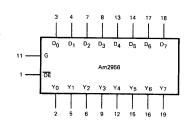

|     | Am2956/2957  | Octal Latches with 3-State Outputs                                  |       |

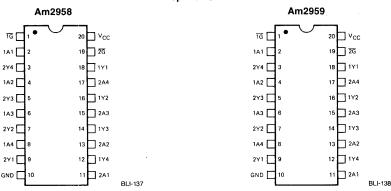

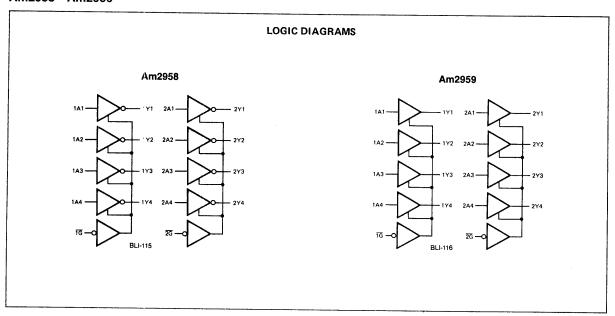

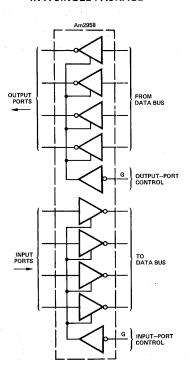

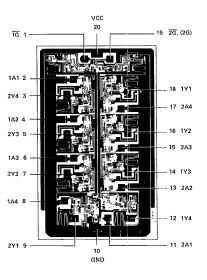

|     | Am2958/2959  | Octal Buffers/Line Drivers/Line Receivers with 3-State Outputs      |       |

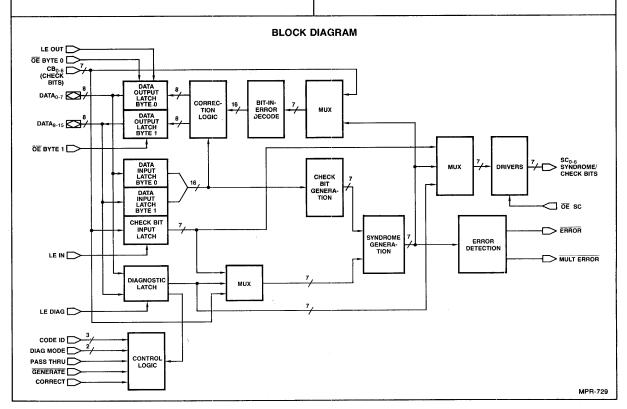

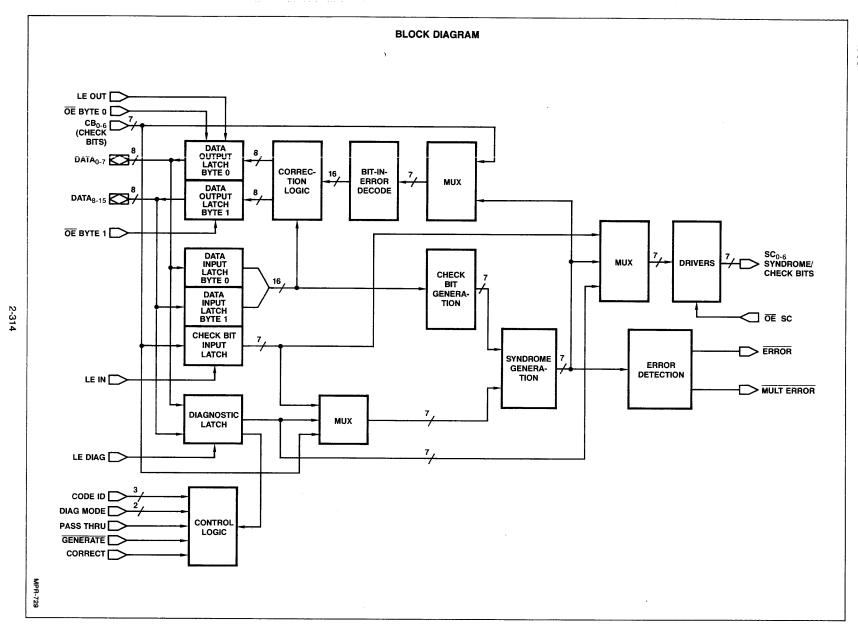

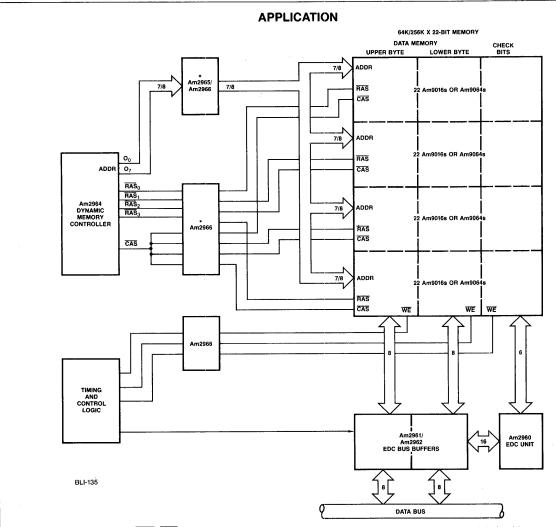

|     | Am2960       | Cascadable 16-Bit Error Detection and Correction Unit               | 2-312 |

|     | Am2961/2962  | 4-Bit Error Correction Multiple Bus Buffers                         |       |

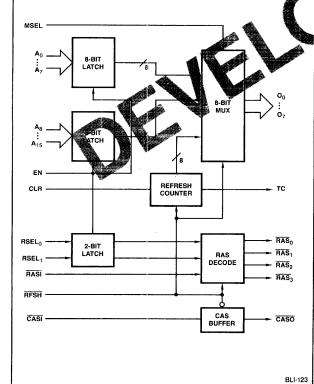

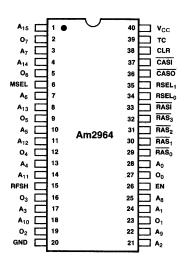

|     | Am2964       | Dynamic Memory Controller                                           |       |

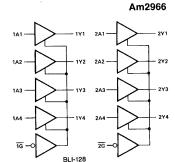

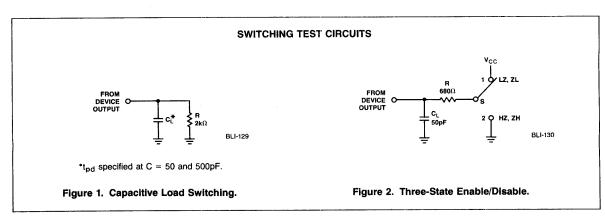

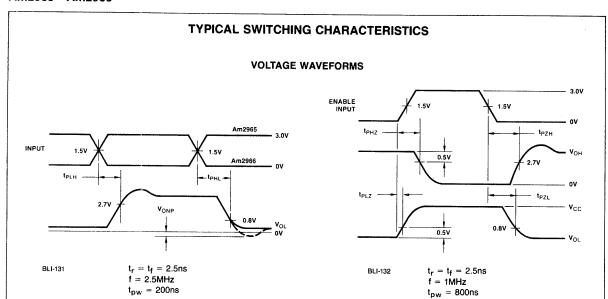

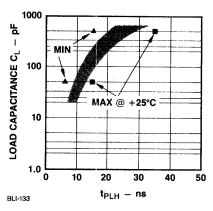

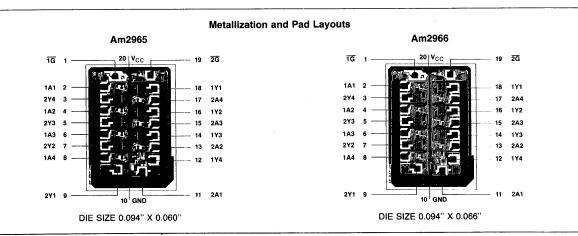

|     | Am2965/2966  | Octal Dynamic Memory Driver with 3-State Outputs                    | 2-331 |

#### **TABLE OF CONTENTS (Cont.)**

|      | Am29112           | Interruptable 8-Bit Microprogram Sequencer                | 2-337 |

|------|-------------------|-----------------------------------------------------------|-------|

|      |                   | Am2900 High Performance Controller Products               |       |

|      | Am29116           | 16-Bit Bipolar Microprocessor                             |       |

|      |                   | Am2900 High Performance Controller Products               |       |

|      | Am29700/701       | Non-Inverting Schottky 64-Bit Random Access Memories      |       |

|      | Am29702/703       | Schottky 64-Bit Random Access Memories                    |       |

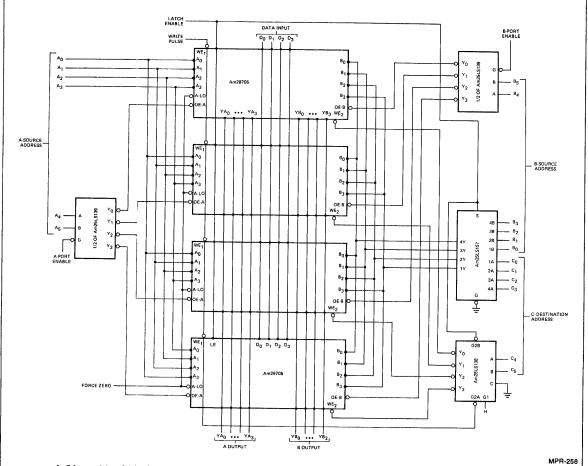

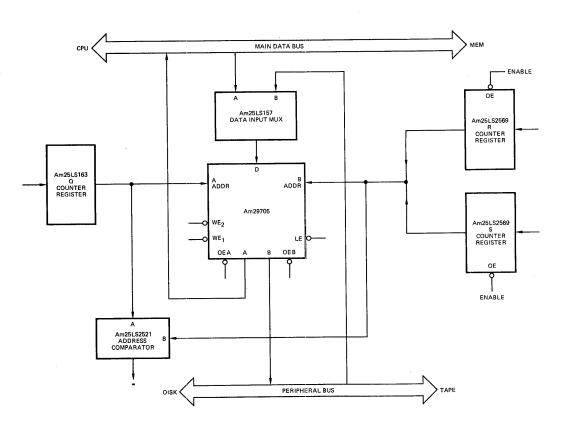

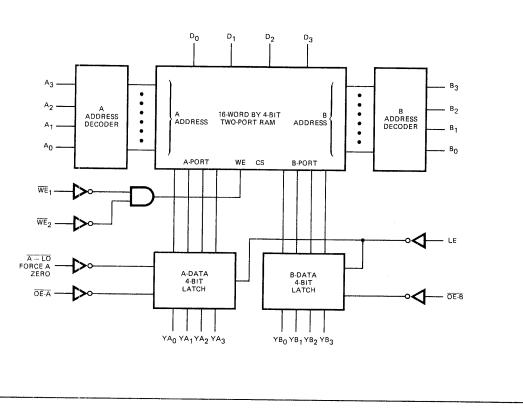

|      | Am29705           | 16-Word by 4-Bit 2-Port RAM                               |       |

|      | Am29705A          | Improved Speed 2-Port RAM                                 |       |

|      | Am29720/721       | Low-Power Schottky 256-Bit Random Access Memories         |       |

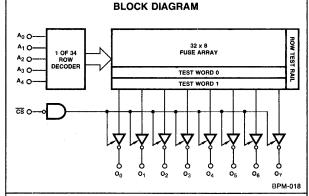

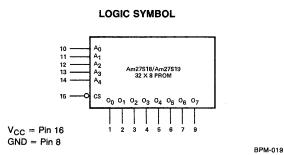

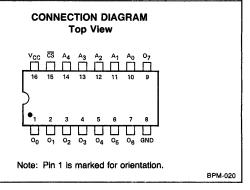

|      | Am29750/751A      | 32-Word by 8-Bit PROMs                                    |       |

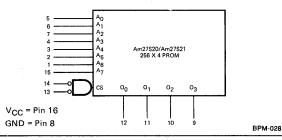

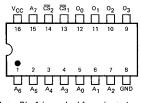

|      | Am29760A/761A     | 256-Word by 4-Bit PROMs                                   |       |

|      | Am29770/771       | 2048-Bit Generic Series Bipolar PROM                      |       |

|      | Am29774/775       | 4096-Bit Generic Series Bipolar PROM with Output Register |       |

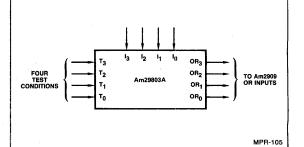

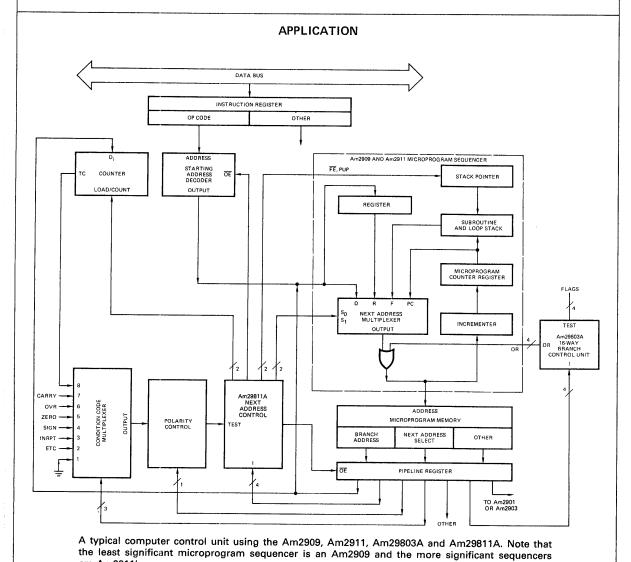

|      | Am29803A          | 16-Way Branch Control Unit                                |       |

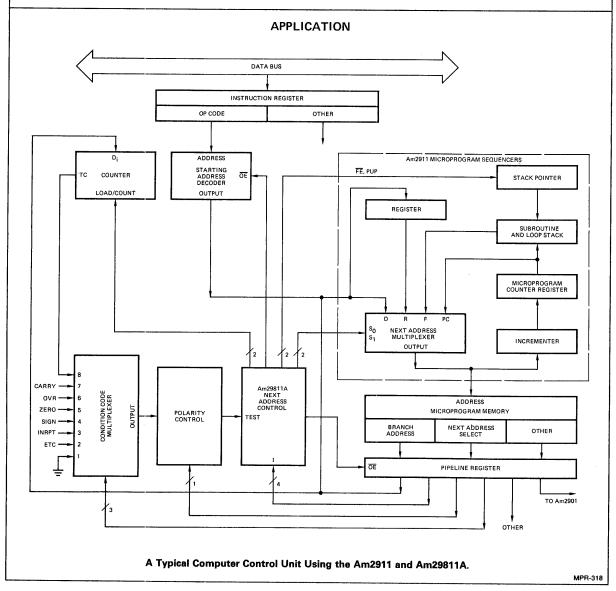

|      | Am29811A          | Next Address Control Unit                                 |       |

| III. | Am2900 Design Sup |                                                           |       |

|      |                   | tions Literature                                          | 3-1   |

|      |                   | and Learning Kit                                          | 3-3   |

|      |                   | ment System                                               |       |

| IV.  |                   | terface Products                                          |       |

|      |                   | ducts                                                     |       |

|      |                   | roducts                                                   |       |

|      |                   | vices Commitment to Excellence                            |       |

|      |                   |                                                           | B-1   |

|      | Ü                 | istributor Locations                                      | C-1   |

|      |                   |                                                           |       |

# 1

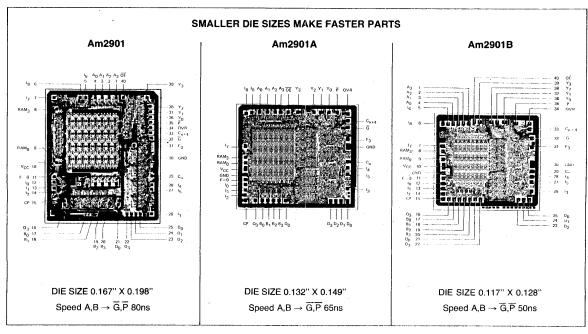

# Am2900 COMPONENTS CONTINUOUSLY BECOME FASTER AND FASTER

#### MORE SPEED: NO MORE POWER

There's a good old tried and proven way to make faster IC's — burn more power. (That's the only real difference between "LS" and "S" devices). But that solution isn't satisfactory for LSI devices like the Am2900 family. Power is constrained to existing levels for reliability reasons.

Am2900 parts are always designed to obtain the maximum speed at a power level which is safe for the package types and operating environment of the part. To increase speeds, new technologies must be used to build faster components at no increase in power.

### NEW CIRCUIT DESIGN TECHNIQUES MAKE FASTER GATES

One way to make faster components is to use new circuit design techniques. The most obvious is internal ECL, which provides very fast gates at similar power levels to LS TTL. Other design techniques, such as low-level logic (with very small logic swings on-chip), can also provide higher speeds without introducing the time penalty of ECL to TTL conversion.

Finally, very low power gates used in non-critical speed paths make more power available for use in critical speed paths. As the 2900 family develops, all these technologies will be used within a single component to achieve the highest speeds without increasing power. Among the first products to take advantage of mixed-circuit technology will be the Am2903A.

## IMPROVED PROCESS CONTROL ALLOWS TIGHTER SPECS

Today's 2900 parts are carefully characterized over a wide range of voltages, temperatures, and process parameters before an AC specification is published. As manufacturing technology improves, the process is subject to smaller run-to-run variations, so that all of the product is closer to design nominal. This makes it possible to specify parameters more closely to typical without incurring large yield losses. The first product reflecting this is the Am2903.

### WHAT'S GOOD FOR THE GOOSE IS GOOD FOR THE GANDER

Many new tools in production technology are emerging, primarily spurred by the emphasis on high-speed MOS memories. The same tools, such as projection masking, also provide for smaller geometries in bipolar circuits. As MOS gets faster, so does bipolar. The Am2901B obtains its speed improvement over the Am2901A through these tools.

#### **DESIGN FOR THE FUTURE**

Every Am2900 part will undergo an evolution as new technologies become practical for production. Every part type will continuously become faster. Within a few short years, 2900-based designs will compete favorably with Schottky MSI on a speed basis at a fraction of the component count.

Most existing 2900 designs can be offered in higher performance versions simply by substitution of the 2901B for the 2901A, the 2909A for the 2909, the 2903A for the 2903, and so forth. Your 2900 design won't run out of speed in a few years. Advanced Micro Devices' 2900 Family will serve tomorrow's needs as well as today's.

#### INTRODUCTION

#### THREE GENERATIONS OF TTL

Transistor-transistor logic has been the dominant technology for digital circuits since it was developed in the mid-1960's. It has proven itself to be manufacturable in high volume using an extremely reliable process technology. The processes used for TTL have evolved over the years, making components smaller, faster and less expensive. Relative to a TTL gate manufactured in 1966, a gate on a circuit manufactured today occupies 1/5 the area, consumes 1/10 the power, is twice as fast and costs less than 1/100 the price.

The circuits built using TTL technology have gone through two generations; the Am2900 Family represents the beginning of the third. Each generation consists of circuits which are fundamental building blocks of systems — circuits which can be interconnected in many different ways to build many different systems. Only by producing such universal circuits can manufacturing volumes be high enough to generate the rapid cost reductions characteristic of the integrated circuit industry.

The quality which distinguishes one generation from another is the level of integration used, and, because of the level of integration, the philosophy behind the circuit.

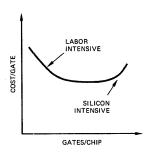

If one draws a curve plotting the cost of an individual gate against the number of gates on a chip, Figure 1 results.

Figure 1. MPR-001

At the left, cost per gate is inversely proportional to the number of gates on the chip. The chip is small enough that it does not represent a significant portion of the cost of the product — it is virtually free. The cost of the product is composed of labor in assembly and test, the cost of processing an order, shipping and fixed overhead. Doubling the number of gates on the chip doesn't materially affect the cost so the cost per gate halves. As the number of gates per chip increases, the die begins to cost more, reversing the downward trend. As die cost dominates, the cost per gate remains relatively flat until the yield of the die begins to decline markedly. The cost per gate then begins to rise again. The lowest cost per gate is achieved at a level of integration corresponding to the flat region. This is the optimum level of integration.

As technology improves, costs are constantly reduced and the optimum level of integration occurs at more and more gates per chip.

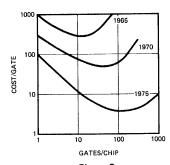

The three curves of Figure 2 are the reason for the three generations of TTL. Each generation has consisted of fundamental system building blocks designed to take advantage of the optimum level of integration at the time.

Figure 2.

MPR-002

#### **GENERATION I - SSI, 1965**

In 1965, the optimum level of integration was three-to-six gates per chip. Users were delighted to buy such chips at \$10–20 each. The circuits were useful in many systems. They consisted of gates — the 7400, 7410, 7420 — and, pressing the state of the art, some flip-flops. They were fundamental building blocks.

#### **GENERATION II - MSI, 1970**

Beginning around 1968, it became economical to put more gates on a chip and the industry was faced with a problem: How does one put 20 gates on a chip and build a universal building block? Clearly, one answer was to bring the inputs and outputs off chip as had been done before. But that was the wrong answer. The right answer was to redefine fundamental building blocks. The new building blocks fell into seven categories:

- Counters

- Decoders

- Multiplexers

- Operators (adders, comparators)

- Encoders

- Registers

- Latches

All systems could be defined in terms of these seven functions, and integrated circuits could be defined at the 20-50 gate/chip level which performed these functions efficiently. This, of course, is MSI. Over the last six or seven years, more and more circuits of this type have been introduced, utilizing standard gold-doped technology, low-power TTL, high-speed TTL, Schottky TTL, and now low-power Schottky TTL technology. Today, there are over 250 different MSI circuits and new ones appear every month. But in today's technology, many of these circuits are not particularly cost effective. They are too small for today's technology and their costs are labor intensive. (Labor costs do not follow traditional semiconductor pricing patterns.) In 1977, the optimum level of integration for bipolar logic is around 500 gates/chip.

#### GENERATION III - The Am2900 Family, 1976

At a 500-gate-per-chip level of integration, one does not build counters, decoders, and multiplexers. A new definition of fundamental system functions is needed. Advanced Micro Devices has defined these eight categories:

- Data Manipulation

- Microprogram Control

- Macroprogram Control

- Priority Interrupt

- Direct Memory Access

- I/O Control

- Memory Control

- Front Panel Control

The Am2900 Family consists of circuits designed to perform those functions efficiently. They are fundamental system building blocks; they contain hundreds of gates per chip; they are fast — utilizing Low-Power Schottky TTL technology; they are expandable; they are flexible — useful in emulation; and they are driven under microprogram control.

#### THE Am2900 FAMILY

The Am2900 Family consists of a series of LSI building blocks designed for use in microprogrammed computers and controllers. Each device is designed to be expandable and sufficiently flexible to be suitable for emulation of many existing machines. It is the wide variety of machine architectures possible with the Am2900 Family which sets it apart from the fixed-instruction microprocessors such as the Am9080A.

While an Am9080A can be used to build a microcomputer with only four or five packages, an Am2900 design will require 30 or 40 or more. The Am9080A design will, therefore, almost always be cheaper. But the Am9080A, or any other fixed-instruction processor, can execute only one instruction set, so it is not really suitable for emulation of another machine.

Moreover, a fixed-instruction processor operates only on words of a single length, usually eight bits. An Am2900 design, on the other hand, can be constructed for any word length which is a multiple of four bits.

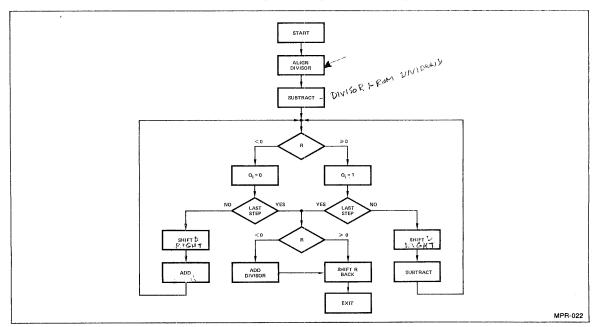

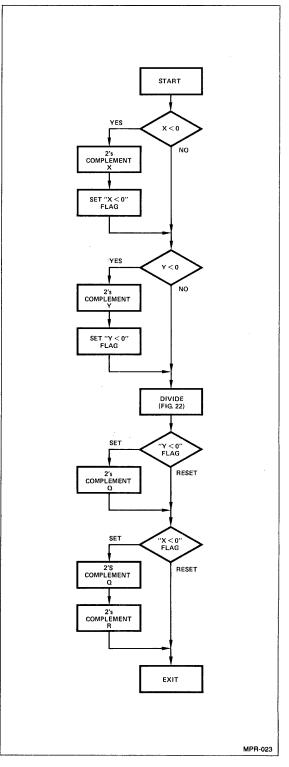

Many applications require specialized operations to be performed at relatively high speed. Such functions as multiply and divide and special graphic control operations, can be done in microcode 10–100 times faster than in fixed-instruction MOS processors.

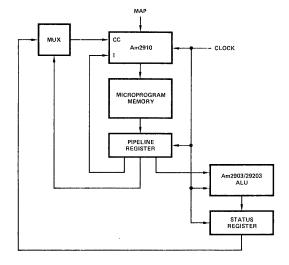

#### MICROPROGRAMMED ARCHITECTURE

Most small processors today are being designed using a technique called microprogramming. In microprogrammed systems, a large portion of the system's control is performed by a read only memory (usually PROM) rather than large arrays of gates and flip-flops. This technique frequently reduces the package count in the controller and provides a highly ordered structure in the controller, not present when random logic is used. Moreover, microprogramming makes changes in the machines' instruction set very simple to perform — reducing the post-production engineering costs for the system substantially.

The Am2900 Family of Bipolar LSI devices has been designed for use in microprogrammed systems. Each device performs a basic system function and is driven by a set of control lines from a microinstruction.

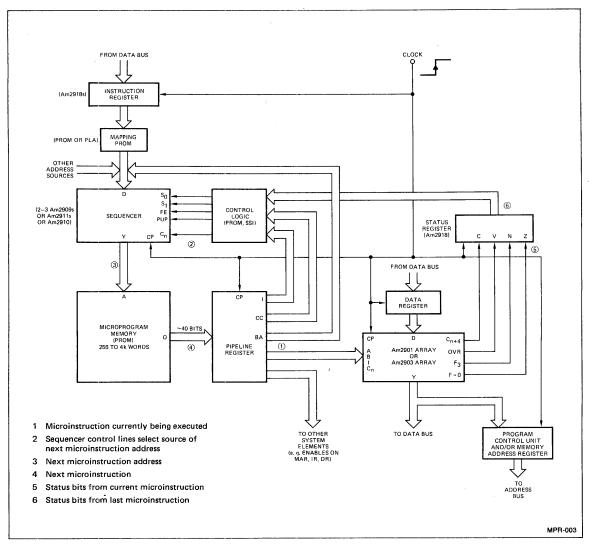

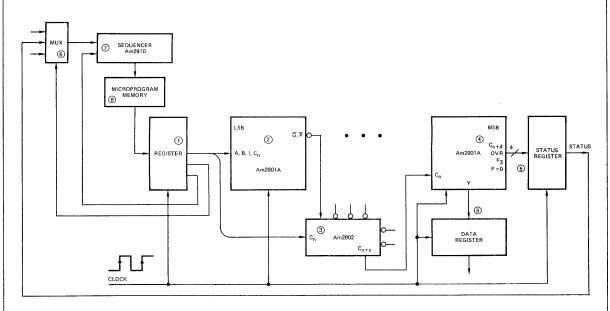

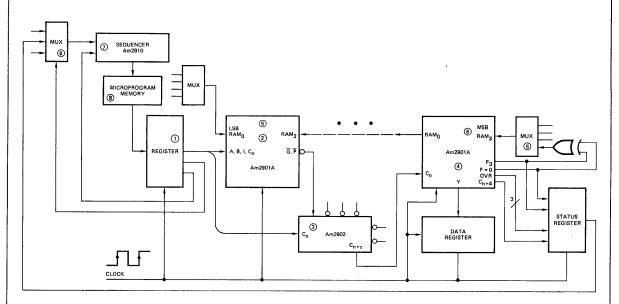

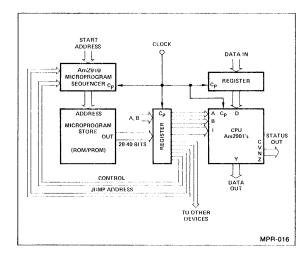

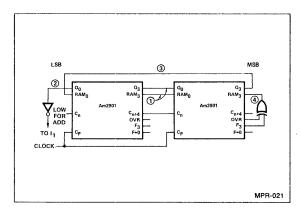

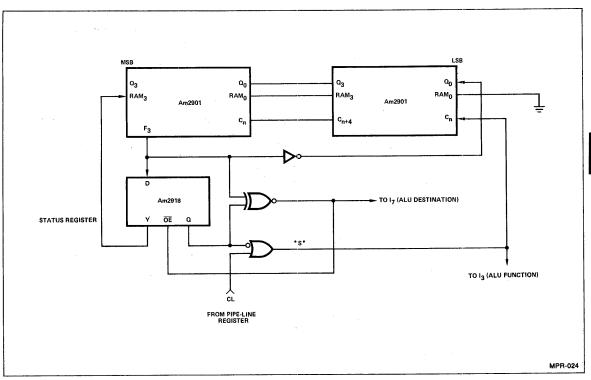

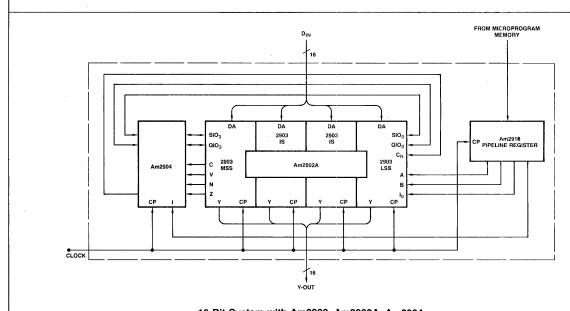

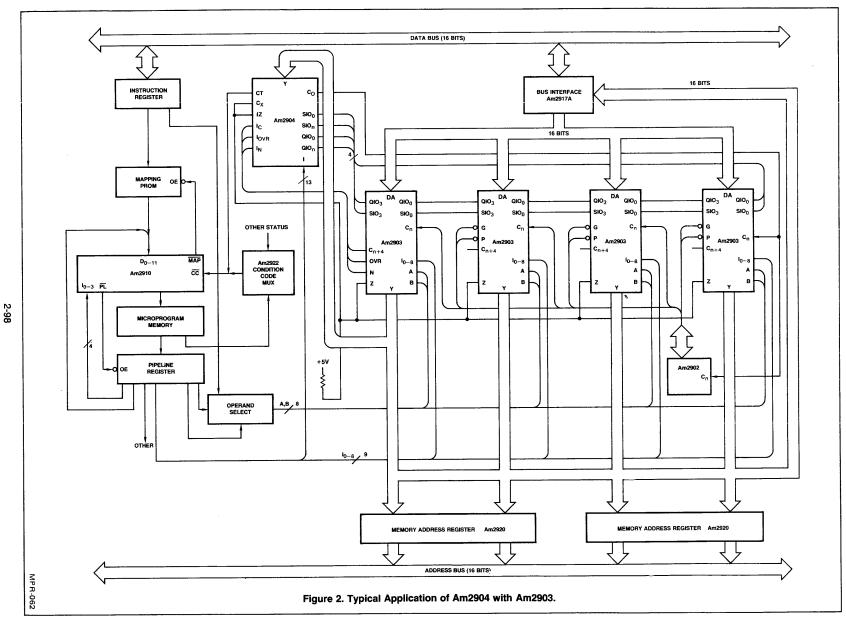

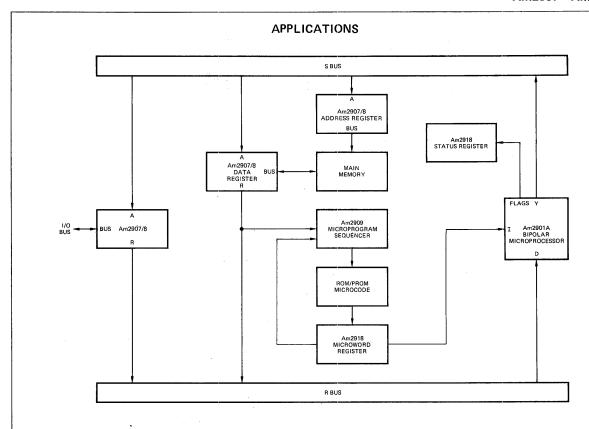

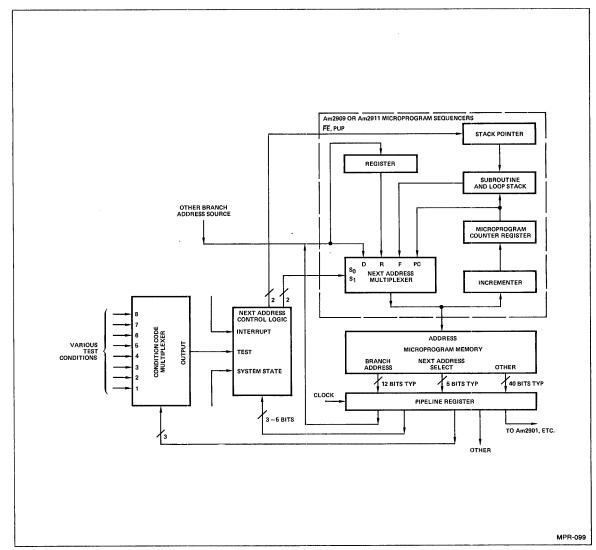

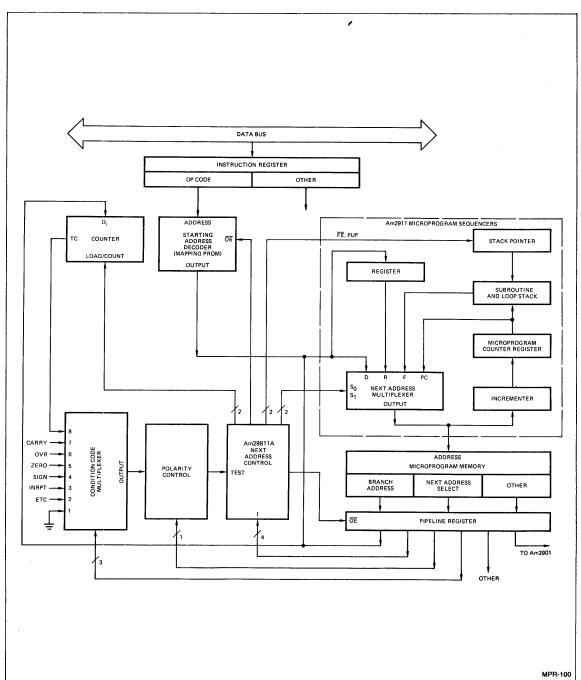

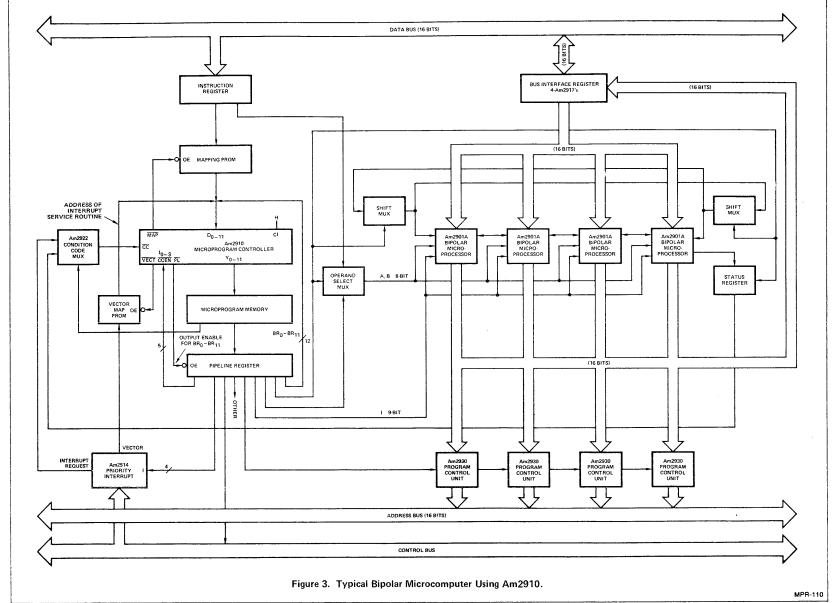

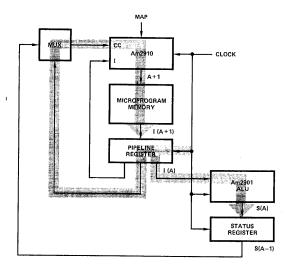

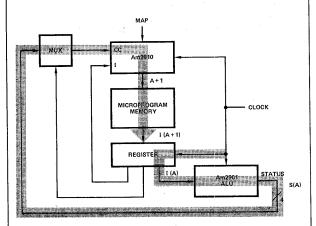

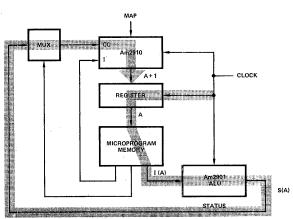

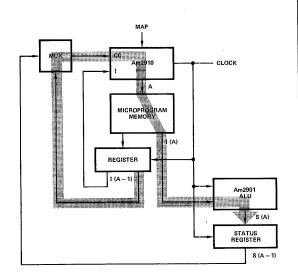

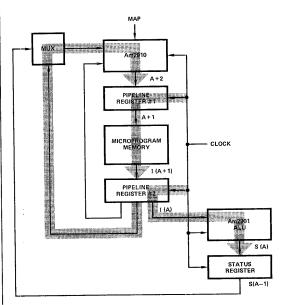

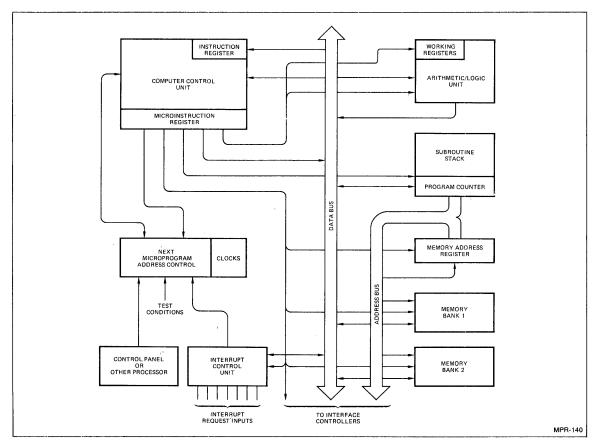

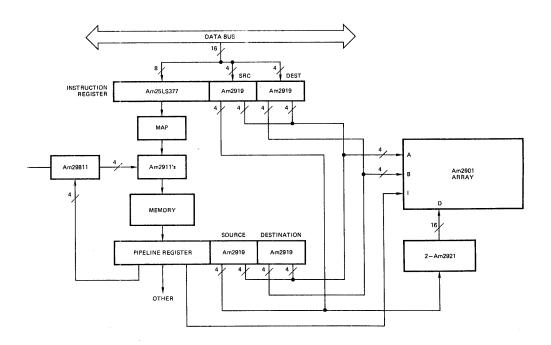

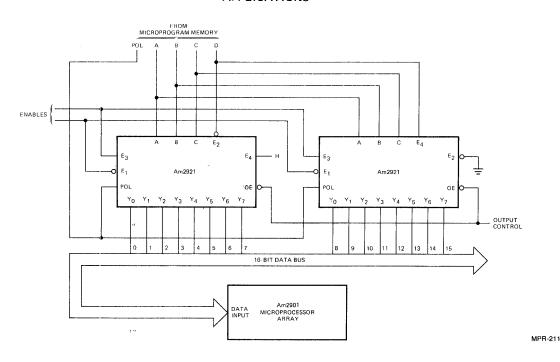

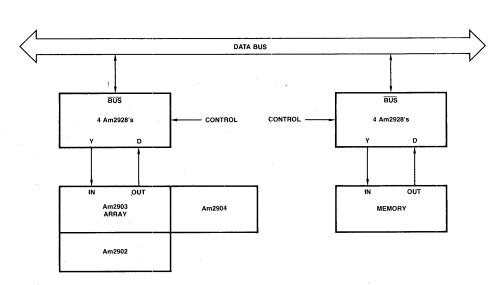

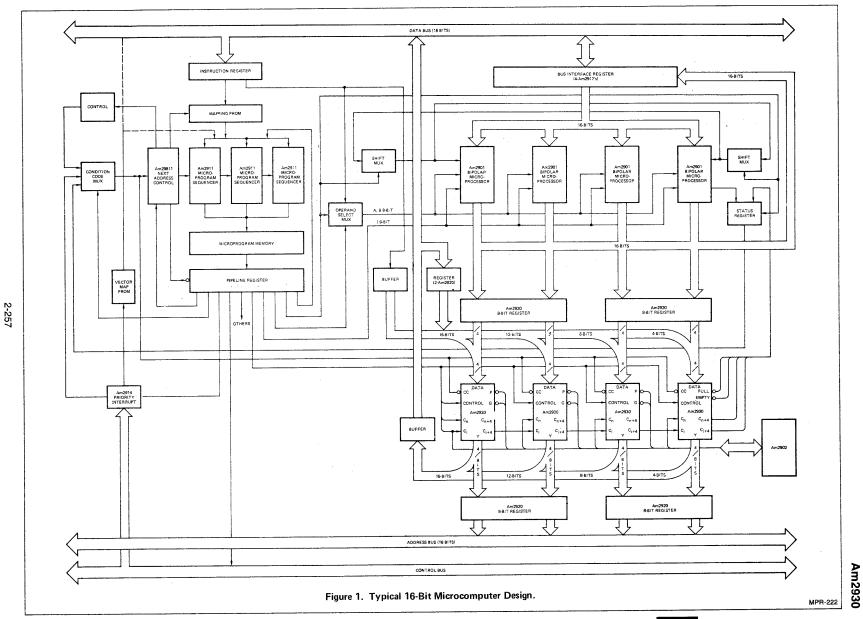

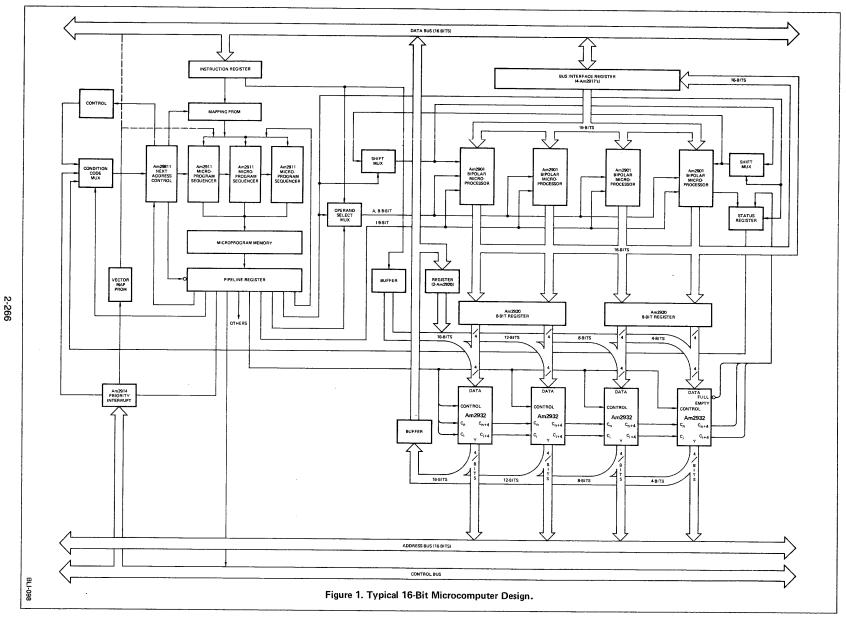

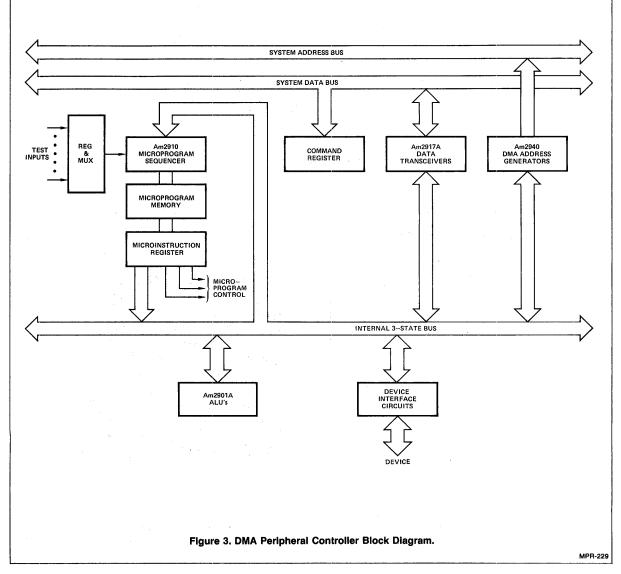

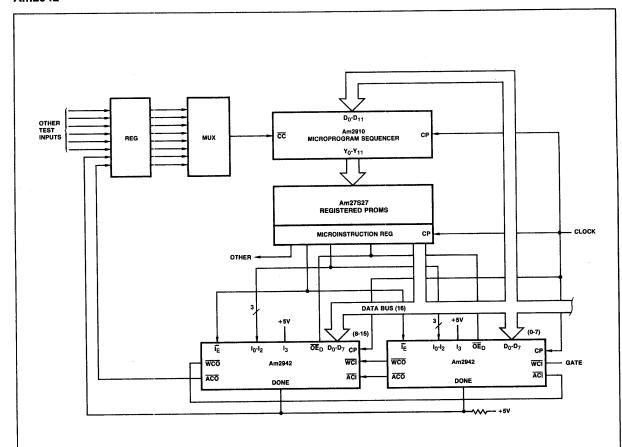

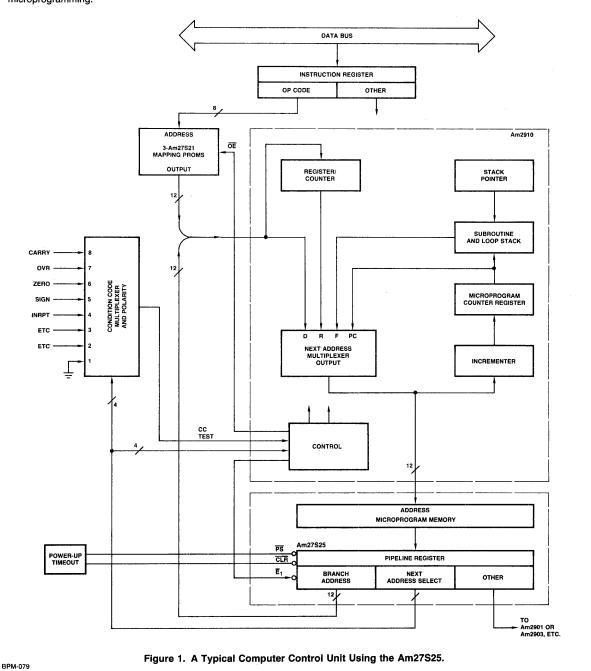

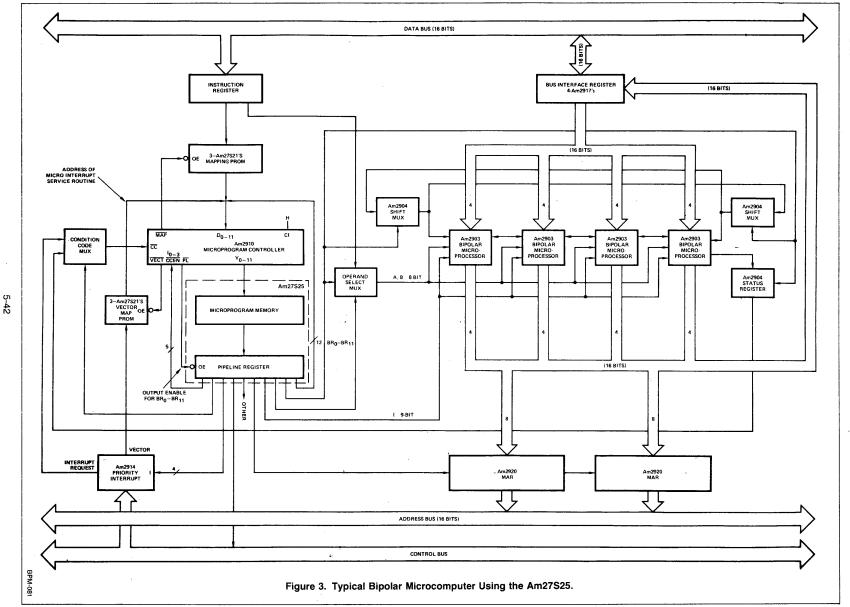

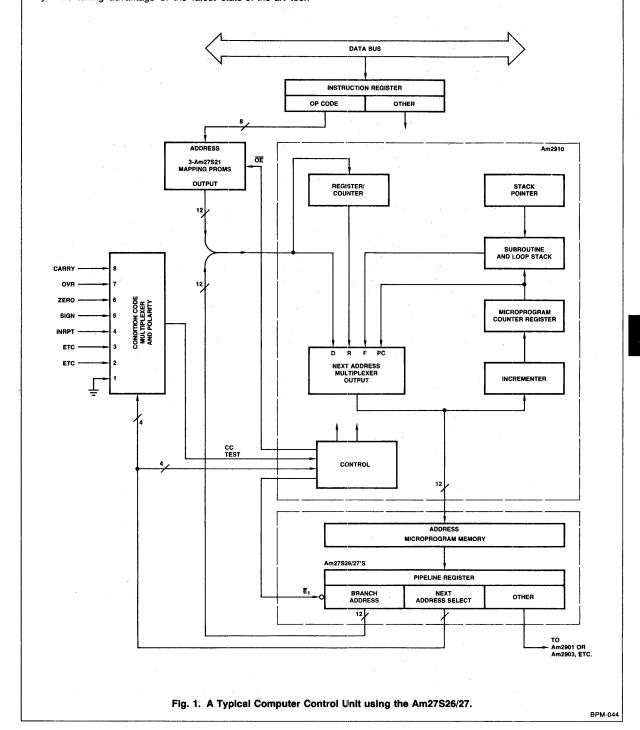

Figure 3 illustrates a typical system architecture. There are two "sides" to the system. At the left is the control circuitry and on the right is the data manipulation circuitry. The block labeled "2901 array" consists of the ALU, scratchpad registers, data steering logic (all internal to the Am2901's), plus left/

right shift control and carry lookahead circuit. Data is processed by moving it from main memory (not shown) into the 2901 registers, performing the required operations on it and returning the result to main memory. Memory addresses may also be generated in the 2901's and sent out to the memory address register (MAR). The four status bits from the 2901's ALU are captured in the status register after each operation.

The logic on the left side is the control section of the computer. This is where the Am2909, 2910, or 2911 is used. The entire system is controlled by a memory, usually PROM, which contains long words called microinstructions. Each microinstruction contains bits to control each of the data manipulation elements in the system. There are, for example, nine bits for the 2901 instruction lines, eight bits for the A and B register addresses, two or three bits to control the shifting multiplexers at the ends of the 2901 array (Figure 19 on 2901 data sheet), and bits to control the register enables on the MAR, instruction register, and various bus transceivers. When the bits in a microinstruction are applied to all the data elements and everything is clocked, then one small operation (such as a data transfer or a register-to-register add) will occur.

A "machine instruction" (such as a minicomputer instruction or a 9080A instruction) is performed by executing several microinstructions in sequence. Each microinstruction therefore contains not only bits to control the data hardware, but also bits to define the location in PROM of the next microinstruction to be executed. The fields are labeled in Figure 3 as I, CC, and BA. The I field controls the sequencer. It indicates where the next address is located — the  $\mu$ PC, the stack, or the direct inputs — and whether the stack is to be pushed or popped.

The CC field contains bits indicating the conditions under which the I field applies. These are compared with the condition codes in the status register and may cause modification to the I field. The comparing and modification occurs in the block labeled "control logic". Frequently this is a PROM or PLA. In the case of the Am2910, it is built into the chip. The BA field is a branch address or the address of a subroutine.

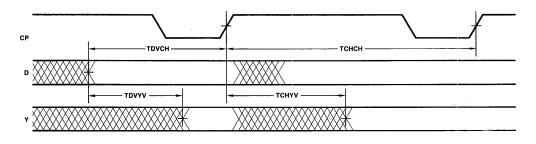

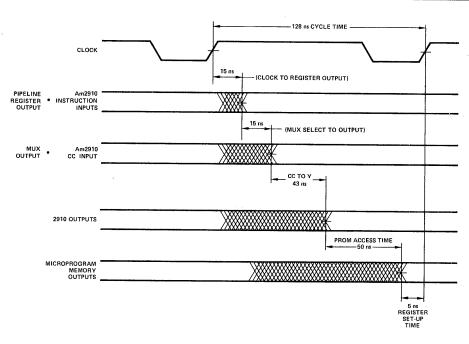

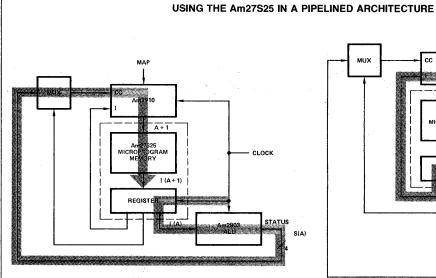

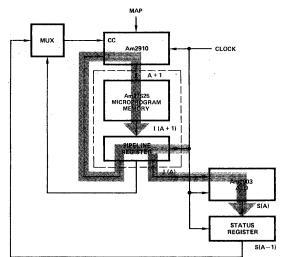

#### **PIPELINING**

The address for the microinstructions is generated by the sequencer, starting from a clock edge. The address goes from the sequencer to the ROM and, an access time later, the microinstruction is at the ROM outputs.

A pipeline register is a register placed on the output of the microprogram memory to essentially split the system in two. The pipeline register contains the microinstruction currently being executed 1. (Refer to the circled numbers in Figure 3.) The data manipulation control bits go out to the system elements and a portion of the microinstruction is returned to the sequencer (2) to determine the address of the next microinstruction to be executed. That address (3) is sent to the ROM and the next microinstruction 4 sits at the input of the pipeline register. So while the 2901's are executing one instruction, the next instruction is being fetched from ROM. Note that there is no sequential logic in the sequencer between the select lines and the output. This is important because the loop 1 to 2 to 3 to 4 must occur during a single clock cycle. During the same time, the loop from 1 to 5 must occur in the 2901's. These two paths are roughly the same (around 200ns worst case for a 16-bit system). The presence of the pipeline register allows the microinstruction fetch to occur in parallel with the data operation rather than serially, allowing the clock frequency to be doubled.

#### Introduction

Figure 3.

The system shown in Figure 3 works as follows. A sequence of microinstructions in the PROM is executed to fetch an instruction from main memory. This requires that the program counter, often in a 2901 working register, be sent to the memory address register and incremented. The data returned from memory is loaded into the instruction register. The contents of the instruction register is passed through a PROM or PLA to generate the address of the first microinstruction which must be executed to perform the required function. A branch to this address occurs through the sequencer. Several microinstructions may be executed to fetch data from memory, perform ALU operations, test for overflow, and so forth. Then a branch will be made back to the instruction fetch cycle. At this point, there may be branches to other sections of micro-

code. For example, the machine might test for an interrupt here and obtain an interrupt service routine address from another mapping ROM rather than start on the next machine instruction. There are obviously many possibilities. Throughout this data book, in application notes, and within data sheets, some suggested techniques will be found.

Additional application notes are in preparation and are planned for publication. Advanced Micro Devices' Applications' staff is available to answer questions and provide technical assistance as well. They may be reached by calling (408) 732-2400, or, outside California (800) 538-8450. Ask for Am2900 Family Applications.

Four-Bit Bipolar Microprocessor Slice

#### **DISTINCTIVE CHARACTERISTICS**

- Two-address architecture –

Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU Performs addition, two subtraction operations, and five logic functions on two source operands.

- Flexible data source selection —

ALU data is selected from five source ports for a total of 203 source operand pairs for every ALU function.

- Left/right shift independent of ALU –

Add and shift operations take only one cycle.

- Four status flags –

Carry, overflow, zero, and negative.

- Expandable –

Connect any number of Am2901's together for longer word lengths.

- Microprogrammable Three groups of three bits each for source operand, ALU function, and destination control.

- Fast –

Am2901B is up to 27% faster than Am2901A, up to 50% faster than Am2901. The Am2901B meets or exceeds all of the specifications for the Am2901 and Am2901A.

#### **TABLE OF CONTENTS**

| Block Diagrams                             |

|--------------------------------------------|

| Function Tables                            |

| Order Codes                                |

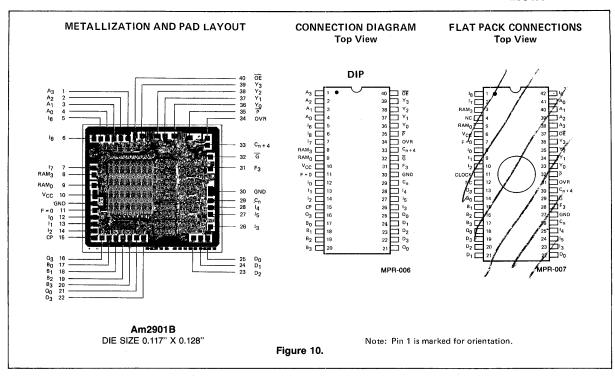

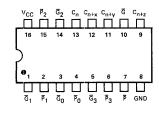

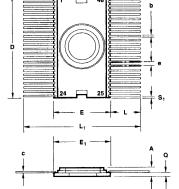

| Connection Diagram 2-7                     |

| Pin Definitions 2-7                        |

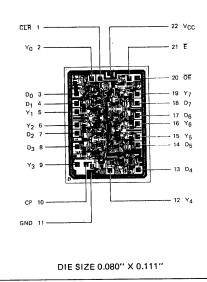

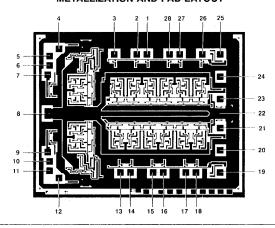

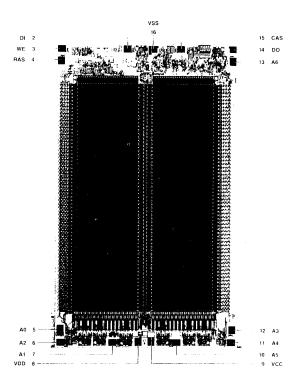

| Metallization Pattern 2-7                  |

| DC Characteristics 2-9                     |

| Switching Characteristics 2-10, 2-11, 2-12 |

| Speed Calculations                         |

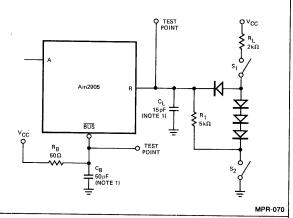

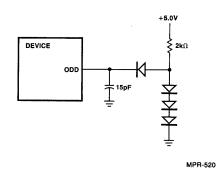

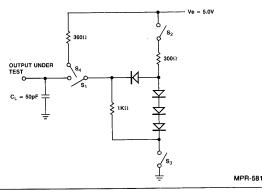

| Burn-in Circuit                            |

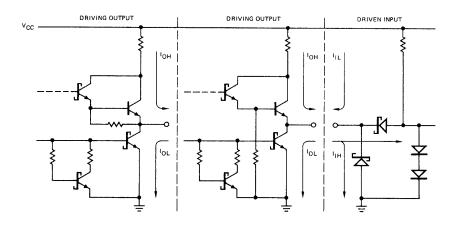

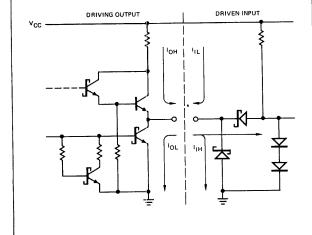

| I/O Interface Conditions                   |

| Applications                               |

|                                            |

For applications information see the last part of this data sheet and chapters III and IV of "Build a Microcomputer", AMD's application note series on the Am2900 Family.

#### **GENERAL DESCRIPTION**

The four-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPU's, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the Am2901 will allow efficient emulation of almost any digital computing machine.

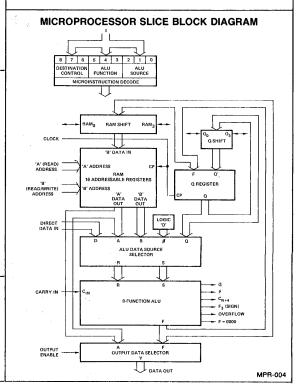

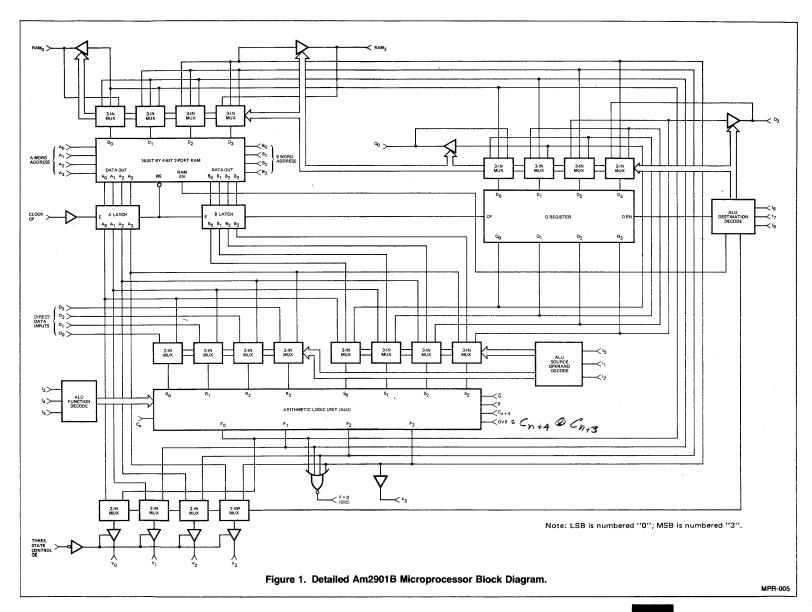

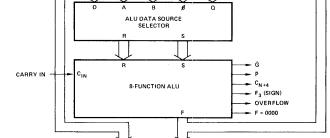

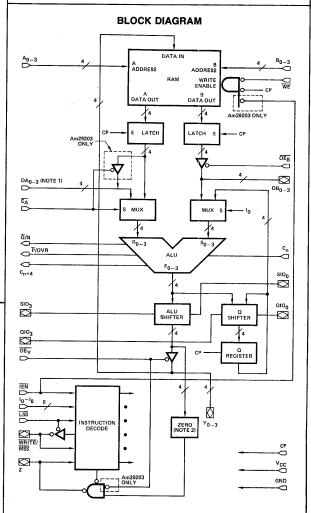

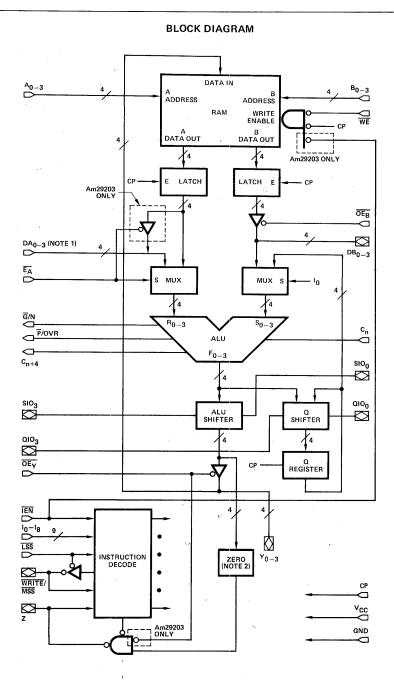

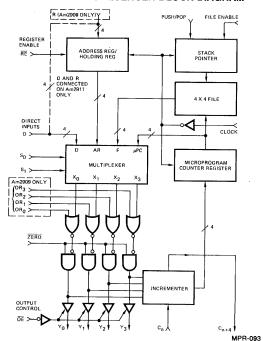

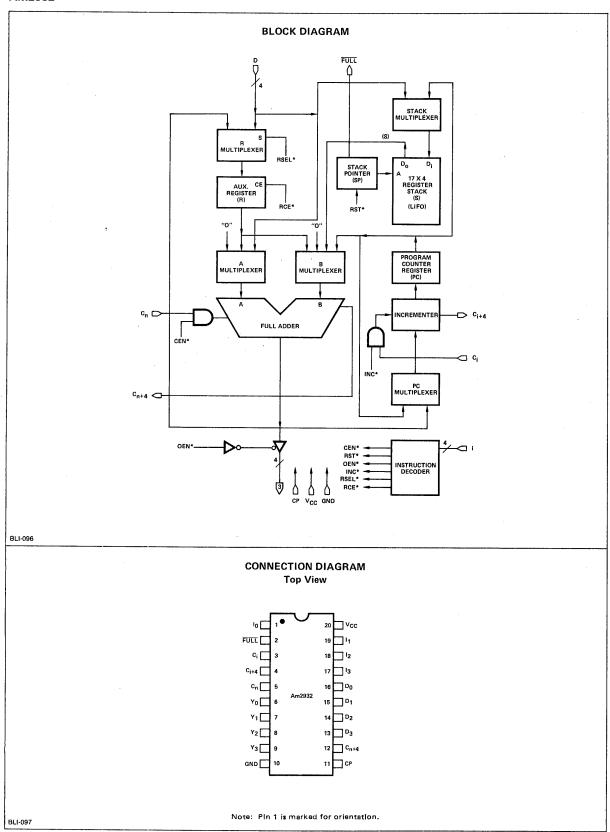

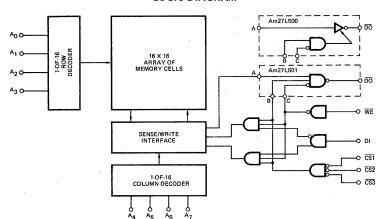

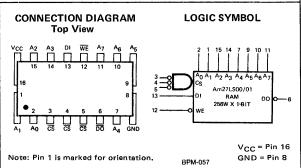

The device, as shown in the block diagram below, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

The Am2901B is a plug-in replacement for the Am2901 or Am2901A, but is 25% faster than the Am2901A and 50% faster than the Am2901.

#### **ARCHITECTURE**

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, A0, BD, BQ, B0, DQ, D0 and Q0. It is apparent that AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I0, I1, and I2 inputs. The definition of I0, I1, and I2 for the eight source operand combinations are as shown in Figure 2. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to select the

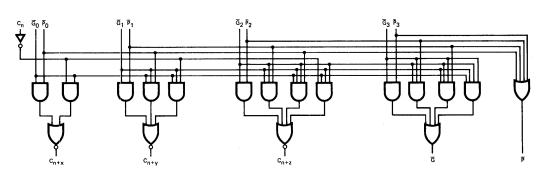

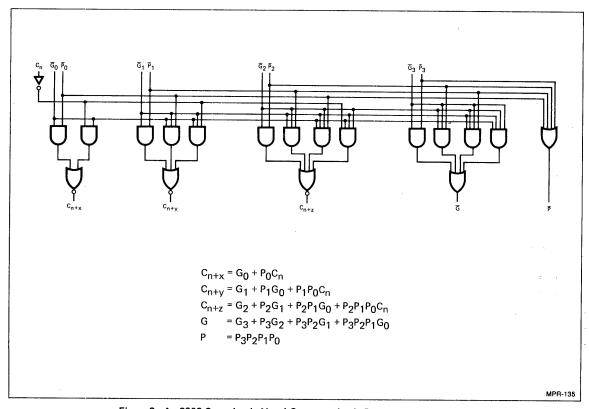

ALU function. The definition of these inputs is shown in Figure 3. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\overline{G}$ , and carry propagate,  $\overline{P}$ , are outputs of the device for use with a carry-look-ahead-generator such as the Am2902. A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in  $(C_n)$  and carry-out  $(C_{n+4})$  are active HIGH.

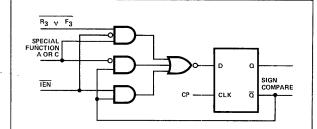

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $F_3$ . The  $F_3$  is non-inverted with respect to the sign bit output  $F_3$ . The  $F_3$  is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices.  $F_3$  is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $F_3$  and  $F_3$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. These combinations are shown in Figure 4.

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control  $(\overline{OE})$  is used to enable the three-state outputs. When  $\overline{OE}$  is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Figure 4 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position ( $\dot{\tau}2$ ). The shifter has two ports; one is labeled RAM0 and the other is labeled RAM3. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the FAM3 buffer is enabled and the RAM0 multiplexer input is enabled. Likewise, in the shift down mode, the RAM0 buffer and RAM3 input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the  $I_6$ ,  $I_7$  and  $I_8$  microinstruction inputs as defined in Figure 4.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-Jown mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  ${\restriction}_6$ ,  ${\restriction}_7$ , and  ${\restriction}_8$  as shown in Figure 4.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) definec by the B address field when the clock input is LOW.

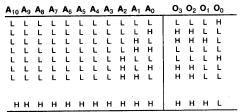

|          | MICRO CODE     |                |                |               | ALU SO |   |

|----------|----------------|----------------|----------------|---------------|--------|---|

| Mnemonic | l <sub>2</sub> | l <sub>1</sub> | l <sub>o</sub> | Octal<br>Code | R      | s |

| AQ       | L              | L.             | L              | 0             | Α      | α |

| AB       | L              | L              | н              | 1             | Α      | В |

| ZQ       | L              | Н              | L              | 2             | 0      | a |

| ZB       | L              | н              | H              | 3             | 0      | В |

| ZA       | н              | L              | L              | 4             | 0      | Α |

| DA       | н              | L              | н              | 5             | D      | Α |

| DQ       | н              | н              | L              | 6             | D      | a |

| DZ       | н              | н              | н              | 7             | D      | 0 |

|          | ı  | MICE | RO C       | ODE           | ALU        | SYMBOL  |  |

|----------|----|------|------------|---------------|------------|---------|--|

| Mnemonic | 15 | 14   | <b>I</b> 3 | Octal<br>Code | Function   | STWIBOL |  |

| ADD      | L  | L    | L          | 0             | R Plus S   | R + S   |  |

| SUBR     | L  | L    | н          | 1             | S Minus R  | S - R   |  |

| SUBS     | L  | н    | L          | 2             | R Minus S  | R - S   |  |

| OR       | L  | н    | н          | 3             | R OR S     | RVS     |  |

| AND      | н  | L    | L          | 4             | RANDS      | R∧S     |  |

| NOTRS    | н  | L    | н          | 5             | RANDS      | ₹∧s     |  |

| EXOR     | н  | н    | L          | 6             | R EX OR S  | R₩S     |  |

| EXNOR    | н  | н    | н          | 7             | R EX-NOR S | R₩S     |  |

Figure 2. ALU Source Operand Control.

Figure 3. ALU Function Control.

|          | MICRO CODE     |                |                |               |       | REG.<br>CTION | v     | RAM<br>SHIFTER |        | Q<br>SHIFTER     |                  |                 |                 |

|----------|----------------|----------------|----------------|---------------|-------|---------------|-------|----------------|--------|------------------|------------------|-----------------|-----------------|

| Mnemonic | I <sub>8</sub> | I <sub>7</sub> | I <sub>6</sub> | Octal<br>Code | Shift | Load          | Shift | Load           | OUTPUT | RAM <sub>0</sub> | RAM <sub>3</sub> | $\mathbf{q}_0$  | $\mathbf{a}_3$  |

| QREG     | L              | L              | L              | 0             | х     | NONE          | NONE  | F → Q          | F      | ×                | X                | ×               | ×               |

| NOP      | L              | L              | Н              | 1             | ×     | NONE          | ×     | NONE           | F      | ×                | ×                | х               | ×               |

| RAMA     | L              | Н              | L              | 2             | NONE  | F→B           | ×     | NONE           | Α      | ×                | ×                | х               | х               |

| RAMF     | L              | Н              | н              | 3             | NONE  | F → B         | ×     | NONE           | F      | ×                | x                | х               | ×               |

| RAMQD    | Н              | L              | L              | 4             | DOWN  | F/2 → B       | DOWN  | 0/2 → 0        | F      | Fo               | IN <sub>3</sub>  | Q <sub>0</sub>  | IN <sub>3</sub> |

| RAMD     | н              | L              | Н              | 5             | DOWN  | F/2 → B       | ×     | NONE           | F      | F <sub>0</sub>   | IN <sub>3</sub>  | α <sub>0</sub>  | ×               |

| RAMQU    | н              | н              | L              | 6             | UP    | 2F → B        | UP    | 20 → 0         | F      | IN <sub>0</sub>  | F <sub>3</sub>   | IN <sub>0</sub> | Q <sub>3</sub>  |

| RAMU     | Н              | н              | н              | 7             | UP    | 2F → B        | ×     | NONE           | F      | INo.             | F <sub>3</sub>   | ×               | Q <sub>3</sub>  |

<sup>\*</sup> PON'T USE

Figure 4. ALU Destination Control.

| N                  | 210 OCTAL                                             | 0                       | 1            | 2          | 3        | 4         | 5            | 6            | 7          |

|--------------------|-------------------------------------------------------|-------------------------|--------------|------------|----------|-----------|--------------|--------------|------------|

| O 15<br>A 4<br>L 3 | ALU<br>Source<br>ALU<br>Function                      | Α, Q                    | A, B         | ο, α       | О, В     | Ο, Α      | D, A         | D, Q         | D, O       |

| 0                  | C <sub>n</sub> = L<br>R Plus S<br>C <sub>n</sub> = H  | A+Q<br>A+Q+1            | A+B<br>A+B+1 | Q<br>Q+1   | B<br>B+1 | A<br>A+1  | D+A<br>D+A+1 | D+Q<br>D+Q+1 | D<br>D+1   |

| 1                  | C <sub>n</sub> = L<br>S Minus R<br>C <sub>n</sub> = H | Q-A-1<br>Q-A            | B-A-1<br>B-A | Q-1<br>Q   | B-1<br>B | A-1<br>A  | A-D-1<br>A-D | Q-D-1<br>Q-D | -D-1<br>-D |

| 2                  | Cn = L<br>R Minus S<br>Cn = H                         | A-Q-1<br>A-Q            | AB1<br>AB    | -Q-1<br>-Q | B1<br>B  | -A-1<br>A | D-A-1<br>D-A | D-Q-1<br>D-Q | D-1<br>D   |

| 3                  | R OR S                                                | ΑVQ                     | A∨B          | a          | В        | А         | D∨A          | DVQ          | D          |

| 4                  | R AND S                                               | ΑΛQ                     | A ^ B        | 0          | 0        | 0         | DAA          | D∧Q          | 0          |

| 5                  | Ř AND S                                               | $\overline{A} \wedge Q$ | Ā∧B          | α          | В        | А         | Õ∧A          | ō∧o          | 0          |

| 6                  | R EX-OR S                                             | Α¥Q                     | A∀B          | Q          | В        | А         | D∀A          | D∀Q          | D          |

| 7                  | R EX-NORS                                             | ĀΨŪ                     | Ā∀B          | ā          | B        | Ā         | D∀∙A         | D∀Q          | D          |

<sup>+ =</sup> Plus; -- = Minus; V = OR; ∧ = AND; ∀ = EX-OR

Figure 5. Source Operand and ALU Function Matrix.

TON'T USE DISABLE FEN A BNABLE FEN

X = Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state

B = Register Addressed by B inputs.

UP is toward MSB, DOWN is toward LSB.

Figure 4. ALU Destination Control

#### SOURCE OPERANDS AND ALU FUNCTIONS

There are eight source operand pairs available to the ALU as selected by the  $I_0$ ,  $I_1$ , and  $I_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_n$ , also affects the ALU results when in the arithmetic mode. The  $C_n$  input has no effect in the logic mode. When  $I_0$  through  $I_5$  and  $C_n$  are viewed together, the matrix of

Figure 5 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed while in the logic mode, the carry will have no bearing on the ALU output. Figure 6 defines the various logic operations that the Am2901 can perform and Figure 7 shows the arithmetic functions of the device. Both carry-in LOW ( $C_n=0$ ) and carry-in HIGH ( $C_n=1$ ) are defined in these operations.

| Ocal<br>  <sub>543</sub> ,  <sub>210</sub> | Group  | Function                         |

|--------------------------------------------|--------|----------------------------------|

| 40<br>41<br>45<br>46                       | AND    | A ^ Q<br>A ^ B<br>D ^ A<br>D ^ Q |

| 3 0<br>5 1<br>3 5<br>3 6                   | OR     | A V Q<br>A V B<br>D V A<br>D V Q |

| 6 0<br>6 1<br>6 5<br>6 6                   | EX-OR  | A∀Q<br>A∀B<br>D∀A<br>D∀Q         |

| 7 0<br>7 1<br>7 5<br>7 6                   | EX-NOR | Ā∀Q<br>Ā∀B<br>D∀A<br>D∀Q         |

| 7 2<br>7 :<br>7 +<br>77                    | INVERT | Q<br>B<br>A                      |

| 62<br>63<br>64                             | PASS   | Q<br>B<br>A<br>D                 |

| 3 2<br>3 3<br>3 4<br>3 7                   | PASS   | Q<br>B<br>A<br>D                 |

| 4 2<br>4 3<br>4 4<br>4 7                   | "ZERO" | 0<br>0<br>0<br>0                 |

| 5 0<br>5 1<br>5 5<br>5 6                   | MASK   | Ā∧Q<br>Ā∧B<br>Ō∧A<br>Ō∧Q         |

Fiure 6. ALU Logic Mode Functions.

| Octal                               | C <sub>n</sub> = 0 | (Low)    | C <sub>n</sub> = 1 | (High)   |

|-------------------------------------|--------------------|----------|--------------------|----------|

| l <sub>543</sub> , l <sub>210</sub> | Group              | Function | Group              | Function |

| 0 0                                 |                    | A+Q      |                    | A+Q+1    |

| 0 1                                 | ADD                | A+B      | ADD plus           | A+B+1    |

| 0 5                                 |                    | D+A      | one                | D+A+1    |

| 0 6                                 |                    | D+Q      |                    | D+Q+1    |

| 0 2                                 |                    | Q        |                    | Q+1      |

| 0 3                                 | PASS               | В        | Increment          | B+1      |

| 0 4                                 |                    | Α        |                    | A+1      |

| 0 7                                 |                    | D        |                    | D+1      |

| 1 2                                 |                    | Q-1      |                    | a        |

| 1 3                                 | Decrement          | B-1      | PASS               | В        |

| 1.4                                 |                    | A-1      |                    | Α        |

| 2 7                                 |                    | D-1      |                    | D        |

| 2 2                                 | ,                  | _Q_1     |                    | Q        |

| 2 3                                 | 1's Comp.          | B-1      | 2's Comp.          | _B       |

| 2 4                                 | INV.               | -A-1     | (Negate)           | _A       |

| 17                                  |                    | D1       |                    | -D       |

| 1 0                                 |                    | Q-A-1    |                    | Q-A      |

| 11                                  | Subtract           | B-A-1    | Subtract           | BA       |

| 15                                  | (1's Comp)         | A-D-1    | (2's Comp)         | AD       |

| 1 6                                 |                    | Q-D-1    |                    | Q-D      |

| 2 0                                 |                    | A-Q-1    |                    | A-Q      |

| 2 1                                 |                    | AB-1     |                    | A-B      |

| 2 5                                 |                    | D-A-1    |                    | D-A      |

| 2 6                                 |                    | D-Q-1    |                    | D-Q      |

Figure 7. ALU Arithmetic Mode Functions.

#### LOGIC FUNCTIONS FOR G, P, $c_{n+4}$ , AND OVR

The four signals G, P,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the Am2901 is in the add or subtract mode. The table below indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Figure 2.

#### Definitions (+ = OR)

| $P_0 = R_0 + S_0$             | $G_0 = R_0 S_0$                              |

|-------------------------------|----------------------------------------------|

| $P_1 = R_1 + S_1$             | $G_1 = R_1 S_1$                              |

| $P_2 = R_2 + S_2$             | $G_2 = R_2 S_2$                              |

| $P_3 = R_3 + S_3$             | $G_3 = R_3S_3$                               |

| $C_4 = G_3 + P_3G_2 + F_3$    | $P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_n$ |

| $C_3 = G_2 + P_2G_1 + F_2G_1$ | $P_2P_1G_0 + P_2P_1P_0C_n$                   |

| 1543 | Function | P                                                                                           | Ğ                                                                                                                                                           | C <sub>n+4</sub>                                                                   | OVR                                                                                |  |  |  |  |  |  |

|------|----------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0    | R + S    | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                 | $\overline{G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0}$                                                                                                        | . C4                                                                               | C <sub>3</sub> <del>∀</del> C <sub>4</sub>                                         |  |  |  |  |  |  |

| 1    | S – R    |                                                                                             | Same as R + S equations, but substitute $\overline{R_i}$ for $R_i$ in definitions                                                                           |                                                                                    |                                                                                    |  |  |  |  |  |  |

| 2    | R – S    |                                                                                             | Same as R + S equations, but substitute $\overline{S_i}$ for $S_i$ in definitions                                                                           |                                                                                    |                                                                                    |  |  |  |  |  |  |

| 3    | R∨S      | LOW                                                                                         | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                                 | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub>       | $\overline{P_3}_{2}P_1P_0 + C_n$                                                   |  |  |  |  |  |  |

| 4    | R ∧ S    | LOW                                                                                         | $\overline{G_3 + G_2 + G_1 + G_0}$                                                                                                                          | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub> | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> + C <sub>n</sub> |  |  |  |  |  |  |

| 5    | R∧S      | LOW ————————————————————————————————————                                                    |                                                                                                                                                             |                                                                                    |                                                                                    |  |  |  |  |  |  |

| 6    | R∀S      | Same as $\overline{R} \forall S$ , but substitute $\overline{R}_i$ for $R_i$ in definitions |                                                                                                                                                             |                                                                                    |                                                                                    |  |  |  |  |  |  |

| 7    | R∀S      | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub>                           | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> + P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> | $\frac{G_3 + P_3G_2 + P_3P_2G_1}{+ P_3P_2P_1P_0 (G_0 + \overline{C_n})}$           | Seenote                                                                            |  |  |  |  |  |  |

$\mathsf{Note} \colon [\overline{\mathsf{P}}_2 + \overline{\mathsf{G}}_2 \overline{\mathsf{P}}_1 + \overline{\mathsf{G}}_2 \overline{\mathsf{G}}_1 \overline{\mathsf{P}}_0 + \overline{\mathsf{G}}_2 \overline{\mathsf{G}}_1 \overline{\mathsf{G}}_0 \mathsf{C}_n] \, \forall \, [\overline{\mathsf{P}}_3 + \overline{\mathsf{G}}_3 \overline{\mathsf{P}}_2 + \overline{\mathsf{G}}_3 \overline{\mathsf{G}}_2 \overline{\mathsf{P}}_1 + \overline{\mathsf{G}}_3 \overline{\mathsf{G}}_2 \overline{\mathsf{G}}_1 \overline{\mathsf{P}}_0 + \overline{\mathsf{G}}_3 \overline{\mathsf{G}}_2 \overline{\mathsf{G}}_1 \overline{\mathsf{G}}_0 \mathsf{C}_n]$

+ = OR

Figure 8.

#### **ORDERING INFORMATION**

Order the part number according to the table below to obtain the desired package, temperature range, and scriening level.

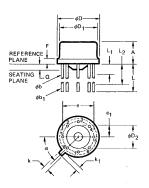

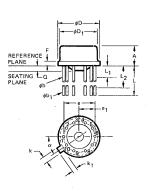

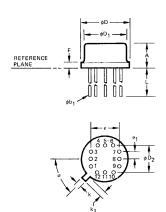

| Am2901<br>Order Number | Am2901A<br>Order Number | Am2901B<br>Order Number | Package Type<br>(Note 1) | Operating Range<br>(Note 2) | Screening Leve<br>(Note 3)                    |

|------------------------|-------------------------|-------------------------|--------------------------|-----------------------------|-----------------------------------------------|

| AM2901PC               | AM2901APC               | AM2901BPC               | P-40                     | С                           | C-1                                           |

| AM2901DC               | AM2901ADC               | AM2901BDC               | D-40                     | С                           | C-1                                           |

| AM2901DC-B             | AM2901ADC-B             | AM2901BDC-B             | D-40                     | С                           | B-2 (Note 4)                                  |

|                        | AM2901ADM               | AM2901BDM               | D-40                     | M                           | C-3                                           |

|                        | AM2901ADM-B             | AM2901BDM-B             | D-40                     | М                           | B-3                                           |

|                        | AM2901AFM               | AM2901BFM               | F-42                     | M                           | C-3                                           |

|                        | AM2901AFM-B             | AM2901BFM-B             | F-42                     | М                           | B-3                                           |

|                        | AM2901AXC<br>AM2901AXM  | AM2901BXC<br>AM2901BXM  | Dice<br>Dice             | С<br>М                      | Visual inspection to MIISTD-883 Method 2010B. |

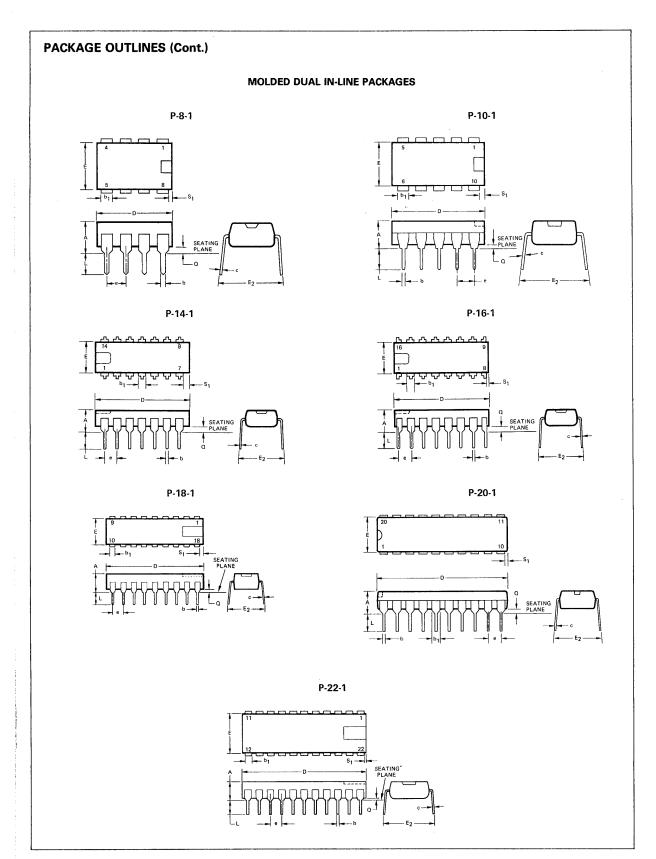

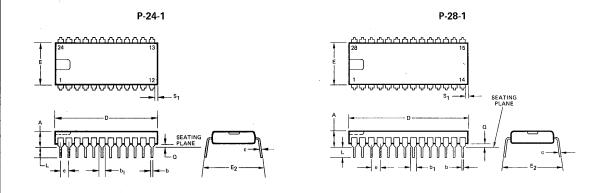

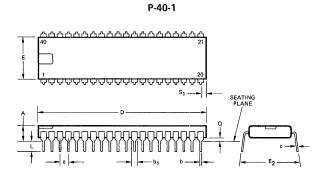

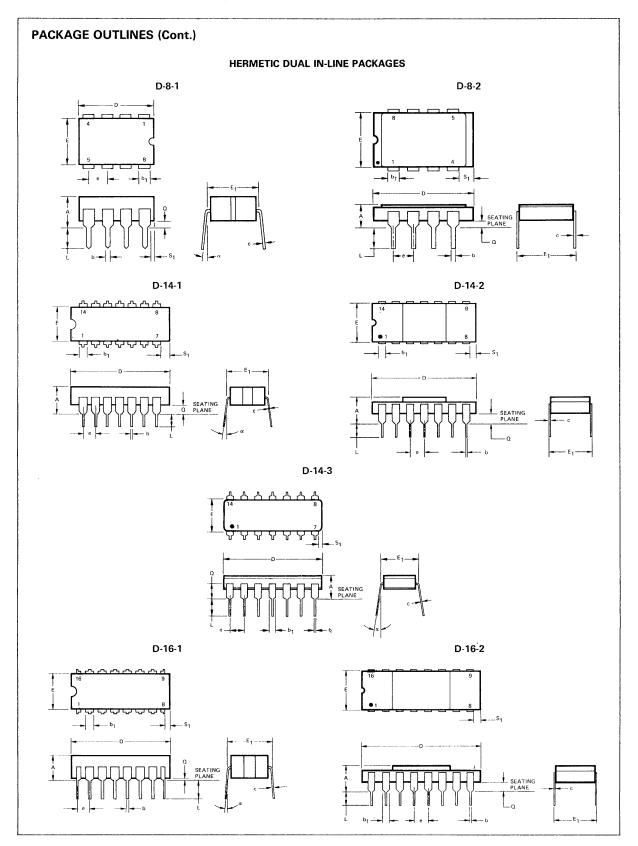

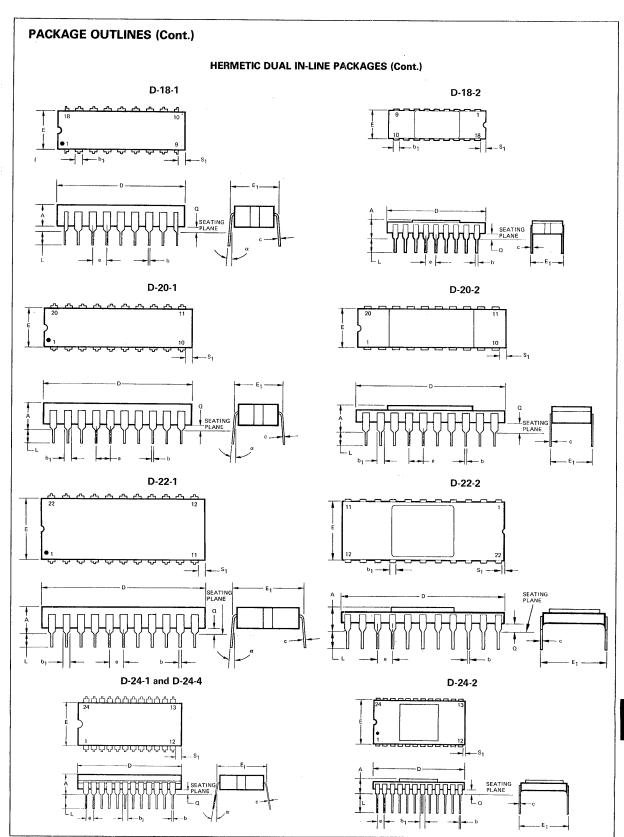

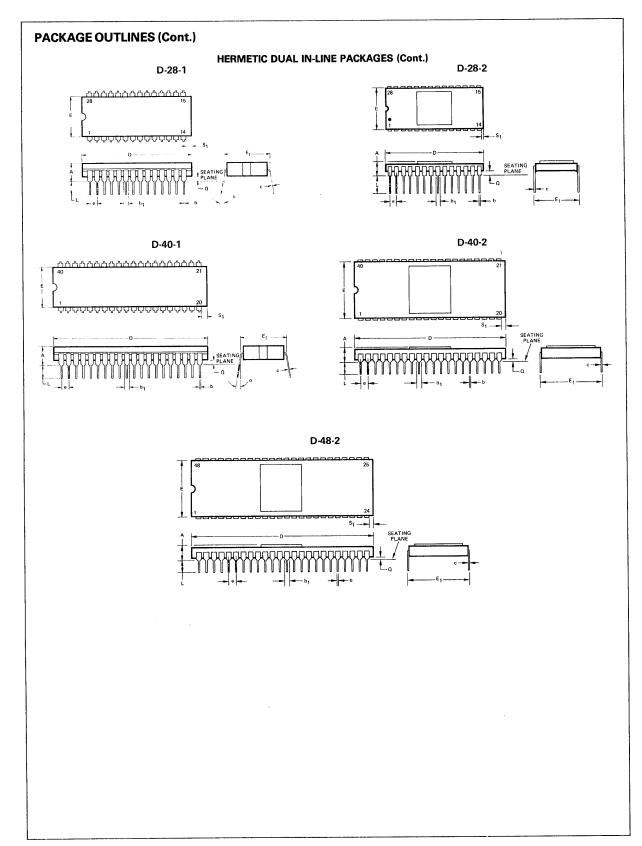

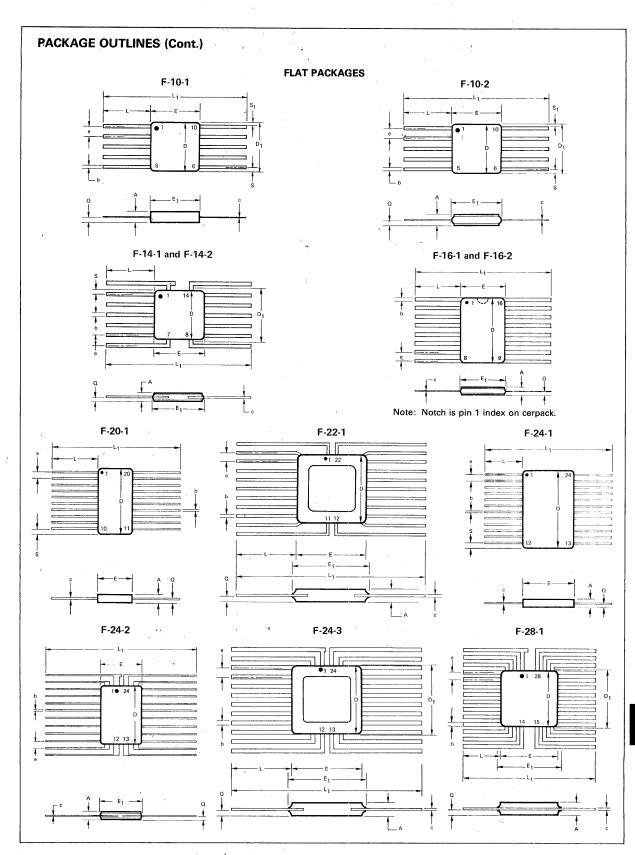

Notes: 1. P = Molded DIP, D = Hermetic DIP, F = Flat Pak. Number following letter is number of leads. See Appendix B fodetailed outline. Where Appendix B contains several dash numbers, any of the variations of the package may be used unless inerwise specified.

- 2. C = 0°C to +70°C, V<sub>CC</sub> = 4.75V to 5.25V, M = -55°C to +125°C, V<sub>CC</sub> = 4.50V to 5.50V.

3. See Appendix A for details of screening. Levels C-1 and C-3 conform to MIL-STD-883, Class C. Level B-3 conforms MIL-STD-883, Class B.

- 4. 96 hour burn-in.

Figure 9.

#### PIN DEFINITIONS

- A<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the A-port.

- B<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the B-port and into which new data can be written when the clock goes LOW.

- I<sub>0-8</sub> The nine instruction control lines. Used to determine what data sources will be applied to the ALU (I<sub>012</sub>), what function the ALU will perform (I<sub>345</sub>), and what data is to be deposited in the Q-register or the register stack (I<sub>678</sub>).

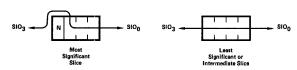

- Q<sub>3</sub> A shift line at the MSB of the Q register (Q<sub>3</sub>) and the register stack (RAM<sub>3</sub>). Electrically these lines are three-state outputs connected to TTL inputs internal to the device. When the destination code on I<sub>678</sub> indicates an up shift (octal 6 or 7) the three-state outputs are enabled and the MSB of the Q register is available on the Q<sub>3</sub> pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are OFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

- Q<sub>0</sub> Shift lines like Q<sub>3</sub> and RAM<sub>3</sub>, but at the LSB of the RAM<sub>0</sub> Q-register and RAM. These pins are tied to the Q<sub>3</sub> and RAM<sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.

- ${f D}_{0 ext{-}3}$  Direct data inputs. A four-bit data field which may be selected as one of the ALU data sources for entering data into the device.  ${f D}_0$  is the LSB.

- Y<sub>0-3</sub> The four data outputs. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code I<sub>678</sub>.

- OE Output Enable. When OE is HIGH, the Youtputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).

- G, P The carry generate and propagate outputs of the internal ALU. These signals are used with the Am2902 for carry-lookahead.

- OVR Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit.

- ${f F}={f 0}$  This is an open collector output which goes HIGH (OFF) if the data on the four ALU outputs  ${f F}_{0-3}$  are all LOW. In positive logic, it indicates the result of an ALU operation is zero.

- F<sub>3</sub> The most significant ALU output bit.

- C<sub>n</sub> The carry-in to the internal ALU.

- $\mathbf{C}_{n+4}$  The carry-out of the internal ALU.

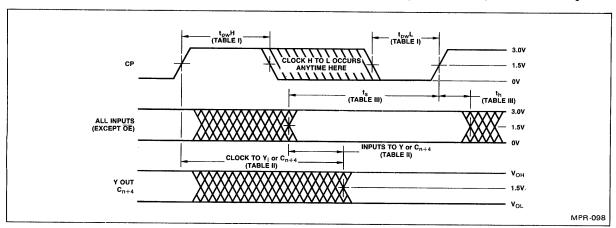

- CP The clock input. The Q register and register stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which compromises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | -65°C to +150°C                 |

|-----------------------------------------------------|---------------------------------|

| Temperature (Ambient) Under Bias                    | –55°C to +125°C                 |

| Supply Voltage to Ground Potential                  | -0.5 V to +7.0 V                |

| DC Voltage Applied to Outputs for HIGH Output State | -0.5 V to +V <sub>CC</sub> max. |

| DC Input Voltage                                    | -0.5 V to +5.5 V                |

| DC Output Current, Into Outputs                     | 30 mA                           |

| DC Input Current                                    | -30 mA to +5.0 mA               |

#### **OPERATING RANGE**

| Part Number<br>Suffix     | $\mathbf{v}_{\mathtt{CC}}$ | Temperature                                      |

|---------------------------|----------------------------|--------------------------------------------------|

| PC, PCB,<br>DC, DCP<br>XC | 4.75V to 5.25V             | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$      |

| DM, DMB<br>FM, FMB<br>XM  | 4.50V to 5.50V             | $T_{C} = -55^{\circ}C \text{ to } +125^{\circ}C$ |

#### **Notes on Testing**

Incoming test procedures on this device should be carefully planned, taking into account the high complexity and power levels of the part. The following notes may be useful.

- 1. Insure the part is adequately decoupled at the test head. Large changes in  $V_{CC}$  current as the device switches may cause erroneous function failures due to  $V_{CC}$  changes.

- 2. Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- Do not attempt to perform threshold tests at high speed.

Following an input transition, ground current may change by

as much as 400mA in 5-8ns. Inductance in the ground cable

may allow the ground pin at the device to rise by 100's of

millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0.4V$  and  $V_{IH} \geqslant 2.4V$  for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- To assist in testing, AMD offers complete documentation on our test procedures and, in most cases, can provide Fairchild Sentry programs, under license.

#### ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

(Group A, Subgroups 1, 2, and 3)

| arameters       | Description                                |                                                                   | Test Conditions (Note 1)                                     |                                                                                                        | Min.                              | Typ.<br>(Note 2) | Max. | Units      |       |  |

|-----------------|--------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------|------------|-------|--|

|                 |                                            |                                                                   |                                                              | I <sub>OH</sub> = -1.6<br>Y <sub>0</sub> , Y <sub>1</sub> , Y <sub>2</sub>                             | ,.Y3                              | 2.4              |      |            |       |  |

| İ               |                                            | V <sub>CC</sub> = MIN.                                            |                                                              | i <sub>OH</sub> = -1.0                                                                                 |                                   | 2.4              |      |            |       |  |

| <b>v</b> он     | Output HIGH Voltage                        | VIN = VIH or                                                      | VII                                                          |                                                                                                        | DμA, OVR, P                       | 2.4              |      |            | Volts |  |

| ı               |                                            | '''                                                               |                                                              | I <sub>OH</sub> = -600                                                                                 |                                   | 2.4              |      |            |       |  |

|                 |                                            |                                                                   |                                                              | I <sub>OH</sub> = -600<br>RAM <sub>0, 3,</sub> 0                                                       |                                   | 2.4              |      |            |       |  |

|                 |                                            |                                                                   |                                                              | I <sub>OH</sub> = -1.6                                                                                 |                                   | 2.4              |      |            |       |  |

| CEX             | Output Leakage Current<br>for F = 0 Output | V <sub>CC</sub> = MIN., V<br>V <sub>IN</sub> = V <sub>IH</sub> or |                                                              |                                                                                                        | -                                 |                  |      | 250        | μΑ    |  |

|                 |                                            |                                                                   | V- V- V- V-                                                  | I <sub>OL</sub> = 20m                                                                                  | A (COM'L)                         |                  |      | 0.5        |       |  |

|                 |                                            | V <sub>CC</sub> = MIN.,                                           | $Y_0, Y_1, Y_2, Y_3$                                         | IOL = 16m/                                                                                             | A (MIL)                           |                  |      | 0.5        |       |  |

| VOL             | Output LOW Voltage                         | VIN = VIH                                                         | G, F = 0                                                     | IOL = 16m                                                                                              | Δ                                 |                  |      | 0.5        | Volt  |  |

|                 |                                            | or VIL                                                            | Cn+4                                                         | I <sub>OL</sub> = 10m.                                                                                 | A                                 |                  |      | 0.5        | VOIL  |  |

|                 |                                            |                                                                   | OVR, P                                                       | I <sub>OL</sub> = 8.0m                                                                                 | A                                 |                  |      | 0.5        |       |  |

|                 |                                            |                                                                   | F <sub>3</sub> , RAM <sub>0, 3</sub> ,<br>Q <sub>0, 3</sub>  | I <sub>OL</sub> = 6.0m                                                                                 | Α .                               |                  |      | 0.5        |       |  |

| V <sub>IH</sub> | Input HIGH Level                           |                                                                   | out logical HIGH<br>nputs (Note 7)                           | ***                                                                                                    |                                   | 2.0              |      |            | Volt  |  |

| VIL             | Input LOW Level                            |                                                                   | Guaranteed input logical LOW voltage for all inputs (Note 7) |                                                                                                        |                                   |                  |      | 0.8        | Volt  |  |

| VI              | Input Clamp Voltage                        | V <sub>CC</sub> = MIN., I                                         | N = -18mA                                                    | _                                                                                                      |                                   |                  |      | -1.5       | Volt  |  |

|                 |                                            |                                                                   |                                                              | Clock, OE                                                                                              |                                   |                  |      | -0,36      |       |  |

|                 |                                            | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.5V                    |                                                              | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub>                                                       |                                   |                  |      | 0,36       | 1     |  |

|                 |                                            |                                                                   |                                                              | B <sub>0</sub> , B <sub>1</sub> , B <sub>2</sub> ,                                                     |                                   |                  |      | -0.36      | mA    |  |

| I <sub>IL</sub> | Input LOW Current                          |                                                                   |                                                              | D <sub>0</sub> , D <sub>1</sub> , D <sub>2</sub>                                                       |                                   |                  |      | -0.72      |       |  |

|                 |                                            |                                                                   |                                                              | 10, 11, 12, 1                                                                                          |                                   |                  |      | -0.36      |       |  |

|                 |                                            |                                                                   |                                                              | 13, 14, 15, 1                                                                                          |                                   |                  |      | -0.72      |       |  |

|                 |                                            |                                                                   |                                                              |                                                                                                        | 2 <sub>0, 3</sub> (Note 4)        |                  |      | -0.8       | 4     |  |

|                 |                                            |                                                                   |                                                              | C <sub>n</sub>                                                                                         |                                   |                  |      | -3.6<br>20 |       |  |

| i               |                                            | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7V                    |                                                              | Clock, OE                                                                                              |                                   |                  |      | 20         | -     |  |

|                 |                                            |                                                                   |                                                              | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub>                                                       |                                   |                  |      | 20         | -     |  |

|                 |                                            |                                                                   |                                                              | B <sub>0</sub> , B <sub>1</sub> , B <sub>2</sub> ,<br>D <sub>0</sub> , D <sub>1</sub> , D <sub>2</sub> |                                   |                  |      | 40         |       |  |

| ΙН              | Input HIGH Current                         |                                                                   |                                                              | 10, 11, 12, 1                                                                                          |                                   |                  |      | 20         | μΑ    |  |

|                 |                                            |                                                                   |                                                              | 13, 14, 15, 1                                                                                          |                                   |                  |      | 40         | 1     |  |

|                 |                                            |                                                                   |                                                              |                                                                                                        | 2 <sub>0, 3</sub> (Note 4)        |                  |      | 100        |       |  |

|                 |                                            |                                                                   |                                                              | C <sub>n</sub>                                                                                         | .0, 3                             |                  | +    | 200        |       |  |

| I <sub>1</sub>  | Input HIGH Current                         | V <sub>CC</sub> = MAX.,                                           | VIN = 5.5V                                                   | 1 ~11                                                                                                  |                                   |                  |      | 1.0        | mA    |  |

| •               |                                            | 33 **********************************                             |                                                              | Y <sub>0</sub> , Y <sub>1</sub> ,                                                                      | V <sub>O</sub> = 2.4V             |                  |      | 50         |       |  |

|                 |                                            |                                                                   |                                                              | Y <sub>2</sub> , Y <sub>3</sub>                                                                        | V <sub>O</sub> = 0.5V             |                  | -    | -50        |       |  |

| lozн            | Off State (High Impedance)                 | V <sub>CC</sub> = MAX.                                            |                                                              |                                                                                                        | V <sub>O</sub> = 2.4V             |                  |      | 100        | μΑ    |  |

| OZL             | Output Current                             |                                                                   |                                                              | RAM <sub>0</sub> , 3                                                                                   | (Note 4)                          |                  |      |            |       |  |

|                 |                                            |                                                                   |                                                              | Q <sub>0,3</sub>                                                                                       | V <sub>O</sub> = 0.5V<br>(Note 4) |                  |      | -800       |       |  |

|                 |                                            |                                                                   |                                                              | Y <sub>0</sub> , Y <sub>1</sub> , Y <sub>2</sub>                                                       | , Y <sub>3</sub> , G              | -30              |      | -85        |       |  |