# SIGNETICS BIPOLAR/MOS MICROPROCESSOR

# DATA MANUAL

SIGNETICS reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

he present rapid growth of the electronic design revolution is being fueled by the microprocessor/microcomputer. As one of the industry leaders, Signetics gives new impetus to advancing the state-of-the-art with its technological strength, product depth and manufacturing know-how. We continue to develop all aspects of the microprocessor/microcomputer area, simultaneously providing products, ready-to-use training, software and development tools that help you to understand and apply Signetics advanced products.

This Microprocessor Data Manual will enable you to examine Signetics complete line of Bipolar and MOS Microprocessors, as well as a full line of support products. Each data sheet fully explains the operation of each product and contains application hints on how to best utilize the products' design advantages.

You will also find a variety of development systems, educational products, prototyping kits and software for both bipolar and MOS. And with a team of field application engineers throughout the country you will find that Signetics can provide you with the answer to your design problems.

We offer one of the broadest selections available of both bipolar and MOS microprocessor/microcomputers. Combined with our complete line of logic, analog, bipolar and MOS memories, a design engineer can select one source that will provide him with the best possible, cost effective solution to his design problems.

This book contains a compilation of all products currently available. Signetics is continuously developing new products. As you see new product announcements, you should contact your local Signetics sales office, representative or authorized distributor or write Signetics directly at 811 East Arques Avenue, Sunnyvale, California, 94086, for the latest technical information.

# TABLE OF CONTENTS

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Chapter 1 BIPOLAR MICROPROCESSORS, PERIPHERALS AND DEVELOPMENT PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                 |

| Microprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

| Bit Slice Family Introduction  8X02 Control Store Sequencer  2901-1 Microprocessor Control Processing Element  Series 3000 Introduction  A Guide to the Selection of Support Components for Signetics Bit Slice Microprocessors  S/N3001 Microprogram Control Unit  S/N3002 Central Processing Element                                                                                                                                                 | 9<br>10<br>16<br>25<br>28<br>32<br>40                             |

| introduction to the Bipolar Fixed Instruction Microprocessor                                                                                                                                                                                                                                                                                                                                                                                           | 49                                                                |

| 8X300 Microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                |

| Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |

| Introduction to System Logic 74S182/183 Look Ahead Carry 54/74LS273 Octal D Flip Flop 54/74LS377 Octal D Flip Flop 82S100/101 Field Programmable Logic Array 82S200/201 Programmable Logic Array 82S102/103 Field Programmable Gate Array 8T31 8-Bit Bidirectional I/O Port 8T32/33/35/36 8-Bit Latched Addressable Bidirectional I/O Port 8T39 Bus Expander 8T58 Transparent Bus Expander 8X01 CRC Generator/Checker 8X08 AM/FM Frequency Synthesizer | 65<br>66<br>69<br>70<br>80<br>86<br>94<br>98<br>105<br>109<br>112 |

| Development Products  3000KT/1000 Designer's Development Kit 3000KT/8080SK 8080 Emulator Kit 8X02AS1000SS Microassembler (software) 8X300KT100SK Designer's Kit 8T32/33/35/36 Programmer Kit 8X300AS100SS MCCAP 8X300 Cross Assembler (software) 8X300AS100SS MCCAP 8X300 Cross Assembler (software)                                                                                                                                                   | 122<br>124<br>125<br>127<br>128                                   |

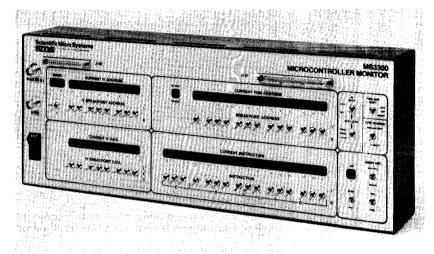

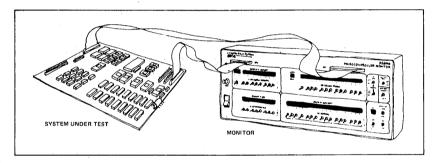

| MS3300 Microcontroller Monitor                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                   |

| Chapter 2 MOS MICROPROCESSORS, PERIPHERALS AND DEVELOPMENT PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                    | 133                                                               |

| Microprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

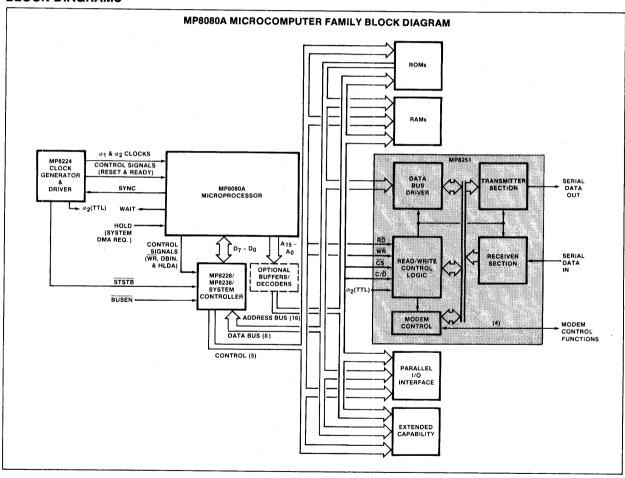

| 2650/2650A-1 Microprocessor ISP-8A/600 Simple Cost Effective Microprocessor (SC/MP-11) MP8080A 8-Bit N-Channel Microprocessor                                                                                                                                                                                                                                                                                                                          | 146                                                               |

| Peripherals Periph |                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

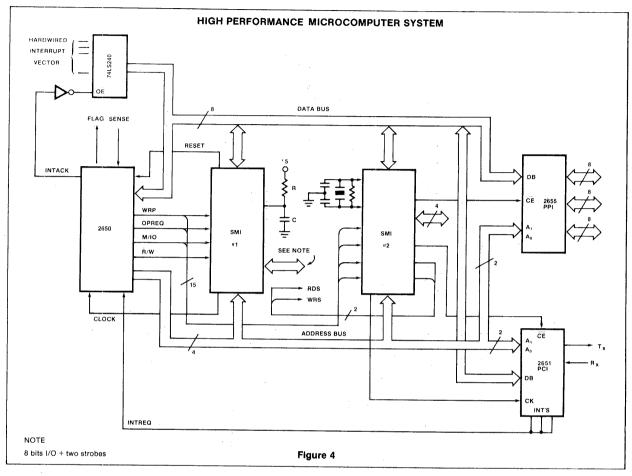

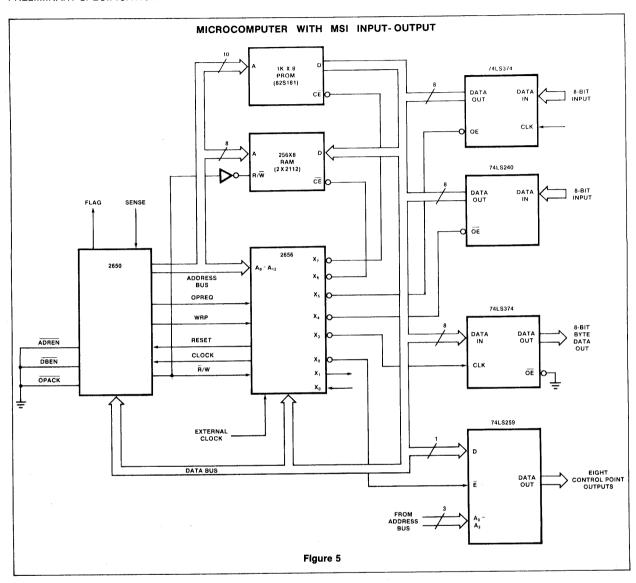

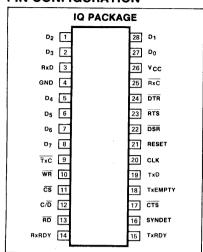

| 2651 Programmable Communication Interface (PCI) 2652 Multi-Protocol Communications Controller (MPCC) 2655 Programmable Peripheral Interface (PPI) 2656 System Memory Interface (SMI) MP8251 Programmable Communication Interface (PCI) MP8255 Programmable Peripheral Interface (PPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 188<br>206<br>208<br>219                                           |

| Development Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

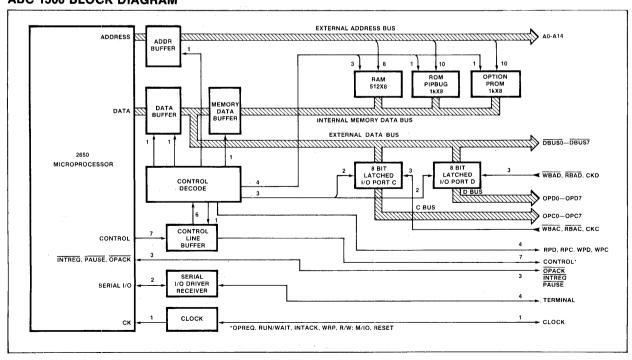

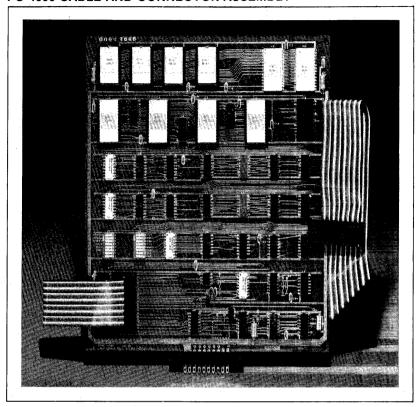

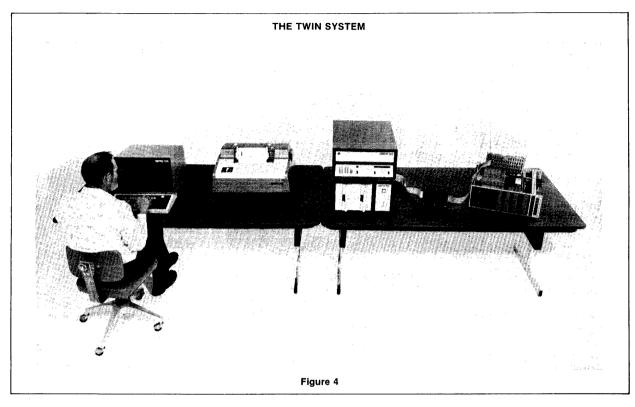

| 2650KT9000 Microprocessor Prototyping Kit 2650PC1500/2650KT9500 Adaptable Board Computer (ABC) PC-4000 2656 System Memory Interface (SMI) Emulator 2650PC1001 Microprocessor Prototyping Card 2650PC2000 4KMemory Card 2650DS2000 Microprocessor Demonstration System 2650PC3000 Intelligent Typewriter Controller 2650AS1000/1100 Assembler Version 3.2 (software) 2650SM1000/1100 Simulator Version 1.2 (software) Signetics' Higher Level Language: PLμS 2650AR1000 Relocatable Assembler Version 5.0 The TWIN (Testware Instrument) System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 241<br>245<br>257<br>259<br>260<br>263<br>266<br>267<br>268<br>268 |

| Chapter 3 STANDARD SUPPORT CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 277                                                                |

| Introduction Bipolar Memory Selection Guide  MOS Memory Selection Guide  7400 Series  8200 Series  8T00 Series Interface  Analog (Linear)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 280<br>282<br>283<br>286<br>287                                    |

| MILITARY PACKAGES SALES OFFICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                 |

# CHAPTER I BIPOLAR Microprocessors Peripherals and Development Products

#### Microcontrol and Arithmetic Units

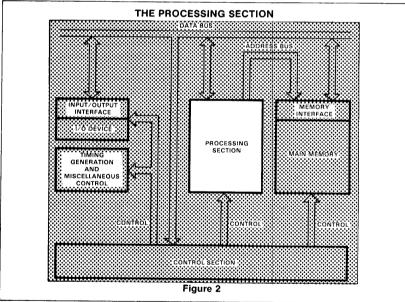

The introduction of the Signetics Bit-Slice Microprocessors has brought new levels of high performance to microprocessor applications not previously possible with MOS technology. Combining the Schottky bipolar microprocessors with industry standard memory and support circuits, microinstruction cycle times of 100ns are possible.

In the majority of cases, the choice of a bipolar microprocessor slice, as opposed to an MOS device, is based on speed or flexibility of microprogramming. Starting with these characteristics, the design of the Signetics slice microprocessors has been optimized around the following objectives:

- · Fast cycle time

- All memory and support chips are industry standard

- · Cooler operation

- Lower total system cost

Furthermore, systems built with large-scale integrated circuits are much smaller and require less power than equivalent systems using medium and/or small scale integrated circuits.

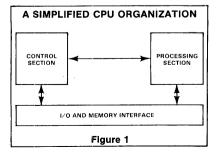

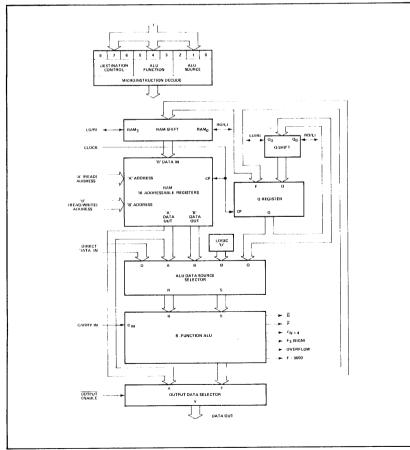

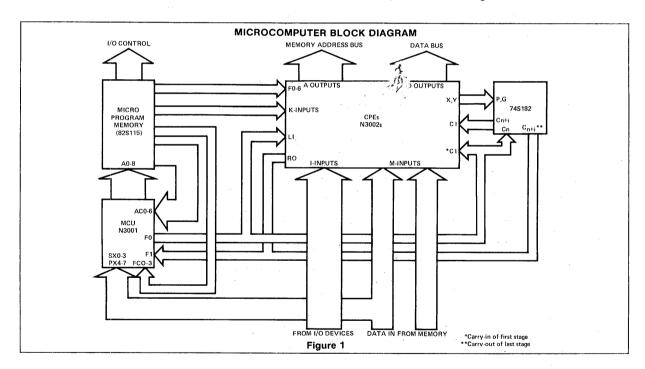

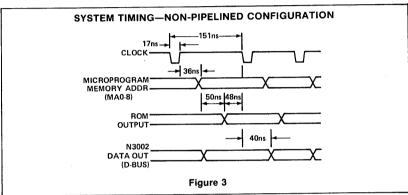

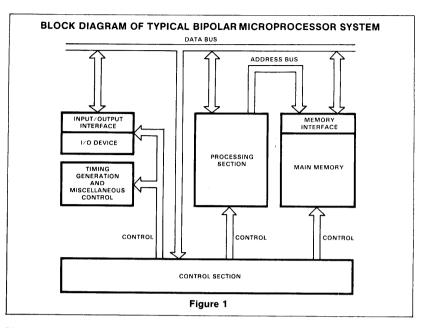

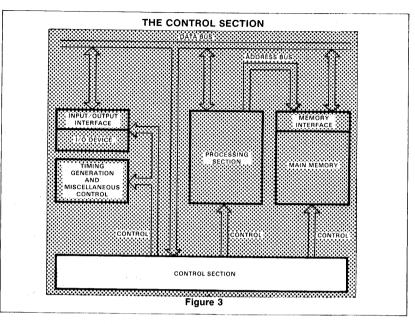

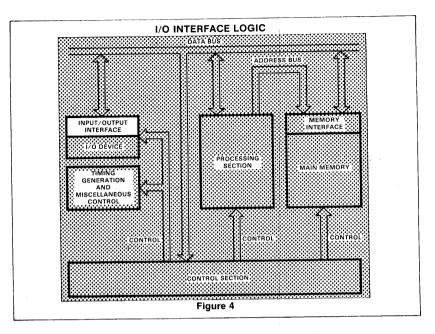

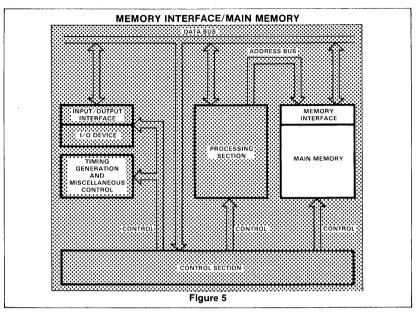

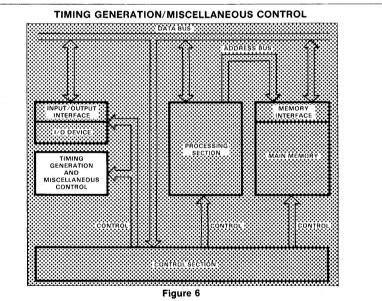

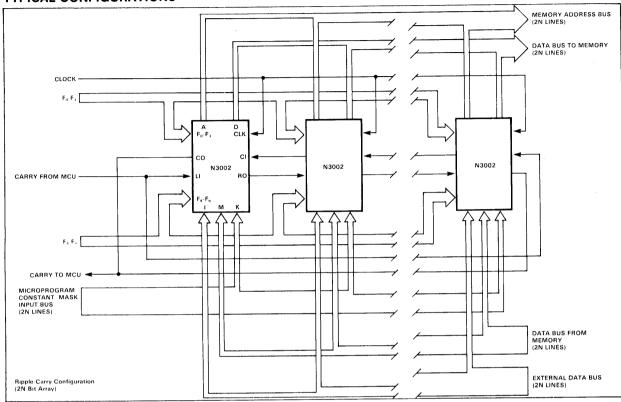

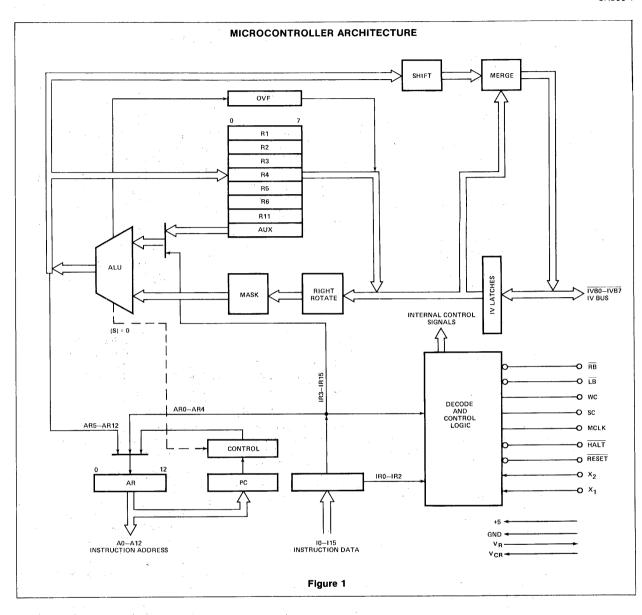

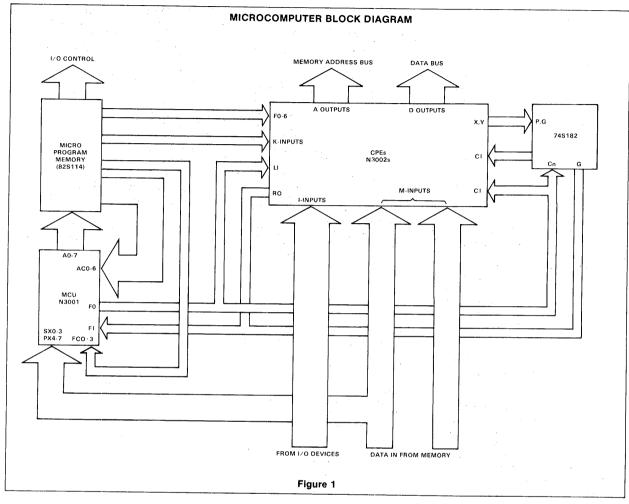

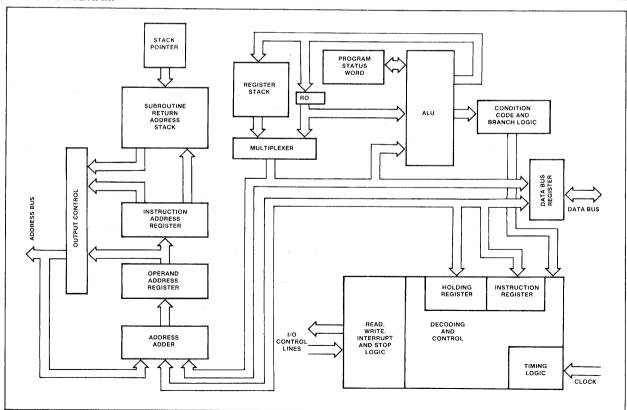

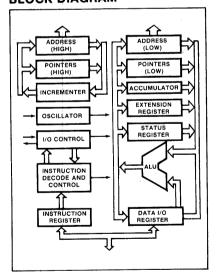

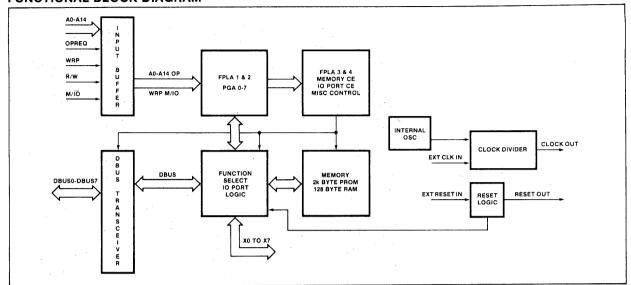

Typically, slice microprocessors are employed in the realization of the Central Processing Unit (CPU) of a computer or for implementing dedicated smart controllers. The generalized and simplified structure of a CPU or "Smart" controller can be typically classified into 3 distinct but interactively related functional sections. These sections are generally referred to as the Processing section, the Control section, and the I/O and Memory Interface section. A simplified block diagram of a CPU is illustrated in Figure 1.

The major functions of the Processing section are to:

- provide data transfer paths:

- manipulate data through logic and arithmetic operations;

- provide storage facilities such as a register file; and

- generate necessary status flags based on the kind of operation performed by the ALU.

The major functions of the Control section are to:

- initiate memory or I/O operations:

- decode macroinstructions;

- control the manipulation and transfer of data:

- · test status conditions; and

- · sample and respond to interrupts.

The major functions of the I/O and Memory Interface section are to:

- multiplex data to the proper destination:

- · provide bus driving/receiving capability; and

- · provide latching capability.

With state-of-the-art bipolar Schottky technology, high-performance microprocessors are designed to perform functions of the Processing section. Due to the limitation on the number of pins and chip size, the overall Processing section is partitioned into several functionally equivalent slices. In today's bipolar microprocessor market, 2-bit and 4bit slice architecture predominates. Each architecture type has its uniqueness but, in general, a slice contains a group of general purpose registers, an accumulator, specialpurpose register(s) ALU and related status flags. All of these elements constitute the Processing section of a CPU. The flexibility of slice components allows the designer to construct a processing section of any desired width as required by his application.

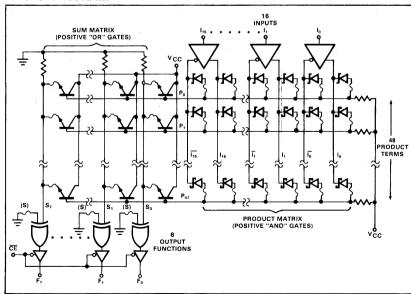

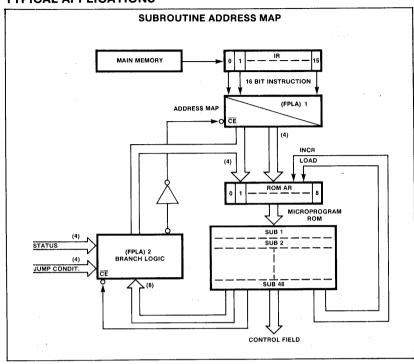

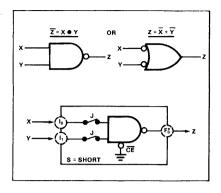

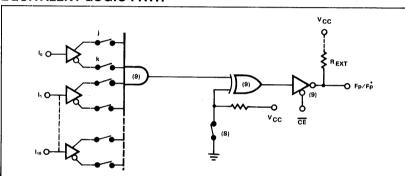

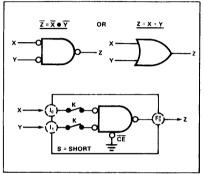

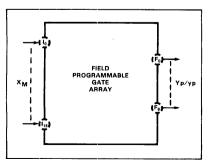

The Control section of the CPU is more complex in design. Typically this section includes the macroinstruction decode logic, test-branch decode, microprogram sequencing logic, and the control store where the microprogram resides. Aside from the microprogram, the remaining portion of the Control section (macroinstruction decode and test-branch decode and sequencing logic), does not lend itself to efficient partitioning into vertical slices. This is due to the random nature of the logic usually found in the Control section. However, horizontal functional grouping is possible. For example, the macroinstruction decode and testbranch decode logic can now be replaced by the FPLA (Field Programmable Logic Array); the random logic traditionally

needed to implement the microprogram sequencing can now be replaced by the Microprogram Control Unit; and, of course, the microprogram can be stored in high density PROMs or ROMs. Since the designer must define his own microstructure, the slice microprocessors permit fundamental optimizations to be made. With slice hardware, the designer may have no macroinstructions at all, placing all of the program in PROM for dedicated control applications. Or he may define, as required, any number of macroinstructions selected specifically for his particular processor purpose. Various minicomputers and several MOS microprocessors have been emulated using slice hardware.

The I/O and Memory Interface section consists mainly of I/O ports, high power bus drivers, receivers, and some temporary register storage facilities. Bidirectional and tri-state devices are the most popular logic elements for implementing this interface structure.

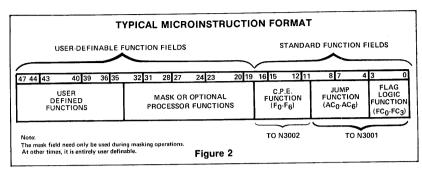

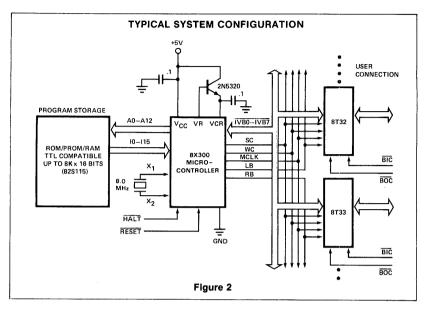

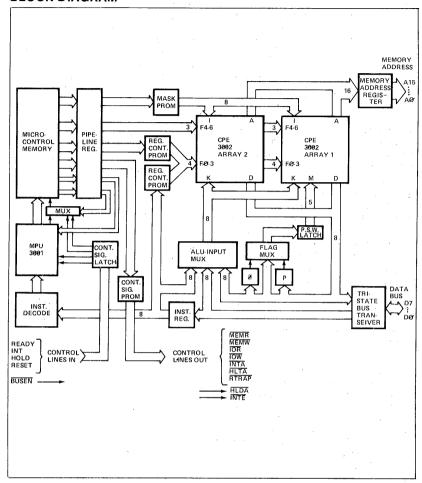

Figure 2 shows an LSI approach to the implementation of the same generalized CPU structure indicated earlier.

Data specifications for Signetics' line of slice microprocessor components are contained within this chapter. Included is the popular 3000 series Microprogram Control Unit and the 2-bit slice Central Processing Element. These Signetics devices feature improved performance specifications over 3000 series components available on the general market. Moreover, the unique Signetics XL plastic package design results in significantly cooler operation of the chip than was previously possible with other plastic package designs. This section also features the 8X02 Control Store Sequencer. This device may be used with any TTL compatible slice processing elements and features extreme ease of use. The 8 simple, yet powerful, instructions permit subroutining and looping (using internal stack), unrestricted jumping, unrestricted conditional branching and conditional instruction skipping

#### **CONTROL STORE SEQUENCER**

PRELIMINARY SPECIFICATION

8X02-I.XL

#### DESCRIPTION

The Signetics 8X02 is a low power Schottky LSI device intended for use in high performance microprogrammed systems to control the fetch sequence of microinstructions. When combined with standard ROM or PROM, the 8X02 forms a powerful microprogrammed control section for computers, controllers, or sequential logic.

#### **FEATURES**

- Low power Schottky process

- 1024 microinstruction addressability

- N-way branch

- · 4-level stack register file (LIFO type)

- · Automatic push/pop stack operation

- "Test and skip" operation on test input line

- 3-bit command code

- · Tri-state buffered outputs

- Auto-reset to address 0 during power-up

- Conditional branching, pop stack, and push stack

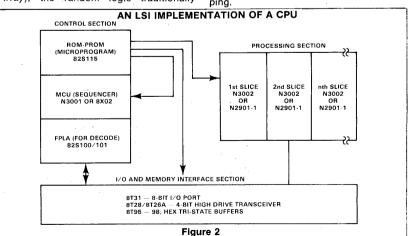

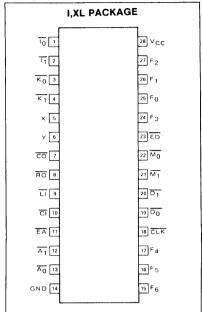

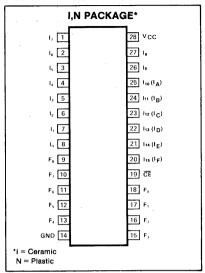

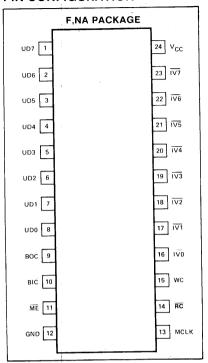

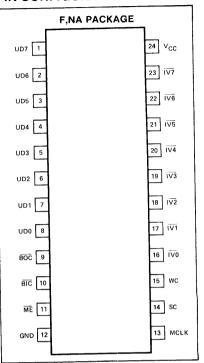

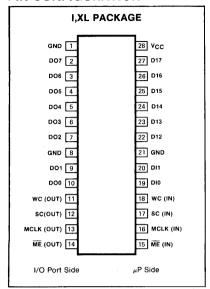

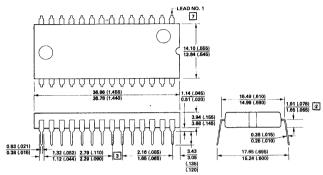

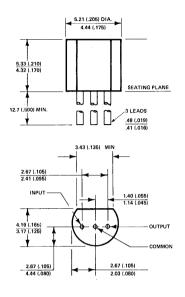

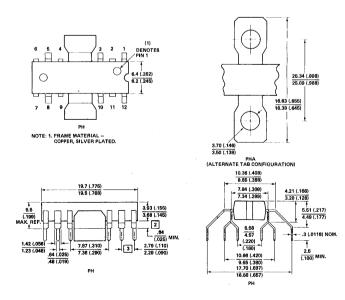

#### PIN CONFIGURATION

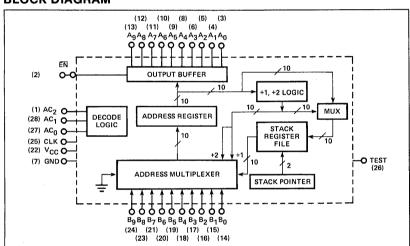

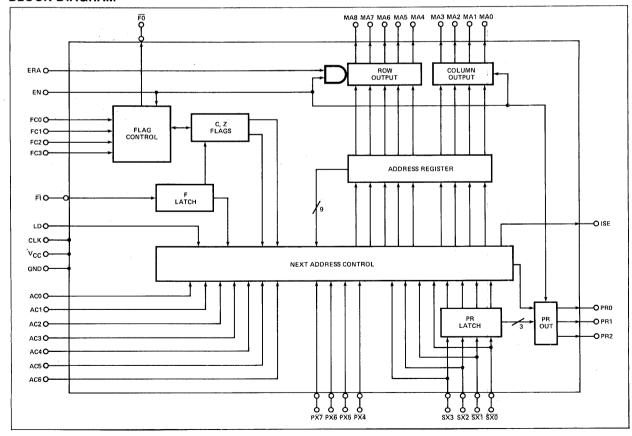

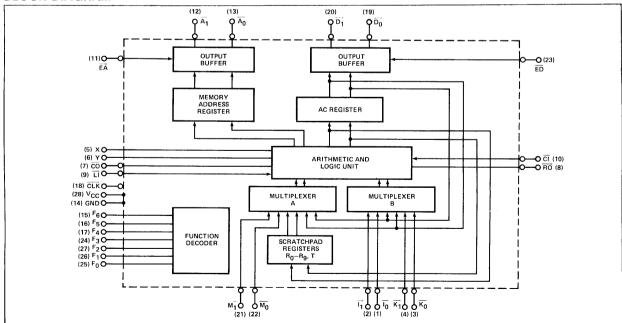

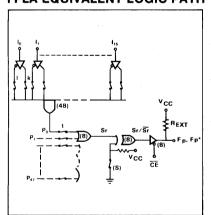

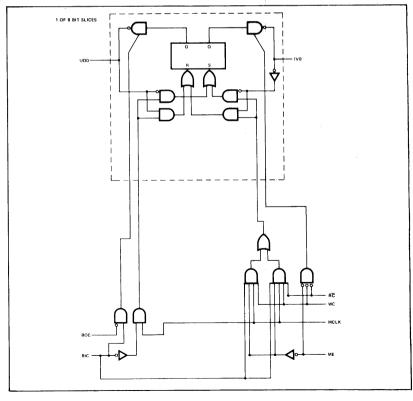

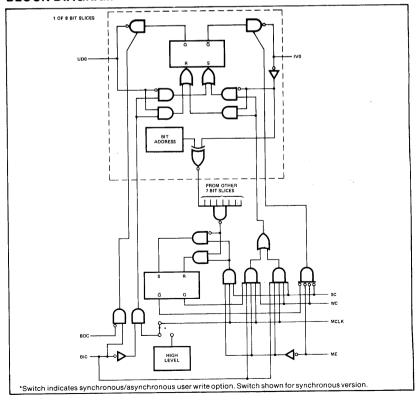

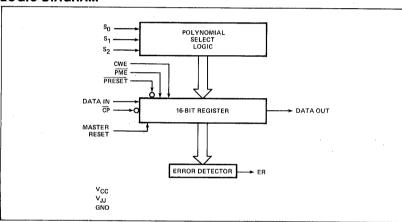

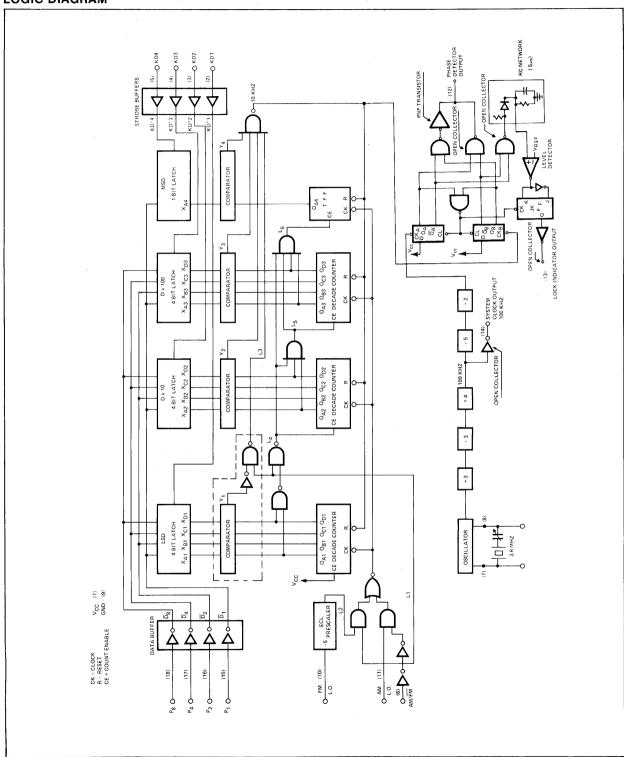

#### **BLOCK DIAGRAM**

#### **PIN DESIGNATION**

| PIN            | SYMBOL                           | NAME AND FUNCTION                                                                                                                                   | TYPE                       |

|----------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5-6<br>8-13    | A <sub>0</sub> -A <sub>9</sub>   | Microprogram Address outputs                                                                                                                        | Three-state<br>Active high |

| 1,28,27        | AC <sub>0</sub> -AC <sub>2</sub> | Next Address Control Function inputs All addressing control functions are selected by these command lines.                                          | Active high                |

| 14-21<br>23-24 | B <sub>0</sub> -B <sub>9</sub>   | Branch Address inputs Determines the next address of an N-way branch when used with the BRANCH TO SUBROUTINE (BSR) or BRANCH ON TEST (BRT) command. | Active high                |

| 2              | ĒN                               | Enable input When in the low state, the Microprogram Address outputs are enabled.                                                                   | Active low                 |

| 25             | CLK                              | Clock Input—High to Low transition for stack operations, Low to High transition for address modification.                                           |                            |

| 26             | TEST                             | Test input Used in conjunction with four NEXT ADDRESS CONTROL FUNCTION commands to effect conditional skips, branches, and stack operations.        | Active high                |

| 7              | GND                              | Ground                                                                                                                                              |                            |

| 22             | v <sub>CC</sub>                  | +5 Volt supply                                                                                                                                      |                            |

PRELIMINARY SPECIFICATION

8X02-I.XL

#### **FUNCTIONAL DESCRIPTION**

The Signetics 8X02 Control Store Sequencer is an LSI device using low power Schottky technology and is intended for use in high performance microprogrammed applications. When used alone, the 8X02 is capable of addressing up to 1K words of microprogram. This may be expanded to any microprogram size by conventional paging techniques.

The Address Register consists of 10 D-type, edge-triggered flip-flops with a common clock. A new address is entered into the Address Register on the low-to-high transition of the clock. The next address to be entered into the Address Register is supplied via the Address Multiplexer.

The Address Multiplexer is a 5-input device that is used to select either the branch input, +1 adder, +2 adder, stack register file, or ground (all zeros) as the source of the next microinstruction address. The proper multiplexer channel is automatically selected via the Decode Logic according to the Address Control Function Input and Test Input line.

The +1, +2 logic is used to increment the present contents of the Address Register by 1 or 2, depending on the function input command. Thus, the next address to the Control Store ROM/PROM may be either the current address plus 1 (N+1) or the current address plus 2 (N+2). If the same Microprogram Address is to be used on successive occasions, the clock to the 8X02 must simply be disabled; therefore, no new address is loaded into the Address Register.

The Stack File Register is used to provide a return address linkage whenever a subroutine or loop is executed. The 4X10 stack operates in a last-in, first-out (LIFO) mode, with the stack pointer always pointing to the next address to be read. Operation of the stack pointer is automatically controlled by the Address Control Function Inputs. Since the stack is 4 words deep, up to 4 loops and/or subroutines may be nested.

The branch input is a 10-bit field of direct inputs to the multiplexer which can be selected as the next control store address. Using the appropriate branch command, an N-way branch is possible where N is the

address of any microinstruction within the 1024 word microcode page. Likewise, the RESET command is a special case of an N-way branch in which the multiplexer selects an all zeros input, forcing the next microinstruction address to be zero.

The Test Input line is used in conjunction with the conditional execution of 4 Address Control Function commands. When the Test Input is false (low), the sequencer simply increments to the next address (N+1). When it is true (high), the sequencer executes a branch as defined by the input command, thereby transferring control to another portion of the microprogram.

All Address Output lines of the 8X02 are three-state buffered outputs with a common enable line  $(\overline{\text{EN}}).$  When the Enable line is high, all outputs are placed in a high-impedance state, and external access to the control store ROM/PROM is possible. This allows a preprogrammed set of microinstructions to be executed from external or built-in test equipment (BITE), vectored interrupts, and Writable Control Store if implemented.

#### **NEXT ADDRESS CONTROL FUNCTION TABLE**

| MNEMONIC | DESCRIPTION                                     | FUNC<br>AC <sub>2</sub> |   |     | TEST          | NEXT ADDRESS                  | STACK                   | STACK POINTER |

|----------|-------------------------------------------------|-------------------------|---|-----|---------------|-------------------------------|-------------------------|---------------|

| TSK      | Test and skip                                   | 0                       | 0 | 0   | False<br>True | Current + 1<br>Current + 2    | N.C.<br>N.C.            | N.C.<br>N.C.  |

| INC      | Increment                                       | 0                       | 0 | 1   | x             | Current + 1                   | N.C.                    | N.C.          |

| BLT      | Branch to loop if test input true               | 0                       | 1 | 0   | False<br>True | Current + 1<br>Stack reg file | X<br>POP (read)         | Decr<br>Decr  |

| POP      | POP stack                                       | 0                       | 1 | 1   | x             | Stack reg file                | POP (read)              | Decr          |

| BSR      | Branch to sub-<br>routine if test<br>input true | 1                       | 0 | 0 . | False<br>True | Current + 1<br>Branch address | N.C.<br>PUSH (Curr + 1) | N.C.<br>Incr  |

| PLP      | Push for looping                                | 1                       | 0 | 1   | x             | Current + 1                   | PUSH (Curr Addr)        | Incr          |

| BRT      | Branch if test input true                       | 1                       | 1 | 0   | False<br>True | Current + 1<br>Branch address | N.C.<br>N.C.            | N.C.<br>N.C.  |

| RST      | Set microprogram<br>address output to<br>zero   | 1                       | 1 | 1   | ×             | All O's                       | N.C.                    | N.C.          |

X = Don't care N.C. = No change PRELIMINARY SPECIFICATION

8X02-I,XL

#### **FUNCTIONAL DESCRIPTION**

The following is a description of each of the eight Next Address Control Functions (AC<sub>2</sub>-AC<sub>0</sub>)

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тѕк      | AC <sub>2-0</sub> = 000: TEST AND SKIP Perform test on Test Input Line. If test is Next Address = Current Address + 1 False (Low): Stack Pointer unchanged If test is Next Address = Current Address + 2 True (High) (i.e. Skip next microinstruction) Stack Pointer unchanged                                                                                         |

| INC      | AC <sub>2-0</sub> = 001: INCREMENT<br>Next Address = Current Address + 1<br>Stack Pointer unchanged                                                                                                                                                                                                                                                                    |

| BLT      | AC <sub>2-0</sub> = -010: BRANCH TO LOOP  IF TEST CONDITION TRUE.  Perform test on Test Input Line.  If test is Next Address = Current Address + 1  False (Low): Stack Pointer decremented by 1  If test is Next Address = Address from Stack  True (High): Register File (POP)  Stack Pointer decremented by 1                                                        |

| POP      | AC <sub>2-0</sub> = 011: POP STACK  Next Address = Address from Stack Register File (POP)  Stack Pointer decremented by 1                                                                                                                                                                                                                                              |

| BSR      | AC <sub>2-0</sub> = 100: BRANCH TO SUBROUTINE  IF TEST CONDITION TRUE.  Perform test on Test Input Line.  If test is Next Address = Current Address + 1  False (Low): Stack Pointer unchanged  If test is Next Address = Branch Address Input (B <sub>0-9</sub> )  True (High): Stack Pointer incremented by 1  PUSH (write) Current Address + 1 → Stack Register File |

| PLP      | AC <sub>2-0</sub> = 101: PUSH FOR LOOPING<br>Next Address = Current Address + 1<br>Stack Pointer incremented by 1<br>PUSH (write) Current Address → Stack Register File                                                                                                                                                                                                |

| BRT      | AC <sub>2-0</sub> = 110: BRANCH ON TEST CONDITION TRUE Perform test on Test Input Line. If test is Next Address = Current Address + 1 False (Low): Stack Pointer unchanged If test is Next Address = Branch Address Input (B <sub>0-9</sub> ) True (High): Stack Pointer unchanged                                                                                     |

| RST      | AC <sub>2-0</sub> = 111: RESET TO ZERO  Next Address = 0  Stack Pointer unchanged                                                                                                                                                                                                                                                                                      |

#### **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER                   | RATING        | UNIT |

|------|-----------------------------|---------------|------|

| VCC  | Power supply voltage        | +7            | Vdc  |

| VIN  | Input voltage               | +5.5          | Vdc  |

| VO   | Off-State output voltage    | +5.5          | Vdc  |

| TA   | Operating temperature range | 0° to +70°    | °C   |

| TSTG | Storage temperature range   | -65° to +150° | °C   |

PRELIMINARY SPECIFICATION

8X02-I,XL

#### **DC ELECTRICAL CHARACTERISTICS** TA = 0°C to +70°C, $4.75 \le V \hat{CC} \le 5.25V$

|                  | PARAMETER                                                                              | TEST CONDITIONS                                   |     | LIMITS           |                         |                |  |

|------------------|----------------------------------------------------------------------------------------|---------------------------------------------------|-----|------------------|-------------------------|----------------|--|

|                  | T ANAMETER                                                                             | TEST CONDITIONS                                   | Min | Typ <sup>1</sup> | Max                     | UNIT           |  |

| VIH              | High level input voltage                                                               |                                                   | 2   |                  |                         | V              |  |

| VIL              | Low level input voltage                                                                |                                                   |     |                  | 0.8                     | V              |  |

| V,               | Input clamp voltage                                                                    | V <sub>CC</sub> = 4.75V, I <sub>I</sub> = -18mA   |     |                  | -1.5                    | V              |  |

| Voн              | High level output voltage                                                              | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -2.6mA | 2.4 |                  |                         | V              |  |

| VOL              | Low level output voltage                                                               | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 8mA    |     |                  | 0.5                     | l v            |  |

| 11               | Input current at maximum<br>Input voltage                                              | V <sub>CC</sub> = 5.25V, V <sub>I</sub> = 5.5V    |     |                  | 100                     | μΑ             |  |

| 'ІН              | High level input current $AC_2$ - $AC_0$ , $\overline{EN}$ , TEST $B_9$ - $B_0$ $CLK$  | V <sub>CC</sub> = 5.25V, V <sub>I</sub> = 2.7V    |     |                  | 40<br>20<br>60          | μΑ<br>μΑ<br>μΑ |  |

| اال              | Low level input current $AC_2$ - $AC_0$ , $\overline{EN}$ , $TEST$ $B_9$ - $B_0$ $CLK$ | V <sub>CC</sub> = 5.25V, V <sub>I</sub> = 0.4V    |     |                  | -0.72<br>-0.36<br>-1.08 | mA<br>mA<br>mA |  |

| los              | Short-circuit output current                                                           | V <sub>CC</sub> = 5.25V                           | -15 | }                | -100                    | mA             |  |

| <sup>1</sup> ozh | High-Z state output current                                                            | V <sub>OUT</sub> = 2.7V                           |     |                  | 20                      | μΑ             |  |

| l OZL            | High-Z state output current                                                            | V <sub>OUT</sub> = 0.4V                           |     |                  | -20                     | μΑ             |  |

| Icc              | Supply current                                                                         | V <sub>CC</sub> = 5.25V                           |     | 165              | 200                     | mA             |  |

NOTE

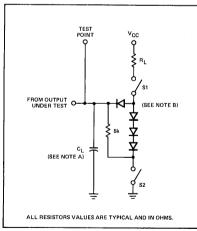

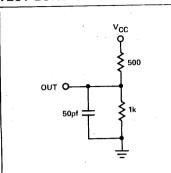

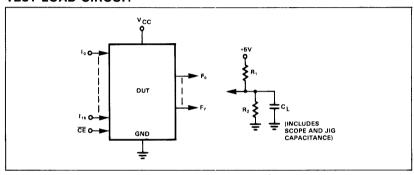

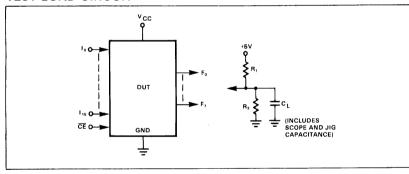

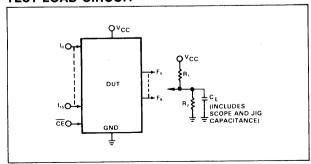

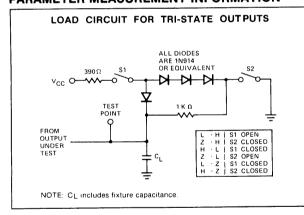

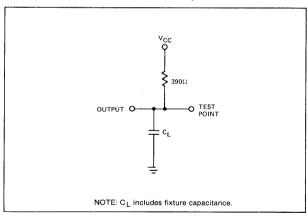

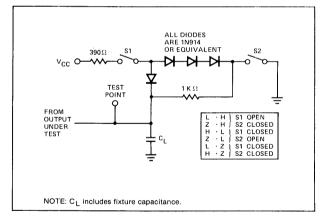

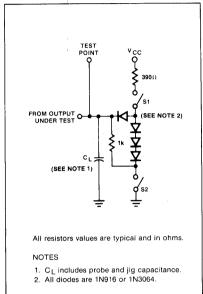

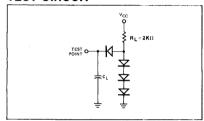

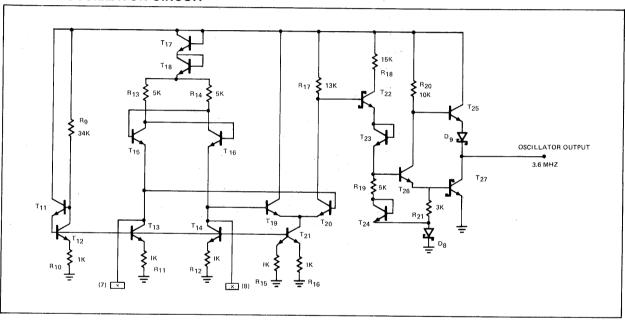

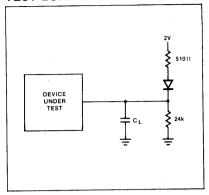

#### **TEST LOAD CIRCUIT**

#### NOTES

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. All diodes are 1N916 or 1N3064.

- C. R<sub>L</sub> = 2k, C = 15pF.

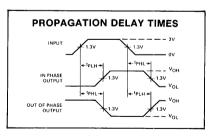

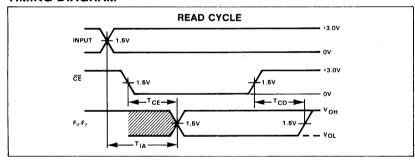

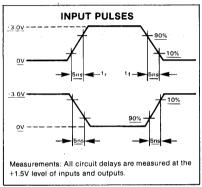

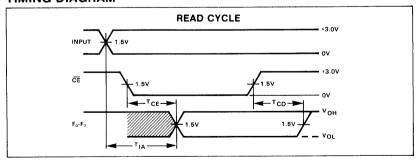

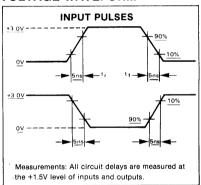

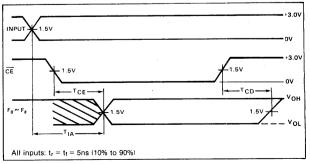

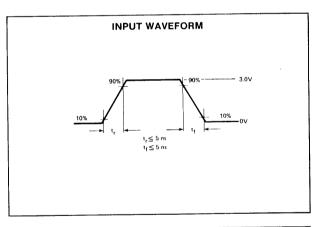

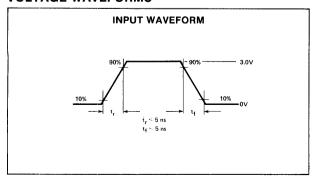

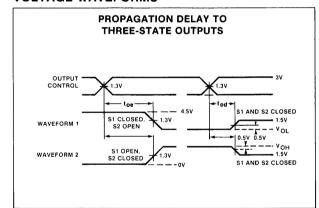

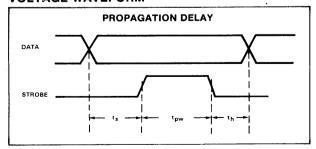

#### **VOLTAGE WAVEFORMS**

<sup>1.</sup> All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

## CONTROL STORE SEQUENCER

PRELIMINARY SPECIFICATION

8X02-I,XL

#### AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ} -70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%$

|                                                                                    | 0404447750                                                                                                                                                                                        | Τ0                             | TO FROM |                                  | LIMITS                           | ;                                | UNIT   |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------|----------------------------------|----------------------------------|----------------------------------|--------|

|                                                                                    | PARAMETER                                                                                                                                                                                         | то                             | FROM    | Min                              | Typ¹                             | Max                              | OI4III |

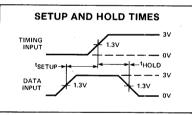

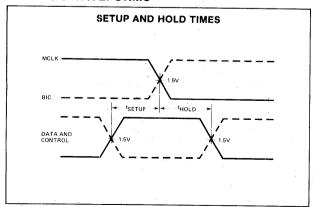

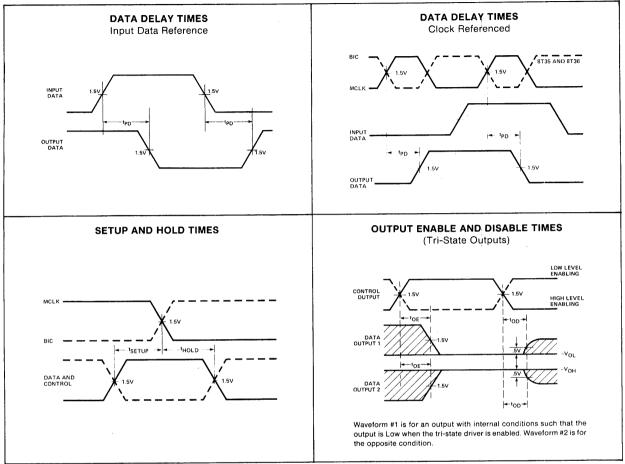

| <sup>t</sup> HI <sup>(1)</sup><br>(0)                                              | Test                                                                                                                                                                                              |                                |         | 0<br>0                           | -10<br>-24                       |                                  | ns     |

| t <sub>SF</sub> <sup>1</sup> (1)<br>(0)<br>t <sub>Sl</sub> <sup>1</sup> (1)<br>(0) | Control and data input setup<br>times with respect to CLK (1)<br>for stack related functions<br>(BLT, POP, BSR, PLP) (2)<br>AC <sub>0</sub> -AC <sub>2</sub>                                      |                                |         | 35<br>35<br>28<br>28             | 23<br>22<br>23<br>22             |                                  | ns     |

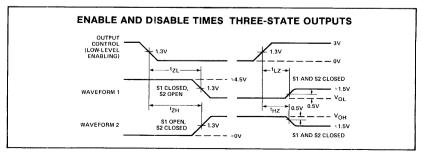

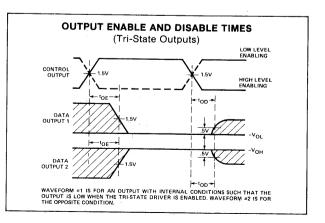

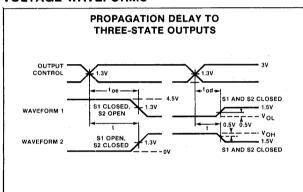

| tPLZ tPHZ tPZL tPZH tPZH tPHL tPHL                                                 | Propagation delay Low to high Z High to high Z High to low High Z to high Propagation delay High to low Low to high                                                                               | A <sub>0</sub> -A <sub>9</sub> | EN      |                                  | 12<br>16<br>14<br>15<br>33<br>33 | 35<br>35<br>25<br>35<br>40<br>40 | ns     |

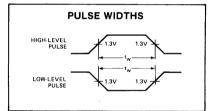

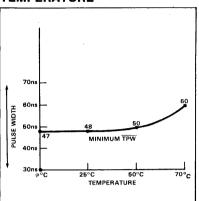

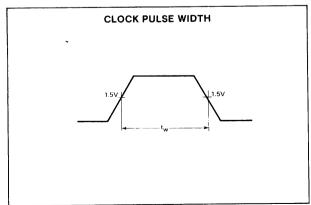

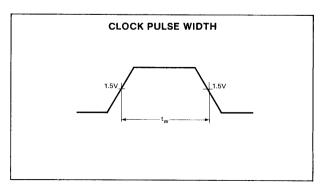

| t <sub>PW</sub>                                                                    | Clock pulse width<br>High<br>Low                                                                                                                                                                  |                                |         | 50<br>60                         | 36<br>42                         |                                  | ns     |

| tsf (1)<br>(0)<br>tsk (1)<br>(0)<br>tsl (1)<br>(0)                                 | Control and data input setup times with respect to CLK (1) for non-stack related functions (TSK, INC, BRT, RST) AC <sub>0</sub> -AC <sub>2</sub> B <sub>0</sub> -B <sub>9</sub> <sup>2</sup> Test |                                |         | 90<br>90<br>27<br>29<br>60<br>60 | 70<br>70<br>22<br>24<br>45<br>45 |                                  | ns     |

| t <sub>HF</sub> (1)<br>(0)<br>t <sub>HK</sub> (1)<br>(0)                           | Control and data input hold times with respect to CLK (1) $AC_0$ - $AC_2$ $B_0$ - $B_9$ <sup>2</sup>                                                                                              |                                |         | 0<br>0<br>0                      | -7<br>-12<br>-12<br>-10          |                                  | ns     |

<sup>1.</sup> Typical values are to T  $_{A}$  = 25°C and V  $_{CC}$  = 5.0 volts 2.  $B_{0}\text{-}B_{9}$  inputs are required to Clock (1) only. See TSK (1) and TSK (0).

### CONTROL STORE SEQUENCER

8X02

PRELIMINARY SPECIFICATION

8X02-I,XL

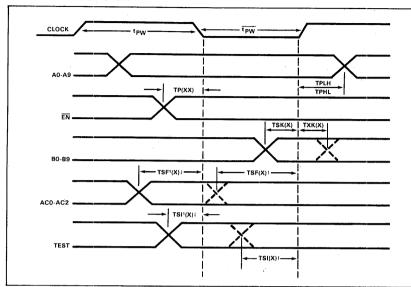

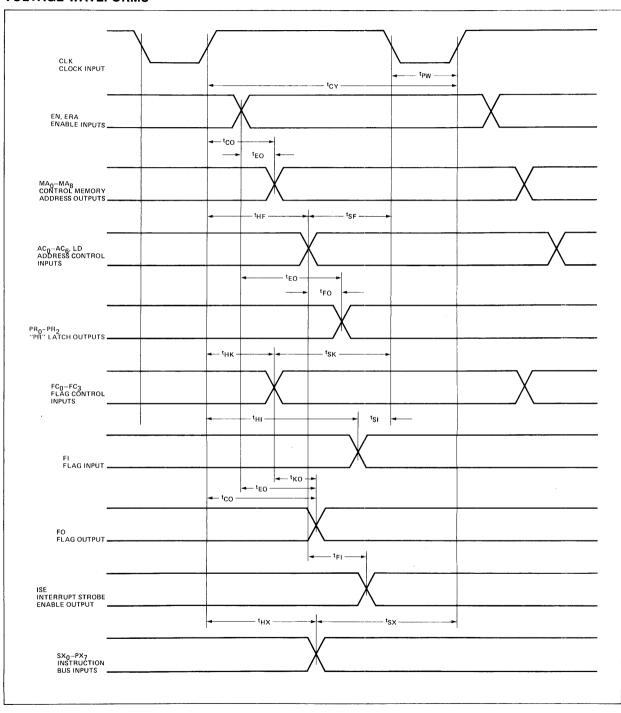

#### **TIMING WAVEFORM**

# PULSE WIDTH (TPW) vs TEMPERATURE

#### DESCRIPTION

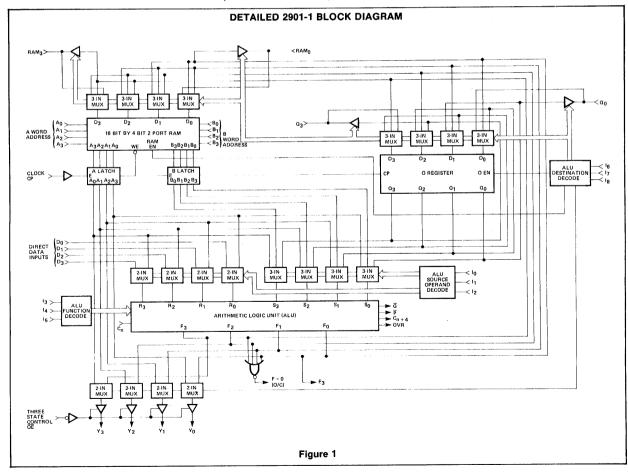

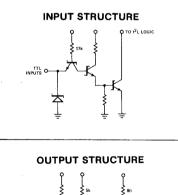

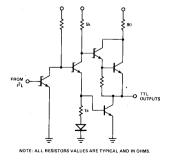

The 4-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPUs, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the 2901-1 will allow efficient emulation of almost any digital computing machine.

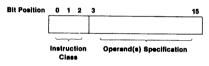

The device, as shown in the block diagram below, consists of a 16-word by 4-bit 2-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The 9-bit microinstruction word is organized into 3 groups of 3 bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

#### **FEATURES**

- 80ns cycle time

- 2-address architecture Independent simultaneous access to 2 working registers saves machine cycles

- 8-function ALU

- Performs addition, 2 subtraction operations, and 5 logic functions on 2 source operands

- Flexible data source selection ALU data is selected from 5 source ports for a total of 203 source operand pairs for every ALU function

- Left/right shift independent of ALU Add and shift operations take only 1 cycle

- 4 status flags

- Carry, overflow, zero, and negative

Expandable

- Connect any number of 2901-1's together for longer word lengths

- Microprogrammable

3 groups of 3 bits each for source operand, ALU function, and destination control

#### **BLOCK DIAGRAM**

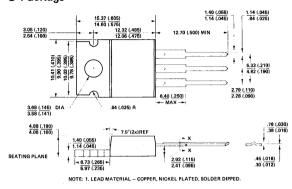

#### PIN CONFIGURATION

#### PIN DESIGNATION

| PIN                     | SYMBOL                             | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TYPE                       |

|-------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1-4                     | A <sub>0</sub> -A <sub>3</sub>     | A Address  The 4 address inputs to the register stack used to select 1 register whose contents are displayed through the A port. $A_0$ is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Active high                |

| 17-20                   | B <sub>0</sub> -B <sub>3</sub>     | <b>B Address</b> The 4 address inputs to the register stack used to select 1 register whose contents are displayed through the B port and into which new data can be written when the clock goes LOW. B <sub>0</sub> is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Active high                |

| 12-14,<br>26-28,<br>5-7 | I <sub>0</sub> -I <sub>8</sub>     | Instruction Control The 9 instruction control lines to the 2901-1 used to determined what data sources will be applied to the ALU (I <sub>012</sub> ), what function the ALU will perform (I <sub>345</sub> ), and what data is to be deposited in the Q register or the register stack (I <sub>678</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                            | Active high                |

| 8 16                    | RAM <sub>3</sub><br>Q <sub>3</sub> | Shift Line A shift line at the MSB of the Q register $(Q_3)$ and the register stack $(RAM_3)$ . Electrically these lines are three-state outputs connected to TTL inputs internal to the 2901-1. When the destination code on $I_{078}$ indicates a left $(up)$ shift $(octal\ 6\ or\ 7)$ the three-state outputs are enabled and the MSB of the Q register is available on the $Q_3$ and the MSB of the ALU output is available on the RAM $_3$ pin. Otherwise, the three-state outputs are off (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a right $(down)$ shift, the pins are used as the data inputs to the MSB of the Q register $(octal\ 4)$ and RAM $(octal\ 4\ or\ 5)$ . | Three-state<br>Active high |

| 9<br>21                 | RAM <sub>0</sub><br>Q <sub>0</sub> | Shift Line Shift lines similar to Q <sub>3</sub> and RAM <sub>3</sub> , at the LSB of the Q register and RAM. These pins are tied to the Q <sub>3</sub> and RAM <sub>3</sub> pins of the adjacent device and are used to transfer data between devices for left and right shifts of the Q register and ALU data.                                                                                                                                                                                                                                                                                                                                                                                                                        | Active high                |

| 22-25                   | D <sub>0</sub> -D <sub>3</sub>     | Direct Data Inputs  A 4-bit data field which may be selected as one of the ALU data sources for entering data into the 2901-1. D <sub>0</sub> is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Active high                |

| 36-39                   | Y <sub>0</sub> -Y <sub>3</sub>     | Data Out The 4 data outputs of the 2901-1. These are three-state output lines. When enabled, they display either the 4 outputs of the ALU or the data on the A port of the register stack, as determined by the destination code I <sub>678</sub> . Y <sub>0</sub> is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Three-state<br>Active high |

| 40                      | ŌĒ                                 | Output Enable When OE is High, the Y outputs are disabled; when OE is Low, the Y outputs are active (high or low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Active low                 |

| 32, 35                  | Ğ, ₱                               | Carry Generate, Propagate The carry generate and propagate outputs of the 2901-1. These signals are used with the N74S182 for carry-lookahead. See Table 7 for the logic equations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Active low                 |

| 34                      | OVR                                | Overflow  This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit. See Table 7 for logic equation.                                                                                                                                                                                                                                                                                                                                                                                                                                         | Active high                |

| 11                      | F = 0                              | $F = 0$ This is an open collector output which goes High (off) if the data on the 4 ALU outputs $F_{0-3}$ are all low. In positive logic, it indicates the result of an ALU operation is zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Active high                |

| 29                      | Cn                                 | Carry In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Active high                |

| 33                      | C <sub>n+4</sub>                   | Carry Out (See Table 7 for logic equations.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Active high                |

| 15                      | СР                                 | Clock The Q register and register stack outputs change on the clock Low-to-High transition. The clock Low time is internally the write enable to the 16X4 RAM which comprises the "master" latches of the register stack. While the clock is Low, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.                                                                                                                                                                                                                                                                                                              | Active high                |

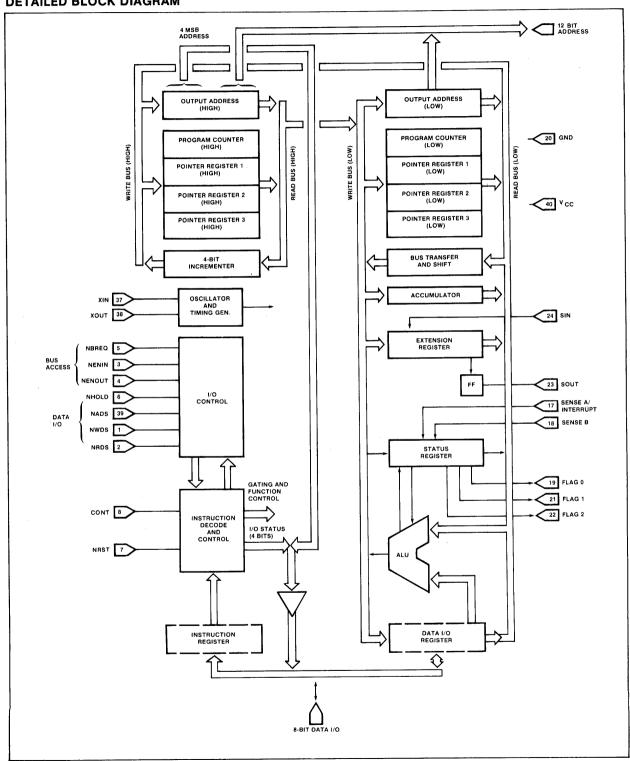

#### SYSTEM DESCRIPTION

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a 4-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are 4 bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A port and B port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is

driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This 3-input multiplexer scheme allows the data to be shifted up (left) 1 bit position, shifted down (right) 1 bit position, or not shifted in either direction.

The RAM A port data outputs and RAM B port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is low. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform 3 binary arithmetic and 5 logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 1, the ALU R-input multiplexer has the RAM A port and the direct

data inputs (D) connected as inputs. Likewise, the ALU S input multiplexer has the RAM A port, the RAM B port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These 5 inputs, when taken 2 at a time, result in 10 possible combinations of source operand pairs. These combinations include AB, AD, AQ, A0, BD, BQ, B0, DQ, D0 and Q0. It is apparent that AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only 7 completely non-redundant source operand pairs for the ALU. The 2901-1 microprocessor implements 8 of these pairs. The microinstruction inputs used to select the ALU source operands are the Io,  $I_1$ , and  $I_2$  inputs. The definition of  $I_0$ ,  $I_1$ , and  $I_2$ for the 8 source operand combinations are as shown in Table 1. Also shown is the octal code for each selection.

| ,              | MICF                                         | юс | 1             | OURCE<br>RANDS |     |

|----------------|----------------------------------------------|----|---------------|----------------|-----|

| l <sub>2</sub> | l <sub>2</sub> l <sub>1</sub> l <sub>0</sub> |    | Octal<br>Code | R              | s   |

| L              | L                                            | L  | 0             | Α              | Q   |

| L              | L                                            | Н  | 1             | Α              | В   |

| L              | Н                                            | L  | 2             | 0              | Q   |

| L              | Н                                            | Н  | 3             | 0              | В   |

| Н              | L                                            | L  | 4             | 0              | Α   |

| Н              | L                                            | Н  | 5             | D              | Α   |

| Н              | Н                                            | L  | 6             | D              | Q · |

| Н              | Н                                            | Н  | . 7           | D              | 0   |

Table 1 ALU SOURCE OPERAND CONTROL

The 2 source operands not fully described as yet are the D input and Q input. The D input is the 4-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

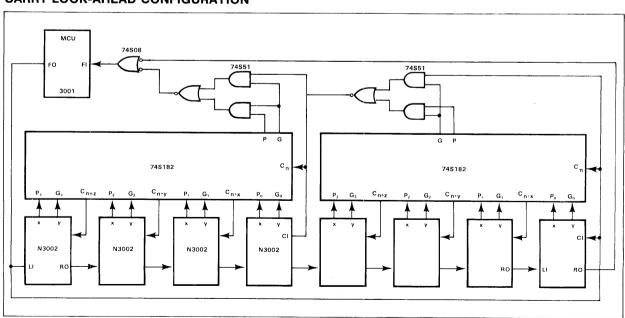

The ALU itself is a high-speed arithmetic/logic operator capable of performing 3 binary arithmetic and 5 logic functions. The I<sub>3</sub>, I<sub>4</sub>, and I<sub>5</sub> microinstruction inputs are used to select the ALU function. The definition of these inputs is shown in Table 2. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate, G. and carry propagate, P, are outputs of the device for use with a carry-look-aheadgenerator such as the N74S182. A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in (Cn) and carry-out (Cn+4) are active high.

| MICRO C                                      | ODE           | ALU        |        |  |  |

|----------------------------------------------|---------------|------------|--------|--|--|

| I <sub>5</sub> I <sub>4</sub> I <sub>3</sub> | Octal<br>Code | Function   | Symbol |  |  |

| LLL                                          | 0             | R Plus S   | R+S    |  |  |

| LLH                                          | 1             | S Minus R  | S - R  |  |  |

| LHL                                          | 2             | R Minus S  | R - S  |  |  |

| LHH                                          | 3             | RORS       | R∨S    |  |  |

| HLL                                          | 4             | RANDS      | R∧S    |  |  |

| H L H                                        | 5             | RANDS      | R∧s    |  |  |

| HHL                                          | 6             | R EX-OR S  | R∀S    |  |  |

| ннн                                          | 7             | R EX-NOR S | R∀S    |  |  |

**Table 2 ALU FUNCTION CONTROL**

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to

| M              | IICRO CODE     |                |               | AM<br>CTION     | 1 4 112415 1211 |                 | SUNCTION SURTED SURFEE |     | -               |                           |                 |                 |

|----------------|----------------|----------------|---------------|-----------------|-----------------|-----------------|------------------------|-----|-----------------|---------------------------|-----------------|-----------------|

| I <sub>8</sub> | I <sub>7</sub> | I <sub>6</sub> | Octal<br>Code | Shift           | Load            | Shift           | Load                   | PUT | RAM₀<br>LO/RI   | RAM <sub>3</sub><br>LI/RO | Q₀<br>LO/RI     | Q₃<br>LI/RO     |

| L              | L              | ۲              | 0             | х               | None            | None            | F→Q                    | · F | х               | х                         | Х               | х               |

| L              | L              | Н              | 1             | x               | None            | Х               | None-                  | F   | ×               | х                         | Х               | x               |

| L              | Н              | L              | 2             | None            | F→B             | X               | None                   | A   | х               | х                         | х               | х               |

| L              | Н              | Н              | 3             | None            | F→B             | х               | None                   | F   | х               | х                         | x               | х               |

| Н              | L              | L              | 4             | Right<br>(Down) | F/2 → B         | Right<br>(Down) | Q/2 → Q                | F   | Fo              | IN <sub>3</sub>           | Q <sub>0</sub>  | IN <sub>3</sub> |

| Н              | L              | н              | 5             | Right (Down)    | F/2 → B         | ×               | None                   | F   | F <sub>0</sub>  | IN <sub>3</sub>           | $Q_0$           | х               |

| Н              | Н              | L              | 6             | Left (Up)       | 2F → B          | Left<br>(Up)    | 2Q → Q                 | F   | IN <sub>o</sub> | F <sub>3</sub>            | IN <sub>0</sub> | $Q_3$           |

| Н              | Н              | н              | 7             | Left<br>(Up)    | 2F → B          | х               | None                   | F   | IN <sub>0</sub> | F <sub>3</sub>            | Х               | $Q_3$           |

X = Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state.

#### Table 3 ALU DESTINATION CONTROL

determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F=0 is high when all F outputs are low. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is high when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstructon inputs. These combinations are shown in Table 3.

The 4-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control (OE) is used to enable the three-state outputs. When OE is high, the Y outputs are in the high-impedance state.

A 2-input multiplexer is also used at the data output such that either the A port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the  $l_{\rm B}$ ,  $l_{\rm T}$ , and  $l_{\rm B}$  microinstruction inputs. Refer to Table 3 for the selected output for each microinstruction code combination

As was discussed previously, the RAM inputs are driven from a 3-input multiplexer. This allows the ALU outputs to be entered

non-shifted, shifted up (left) one position (X2) or shifted down (right) one position ( $\pm 2$ ). The shifter has 2 ports; one is labeled RAM0 and the other is labeled RAM3. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM3 buffer is enabled and the RAM0 multiplexer input is enabled. Likewise, in the shift down mode, the RAM0 buffer and RAM3 input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the  $I_6,\ I_7,\$ and  $I_8$  microinstruction inputs as defined in Table 3.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has 2 ports; one is labeled  $Q_0$  and the other is  $Q_3.$  The operation of these 2 ports is similar to the RAM shifter and is also controlled from  $I_6,\ I_7,\$ and  $I_8$  as shown in Table 3.

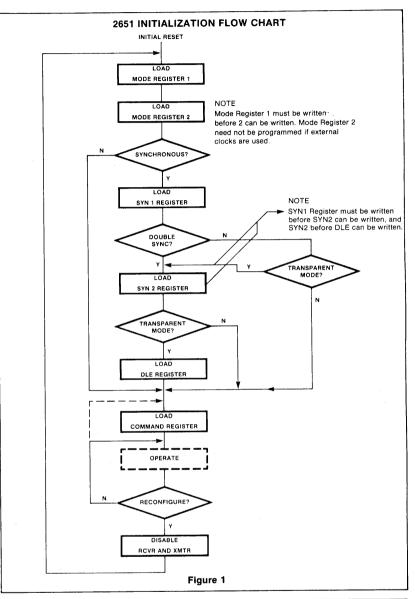

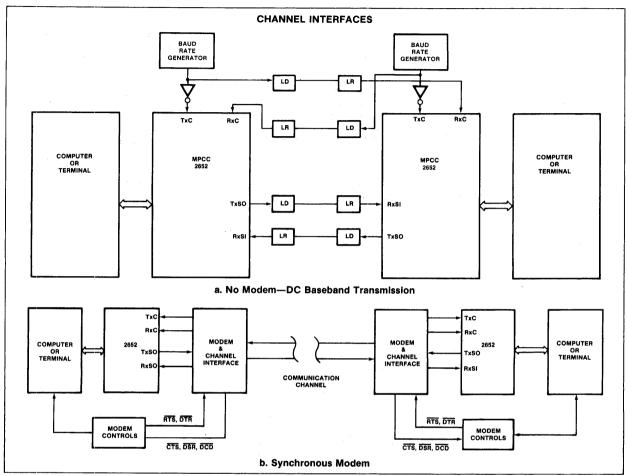

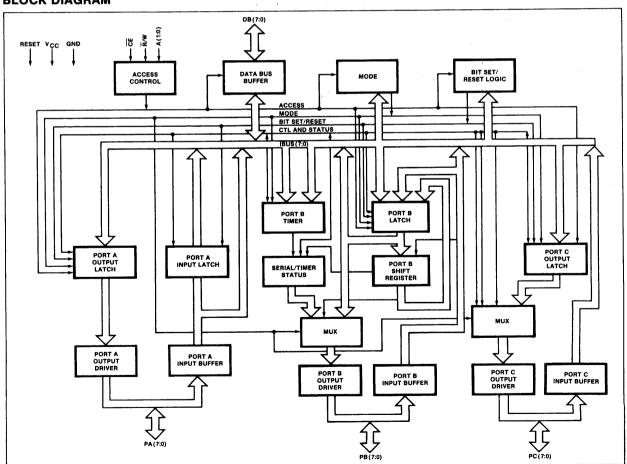

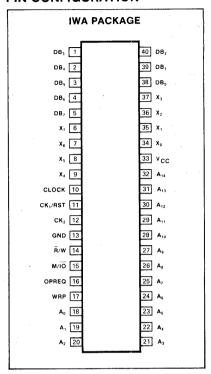

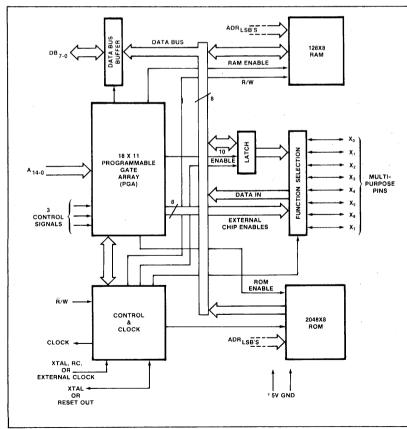

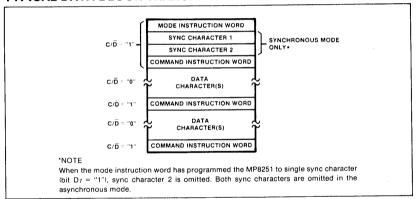

The clock input to the 2901-1 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the low-to-high transition of the clock. When the clock input is high, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is low, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is low.