SONY

# Semiconductor IC

# Data Book 1986 Microprocessors

# SONY®

# Semiconductor Integrated Circuit Data Book 1986

| List of Model Names/<br>Index by Usage | 1 |

|----------------------------------------|---|

| Description                            | 2 |

| Microprocessors                        | 3 |

**Peripherals**

# Semiconductor Integrated Circuit Data Book 1986

### **PREFACE**

This is the 1986 version of the Sony semiconductor IC databook. This book covers all the semiconductor products manufactured and marketed by Sony.

In preparation of this databook, as much characteristic and application data as possible have been collected and added with a view of making this book a convenient reference for users of Sony products. If, however, you are dissatisfied with this book in any way, please write; we welcome suggestions and comments.

The Sony semiconductor IC databook has been edited to include only accurate and reliable data. However, because of technical improvements and other modifications the contents are subject to change without notice.

The circuit examples used in this book are for illustration of typical applications only; we are not responsible for any problems that may occur in the circuitry and patents of any third party if these examples are put in practice.

## Package abbreviations

DIP: Dual Inline Package

MFP: Mini Flat Package (=Flat DIP)

QIP: Quad Inline Package (=Flat QUIP)

PGA: Pin Grid Array

SRK: Shrink Dual Inline Package

# Contents

|    |                                                                                                                                       | F | age |   |

|----|---------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|

| 1. | List of Model Names and Index by usage ······                                                                                         | ( | 6   | ) |

| 2. | IC Nomenclature ·····                                                                                                                 | ( | 7   | ) |

| 3. | Precautions for IC Application ······  A) Absolute maximum ratings  B) Protection against electrostatic breakdown  C) Mounting method | ( | 8   | ) |

| 4. | Quality Assurance and Reliability                                                                                                     | ( | 14  | ) |

| 5. | Block Diagram ····                                                                                                                    | ( | 18  | ) |

| 6. | Data Sheet                                                                                                                            | ( | 19  | ) |

# 1. List of Model Names and Index by Usage

| Туре     | Page | Туре                  | Page | Туре                  | Page |

|----------|------|-----------------------|------|-----------------------|------|

| CXQ70108 | 21   | CXQ71054              | 182  | CXQ71071              | 264  |

| CXQ70116 | 71   | CXQ71055              | 207  | CXQ71086/<br>CXQ71087 | 137  |

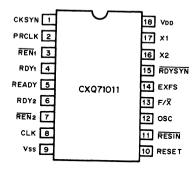

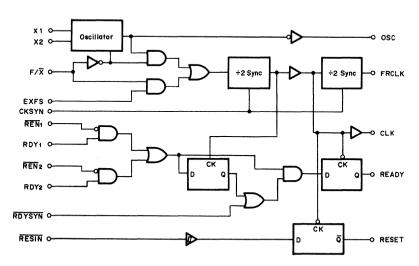

| CXQ71011 | 123  | CXQ71059              | 230  | CXQ71088              | 142  |

| CXQ71051 | 150  | CXQ71082/<br>CXQ71083 | 132  |                       |      |

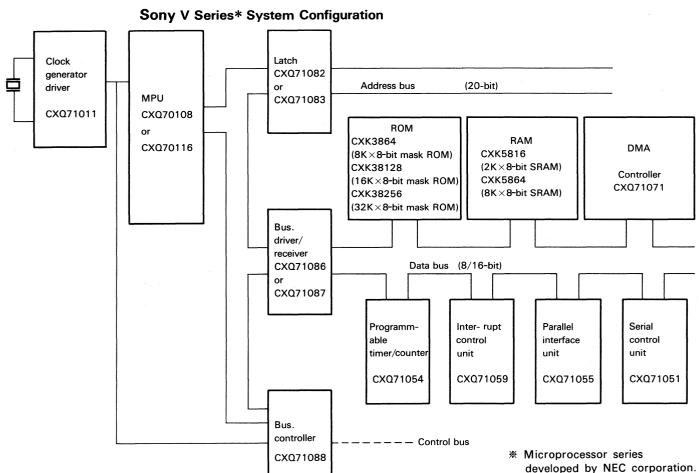

### ■ Microprocessors

| Туре     | Function              | Page |

|----------|-----------------------|------|

| CXQ70108 | 8-bit Microprocessor  | 21   |

| CXQ70116 | 16-bit Microprocessor | 71   |

### ■ Peripherals

| Туре     | Function                               | Page |

|----------|----------------------------------------|------|

| CXQ71011 | Clock pulse Generator/driver           | 123  |

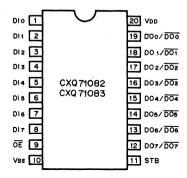

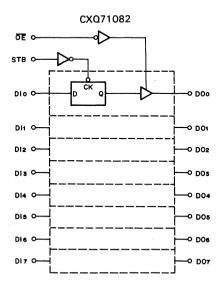

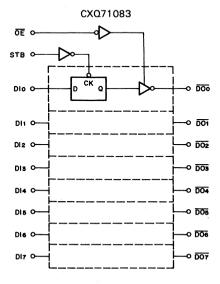

| CXQ71082 | 8-bit latch (non invert)               | 132  |

| CXQ71083 | 8-bit latch (invert)                   | 132  |

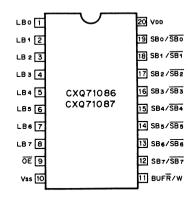

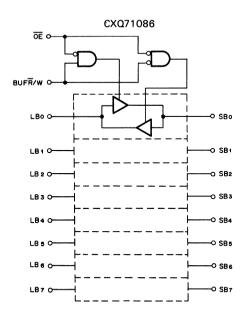

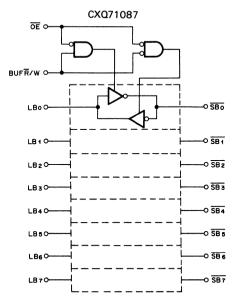

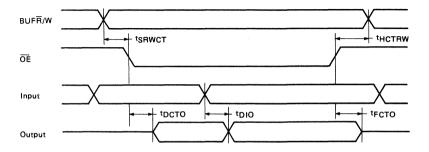

| CXQ71086 | 8-bit bus driver/receiver (non invert) | 137  |

| CXQ71087 | 8-bit bus driver/receiver (invert)     | 137  |

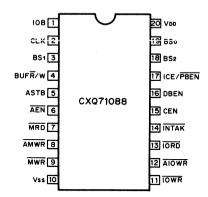

| CXQ71088 | System bus controller                  | 142  |

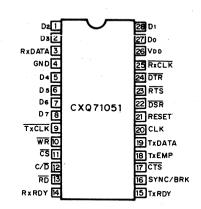

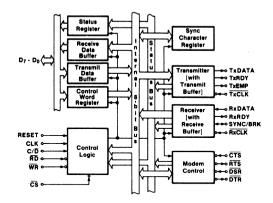

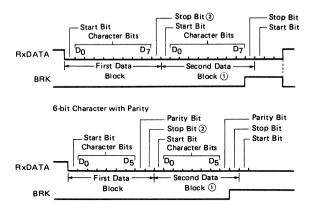

| CXQ71051 | Serial Interface unit                  | 150  |

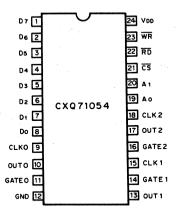

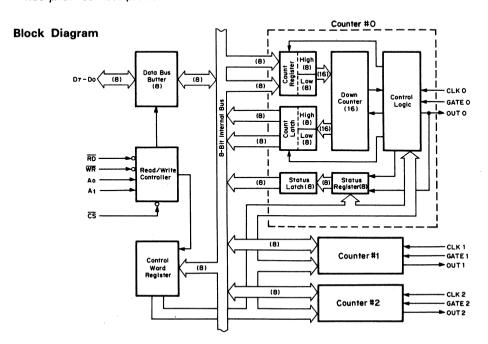

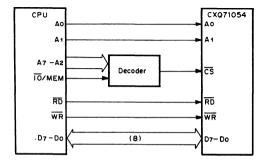

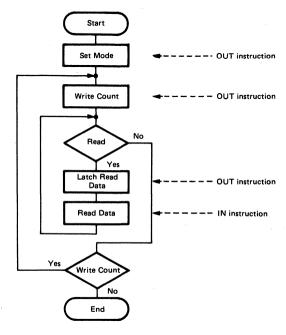

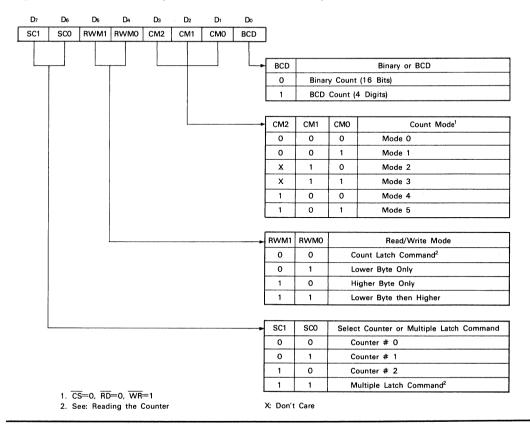

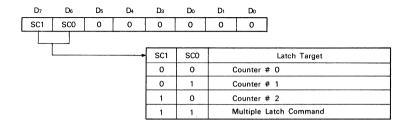

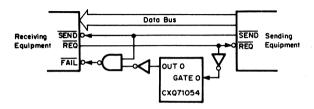

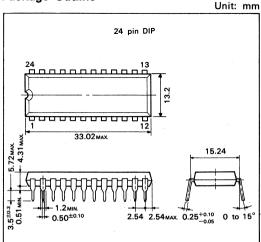

| CXQ71054 | Programmable timer/counter             | 182  |

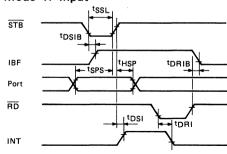

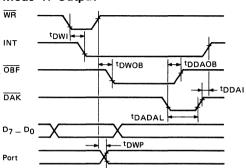

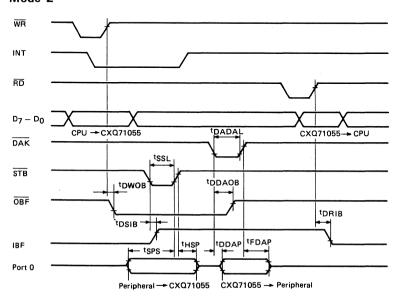

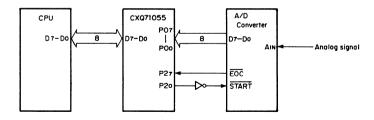

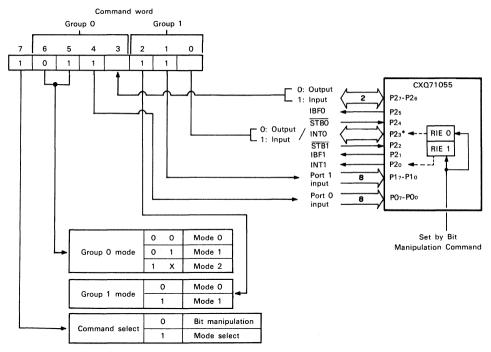

| CXQ71055 | Parallel interface unit                | 207  |

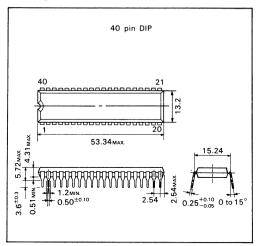

| CXQ71059 | Interrupt control unit                 | 230  |

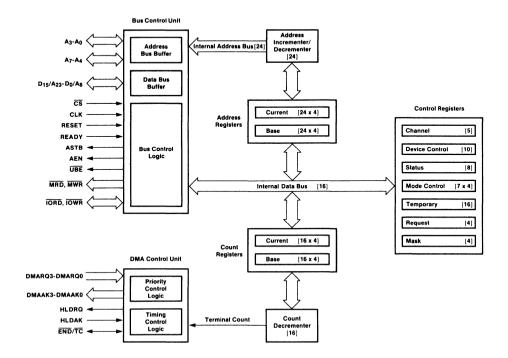

| CXQ71071 | DMA controller                         | 264  |

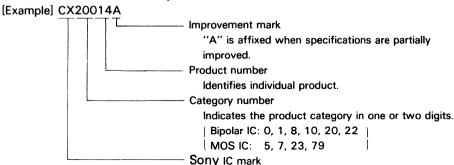

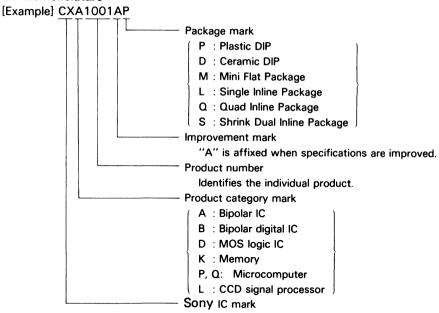

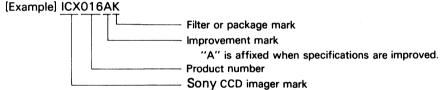

# 2. IC Nomenclature

### 1. Nomenclature of IC product name

Currently, both the conventional and new nomenclature systems are mixed in naming IC products.

### a) Conventional nomenclature system

### b) New nomenclature

# 2. Nomenclature for CCD image product name

# 3. Precautions for IC Application

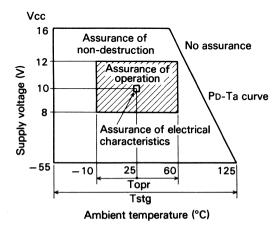

## A) Absolute maximum ratings

The maximum ratings for semiconductor devices are normally specified by "absolute maximum ratings". The values shown in the maximum ratings table must never be exceeded even in a moment.

If the maximum rating is ever exceeded, device deterioration or damage will occur immediately. Then, even if the affected device can operate, the life will be considerably short.

Maximum rating must never be reached for two items at the same time.

### IC maximum ratings

The following maximum ratings are used for ICs.

# (1) Maximum power supply voltage Vcc (VDD)

The maximum voltage that can be applied between the power supply terminal and ground terminal.

This power supply voltage rating is directly related to the dielectric voltage of transistors in the internal circuit; the transistors may be destroyed if this voltage is exceeded.

### (2) Allowable power dissipation PD

The maximum power consumption allowed in IC

In the circuit design the absolute maximum ratings must not be exceeded, and it must be designed only after considering the worst situations among the following:

- Fluctuation in source voltage

- Scattering in the electrical characteristics of electrical parts (transistors, resistors, capacitors, etc.)

- Power dissipation in circuit adjustment

- Ambient temperature

- Fluctuation in input signal

- Abnormal pulses

If this allowable power dissipation is exceeded, electrical and thermal damage may result.

This value varies with the amount of IC integration in package types.

### (3) Operating ambient temperature Topr

The temperature range within which IC can operate satisfactorily.

Even if this temperature range is exceeded and some deterioration in operating characteristics is noted, the IC is not always damaged.

For some ICs, the electrical characteristics at Ta = 25°C are not guaranteed even in this temperature range.

### (4) Storage temperature Tstg

The temperature range for storing the IC which is not operating.

This temperature is restricted by the package material, and the intrinsic properties of the semiconductor.

### (5) Other values

The input voltage Vin, output voltage Vout, input current lin, output current lout and other values may be specified in some IC's.

The relationship among these maximum ratings for IC is shown below.

# B) Protection against electrostatic breakdown

There have been problems of electrostatic destruction of electronic devices since the 2nd World War. Their history is closely related to the advancement in the semiconductor devices; that is, with the development of semiconductor technology, new problems in electrostatic destruction have arisen. This situation, perhaps, can be understood by recalling the case of MOS FET.

Today, the problem of electrostatic destruction is again drawing people's attention as we are entering the era of LSI and VLSI. Here are our suggestions for preventing electrostatic destruction in the device fabrication process.

# Factors causing electrostatic generation in manufacture process

A number of dielectric materials are used in manufacture process. Friction of these materials with the substrate can generate static electricity which may destroy the semiconductor device.

Factors that can cause electrostatic destruction in the manufacture process are shown below:

# Causes of electrostatic destruction of semiconductor parts in manufacture process

# Handling precautions for preventing electrostatic destruction

Explained below are procedures that must be taken in fabrication for preventing the electrostatic destruction of semiconductor devices.

The following basic rules must be obeyed.

- 1 Equalize potentials of terminals when transporting or storing.

- 2 Equalize the potentials of the electric device, work bench, and operator's body that may come in contact with the semiconductor device.

- ③ Prepare an environment that does not generate static electricity.

One method is keeping relative humidi-

ty in the work room about 50%.

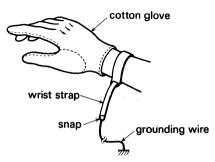

### Operator

### 1) Clothes

Do not use nylon, rubber and other materials which easily generate static electricity. For clothes, use cotton, or antistatic-treated materials. Wear gloves during operation.

### 2) Grounding of operator's body

The operator should connect the specified wrist strap to his arm. If wrist strap cannot be used, then the operator should touch the grounding point with his hand, before handling any semiconductor device.

### example of grounding band

When using a copper wire for grounding, connect a 1M resistance in series near the hand for safety.

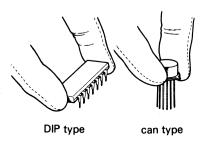

### 3) Handling of semiconductor device

Do not touch the lead. Touch the body of semiconductor device when holding. Limit the number of handling times to a minimum. Do not take the device out of the magazine or package box unless it is absolutely necessary.

### holding of semiconductor device

### **Equipment and tools**

### 1) Grounding of equipment and tools

Ground the equipments and tools that are to be used. Check insulation beforehand to prevent leakage.

### [Check point]

- measuring instrument

- convever

- electric deburr brush

- carrier

- solder dipping tank

- lead cutter

- shelves and racks

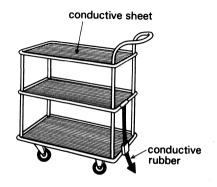

### grounding of carrier

### 2) Grounding of work table

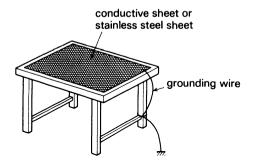

Ground the work table as illustrated. Do not put anything which can easily generate static electricity, such as foam styrol, on the work table.

### grounding of work table

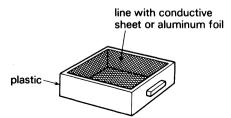

### 3) Semiconductor device case

Use the metal case, or the antistatic plastic case (lined with conductive sheet or aluminum foil)

# plastic case for semiconductor devices

### 4) Insertion of semiconductor device

Insert the semiconductor device in mounting process or on the belt conveyer. The insertion should be done on a conductive sheet, or a wood or metal carrier.

### 5) Operation in energized state

When the substrate is checked while energizing the substrate where the delicate semiconductor device is mounted, be sure to place the substrate on corrugated cardboard, wood, or on a metal carrier.

### 6) Other points of caution

Take note of the kind of the brush material used for removing lead chips. Use metal or antistatic-treated plastic brushes.

# Transporting, storing and packaging methods

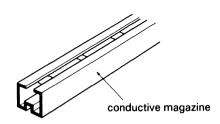

### 1) Magazine

Use the metal, or antistatic-treated plastic IC magazines.

The plastic magazines used for shipping ICs are antistatic-treated, and they can be used for storing ICs.

magazine

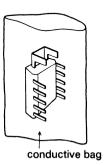

### 2) Bag

Use a conductive bag for keeping ICs. If use of a vinyl bag is unavoidable, be sure to wrap the IC with aluminum foil.

bag

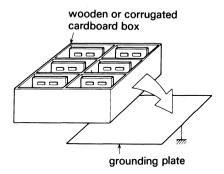

### 3) Handling of delivery box

The delivery box used for carrying substrates must be made of wood or corrugated cardboard. Do not use a vinyl chloride or acrylic delivery box, otherwise static electricity will be generated.

### handling of delivery box

### 4) Treatment after vehicle transport

After truck transport, place the magazine, package box or delivery box on the grounded rack, work table, or concrete floor for discharging. Do not pull the delivery box for more than 1 meter except on a concrete or a wooden floor.

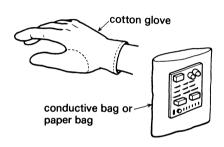

### 5) Handling of mounted substrates

Wear cotton gloves when handling. As far as possible, avoid touching soldered faces. When handling mounted substrates individually, be sure to use a conductive or paper bag. Do not use a polyethylene bag.

### handling of mounted substrate

### Soldering operation

### 1) Soldering iron

Use a soldering iron with a grounded metal part or a soldering iron whose insulation resistance after five minutes from energizing is greater than 10 M  $\Omega$  (DC 500V)

### 2) Operation

After inserting the semiconductor device into the substrate, solder it as quickly as possible. Do not carry the substrate with the inserted semiconductor device by car.

### 3) Correction

When correcting parts (semiconductor device and CR parts) after solder-dipping, be sure to wear cotton gloves. Also, connect the grounding band to the arm, or touch the grounding point before operation.

### 4) Manual soldering

Solder with wrist strap connected to the hand, or by touching the grounding point from time to time during operation.

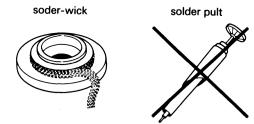

### 5) Removing semiconductor device

Do not use the Solder-Pult when removing the semiconductor device. Use a Soder-wick or equivalent.

### solder remover

### 6) Soldering work table

Use a grounded work table, corrugated cardboard, or wooden work table for soldering. Do not solder on foam styrol, vinyl, or decorative board.

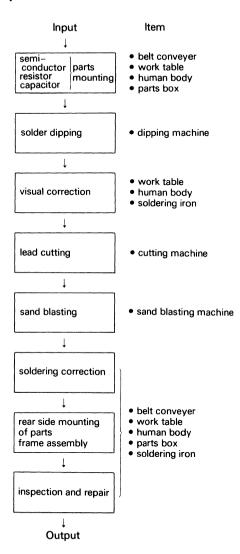

## C) Mounting method

### Soldering and solderability

### (1) Solderability guaranteed by JIS

JIS specifies solderability of an IC terminal (lead) in "JIS-C7022 Test Procedure A-2". An abstract of this standard follows:

- Rosin flux must be used, and the terminal must be dipped in it for 5-10 seconds

- H63A or equivalent solder must be used, and the terminal must be dipped in the solder which has been heated to 230°C±5°C for 5±1 seconds

- Using a microscope, measure the area (%) deposited with solder. JIS specifies that more than 95% of the

total area should be coated with solder.

### (2) Area for soldering warranty

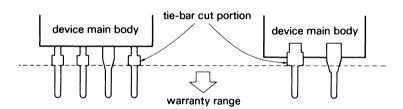

Soldering is warranted for a specific portion of the terminal. The warranted portion is shown in the following figure.

The tie-bar cut portion also serves as a dam to prevent the sealing resin flowing out during device fabrication; it is cut off at the end of the process. Since the terminal is exposed at the cut-off end, the area for soldering is restricted. The portion near the resin is often covered with burrs when sealing with resin; it is not in the soldering warranty area.

### warranty area for soldering

# Resistance to soldering heat

### (1) Specification of JIS

JIS specifies the method for testing the resistance to soldering heat. This method is used for guaranteeing the IC resistance against thermal stresses by soldering. An abstract of this standard is as follows:

Dip the device terminal only once for 10±1 seconds in a solder bath of 260°C±5°C, or for 3<sup>+0.5</sup><sub>-0</sub> seconds in a solder bath of 350°C ±10°C, for a distance of up to 1 to 1.5 mm from the main body.

The temperature of 260°C  $\pm 5$ °C assumes the soldering with solder flow system, and the temperature 350°C  $\pm 10$ °C assumes soldering by soldering iron.

- Leave the device for more than two hours after dipping, then measure the device characteristics.

- Normally, the warranty is limited for 10 seconds at 260°C ±5°C. The distance between the device main body and solder bath is assumed as 1.6 mm.

# 4. Quality Assurance and Reliability

# Sony's Policy of Quality Assurance

The Sony semiconductor embodies two fundamental ideas: "highest quality" and "lowest cost". There are the two key points for realizing these ideas.

One is the "quality" of men fabricating the semiconductor devices. The reliability of these people is reflected in the Sony products. Accordingly, Sony is making a continuous effort to raise the "quality" of people capable of manufacturing and fabricating Sony semiconductor devices.

The other point is a source management system combined with the concept of thorough quality design. With this system, higher quality products can be steadily manufactured through automation of device design, process design, and the fabrication process.

Sony is making constant efforts to supply the most economical and most useful products of very high quality for users.

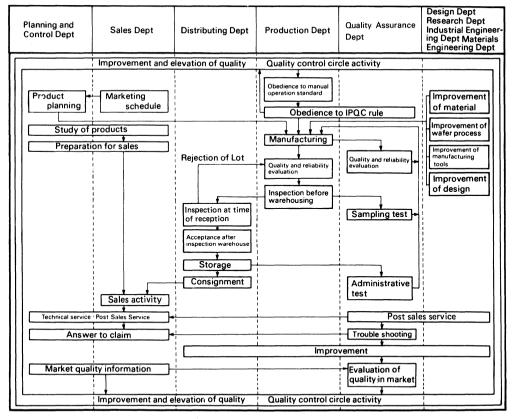

### Quality assurance system of semiconductor products

# Quality assurance criteria and reliability test criteria

### 1) Quality assurance in shipping

Establishing quality in the design and in fabrication is essential to keep the quality and reliability levels of the semiconductor devices at a high level. This is done by the "Zero-defect" (ZD) movement. Further sampling checks, in units of shipping lot, is done on products that have been "total-inspected" at the final fabrication

stage, thus ensuring no detective items. This sampling inspection is done in accordance with MIL-STD-105D.

### 2) Reliability

The reliability test is done, periodically, to confirm reliability level.

### Periodical reliability test

|             |                                                                                     | Test Hour                                             | LTPD (%) |

|-------------|-------------------------------------------------------------------------------------|-------------------------------------------------------|----------|

|             | Electrical characteristic test                                                      | In order to know the qua<br>types are selected and te | •        |

| LIFE TEST   | High temperature operation                                                          | Up to 1000 hr                                         | 10%      |

|             | High temperature storage                                                            | Up to 1000 hr                                         | 10%      |

|             | Low temperature storage                                                             | Up to 1000 hr                                         | 10%      |

|             | High temperature and high humidity storage                                          | Up to 1000 hr                                         | 10%      |

|             | High humidity bias test                                                             | Up to 1000 hr                                         | 10%      |

|             | High temperature and high humidity with bias                                        | Up to 500 hr                                          | 10%      |

|             | Pressure cooker                                                                     | Up to 200 hr                                          | 10%      |

| ENVIRONMENT | Soldering heat resistance heat cycle                                                | 10 s                                                  | 15%      |

| TEST        | Heat cycle                                                                          | 10 cycle                                              | 15%      |

| MECHANICAL  | Solderability                                                                       | Japan Industrial                                      | 15%      |

| TEST        | Lead strength                                                                       | Standard (JIS)                                        | 15%      |

| OTHER TESTS | if necessary test, are selected accordingly to JIS C7021, C7022, EIAJ SD121, IC121. |                                                       |          |

<sup>\*</sup> These tests are selected by sampling standard.

These tests and Inspection data are useful not only to estimate quality in the market place but also as data to improve design and wafer processes.

# Reliability test standard for acceptance of products

| Item                                            | Condition                                                                                                                                                                | Supply voltage            | Testing time                  | LTPD (%) |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------|----------|

| High temperature operation                      | Ta=125°C, 150°C                                                                                                                                                          | TYP                       | 1000 hr                       | 5%       |

| High temperature with bias                      | Ta = 125°C, 150°C                                                                                                                                                        | TYP                       | 1000 hr                       | 5%       |

| High temperature storage                        | Ta = 150°C                                                                                                                                                               |                           | 1000 hr                       | 5%       |

| Low temperature storage                         | Ta = -65°C                                                                                                                                                               |                           | 1000 hr                       | 5%       |

| High temperature and humidity storage           | Ta = 85°C, 85%RH                                                                                                                                                         |                           | 1000 hr                       | 5%       |

| High temperature and<br>High humidity with bias | Ta = 85°C, 85%RH                                                                                                                                                         | TYP<br>(I hr on/3 hr off) | 1000 hr                       | 5%       |

| Pressure cooker                                 | Ta = 121°C, 100%RH, per square inch                                                                                                                                      | , 30 pounds               | 1000 hr                       | 5%       |

| Temperature cycle                               | $Ta = -65^{\circ}C \text{ to } +150^{\circ}$                                                                                                                             | D <sub>C</sub> C          | 100 C                         | 10%      |

| Heat shock                                      | Ta = 0°C to +100°C                                                                                                                                                       | •                         | 5 C                           | 10%      |

| Soldering heat resistance                       | Tsolder = 260°C                                                                                                                                                          |                           | 10 S                          | 105      |

| Solderability                                   | Tsolder =230°C (Rosin type flux)                                                                                                                                         |                           | 5 S                           | 10%      |

| Mechanical shock                                | X, Y, Z 1500G<br>0.5 ms half sine wave                                                                                                                                   | •                         | 3 times for each direction    | 10%      |

| Vibration                                       | X, Y, Z 20G 10~200 sine wave vibration                                                                                                                                   | 00∼10 Hz (4 min)          | 16 minutes for each direction | 10%      |

| Constant acceleration                           | X, Y, Z 20,000 G<br>centrifugal acceleration                                                                                                                             | on                        | 1 minute for each direction   | 10%      |

| Fall by gravity                                 | Falling from the heigh<br>to maple plate by gra                                                                                                                          |                           | 3 times                       | 10%      |

| Lead strength (Bend)                            | Based on JIS                                                                                                                                                             |                           |                               | 10%      |

| Electrostatics strength                         | Device must be designed again, when electrostatic strength is below standard supplying surge voltage To each pin under the conditions of C = 200PF and Rs = 0 $\Omega$ . |                           |                               |          |

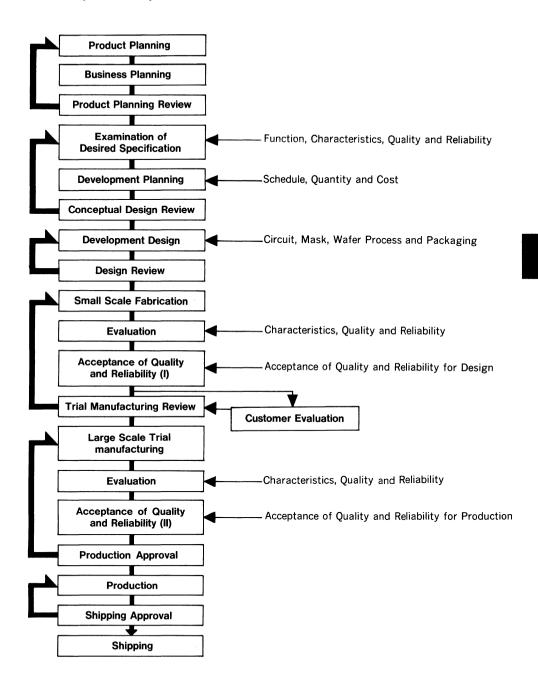

# From development to production

000

# Microprocessors

## ■ Microprocessors

| Туре     | Function              | Page |

|----------|-----------------------|------|

| CXQ70108 | 8-bit Microprocessor  | 21   |

| CXQ70116 | 16-bit Microprocessor | 71   |

# CXQ70108

# 8-Bit Microprocessor

### Description

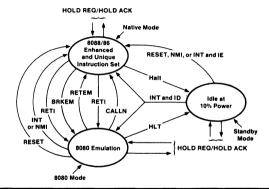

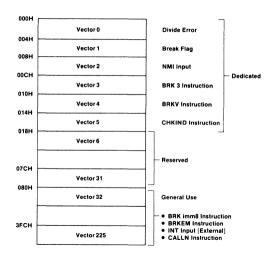

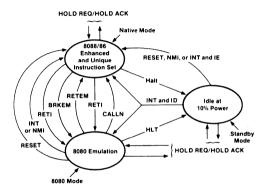

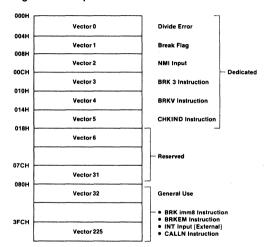

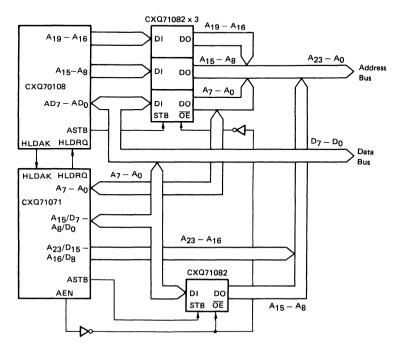

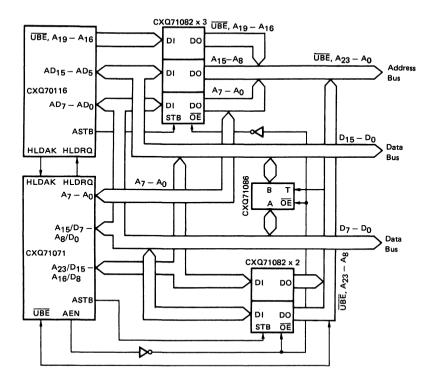

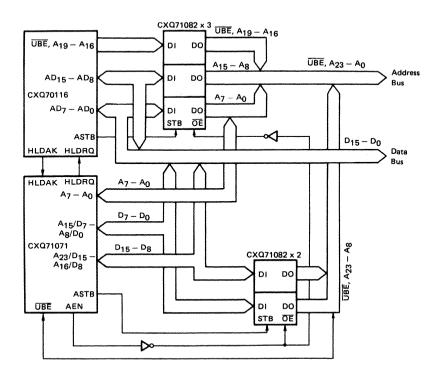

The CXQ70108 is a CMOS 8-bit microprocessor with internal 16-bit architecture and an 8-bit external data bus. The CXO70108 instruction set is a superset of the 8086/8088; however, mnemonics and execution times are different. The CXQ70108 additionally has a powerful instruction set including bit processing. packed BCD operations, and high-speed multiplication/ division operations. The CXQ70108 can also emulate the functions of an 8080 and comes with a standby mode that significantly reduces power consumption. It is software-compatible with the CXQ70116 16-bit microprocessor.

#### Features

- · Minimum instruction execution time: 250 ns (at 8 MHz)

- Maximum addressable memory: 1 Mbytes

- · Abundant memory addressing modes

- 14 × 16-bit register set

- 101 instructions

- Instruction set is a superset of 8086/8088 instruction set

- · Bit, byte, word and block operations

- Bit field operation instructions

- Packed BCD operation instructions

- Multiplication/division instructions execution time: 2.4 µs to 7.1 µs (at 8 MHz)

- · High-speed block transfer instructions: 1 Mbvtes/s (at 8 MHz)

- · High-speed calculation of effective addresses:

- 2 clock cycles in any addressing mode

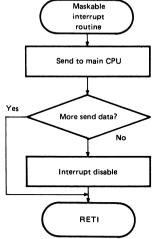

- Maskable (INT) and nonmaskable (NMI) interrupt inputs

- IEEE-796 bus compatible interface

- 8080 emulation functions

- CMOS technology

- · Low power consumption

- · Standby function

- · Single power supply

- 5 MHz or 8 MHz clock

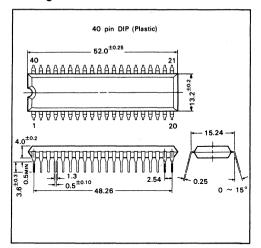

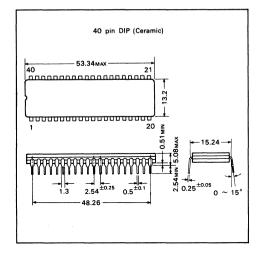

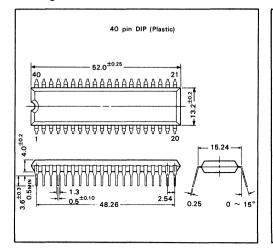

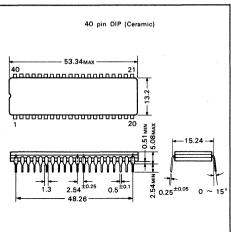

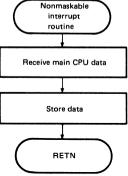

- 40-pin Plastic/Ceramic DIP (600 mil)

- NEC  $\mu$ PD70108 (V20) compatible

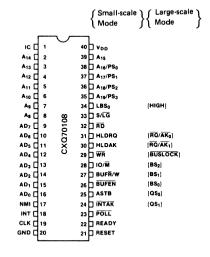

### Pin Configuration (Top View)

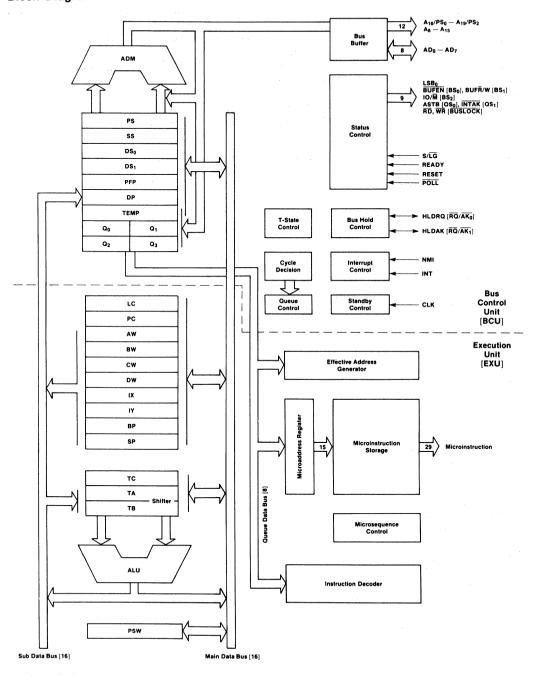

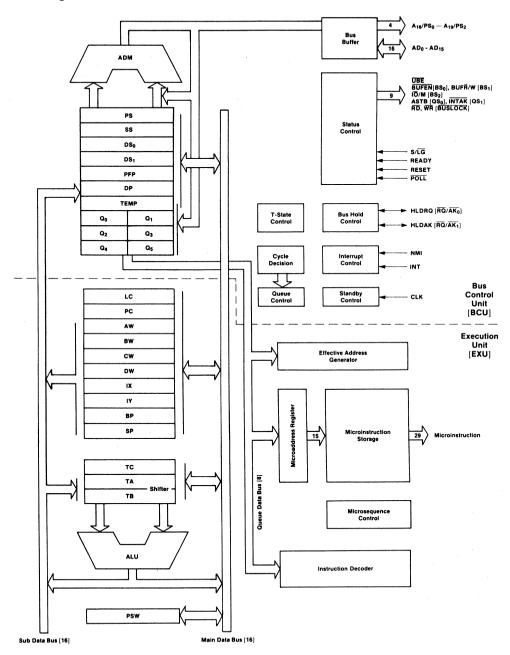

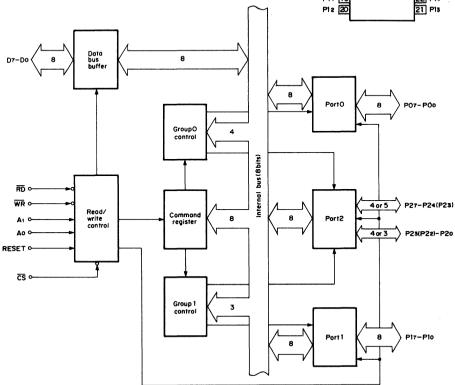

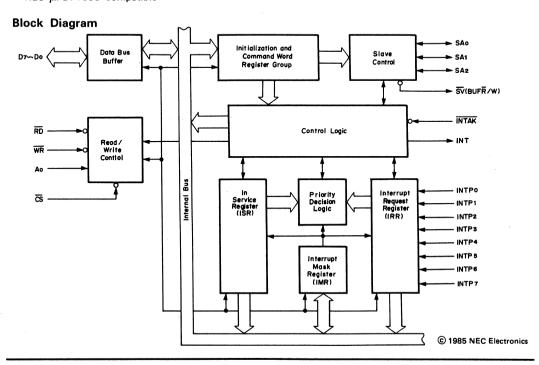

### **Block Diagram**

### Pin Identification

| No.   | Symbol                    | Direction       | Function                                                                   |  |

|-------|---------------------------|-----------------|----------------------------------------------------------------------------|--|

| 1     | IC*                       |                 | Internally connected                                                       |  |

| 2—8   | A14—A8                    | Out             | Address bus, middle bits                                                   |  |

| 9—16  | AD7—AD0                   | In/Out          | Address/data bus                                                           |  |

| 17    | NMI                       | In              | Nonmaskable interrupt input                                                |  |

| 18    | INT                       | In              | Maskable interrupt input                                                   |  |

| 19    | CLK                       | In              | Clock input                                                                |  |

| 20    | GND                       |                 | Ground                                                                     |  |

| 21    | RESET                     | In              | Reset input                                                                |  |

| 22    | READY                     | ln              | Ready input                                                                |  |

| 23    | POLL                      | In              | Poll input                                                                 |  |

| 24    | INTAK (QS1)               | Out             | Interrupt acknowledge output (queue status bit 1 output)                   |  |

| 25    | ASTB (QS <sub>0</sub> )   | Out             | Address strobe output (queue status bit 0 output)                          |  |

| 26    | BUFEN (BS <sub>0</sub> )  | Out             | Buffer enable output (bus status bit 0 output)                             |  |

| 27    | BUFR/W (BS <sub>1</sub> ) | Out             | Buffer read/write output (bus status bit 1 output)                         |  |

| 28    | IO/M (BS <sub>2</sub> )   | Out             | Access is I/O or memory (bus status bit 2 output)                          |  |

| 29    | WR (BUSLOCK)              | Out             | Write strobe output (bus lock output)                                      |  |

| 30    | HLDAK (RQ/AK1)            | Out<br>(In/Out) | Hold acknowledge output, (bus hold request input/<br>acknowledge output 1) |  |

| 31    | HLDRQ (RQ/AKo)            | In<br>(In/Out)  | Hold request input (bus hold request input/acknowledge output 0)           |  |

| 32    | RD                        | Out             | Read strobe output                                                         |  |

| 33    | S/ <del>LG</del>          | In              | Small-scale/large-scale system input                                       |  |

| 34    | LBSo(HIGH)                | Out             | Latched bus status output 0 (always high in large-scale systems)           |  |

| 35—38 | A19/PS3—A16/PS0           | Out             | Address bus, high bits or processor status output                          |  |

| 39    | A15                       | Out             | Address bus, bit 15                                                        |  |

| 40    | V <sub>DD</sub>           |                 | Power supply                                                               |  |

Notes: \*IC should be connected to ground.

Where pins have different functions in small- and large-scale systems, the large-scale system pin symbol and function are in parentheses.

Unused input pins should be tied to ground or  $V_{DD}$  to minimize power dissipation and prevent the flow of potentially harmful currents.

#### Pin Functions

Some pins of the CXQ70108 have different functions according to whether the microprocessor is used in a small- or large-scale system. Other pins function the same way in either type of system.

#### A<sub>15</sub> — A<sub>8</sub> [Address Bus]

For small- and large-scale systems.

The CPU uses these pins to output the middle 8 bits of the 20-bit address data. They are three-state output and float to the high impedance during hold acknowledge.

#### AD7 - AD0 [Address/Data Bus]

For small- and large-scale systems.

The CPU uses these pins as the time-multiplexed address and data bus. They are active high. This bus contains the lower 8 bits of the 20-bit address during T1 of the bus cycle and is used as an 8-bit data bus during T2, T3, and T4 of the bus cycle.

Sixteen-bit data I/O is performed in two steps. The low byte is sent first, followed by the high byte. The address/data bus is a three-state bus and can be high or low during standby mode. The bus will float to the high impedance during hold and interrupt acknowledge.

#### NMI [Nonmaskable Interrupt]

For small- and large-scale systems.

This pin is used to input nonmaskable interrupt requests. NMI cannot be masked by software. This input is positive edge-triggered and can be sensed during any clock cycle. Actual interrupt processing begins, however, after completion of the instruction in progress.

The contents of interrupt vector 2 determine the starting address for the interrupt-servicing routine. Note that a hold request will be accepted even during NMI acknowledge.

This interrupt will cause the CXQ70108 to exit the standby mode.

#### INT [Maskable Interrupt]

For small- and large-scale systems.

This pin is a level-triggered interrupt request that can be masked by software.

INT is active high and is sensed during the last clock of the instruction. The interrupt will be accepted if the system is in interrupt enable state (if the interrupt enable flag IE is set). The CPU outputs the INTAK signal to inform external devices that the interrupt request has been granted.

If NMI and INT interrupts occur at the same time, NMI has higher priority than INT and INT cannot be accepted. A hold request will be accepted during INT acknowledge.

This interrupt causes the CXQ70108 to exit the standby mode.

#### CLK [Clock]

For small- and large-scale systems.

This pin is used for external clock input.

### **RESET [Reset]**

For small- and large-scale systems.

This pin is used for the CPU reset signal. It is active high. Input of this signal has priority over all other operations. After the reset signal input returns low, the CPU begins execution of the program starting at address FFFFOH.

In addition to causing normal CPU start, RESET input will cause the CXQ70108 to exit the standby mode.

### READY [Ready]

For small- and large-scale systems.

When the memory or I/O device being accessed cannot complete data read or write within the CPU basic access time, it can generate a CPU wait state (Tw) by setting this signal to inactive (low) and requesting a read/write cycle delay.

If the READY signal is active (high) during either T3 or Tw state, the CPU will not generate a wait state.

### POLL [Poll]

For small- and large-sclae systems.

The CPU checks this input upon execution of the POLL instruction. If the input is low, then execution continues. If the input is high, the CPU will check the POLL input every five clock cycles until the input becomes low again.

The POLL and READY functions are used to synchronize CPU program execution with the operation of external devices

### RD [Read Strobe]

For small- and large-scale systems.

The CPU outputs this strobe signal during data read from an I/O device or memory. The  $IO/\overline{M}$  signal is used to select between I/O and memory.  $\overline{RD}$  will be high during standby mode. It is three-state and floats to the high impedance during hold acknowledge.

### S/LG [Small/Large]

For small- and large-scale systems.

This signal determines the operation mode of the CPU. This signal is fixed either high or low. When this signal is high, the CPU will operate in small-scale system mode, and when low, in the large-scale system mode. A small-scale system will have at most one bus master such as a DMA controller device on the bus. A large-scale system can have more than one bus master accessing the bus as well as the CPU.

Pins 24 to 31 and pin 34 function differently depending on the operating mode of the CPU. Separate nomenclature is adopted for these signals in the two operation modes.

| Pin No.  | Fur                  | oction             |

|----------|----------------------|--------------------|

| FIII NO. | S/LG-high            | S/LG-low           |

| 24       | INTAK                | QS <sub>1</sub>    |

| 25       | ASTB                 | QS <sub>0</sub>    |

| 26       | BUFEN                | BS <sub>0</sub>    |

| 27       | BUFR/W               | BS <sub>1</sub>    |

| 28       | IO/M BS <sub>2</sub> |                    |

| 29       | WR                   | BUSLOCK            |

| 30       | HLDAK                | RQ/AK <sub>1</sub> |

| 31       | HLDRQ                | RQ/AK <sub>0</sub> |

| 34       | LBS <sub>0</sub>     | Always high        |

### INTAK [Interrupt Acknowledge]

For small-scale systems.

The CPU generates the INTAK signal low when it accepts an INT signal.

The interrupting device synchronizes with this signal and outputs the interrupt vector to the CPU via the data bus (AD7 — AD0). INTAK will be high during standby mode.

#### ASTB [Address Strobe]

For small-scale systems.

The CPU outputs this strobe signal to latch address information at an external latch. ASTB will be low during standby mode.

### **BUFEN** [Buffer Enable]

For small-scale systems.

It is used as the output enable signal for an external bidirectional buffer. The CPU generates this signal during data transfer operations with external memory or I/O devices or during input of an interrupt vector.

BUFEN will be high during standby mode. It is three-state and floats to the high impedance during hold acknowledge.

### BUFR/W [Buffer Read/Write]

For small-scale systems.

The output of this signal determines the direction of data transfer with an external bidirectional buffer. A high output causes transmission from the CPU to the external device; a low signal causes data transfer from the external device to the CPU.

BUFR/W will be either high or low during standby mode. It is three-state and floats to the high impedance during hold acknowledge.

### IO/M [IO/Memory]

For small-scale systems.

The CPU generates this signal to specify either I/O access or memory access. A high-level output specifies I/O and a low-level specifies memory.

$10/\overline{M}$  will be either high or low during standby mode. It is three-state and floats to the high impedance during hold acknowledge.

### WR [Write Strobe]

For small-scale systems.

The CPU generates this strobe signal during data write to an I/O device or memory. Selection of either I/O or memory is performed by the  $IO/\overline{M}$  signal.

WR will be high during standby mode. It is three-state and floats to the high impedance during hold acknowledge.

#### HLDAK [Hold Acknowledge]

For small-scale systems.

The HLDAK signal is used to indicate that the CPU accepts the hold request signal (HLDRQ). When this signal is high, the address bus, address/data bus, and the control lines become high impedance.

### **HLDRQ** [Hold Request]

For small-scale systems.

This input signal is used by external devices to request the CPU to release the address bus, address/data bus, and the control bus.

### LBSo [Latched Bus Status 0]

For small-scale systems.

The CPU uses this signal along with the  $IO/\overline{M}$  and  $BUF\overline{R}/W$  signals to inform an external device what the current bus cycle is.

| IO/M | BUFR/W | LBS <sub>0</sub> | Bus Cycle             |

|------|--------|------------------|-----------------------|

| 0    | 0      | 0                | Program fetch         |

| 0    | 0      | 1                | Memory read           |

| 0    | 1      | 0                | Memory write          |

| 0    | 1      | 1                | Passive state         |

| 1    | 0      | 0                | Interrupt acknowledge |

| 1    | 0      | 1                | I/O read              |

| 1    | 1      | 0                | I/O write             |

| 1    | 1      | 1                | Halt                  |

### A19/PS3 - A16/PS0 [Address Bus/Processor Status]

For small- and large-scale systems.

These pins are time-multiplexed to operate as an address bus and as processor status signals.

When used as the address bus, these pins are the high 4 bits of the 20-bit memory address. During I/O access, all 4 bits output data 0.

The processor status signals are provided for both memory and I/O use. PS3 is always 0 in the native mode and 1 in 8080 emulation mode. The interrupt enable flag (IE) is pin on pin PS2. Pins PS1 and PS0 indicate which memory segment is being accessed.

| A17/PS1 | A <sub>16</sub> /PS <sub>0</sub> | Segment         |

|---------|----------------------------------|-----------------|

| 0       | 0                                | Data segment 1  |

| 0       | 1                                | Stack segment   |

| 1       | 0                                | Program segment |

| 1       | 1                                | Data segment 0  |

A<sub>19</sub>/PS<sub>3</sub> — A<sub>16</sub>/PS<sub>0</sub> will be either high or low during standby mode. They are three-state and float to the high impedance during hold acknowledge.

#### QS<sub>1</sub>, QS<sub>0</sub> [Queue Status]

For large-scale systems.

The CPU uses these signals to allow external devices, such as the floating-point arithmetic processor chip, to monitor the status of the internal CPU instruction queue.

| QS <sub>1</sub> | QS <sub>0</sub> | Instruction Queue Status        |

|-----------------|-----------------|---------------------------------|

| 0               | 0               | NOP (queue does not change)     |

| 0               | 1               | First byte of instruction       |

| 1               | 0               | Flush queue                     |

| 1               | 1               | Subsequent bytes of instruction |

The instruction queue status indicated by these signals is the status when the execution unit (EXU) accesses the instruction queue. The data output from these pins is therefore valid only for one clock cycle immediately following queue access. These status signals are provided so that the floating-point processor chip can monitor the CPU's program execution status and synchronize its operation with the CPU when control is passed to it by the FPO (Floating Point Operation) instructions.

QS1, QSo will be low during standby mode.

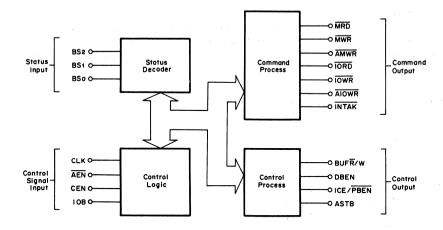

### BS2 - BS0 [Bus Status]

For large-scale systems.

The CPU uses these status signals to allow an external bus controller to monitor what the current bus cycle is.

The external bus controller decodes these signals and generates the control signals required to perform access of the memory or I/O device.

| BS <sub>2</sub> | BS <sub>1</sub> | BSo | Bus Cycle             |  |  |  |

|-----------------|-----------------|-----|-----------------------|--|--|--|

| 0               | 0               | 0   | Interrupt acknowledge |  |  |  |

| 0               | 0               | 1   | I/O read              |  |  |  |

| 0               | 1               | 0   | I/O write             |  |  |  |

| 0               | 1               | 1   | Halt                  |  |  |  |

| 1               | 0               | -0  | Program fetch         |  |  |  |

| 1               | 0               | 1   | Memory read           |  |  |  |

| 1               | 1               | 0   | Memory write          |  |  |  |

| 1               | 1               | 1   | Passive state         |  |  |  |

BS2 — BS0 will be high during standby mode. They are three-state and floats to the high impedance during hold acknowledge.

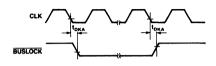

### **BUSLOCK** [Bus Lock]

For large-scale systems.

The CPU uses this signal to secure the bus while executing the instruction immediately following the BUSLOCK prefix instruction. It is a status signal to the other bus masters in a multiprocessor system inhibiting them from using the system bus during this time.

The output of this signal is three-state and becomes high impedance during hold acknowledge. BUSLOCK is high during standby mode except if the HALT instruction has a BUSLOCK prefix.

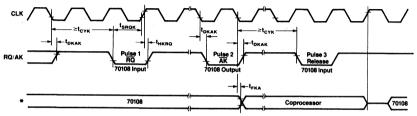

### RQ/AK1, RQ./AK0 [Hold Request/Acknowledge]

For large-scale systems.

These pins function as bus hold request inputs ( $\overline{RQ}$ ) and as bus hold acknowledge outputs ( $\overline{AK}$ ).  $\overline{RQ}/\overline{AK}$ 0 has a higher priority than  $\overline{RQ}/\overline{AK}$ 1.

These pins have three-state outputs with on-chip pull-up resistors which keep the pin at high level when the output is high impedance.

### VDD [Power Supply]

For small-and large-scale systems.

This pin is used for the +5V power supply.

### GND [Ground]

For small- and large-scale systems.

This pin is used for ground.

### IC [Internally Connected]

This pin is used for tests performed at the factory by SONY. The CXQ70108 is used with this pin at ground potential.

### **Absolute Maximum Ratings**

$(Ta=+25^{\circ}C)$

| Symbol | Rating Value            | Unit                                                                                                                                                                                                   |

|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | -0.5 to +0.7            | V                                                                                                                                                                                                      |

| Vı     | -0.5 to VDD+0.3         | V                                                                                                                                                                                                      |

| Vĸ     | -0.5 to VDD+1.0         | V                                                                                                                                                                                                      |

| Vo     | -0.5 to VDD+0.3         | V                                                                                                                                                                                                      |

| PDMAX  | +0.5                    | W                                                                                                                                                                                                      |

| Topr   | -40 to +85              | °C                                                                                                                                                                                                     |

| Tstg   | -65 to +150             | °C                                                                                                                                                                                                     |

|        | VDD VI VK VO PDMAX Topr | Vob         -0.5 to +0.7           VI         -0.5 to Vbb+0.3           Vκ         -0.5 to Vbb+1.0           Vo         -0.5 to Vbb+0.3           PDMAX         +0.5           Topr         -40 to +85 |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC Characteristics

CXQ70108-5,  $T_a=-40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD}=+5V\pm10\%$ CXQ70108-8,  $T_a=-10^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{DD}=+5V\pm5\%$

| Parameter                   | Combal |                     | Limits    |                      | 11   | Test Conditions                 |  |

|-----------------------------|--------|---------------------|-----------|----------------------|------|---------------------------------|--|

| Parameter                   | Symbol | Min.                | Min. Typ. |                      | Unit | rest Conditions                 |  |

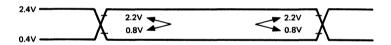

| Input voltage high          | ViH    | 2.2                 |           | V <sub>DD</sub> +0.3 | ٧    |                                 |  |

| Input voltage low           | VIL    | -0.5                |           | 0.8                  | V    |                                 |  |

| CLK input voltage high      | Vкн    | 3.9                 |           | V <sub>DD</sub> +1.0 | ٧    |                                 |  |

| CLK input voltage low       | VĸL    | -0.5                |           | 0.6                  | ٧    |                                 |  |

| Output voltage high         | Vон    | $0.7 \times V_{DD}$ |           |                      | ٧    | I <sub>OH</sub> =-400 μA        |  |

| Output voltage low          | Vol    |                     |           | 0.4                  | ٧    | I <sub>OL</sub> =2.5 mA         |  |

| Input leakage current high  | Ішн    |                     |           | 10                   | μΑ   | V <sub>I</sub> =V <sub>DD</sub> |  |

| Input leakage current low   | Luc    |                     |           | -10                  | μΑ   | V <sub>I</sub> =0V              |  |

| Output leakage current high | Ісон   |                     |           | 10                   | μΑ   | Vo=VDD                          |  |

| Output leakage current low  | ILOL   |                     |           | -10                  | μΑ   | V <sub>0</sub> =0V              |  |

|                             | loo    | 70108-5             | 30        | 60                   | mA   | Normal operation                |  |

| Supply current              |        | 5 MHz               | 5         | 10                   | mA   | Standby mode                    |  |

|                             |        | 70108-8             | 45        | 80                   | mA   | Normal Operation                |  |

|                             | 8 MH   |                     | 6         | 12                   | mA   | Standby mode                    |  |

### Capacitance

$(Ta=+25^{\circ}C, V_{DD}=0V)$

| Parameter         | Symbol | Lin  | nits | Unit  | Test Conditions                |  |  |

|-------------------|--------|------|------|-------|--------------------------------|--|--|

| Farameter         | Symbol | Min. | Max. | Oille |                                |  |  |

| Input capacitance | Cı     |      | 15   | pF    | fc=1 MHz                       |  |  |

| I/O capacitance   | Сю     |      | 15   | pF    | Unmeasured pins returned to OV |  |  |

## **AC** Characteristics

CXQ70108-5,  $Ta=-40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{DD}=+5V\pm10\%$ CXQ70108-8,  $Ta=-10^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{DD}=+5V\pm5\%$

| D                                   | Symbol | CXQ70108-5 |      | CXQ70108-8 |      | 11:4 | Test                   |

|-------------------------------------|--------|------------|------|------------|------|------|------------------------|

| Parameter                           |        | Min.       | Max. | Min.       | Max. | Unit | Conditions             |

| Small/Large Scale                   |        |            |      |            |      |      |                        |

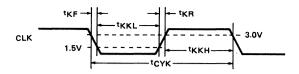

| Clock cycle                         | tcyk   | 200        | 500  | 125        | 500  | ns   |                        |

| Clock pulse width high              | tĸĸн   | 69         |      | 50         |      | ns   | V <sub>KH</sub> =3.0V  |

| Clock pulse width low               | tkkl   | 90         |      | 60         |      | ns   | V <sub>KL</sub> =1.5V  |

| Clock rise time                     | tkr    |            | 10   |            | 8    | ns   | 1.5V to 3.0V           |

| Clock fall time                     | tkf    |            | 10   |            | 7    | ns   | 3.0V to 1.5V           |

| READY inactive setup to CLK ↓       | tsrylk | -8         |      | -8         |      | ns   |                        |

| READY inactive hold after CLK ↑     | thkryh | 30         |      | 20         |      | ns   | *                      |

| READY active setup to Cl.K ↑        | tsryhk | tKKL-8     |      | tKKL-8     |      | ns   |                        |

| READY active hold after CLK 1       | thkryl | 30         |      | 20         |      | ns   |                        |

| Data setup time to CLK ↓            | tsok   | 30         |      | 20         |      | ns   |                        |

| Data hold time after CLK ↓          | thkD   | 10         |      | 10         |      | ns   |                        |

| NMI, INT, POLL setup time to CLK 1  | tsıĸ   | 30         |      | 15         |      | ns   | ,                      |

| RESET setup time to CLK ↑           | tsrst  | 30         |      | 20         |      | ns   |                        |

| RESET hold time after CLK 1         | thrst  | 10         |      | 10         |      | ns   |                        |

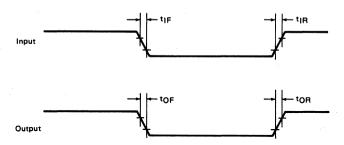

| Input rise time (except CLK)        | tir    |            | 20   |            | 20   | ns   | 0.8V to 2.2V           |

| Input fall time (except CLK)        | tıғ    |            | 12   |            | 12   | ns   | 2.2V to 0.8V           |

| Output rise time                    | tor    |            | 20   |            | 20   | ns   | 0.8V to 2.2V           |

| Output fall time                    | tor    |            | 12   |            | 12   | ns   | 2.2V to 0.8V           |

| Small Scale                         |        |            |      |            |      |      |                        |

| Address delay time from CLK         | tdka   | 10         | 90   | 10         | 60   | ns   |                        |

| Address hold time from CLK          | thka   | 10         |      | 10         |      | ns   |                        |

| PS delay time from CLK ↓            | tokp   | 10         | 90   | 10         | 60   | ns   |                        |

| PS float delay time from CLK ↑      | tFKP   | 10         | 80   | 10         | 60   | ns   |                        |

| Address setup time to ASTB ↓        | tsast  | tKKL-60    |      | tKKL-30    |      | ns   | 0 -100 -5              |

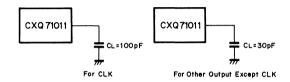

| Address float delay time from CLK ↓ | tfka   | thka       | 80   | thka       | 60   | ns   | C <sub>L</sub> =100 pF |

| ASTB ↑ delay time from CLK ↓        | toksth |            | 80   |            | 50   | ns   |                        |

| ASTB ↓ delay time from CLK ↑        | tokstl |            | 85   |            | 55   | ns   |                        |

| ASTB width high                     | tstst  | tkkl-20    |      | tkkl-10    |      | ns   |                        |

| Address hold time from ASTB ↓       | thsta  | tккн-10    |      | tkkl-10    |      | ns   |                        |

| Parameter                           | Symbol | CXQ701   | 08-5 | CXQ70108-8 |      | Unit | Test                   |

|-------------------------------------|--------|----------|------|------------|------|------|------------------------|

| Farameter                           | Symbol | Min.     | Max. | Min.       | Max. | Unit | Conditions             |

| Control delay time from CLK         | tokct  | 10       | 110  | 10         | 65   | ns   |                        |

| Address float to RD ↓               | tafrl  | 0        |      | 0          |      | ns   |                        |

| RD ↓ delay time from CLK ↓          | tokal  | 10       | 165  | 10         | 80   | ns   |                        |

| RD ↑ delay time from CLK ↓          | tokrh  | 10       | 150  | 10         | 80   | ns   |                        |

| Address delay time from RD ↑        | tdrha  | tcyk-45  |      | tcyk-40    |      | ns   |                        |

| RD width low                        | trr    | 2tcyk-75 |      | 2tcyk-50   |      | ns   | $C_L=100 pF$           |

| Data output delay time from CLK     | toko   | 10       | 90   | 10         | 60   | ns   |                        |

| Data float delay time from CLK ↓    | tFKD   | 10       | 80   | 10         | 60   | ns   |                        |

| WR width low                        | tww    | 2tcyk-60 |      | 2tcyk-40   |      | ns   |                        |

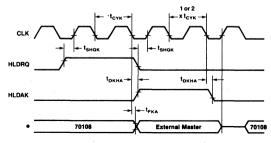

| HLDRQ setup time to CLK 1           | tsнок  | 35       |      | 20         |      | ns   |                        |

| HLDAK delay time from CLK ↓         | tokha  | 10       | 160  | 10         | 100  | ns   |                        |

| Large Scale                         |        |          |      |            |      |      |                        |

| Address delay time from CLK         | toka   | 10       | 90   | 10         | 60   | ns   |                        |

| Address hold time from CLK          | thka   | 10       |      | 10         |      | ns   |                        |

| PS delay time from CLK ↓            | tokp   | 10       | 90   | 10         | 60   | ns   |                        |

| PS float delay time from CLK 1      | tfkp   | 10       | 80   | 10         | 60   | ns   |                        |

| Address float delay time from CLK ↓ | tfka   | thka     | 80   | thka       | 60   | ns   |                        |

| Address delay time from RD ↑        | torha  | tcyk-45  |      | tcyk-40    |      | ns   |                        |

| ASTB ↑ delay time from BS ↓         | tobst  |          | 15   |            | 15   | ns   |                        |

| BS ↓ delay time from CLK ↑          | tokbl  | 10       | 110  | 10         | 60   | ns   |                        |

| BS ↑ delay time from CLK ↓          | tokbh  | 10       | 130  | 10         | 65   | ns   | 0100 5                 |

| RD ↓ delay time from address float  | tDAFRL | 0        |      | 0          |      | ns   | C <sub>L</sub> =100 pF |

| RD ↓ delay time from CLK ↓          | tokrl  | 10       | 165  | 10         | 80   | ns   |                        |

| RD ↑ delay time from CLK ↓          | tokrh  | 10       | 150  | 10         | 80   | ns   |                        |

| RD width low                        | trr    | 2tcYK-75 |      | 2tcyk-50   |      | ns   |                        |

| Data output delay time from CLK ↓   | toko   | 10       | 90   | 10         | 60   | ns   |                        |

| Data float delay time from CLK ↓    | trkd   | 10       | 80   | 10         | 60   | ns   |                        |

| AK delay time from CLK ↓            | tokak  |          | 70   |            | 50   | ns   |                        |

| RQ setup time to CLK 1              | tsrok  | 20       |      | 10         |      | ns   |                        |

| RQ hold time after CLK 1            | thkra  | 40       |      | 30         |      | ns   |                        |

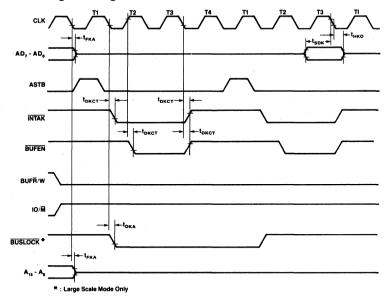

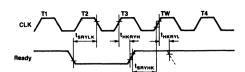

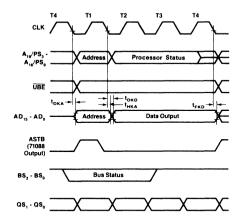

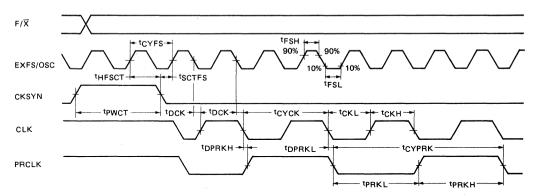

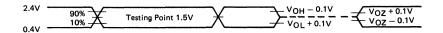

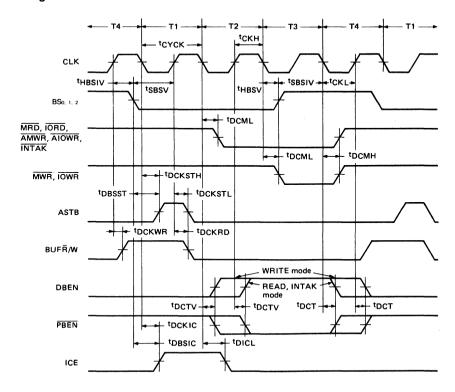

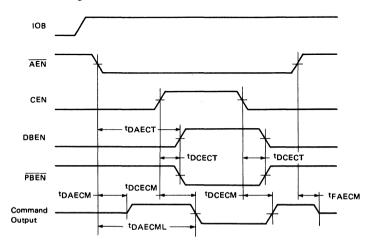

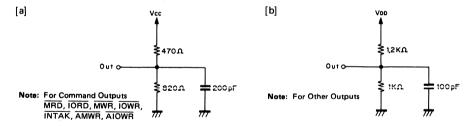

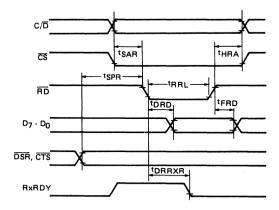

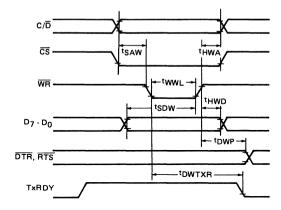

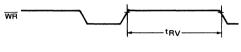

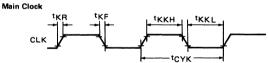

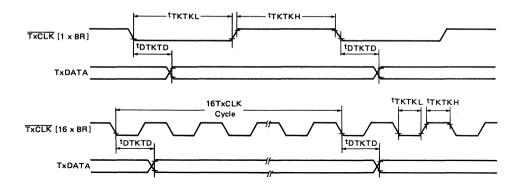

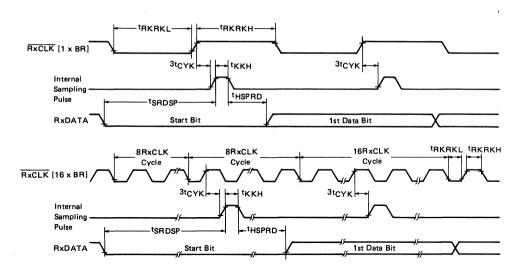

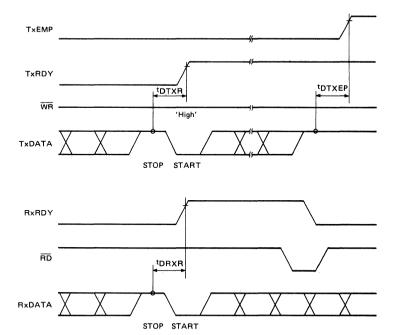

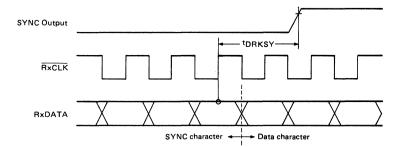

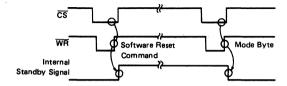

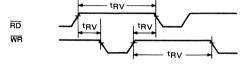

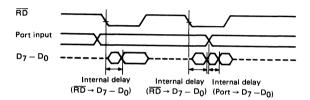

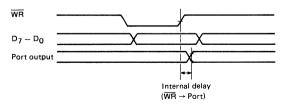

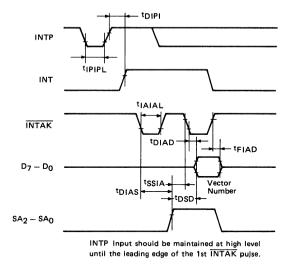

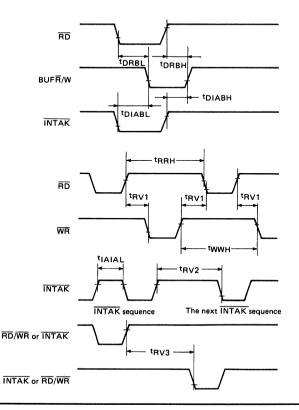

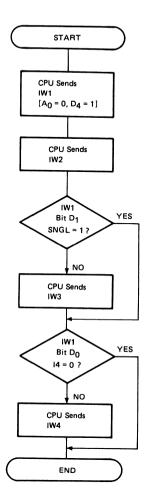

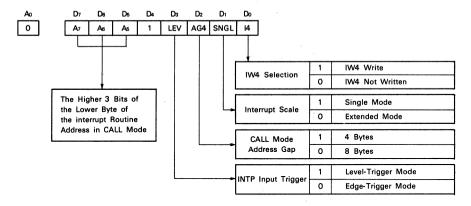

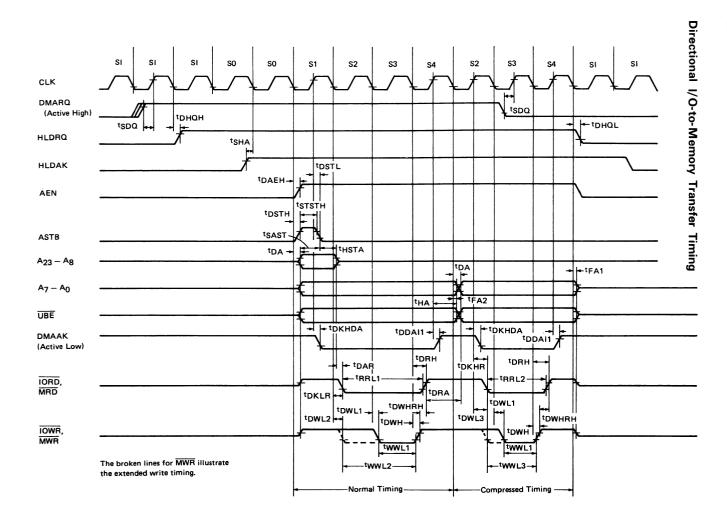

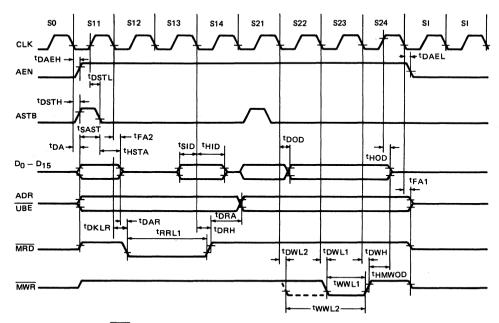

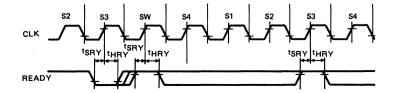

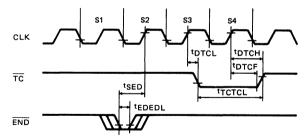

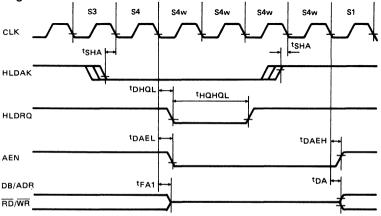

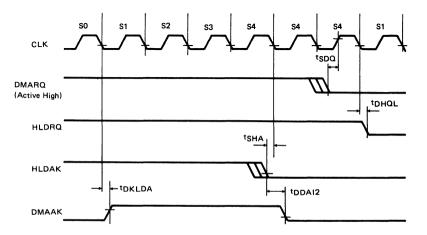

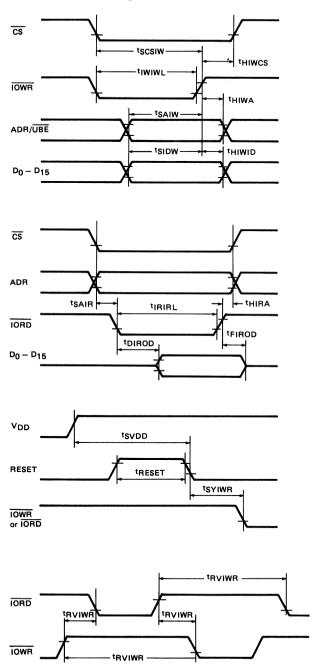

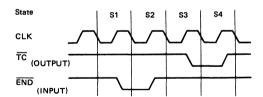

## Timing Waveforms

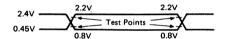

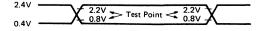

# AC Test input Waveform [Except CLK]

### **AC Output Test Points**

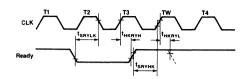

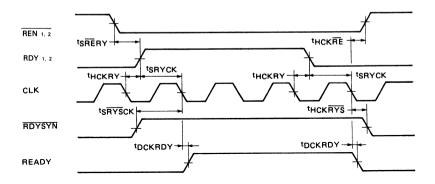

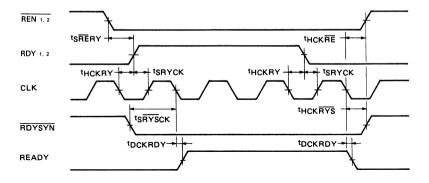

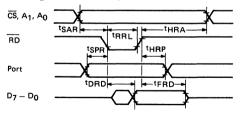

### Wait [Ready] Timing

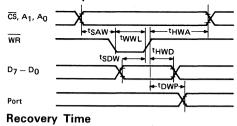

# POLL, NMI, INT Input Timing

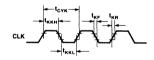

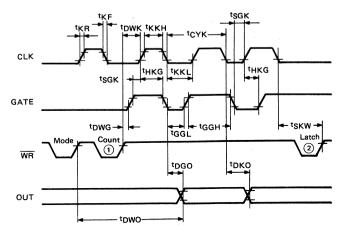

## **Clock Timing**

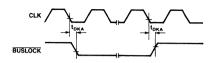

# **BUSLOCK** Output Timing

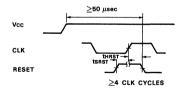

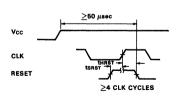

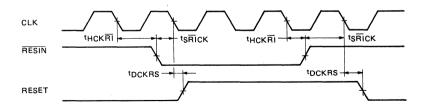

### **RESET Timing**

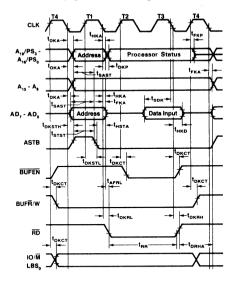

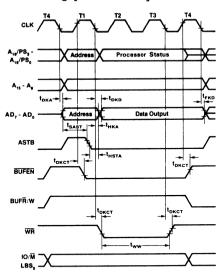

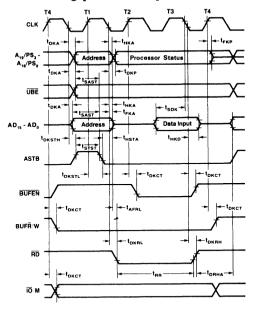

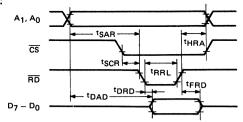

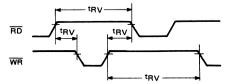

## Read Timing [Small Scale]

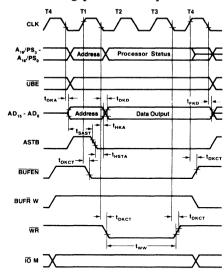

### Write Timing [Small Scale]

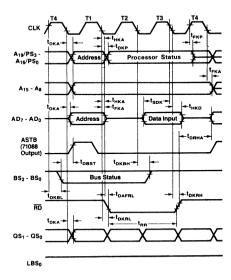

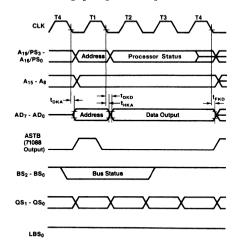

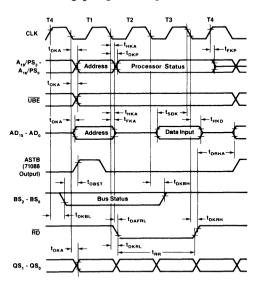

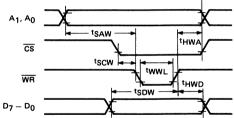

### Read Timing [Large Scale]

### Write Timing [Large Scale]

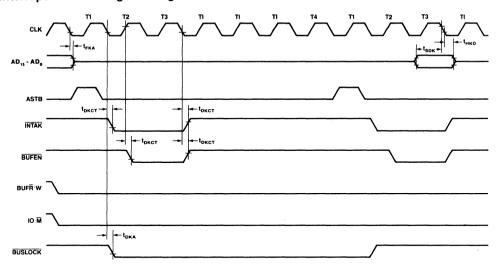

## Interrupt Acknowledge Timing

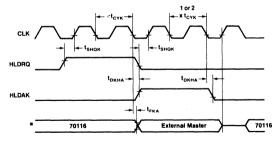

# Hold Request/Acknowledge Timing [Small Scale]

\* : A,,/PS, - A,,/PS, A,, - A, AD, - AD, RD, LBS, IO/M, BUFR/W, WR, BUFEN

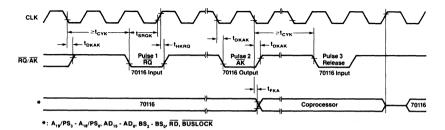

# Bus Request/Acknowledge Timing [Large Scale]

<sup>\* :</sup> A,,/PS, - A,e/PS, A,, - A, AD, - AD, BS, - BS, RD, BUSLOCK

## **Register Configuration**

## Program Counter [PC]

The program counter is a 16-bit binary counter that contains the segment offset address of the next instruction which the EXU is to execute.

The PC increments each time the microprogram fetches an instruction from the instruction queue. A new location value is loaded into the PC each time a branch, call, return, or break instruction is executed. At this time, the contents of the PC are the same as the Prefetch Pointer (PEP)

## Prefetch Pointer [PFP]

The prefetch pointer (PFP) is 16-bit binary counter which contains a segment offset which is used to calculate a program memory address that the bus control unit (BCU) uses to prefetch the next byte for the instruction queue. The contents of PFP are an offset from the PS (Program Segment) register.

The PFP is incremented each time the BCU prefetches an instruction from the program memory. A new location will be loaded into the PFP whenever a branch, call, return, or break instruction is executed. At that time the contents of the PFP will be the same as those of the PC (Program Counter).

## Segment Registers [PS. SS. DSo. and DS1]

The memory addresses accessed by the CXQ70108 are divided into 64K-byte logical segments. The starting (base) address of each segment is specified by a segment register, and the offset from this starting address is specified by the contents of another register or by the effective address.

These are the four types of segment registers used.

| Segment Register                 | Default Offset        |  |  |

|----------------------------------|-----------------------|--|--|

| PS (Program Segment)             | PFP                   |  |  |

| SS (Stack Segment)               | SP, effective address |  |  |

| DS <sub>0</sub> (Data Segment 0) | IX, effective address |  |  |

| DS <sub>1</sub> (Data Segment 1) | IY                    |  |  |

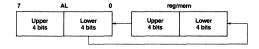

#### General-Purpose Registers [AW, BW, CW, and DW]

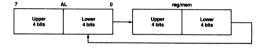

There are four 16-bit general-purpose registers. Each one can be used as one 16-bit register or as two 8-bit registers by dividing them into their high and low bytes (AH, AL, BH, BL, CH, CL, DH, DL).

Each register is also used as a default register for processing specific instructions. The default assignments are:

AW: Word multiplication/division, word I/O, BCD rotation, data conversion, translation

AL: Byte multiplication/division, byte I/O, BCD rotation, data conversion, translation

AH: Byte multiplication/division

BW: Translation

CW: Loop control branch, repeat prefix

CL: Shift instructions, rotation instructions, BCD operations

DW: Word multiplication/division, indirect addressing I/O

## Pointers [SP, BP] and index Registers [IX, IY]

These registers serve as base pointers or index registers when accessing the memory using based addressing, indexed addressing, or based indexed addressing.

These registers can also be used for data transfer and arithmetic and logical operations in the same manner as the general-purpose registers. They cannot be used as 8-bit registers.

Also, each of these registers acts as a default register for specific operations. The default assignments are:

SP: Stack operations

IX: Block transfer (source), BCD string operations

IY: Block transfer (destination), BCD string operations

## Program Status Word [PSW]

The program status word consists of the following six status and four control flags.

Status Flags

Control Flags

- V (Overflow)

- MD (Mode)

- S (Sign)

- . DIR (Direction)

- · Z (Zero)

- IE (Interrupt Enable)

- AC (Auxiliary Carry)

- BRK (Break)

- P (Parity)

- CY (Carry)

When the PSW is pushed on the stack, the word images of the various flags are as shown here.

#### **PSW**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| М  | 1  | 1  | 1  | ٧  | D  | ı | В | s | Z | 0 | Α | 0 | Р | 1 | C |

| D  |    |    |    |    | 1  | Ε | R |   |   |   | С |   |   |   | Υ |

|    |    |    |    |    | R  |   | Κ |   |   |   |   |   |   |   |   |

The status flags are set and reset depending upon the result of each type of instruction executed. Instructions are provided to set, reset, and complement the CY flag directly.

Other instructions set and reset the control flags and control the operation of the CPU.

## **High-Speed Execution of Instructions**

This section highlights the major architectural features that enhance the performance of the CXQ70108.

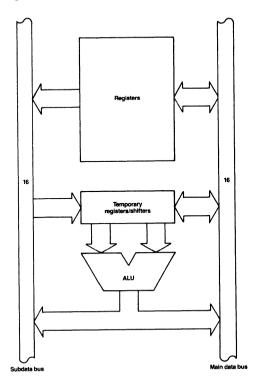

- · Dual data bus in EXU

- · Effective address generator

- 16/32-bit temporary registers/shifters (TA, TB)

- 16-bit loop counter

- PC and PFP

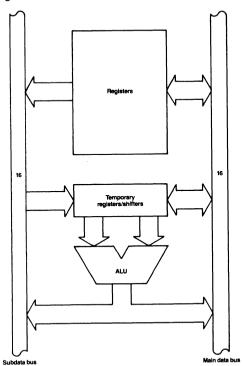

#### **Dual Data Bus Method**

To reduce the number of processing steps for instruction execution, the dual data bus method has been adopted for the CXQ70108 (figure 1). The two data buses (the main data bus and the subdata bus) are both 16 bits wide. For addition/subtraction and logical and comparison operations, processing time has been speeded up some 30% over single-bus systems.

Fig. 1. Dual Data Buses

Fig. 2. Effective Address Generator

#### Example

ADD AW, BW ;AW  $\leftarrow$  AW + BW Step 1 TA  $\leftarrow$  AW TA  $\leftarrow$  BW AW  $\leftarrow$  TA  $\leftarrow$  TB Step 3 AW  $\leftarrow$  TA  $\leftarrow$  TB

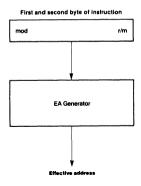

## Effective address Generator

This circuit (figure 2) performs high-speed processing to calculate effective addresses for accessing memory.

Calculating an effective address by the microprogramming method normally requires 5 to 12 clock cycles. This circuit requires only two clock cycles for addresses to be generated for any addressing mode. Thus, processing is several times faster.

## 16/32-Bit Temporary Registers/Shifters [TA, TB]

These 16-bit temporary registers/shifters (TA, TB) are provided for multiplication/division and shift/rotation instructions.

These circuits have decreased the execution time of multiplication/division instructions. In fact, these instructions can be executed about four times faster than with the microprogramming method.

TA + TB: 32-bit temporary register/shifter for multiplication and division instructions.

TB: 16-bit temporary register/shiffter for shift/rotation instructions.

## Loop Counter [LC]

This counter is used to count the number of loops for a primitive block transfer instruction controlled by a repeat prefix instruction and the number of shifts that will be performed for a multiple bit shift/rotation instruction.

The processing performed for a multiple bit rotation of a register is shown below. The average speed is approximately doubled over the microprogram method.

## Example

RORC AW, CL ; CL = 5

Microprogram method

LC method

$8 + (4 \times 5) = 28$  clocks

7 + 5 = 12 clocks

## Program Counter and Prefetch Pointer [PC and PFP]

The CXQ70108 microprocessor has a program counter (PC), which addresses the program memory location of the instruction to be executed next, and a prefetch pointer (PFP), which addresses the program memory location to be accessed next. Both functions are provided in hardware. A time saving of several clocks is realized for branch, call, return, and break instruction execution, compared with microprocessors that have only one instruction pointer.

#### **Enhanced Instructions**

In addition to the 8088/86 instructions, the CXQ70108 has the following enhanced instructions.

| Instruction                                                       | Function                                                                  |

|-------------------------------------------------------------------|---------------------------------------------------------------------------|

| PUSH imm                                                          | Pushes immediate data onto stack                                          |

| PUSH R                                                            | Pushes 8 general registers onto stack                                     |

| POP imm                                                           | Pops immediate data from stack                                            |

| POP R                                                             | Pops 8 general registers from stack                                       |

| MUL imm                                                           | Executes 16-bit multiply of register or memory contents by immediate data |

| SHL imm8 SHR imm8 SHRA imm8 ROL imm8 ROR imm8 ROLC imm8 RORC imm8 | Shifts/rotates register or memory by immediate value                      |

| CHKIND                                                            | Checks array index against designated boundaries                          |

| INM                                                               | Moves a string from an I/O port to memory                                 |

| OUTM                                                              | Moves a string from memory to an I/O port                                 |

| PREPARE                                                           | Allocates an area for a stack frame and copies previous frame pointers    |

| DISPOSE                                                           | Frees the current stack frame on a procedure exit                         |

## **Enhanced Stack Operation Instructions**

#### PUSH imm/POP imm

These instructions allow immediate data to be pushed onto or popped from the stack.

#### PUSH R/POP R

These instructions allow the contents of the eight general registers to be pushed onto or popped from the stack with a single instruction.

#### **Enhanced Multiplication Instructions**

## MUL rea16, imm16/MUL mem16, imm16

These instructions allow the contents of a register or memory location to be 16-bit multiplied by immediate data

#### Enhanced Shift and Rotate Instructions

## SHL reg, imm8/SHR reg, imm8/SHRA reg, imm8

These instructions allow the contents of a register to be shifted by the number of bits defined by the immediate data.

#### ROL rea, imm8/ROR rea, imm8/ROLC rea, imm8/RORC rea, imm8

These instructions allow the contents of a register to be rotated by the number of bits defined by the immediate data.

## **Check Array Boundary Instruction**

#### CHKIND reg16, mem32

This instruction is used to verify that index values pointing to the elements of an array data structure are within the defined range. The lower limit of the array should be in memory location mem32, the upper limit in mem32  $\pm$  2. If the index value in reg16 is not between these limits when CHKIND is executed, a BRK 5 will occur. This causes a jump to the location in interrupt vector 5.

#### **Block I/O Instructions**

## OUTM DW, src-block/INM dst-block, DW

These instructions are used to output or input a string to or from memory, when preceded by a repeat prefix.

#### Stack Frame Instructions

#### PREPARE imm16, imm8

This instruction is used to generate the stack frames required by block-structured languages, such as PASCAL and Ada. The stack frame consists of two areas. One area has a pointer that points to another frame which has variables that the current frame can access. The other is a local variable area for the current procedure.

#### DISPOSE

This instruction releases the last stack frame generated by the PREPARE instruction. It returns the stack and base pointers to the values they had before the PREPARE instruction was used to call a procedure.

## Unique Instructions

In addition to the 8088/86 instructions and the enhanced instructions, the CXQ70108 has the following unique instructions.

| Instruction | Function                                            |  |  |

|-------------|-----------------------------------------------------|--|--|

| INS         | Insert bit field                                    |  |  |

| EXT         | Extract bit field                                   |  |  |

| ADD4S       | Adds packed decimal strings                         |  |  |

| SUB4S       | Subtracts one packed decimal string from another    |  |  |

| CMP4S       | Compares two packed decimal strings                 |  |  |

| ROL4        | Rotates one BCD digit left through AL lower 4 bits  |  |  |

| ROR4        | Rotates one BCD digit right through AL lower 4 bits |  |  |

| TEST1       | Tests a specified bit and sets/resets Z flag        |  |  |

| NOT1        | Inverts a specified bit                             |  |  |

| CLR1        | Clears a specified bit                              |  |  |

| SET1        | Sets a specified bit                                |  |  |

| REPC        | Repeats next instruction until CY flag is cleared   |  |  |

| REPNC       | Repeats next instruction until CY flag is set       |  |  |

| FPO2        | Additional floating point processor call            |  |  |

#### Variable Length Bit Field Operation Instructions

This category has two instructions: INS (Insert Bit Field) and EXT (Extract Bit Field). These instructions are highly effective for computer graphics and high-level languages. They can, for example, be used for data structures such as packed arrays and record type data used in PASCAL.

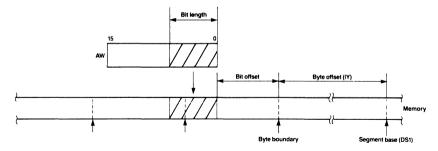

#### INS reg8, reg8/INS reg8, imm4

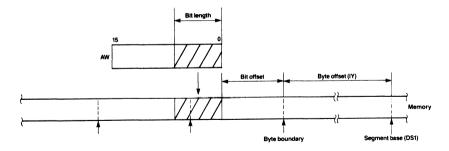

This instruction (figure 3) transfers low bits from the 16-bit AW register (the number of bits is specified by the second operand) to the memory location specified by the segment base (DS1 register) plus the byte offset (IY register). The starting bit position within this byte is specified as an offset by the lower 4-bits of the first operand.

After each complete data transfer, the IY register and the register specified by the first operand are automatically updated to point to the next bit field.

Either immediate data or a register may specify the number of bits transferred (second operand). Because the maximum transferable bit length is 16-bits, only the lower 4-bits of the specified register (00H to 0FH) will be valid.

Bit field data may overlap the byte boundary of memory.

Fig. 3. Bit Field Insertion

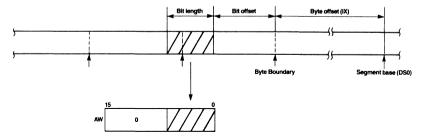

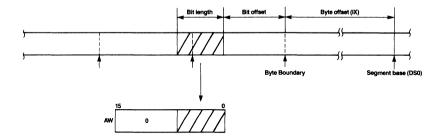

## EXT reg8, reg8/EXT reg8, imm4

This instruction (figure 4) loads to the AW register the bit field data whose bit length is specified by the second operand of the instruction from the memory location that is specified by the DSo segment register (segment base), the IX index register (byte offset), and the lower 4-bits of the first operand (bit offset).

After the transfer is complete, the IX register and the lower 4-bits of the first operand are automatically updated to point to the next bit field.

Either immediate data or a register may be specified for the second operand. Because the maximum transferrable bit length is 16 bits, however, only the lower 4-bits of the specified register (OH to OFH) will be valid.

Bit field data may overlap the byte boundary of memory.

Fig. 4. Bit Field Extraction

## Packed BCD Operation Instructions

The instructions described here process packed BCD data either as strings (ADD4S, SUB4S, CMP4S) or byte-format operands (ROR4, ROL4). Packed BCD strings may be from 1 to 255 digits in length.

When the number of digits is even, the zero and carry flags will be set according to the result of the operation. When the number of digits is odd, the zero and carry flags may not be set correctly in this case, (CL = odd), the zero flag will not be set unless the upper 4 bits of the highest byte are all zero. The carry flag will not be set unless there is a carry out of the upper 4 bits of the highest byte. When CL is odd, the contents of the upper 4 bits of the highest byte of the result are undefined.

#### ADD4S

This instruction adds the packed BCD string addressed by the IX index register to the packed BCD string addressed by the IY index register, and stores the result in the string addressed by the IY register. The length of the string (number of BCD digits) is specified by the CL register, and the result of the operation will affect the carry flag (CY) and zero flag (Z).

BCD string (IY, CL) ← BCD string (IY, CL) + BCD string (IX, CL)

#### SUB4S

This instruction subtracts the packed BCD string addressed by the IX index register from the packed BCD string addressed by the IY index register, and stores the result in the string addressed by the IY register. The length of the string (number of BCD digits) is specified by the CL register, and the result of the operation will affect the carry flag (CY) and zero flag (Z).

BCD string (IY, CL) ← BCD string (IY, CL) - BDC String (IX, CL)

#### CMP4S

This instruction performs the same operation as SUB4S except that the result is not stored and only carry flags (CY) and zero flag (Z) are affected.

BCD string (IY, CL) - BCD string (IX, CL)

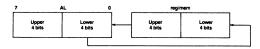

#### ROL4

This instruction (figure 5) treats the byte data of the register or memory directly specified by the instruction byte as BCD data and uses the lower 4-bits of the AL register (ALL) to rotate that data one BCD digit to the left.

## Fig. 5. BCD Rotate Left (ROL4)

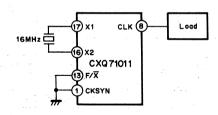

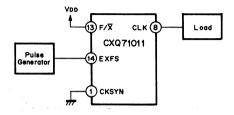

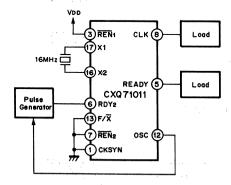

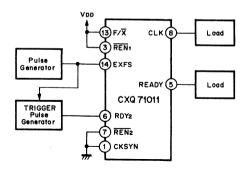

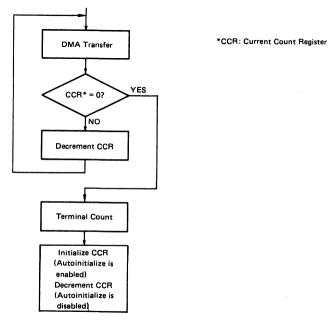

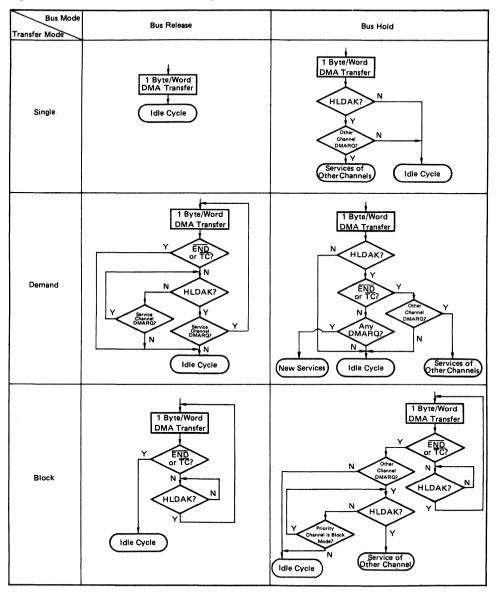

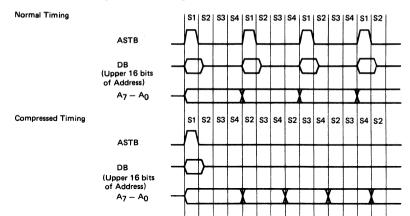

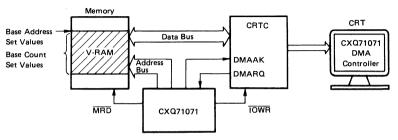

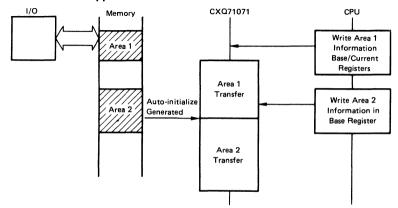

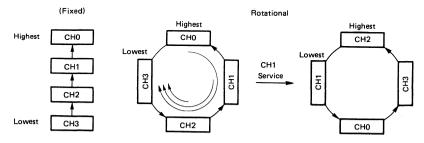

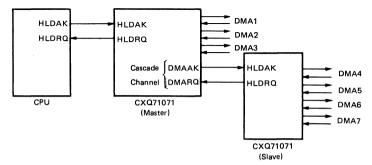

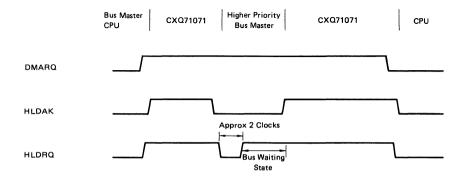

## ROR4