# LSI Logic Data Book

1986

1986

Bipolar and CMOS LSI/VLSI

General Information

LSI Devices

2

**Application Reports**

**Mechanical Data**

4

# LSI Logic Data Book

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

TI warrants performance of its semiconductor products, including SNJ and SMJ devices, to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Specifications contained in this data book supersede all data for these products published by TI in the United States before November 1985.

ISBN 0-89512-197-2

Copyright © 1986, Texas Instruments Incorporated

#### INTRODUCTION

The LSI Logic Data Book presents pertinent technical information on Texas Instruments complex bipolar and CMOS LSI logic integrated circuits. The bipolar LSI products described in this volume include:

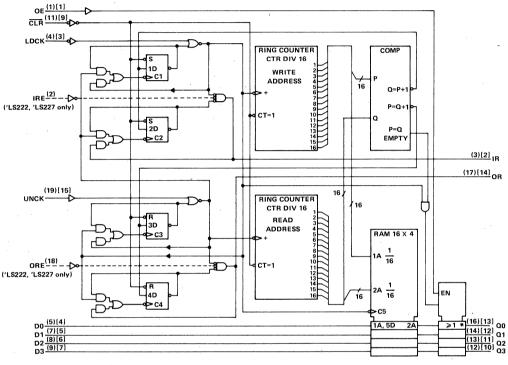

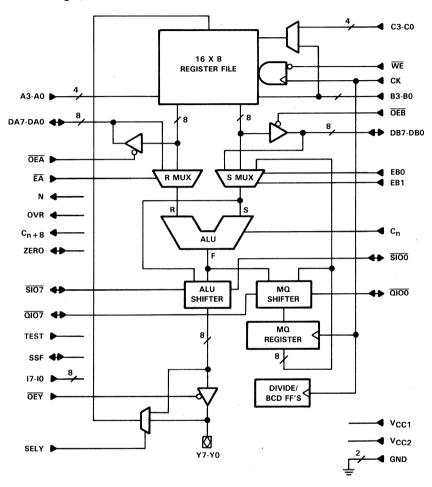

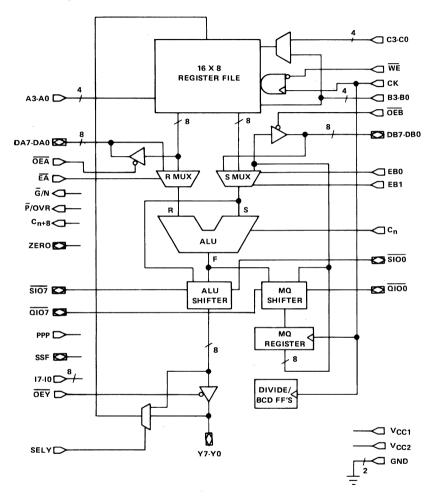

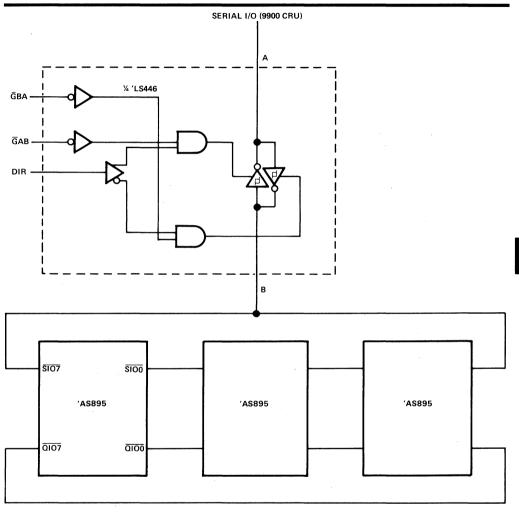

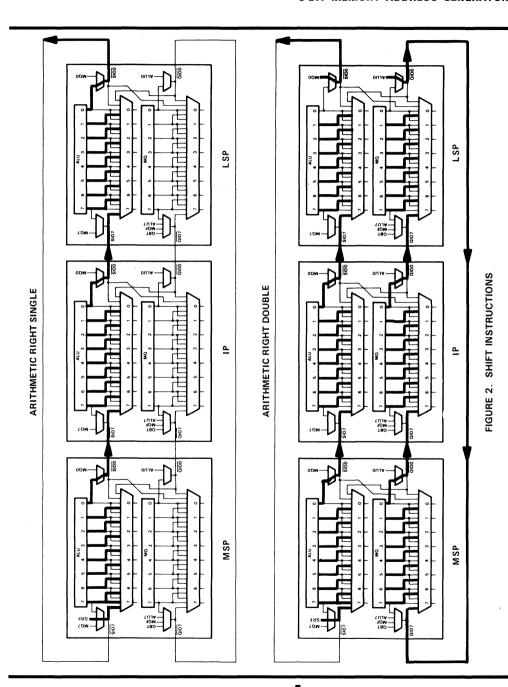

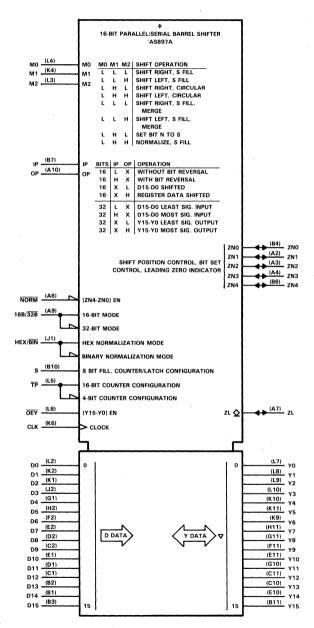

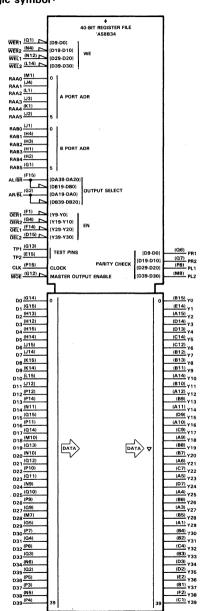

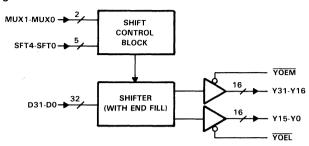

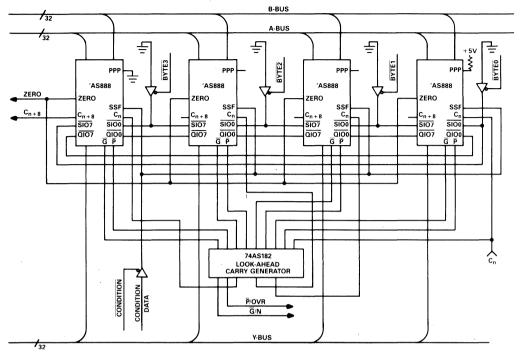

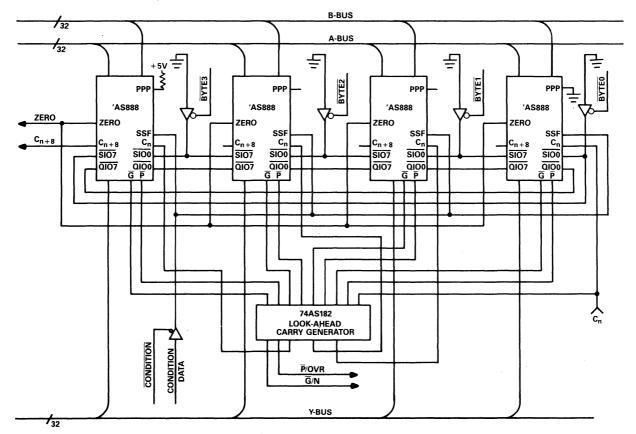

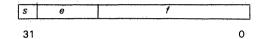

- The fastest TTL-compatible 8-bit processor slice chip set available. The chip set includes an 8-bit registered ALU, a 14-bit microsequencer, a 16- and 32-bit expandable barrel shifter, and a 16-word by 4-bit register file.

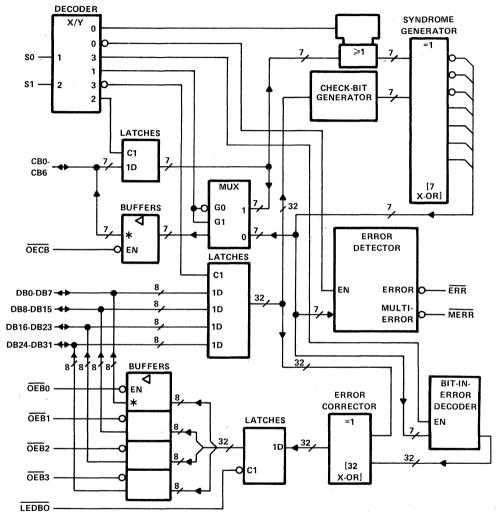

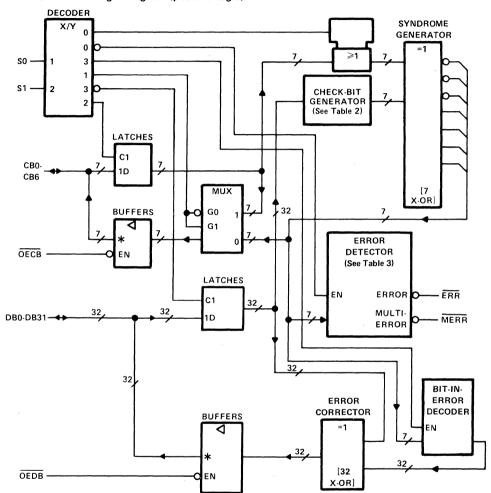

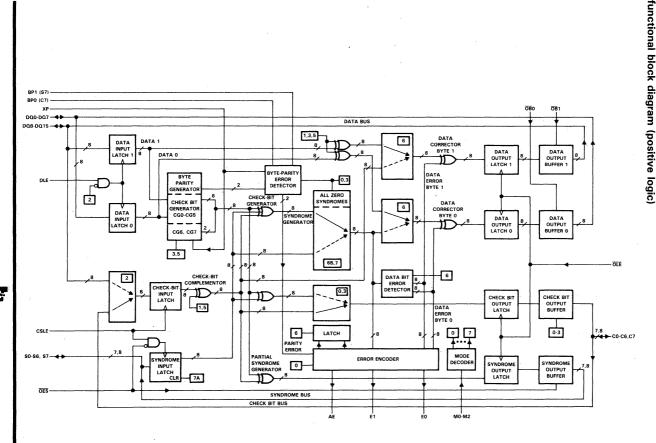

- The fastest stand-alone 32-bit error detection and correction circuit (EDAC)

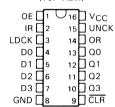

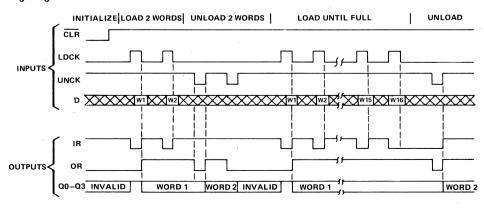

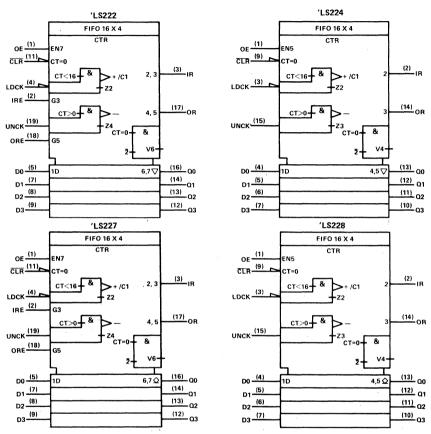

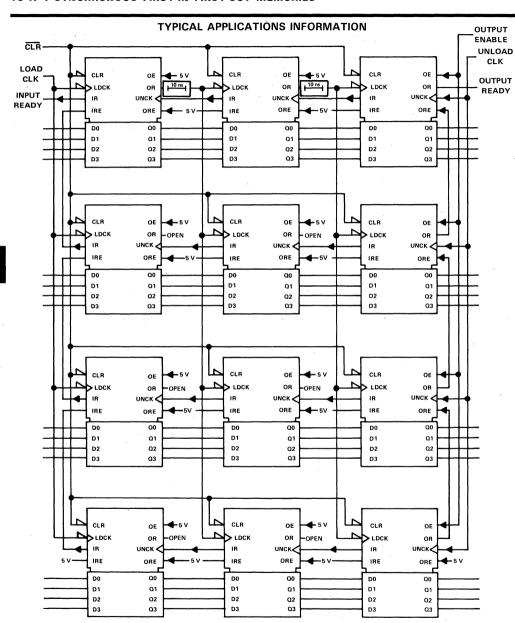

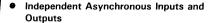

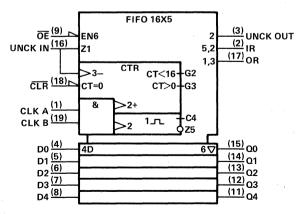

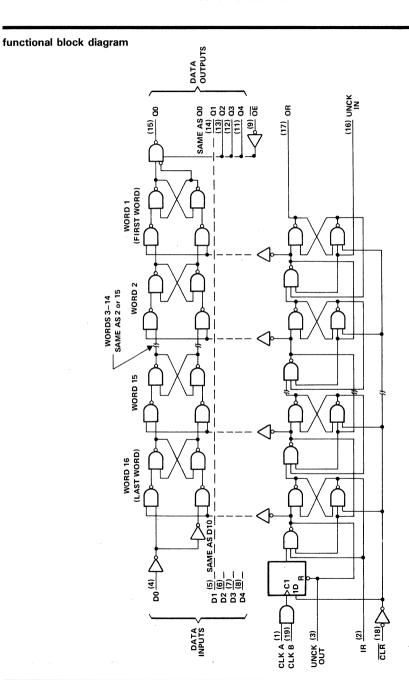

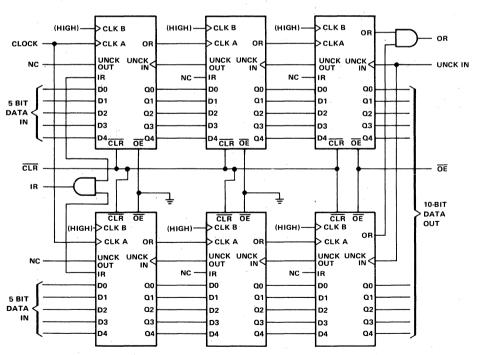

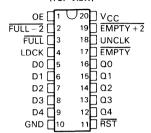

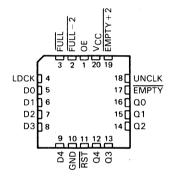

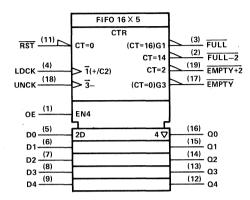

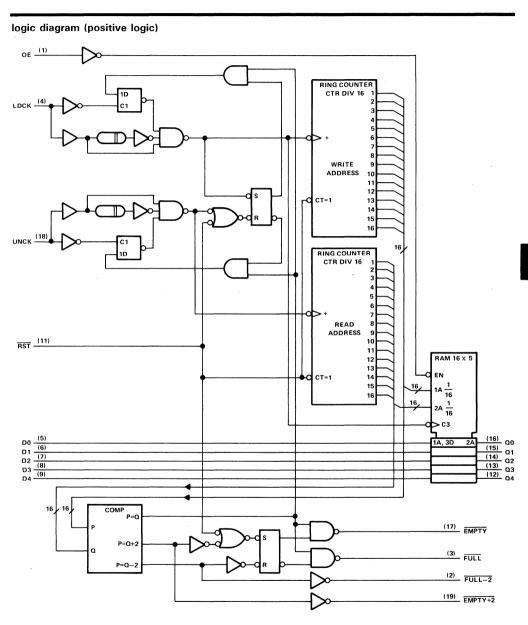

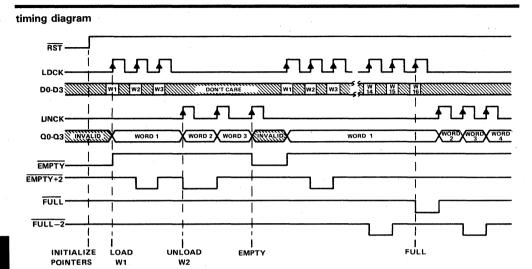

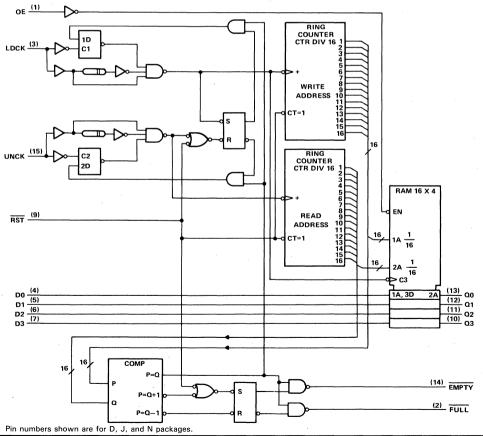

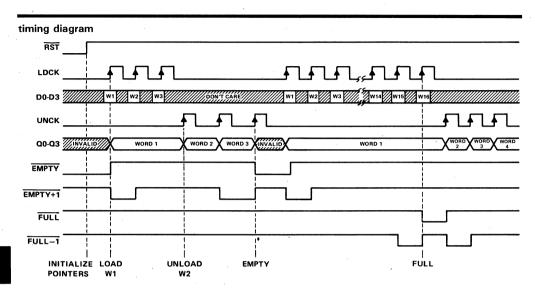

- High-performance 16 × 4 and 16 × 5 "zero-fall-through" FIFOs (first in, first out) memory devices with 24-nanosecond fall-through times

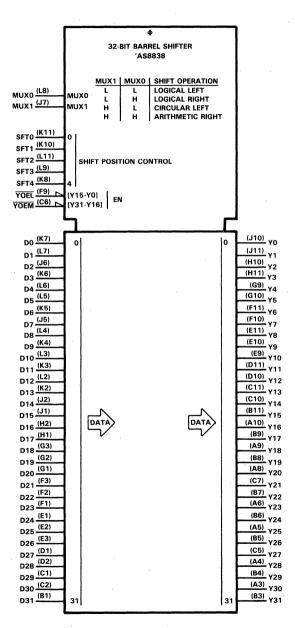

- A high-speed "flash" 32-bit barrel shifter (SN74AS8838). The SN74AS8838 is the first member of the Texas Instruments 32-bit processor chip set.

Specifications on CMOS LSI products included in this volume describe the following:

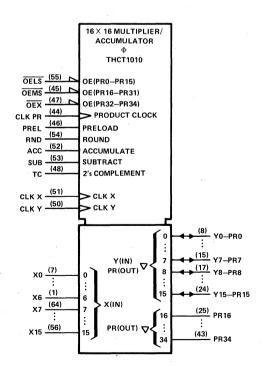

- The THCT1010, which is the lowest power 16- × 16-bit multiplier and accumulator (MAC) available.

- Two 64K and 256K DRAM controllers with inputs that are TTL- and CMOS-voltage compatible.

- Two high-speed CMOS multilevel pipeline registers, which offer a reduction in power over previously available devices.

To assist you in the selection of complex MSI logic components to complement a system design, the LSI Logic Data Book contains specifications on high-performance bus transceivers, readback latches, comparators, and controllers.

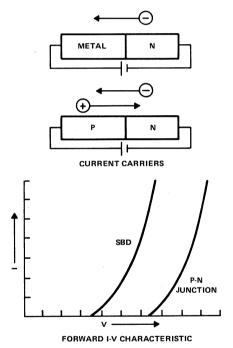

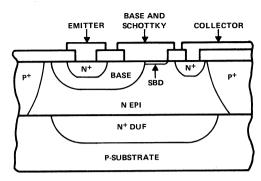

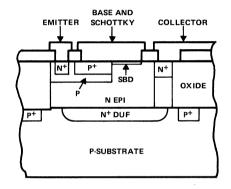

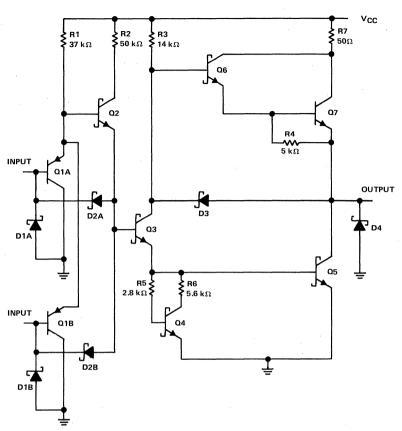

Many Texas Instruments leadership bipolar LSI functions use our new advanced bipolar technology, IMPACT™ (IMPlanted Advanced Composed Technology). This unique innovation offers performance advantages in speed, power, and circuit density over preceding bipolar technologies. The process offers such features as:

- 2-μm feature size

- 7-μm metal pitch

- Walled emitters

- Ion implantation

- Oxide isolation

- Composed masks

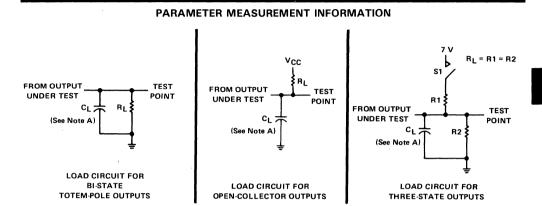

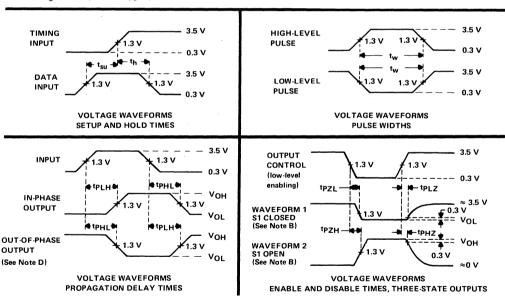

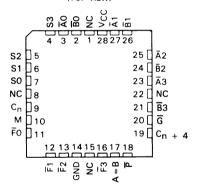

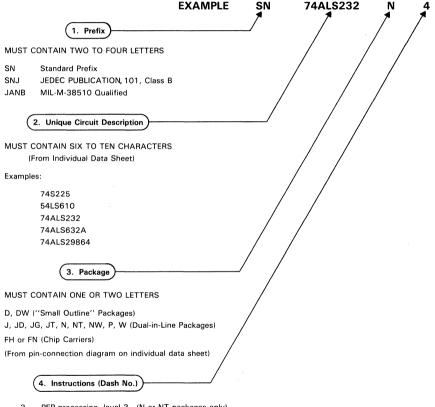

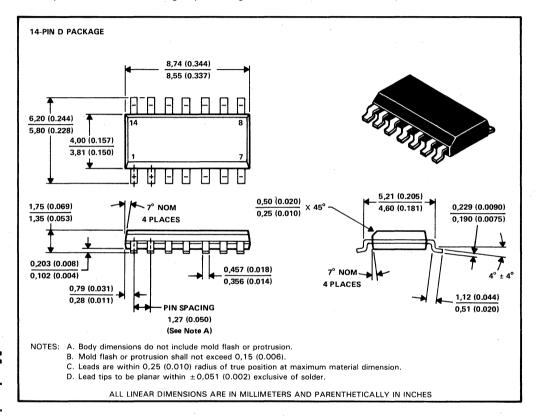

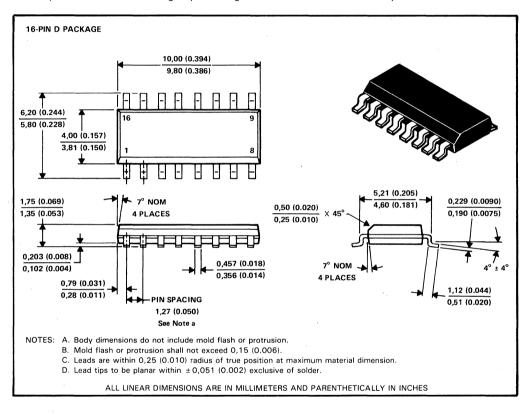

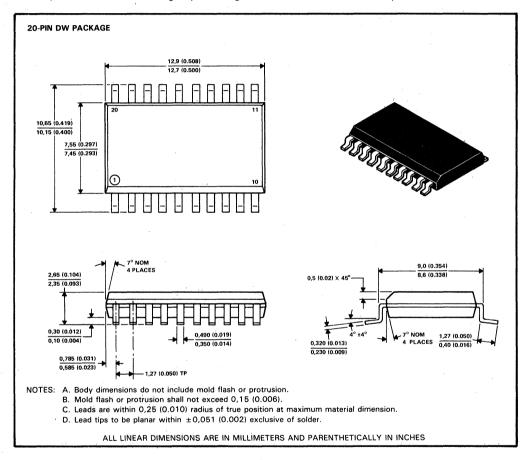

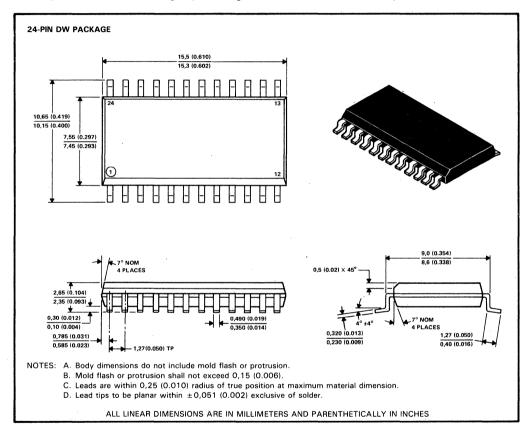

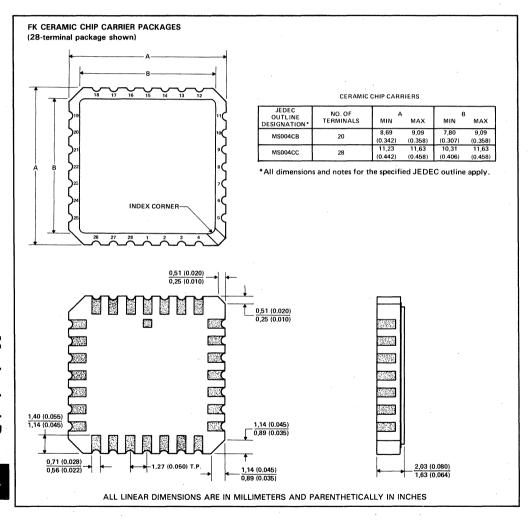

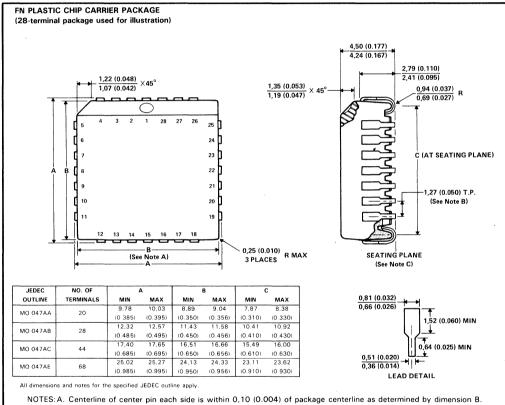

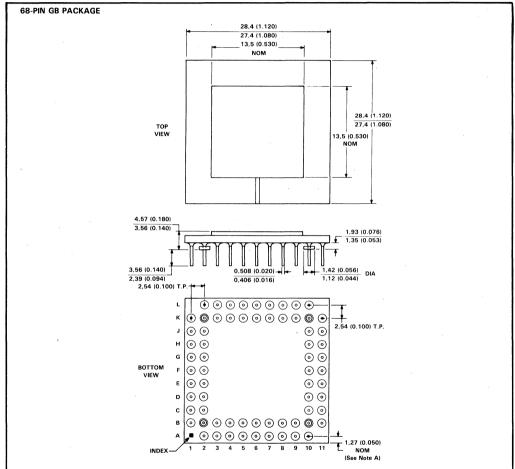

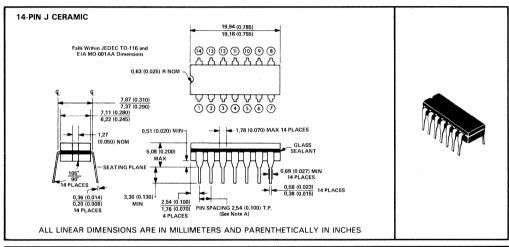

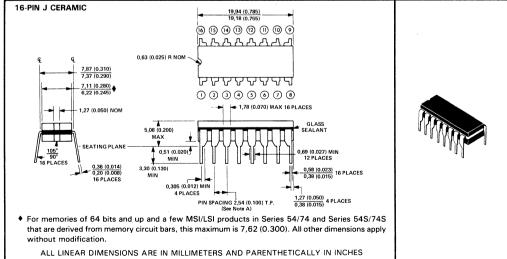

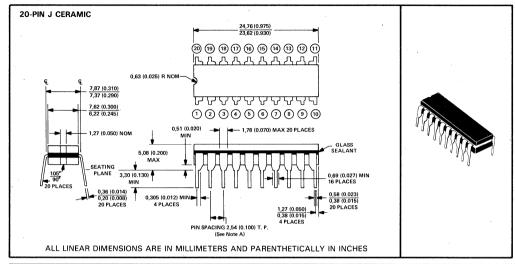

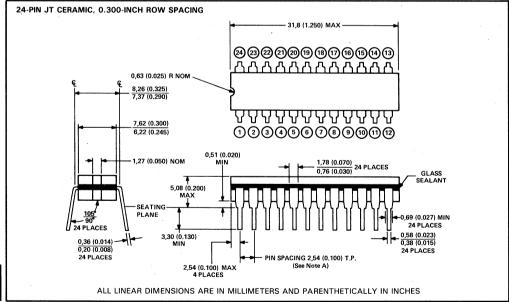

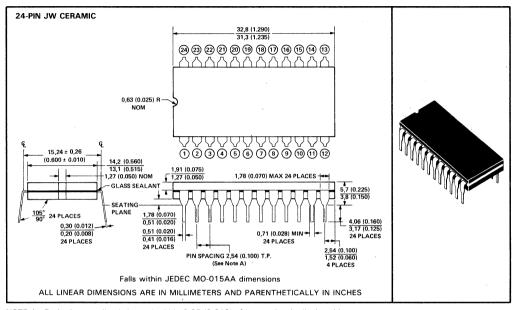

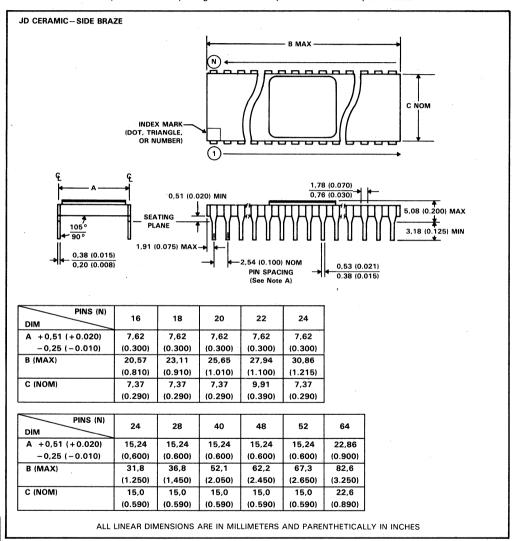

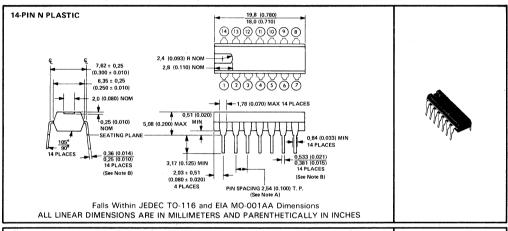

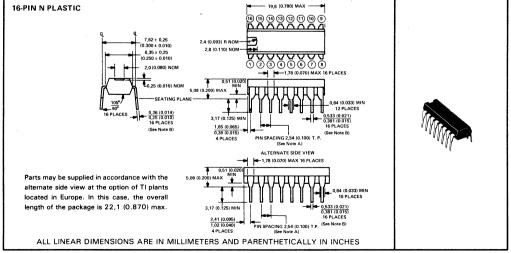

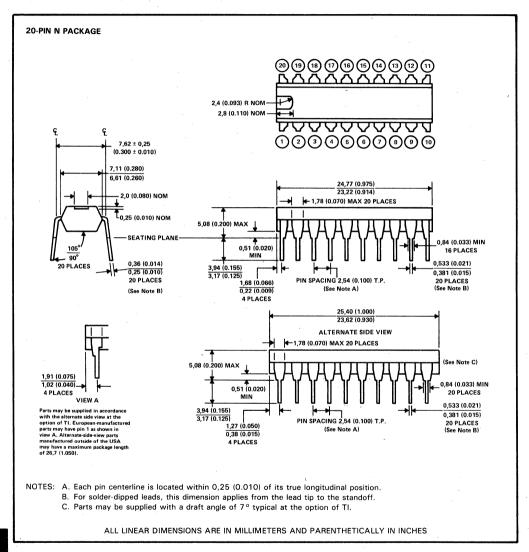

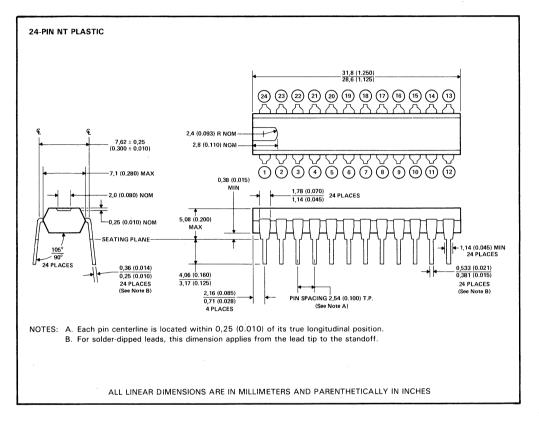

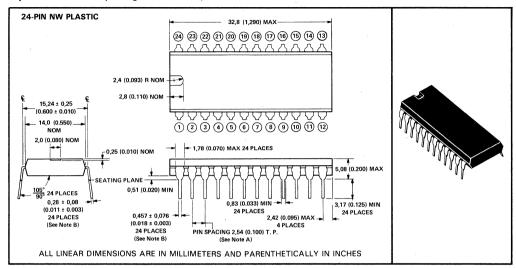

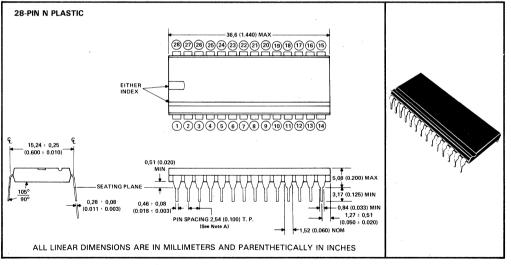

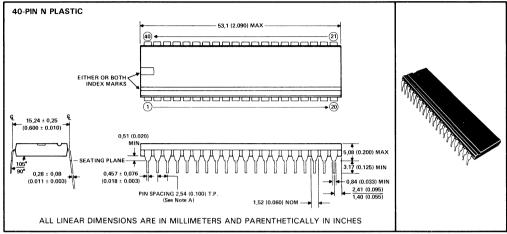

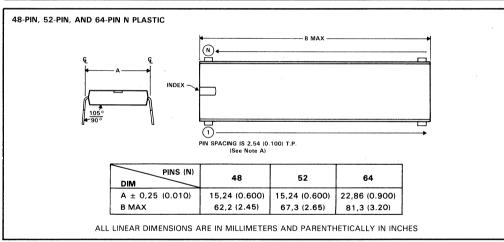

This data book provides a functional index to all bipolar digital device types available or under development. Packaging dimensions given in the Mechanical Data section of this book are in metric measurement (and parenthetically in inches), which should simplify board layout for designers involved in metric conversion and new designs. The general information section includes an explanation of the function tables, parameter measurement information, and typical characteristics related to the products listed in this volume.

Complete technical data for any Texas Instruments semiconductor/component product is available from your nearest TI field sales office, local authorized TI distributor, or by writing direct to:

Texas Instruments Incorporated P.O. Box 225012, MS 308 Dallas, Texas 75265

We sincerely believe that you will find the new LSI Logic Data Book a meaningful addition to your technical library.

vi

## **General Information**

Numerical Index Glossary Explanation of Function Tables Parameter Measurement Information Functional Index

## LSI Devices

2

# **Application Reports**

3

Advanced Schottky Family

Error Detection and Correction

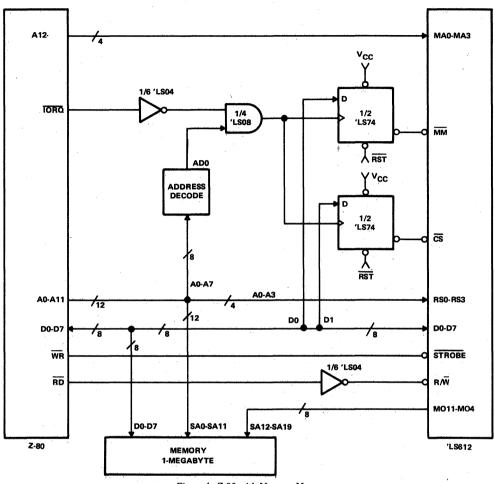

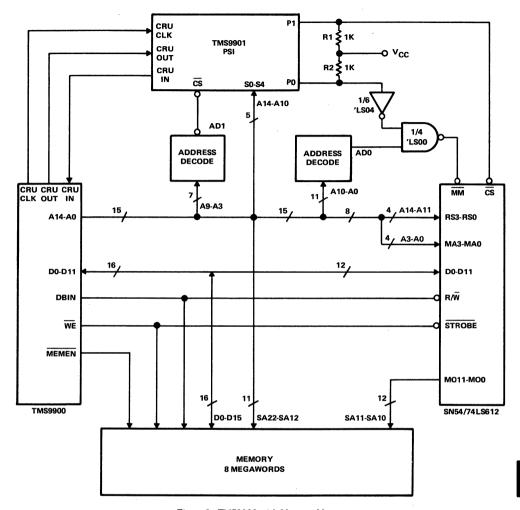

Memory Mapping

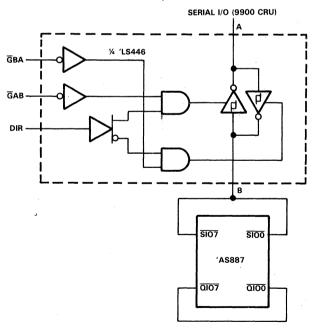

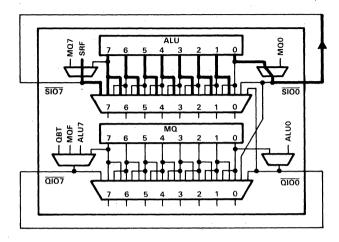

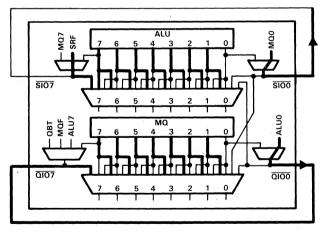

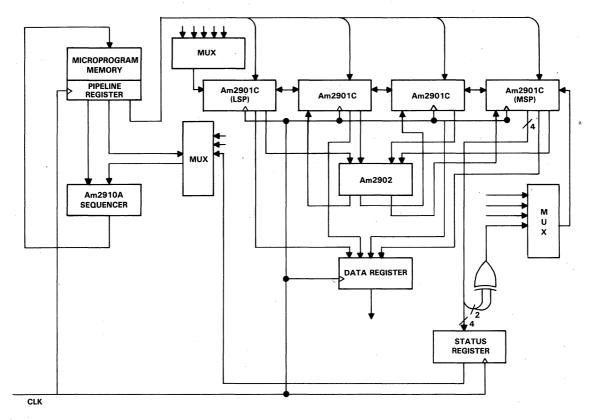

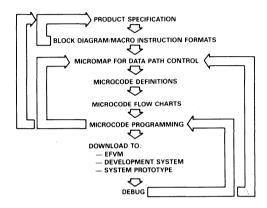

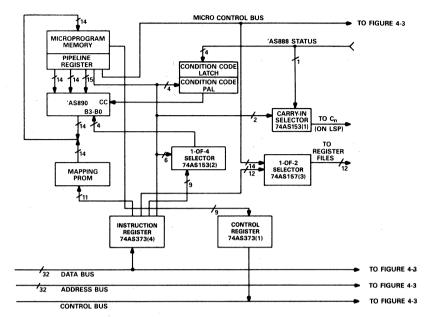

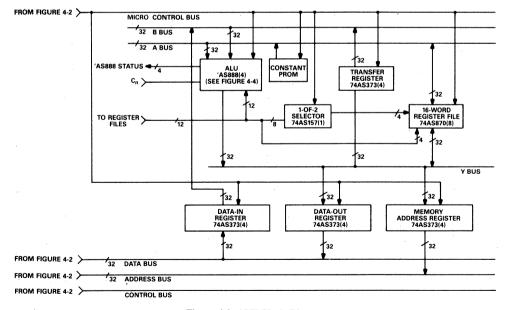

Bit-Slice Processor 8-Bit Family

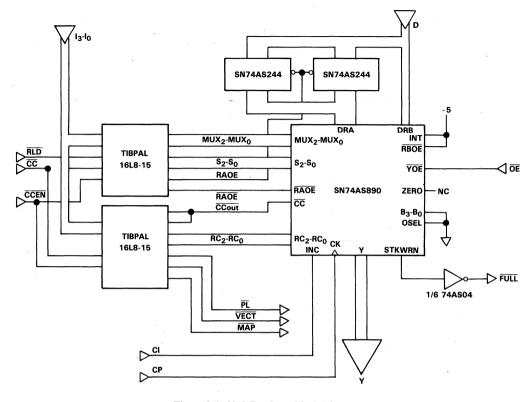

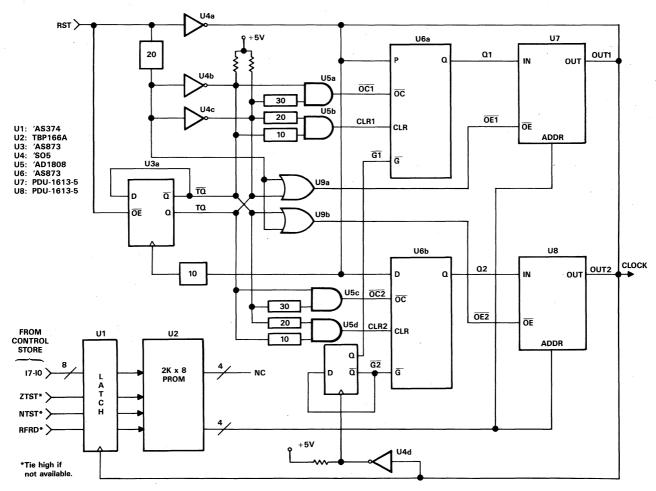

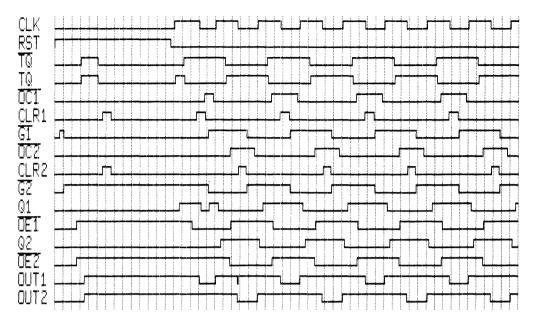

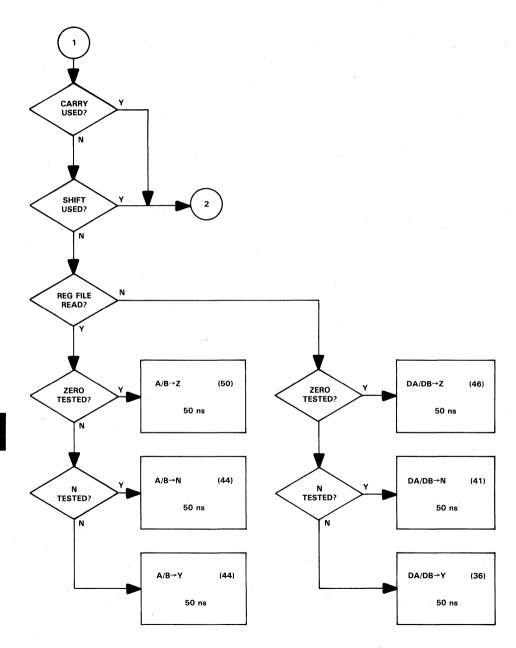

Excerpt — SN74AS888, SN74AS890

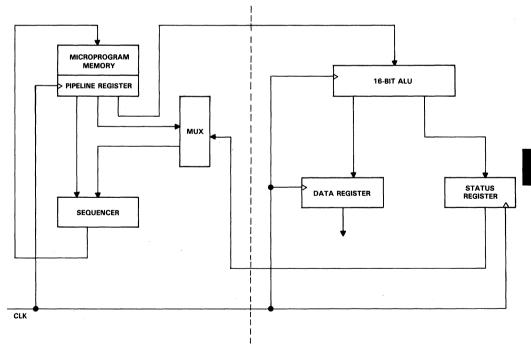

Bit-Slice Processor User's Guide

# **Mechanical Data**

4

| NNSAAS181A SN74AS181A 2-3 SN54AS8852 SN74AS852 2-201 SN54LS222 SN74LS224 2-13 SN54AS856 SN74AS866 2-207 SN54LS224 SN74LS224 2-13 SN54AS867 SN74AS867 2-213 SN54LS227 SN74LS227 2-13 SN54AS867 SN74AS867 2-213 SN54LS227 SN74LS227 2-13 SN54AS867 SN74AS869 2-213 SN54LS228 SN74LS228 2-13 SN54AS870 SN74AS870 2-219 SN54LS228 SN74LS228 2-13 SN54AS871 SN74AS871 2-219 SN54LS228 SN74LS228 2-23 SN54AS877 SN74AS877 2-225 SN54LS228 SN74LS228 2-23 SN54AS877 SN74AS877 2-225 SN54LS228 SN74LS228 2-23 SN54AS8877 SN74AS877 2-225 SN54LS232A SN74LS233A 2-23 SN54AS8877 SN74AS881 2-233 SN54AS230 SN74AS230 2-24 SN54AS881 SN74AS881 2-233 SN54AS230 SN74AS230 2-24 SN54AS882 SN74AS882 2-223 SN54AS238 SN74AS280 2-24 SN54AS888 SN74AS882 2-233 SN54AS280 SN74AS280 2-24 SN54AS888 SN74AS88 2-233 SN54AS280 SN74AS280 2-24 SN54AS888 SN74AS88 SN74AS88 2-233 SN54AS280 SN74AS280 2-24 SN54AS889 SN74AS88 2-233 SN54AS280 SN74AS280 2-25 SN54AS89 SN74AS88 SN74AS88 2-233 SN54AS280 SN74AS286 2-23 SN54AS89 SN74AS88 2-233 SN54AS280 SN74AS286 2-23 SN54AS89 SN74AS89 2-233 SN54AS280 SN74AS286 2-23 SN54AS89 SN74AS89 2-233 SN54AS281 SN74IS611 2-269 SN54AS89 SN74AS89 2-249 SN54AS581 SN74IS612 2-269 SN54AS893 SN74AS89 2-249 SN54AS816 SN74IS612 2-269 SN54AS893 SN74AS89 2-249 SN54AS816 SN74IS612 2-269 SN54AS893 SN74AS89 2-249 SN54AS816 SN74IS613 2-269 SN54AS89 SN74AS89 2-249 SN54AS632 SN74IS633 2-297 SN74IS99 2-2449 SN54AS632 SN74IS633 2-291 SN54AS89 SN74AS99 2-2449 SN54AS632 SN74IS633 2-291 SN74IS99 2-2449 SN54AS632 SN74IS633 2-291 SN74IS99 2-2449 SN54AS632 SN74IS633 2-291 SN74IS99 2-2449 SN54AS634 SN74IS634 2-291 SN54AS634 SN74IS634 2-291 SN54AS636 SN74AS89 SN74AS89 2-249 SN54AS636 SN74AS634 2-291 SN54AS69 SN74IS634 2-291 SN54AS69 SN74IS634 2-291 SN54AS69 SN74IS69 SN74IS69 SN74IS99 2-2493 SN54AS69 SN74IS69 SN74IS69 SN74IS99 2-2493 SN54AS69 SN74IS69 |             | Allinger        | NOAL INDEV        |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|-------------------|---------------------|

| SNS4LS222   SN74LS222   2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                 |                   |                     |

| SN54LS224   SN74LS225   2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                 |                   |                     |

| SNA4LS272   SN74S225   2-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                 |                   |                     |

| SN54LS227   SN74LS227   2-13   SN54AS870   SN74AS870   2-219   SN54LS228   SN74LS228   2-13   SN54AS871   2-219   SN54LS2292   SN74ALS228   2-27   SN54AS871   SN74AS877   2-225   SN54ALS232A   SN74ALS232A   2-37   SN54AS881A   2-3   SN54ALS232A   SN74ALS232A   2-37   SN54AS881A   2-3   SN54ALS232A   SN74ALS233A   2-37   SN54AS881A   SN74AS881A   2-2   SN54ALS230   SN74ALS280   2-47   SN54AS881A   SN74AS881A   2-2   SN54ALS280   SN74AS280   2-47   SN54AS885   SN74AS887   2-245   SN54AS280   SN74AS280   2-47   SN54AS885   SN74AS887   2-245   SN54AS280   SN74AS280   2-47   SN54AS888   SN74AS888   2-293   SN54LS280   SN74AS286   2-53   SN54AS889   SN74AS889   2-243   SN54LS281   SN74LS610   2-59   SN54AS890   SN74AS890   2-243   SN54LS611   SN74LS611   2-59   SN54AS895   SN74AS895   2-361   SN54LS612   SN74LS616   2-59   SN54AS895   SN74AS896   2-241   SN54LS613   SN74LS616   2-69   SN54ALS964   SN74ALS964   2-429   SN54LS616   SN74ALS616   2-69   SN54ALS964   SN74ALS994   2-429   SN54LS617   SN74LS617   2-69   SN54ALS964   SN74ALS994   2-441   SN54ALS617   SN74ALS617   2-69   SN54ALS964   SN74ALS994   2-441   SN54ALS617   SN74ALS618   2-91   SN54ALS964   SN74ALS994   2-441   SN54ALS632   SN74ALS632   2-91   SN74ALS994   2-447   SN54ALS633   SN74ALS633   2-91   SN74ALS994   2-447   SN54ALS634   SN74ALS634   2-91   SN74ALS995   2-446   SN54ALS635   SN74ALS636   2-91   SN74ALS996   2-467   SN54ALS634   SN74ALS636   2-91   SN74ALS996   2-467   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   3-483   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   SN74ALS996   2-467   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   SN74ALS996   2-467   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   SN74ALS996   2-467   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   SN74ALS996   2-667   SN54ALS648   SN74ALS646   2-111   SN54ALS2967   SN74ALS2968   2-693   SN54ALS648   SN74ALS666   2-125   SN54ALS29818   SN74ALS2962   2-659   SN54ALS661   SN74ALS666   2-125   SN54ALS2986   SN74ALS2962   2-659   SN54ALS661   SN74ALS666   2-125   SN54AL   | SN54LS224   |                 |                   |                     |

| SN54LS228                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                 |                   |                     |

| SNF4ALS229A   SN74ALS229A   2.27   SNF4AS887   SN74AS887   2.225   SNF4ALS223A   SN74ALS232A   2.33   SNF4AS881A   SN74AS881A   2.23   SNF4ALS23A   SN74ALS233A   2.37   SNF4AS881A   SN74AS882A   2.231   SNF4ALS23A   SN74ALS280   2.47   SNF4AS885   2.239   SNF4ALS280   SN74AS280   2.47   SNF4AS885   SN74AS886   2.295   SNF4AS280   SN74AS286   2.53   SNF4AS888   2.293   SNF4AS280   SN74AS286   2.55   SNF4AS888   2.293   SNF4ALS280   SN74AS286   2.55   SNF4AS889   SN74AS889   2.243   SNF4AS286   SN74AS286   2.55   SNF4AS889   SN74AS889   2.243   SNF4LS611   SN74LS611   2.59   SNF4AS895   SN74AS895   2.361   SNF4LS611   SN74LS611   2.59   SNF4AS895   SN74AS895   2.361   SNF4LS612   SN74LS612   2.59   SNF4AS895   SN74AS897A   2.411   SNF4LS612   SN74LS616   2.69   SNF4ALS964   SN74ALS964   2.429   SNF4ALS618   SN74ALS616   2.69   SNF4ALS964   SN74ALS964   2.429   SNF4ALS619   SNF4ALS616   2.69   SNF4ALS964   SN74ALS964   2.429   SNF4ALS617   SNF4ALS617   2.69   SNF4ALS964   SN74ALS990   2.441   SNF4ALS617   SNF4ALS618   2.91   SNF4ALS991   2.441   SNF4ALS632   SNF4ALS632   2.91   SNF4ALS991   2.441   SNF4ALS633   SNF4ALS634   2.91   SNF4ALS993   2.449   SNF4ALS634   SNF4ALS634   2.91   SNF4ALS993   2.449   SNF4ALS635   SNF4ALS634   2.91   SNF4ALS995   2.467   SNF4ALS634   SNF4ALS634   2.91   SNF4ALS996   2.467   SNF4ALS636   SNF4ALS636   2.91   SNF4ALS996   2.467   SNF4ALS636   SNF4ALS636   2.91   SNF4ALS996   2.467   SNF4ALS64   SNF4ALS64   2.111   SNF4ALS996   SNF4ALS996   2.467   SNF4ALS66   SNF4ALS66   2.111   SNF4ALS996   SNF4ALS996   2.467   SNF4ALS66   SNF4ALS66   2.111   SNF4ALS996   SNF4ALS996   2.467   SNF4ALS66   SNF4ALS66   2.111   SNF4ALS996   SNF4ALS996   2.699   SNF4ALS66   SNF4ALS66   2.111   SNF4ALS998   SNF4ALS998   2.699   SNF4ALS66   SNF4ALS66   2.111   SNF4ALS998   SNF4ALS998   2.699   SNF4ALS66   S   | SN54LS227   |                 |                   | SN74AS870 2-219     |

| SNF4ALS222A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SN54LS228   |                 |                   |                     |

| SNF4ALS233A   2-37   SNF4ASB82A   SN74ASB82A   2-231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SN54ALS229A |                 |                   |                     |

| SNSAALS280         SN7AAS250         2.43         SNSAALS2887         2.245           SNSAALS280         SN7AAS280         2.47         SNSAAS288         2.93           SNSAAS286         SN7AAS286         2.53         SNSAAS288         2.93           SNSALS286         SN7AAS288         2.53         SNSAAS895         SN7AAS8890         2.343           SNSALS610         SN74LS611         2.59         SNSAAS895         SN7AAS895         2.361           SNSALS612         SN74LS613         2.59         SNSAALS97A         SN7AALS963         2.423           SNSALS613         SN74LS616         2.69         SNSAALS964         SN7AALS963         2.423           SNSAALS616         SN7AALS917         2.69         SNSAALS964         SN7AALS990         2.441           SNSAALS632         SN7AALS932         2.81         SN7AALS991         2.441           SNSAALS633         SN7AALS933         2.81         SN7AALS993         2.449           SNSAALS633         SN7AALS934         2.81         SN7AALS993         2.449           SNSAALS633         SNFAALS634         2.81         SN7AALS993         2.449           SNSAALS634         SNFAALS934         2.81         SN7AALS993         2.449 <td>SN54ALS232A</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SN54ALS232A |                 |                   |                     |

| SN54ALS280 SN74ALS280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SN54ALS233A |                 |                   |                     |

| SN54AS286   SN74AS286   2-93   SN54AS888   SN74AS888   2-93   SN54AS286   SN74AS286   2-53   SN54AS895   SN74AS895   2-343   SN54LS610   SN74LS610   2-59   SN54AS895   SN74AS895   2-241   SN54LS611   SN74LS611   2-59   SN54AS895   SN74AS897   2-411   SN54LS612   SN74LS612   2-59   SN54AS897   SN74AS897   2-411   SN54LS613   SN74LS613   2-59   SN54ALS964   SN74ALS963   2-429   SN54LS616   SN74ALS616   2-69   SN54ALS964   SN74ALS963   2-441   SN54ALS617   SN74LS617   2-69   SN54ALS964   SN74ALS963   2-441   SN54ALS618   SN74LS612   2-97   SN74ALS991   2-441   SN54ALS632   SN74ALS632   2-97   SN74ALS993   2-449   SN54ALS633   SN74ALS633   2-81   SN74ALS993   2-449   SN54ALS634   SN74ALS634   2-81   SN74ALS993   2-449   SN54ALS635   SN74ALS634   2-81   SN74ALS993   2-449   SN54ALS634   SN74ALS634   2-81   SN74ALS993   2-457   SN54ALS634   SN74ALS634   2-97   SN74ALS996   2-465   SN54ALS636   SN74ALS636   2-81   SN54ALS2967   SN74ALS996   2-463   SN54ALS64   SN74ALS646   2-111   SN54ALS2968   SN74ALS986   2-483   SN54ALS64   SN74ALS64   2-111   SN54ALS2968   SN74ALS986   2-483   SN54ALS64   SN74ALS64   2-111   SN54ALS2968   SN74ALS986   2-483   SN54ALS64   SN74ALS64   2-111   SN54ALS2968   SN74ALS383   2-253   SN54ALS64   SN74ALS64   2-111   SN54ALS2968   SN74ALS2967   2-483   SN54ALS64   SN74ALS64   2-111   SN54ALS2988   SN74ALS2988   2-23   SN54ALS64   SN74ALS66   2-111   SN54ALS2988   SN74ALS2988   2-23   SN54ALS64   SN74ALS66   2-111   SN54ALS2988   SN74ALS2988   2-23   SN54ALS65   SN74ALS66   2-111   SN54ALS2988   SN74ALS2988   2-23   SN54ALS66   SN74ALS66   2-125   SN54ALS29818   SN74ALS29818   2-23   SN54ALS66   SN74ALS66   2-125   SN54ALS2988   SN74ALS29819   2-23   SN54ALS66   SN74ALS66   2-125   SN54ALS2988   SN74ALS2984   2-25   SN54ALS66   SN74ALS66   2-16   SN54ALS2988   SN74ALS2986   2-25   | 4.          |                 |                   |                     |

| SN54AS286   SN74AS286   2-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                 |                   |                     |

| SN54LS610   SN74LS610   2-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                 |                   |                     |

| SN54LS611                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SN54AS286   | SN74AS286 2-5   | 3 SN54AS890       |                     |

| SN54LS612         SN74LS613         SN74LS613         2.59         SN54ALS964         SN74ALS964         2.429           SN54ALS616         SN74ALS617         2.69         SN74ALS990         2.441           SN54ALS617         SN74ALS617         2.69         SN74ALS990         2.441           SN54ALS632         SN74ALS632A         2.81         SN74ALS992         2.449           SN54ALS633         SN74ALS632         2.97         SN74ALS993         2.449           SN54ALS633         SN74ALS634         2.81         SN74ALS994         2.457           SN54ALS634         SN54ALS634         2.81         SN74ALS996         2.465           SN54ALS634         SN74ALS634         2.81         SN54ALS966         2.457           SN54ALS635         SN44ALS635         2.81         SN54ALS636         2.411           SN54ALS646         SN74ALS646         2.111         SN54ALS647         3.744           SN54ALS647         SN74ALS648         2.111         SN54ALS630         SN74ALS648           SN54ALS648         SN74ALS648         2.111         SN54ALS630         SN74ALS648           SN54ALS649         SN74ALS648         2.111         SN54ALS630         SN74ALS649         2.125           SN5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SN54LS610   |                 |                   |                     |

| SN54ALS613   SN74LS613   2.59   SN54ALS964   SN74ALS964   2.429   SN54ALS616   SN74ALS616   2.69   SN74ALS990   2.441   SN54ALS617   SN74ALS617   2.69   SN74ALS991   2.441   SN54ALS623   SN74ALS632A   2.81   SN74ALS993   2.449   SN54ALS632   SN74ALS633   2.81   SN74ALS993   2.449   SN54ALS633   SN74ALS633   2.81   SN74ALS995   2.457   SN54ALS634   SN74ALS634   2.97   SN74ALS995   2.457   SN54ALS634   SN74ALS634   2.97   SN74ALS995   2.457   SN54ALS635   SN74ALS634   2.97   SN74ALS996   2.465   SN54ALS635   SN74ALS636   2.111   SN54ALS2967   SN74ALS2967   2.483   SN54ALS646   SN74ALS646   2.111   SN54ALS2967   SN74ALS2967   2.483   SN54ALS647   SN74ALS648   2.111   SN54ALS2968   SN74ALS2967   2.483   SN54ALS648   SN74ALS648   2.111   SN54ALS2968   SN74ALS2968   2.503   SN54ALS649   SN74ALS648   2.111   SN54ALS2961   SN74ALS2967   2.503   SN54ALS649   SN74ALS648   2.111   SN54ALS6301   SN74ALS6400   2.503   SN54ALS649   SN74ALS649   2.111   SN5ALS6801   SN74ALS6400   2.509   SN54ALS649   SN74ALS649   2.111   SN5ALS8838   SN74ALS843   2.513   SN54ALS651   SN74ALS651   2.125   SN5AALS8838   SN74ALS8838   2.523   SN5AALS651   SN74ALS651   2.125   SN5AALS29818   SN74ALS29818   2.533   SN5ALS651   SN74ALS652   2.125   SN5AALS29818   SN74ALS29819   2.533   SN5ALS652   SN74ALS653   2.125   SN5AALS29821   SN74ALS29819   2.533   SN5ALS665   SN74ALS666   2.137   SN5ALS29821   SN74ALS29822   2.545   SN5AALS663   SN74ALS666   2.137   SN5AALS29821   SN74ALS29822   2.545   SN5AALS664   SN74ALS666   2.137   SN5AALS29825   SN74ALS29826   2.551   SN5AALS665   SN74ALS666   2.137   SN5AALS29825   SN74ALS29826   2.555   SN5AALS665   SN74ALS666   2.137   SN5AALS29826   SN74ALS29826   2.555   SN5AAS821   SN74AS821   2.145   SN5AALS29826   SN74ALS29826   2.555   SN5AAS822   SN74AS824   2.163   SN5AALS29826   SN74ALS29826   2.555   SN5AAS824   SN74AS824   2.163   SN5AALS29826   SN74ALS29826   2.557   SN5AAS824   SN74AS844   2.163   SN5AALS29864   SN74ALS29826   2.577   SN5AAS842   SN74AS844   2.163   SN5AALS29864   SN74ALS29826   2.57   | SN54LS611   |                 |                   |                     |

| SN54ALS616   SN74ALS617   2-69   SN74ALS990   2-441   SN54ALS617   SN74ALS617   2-69   SN74ALS991   2-441   SN54ALS632A   SN74ALS632A   2-81   SN74ALS992   2-449   SN54ALS633   SN74ALS632   2-97   SN74ALS993   2-449   SN54ALS633   SN74ALS633   2-81   SN74ALS994   2-457   SN54ALS634   SN74ALS634   2-81   SN74ALS996   2-465   SN54ALS634   SN74ALS634   2-81   SN74ALS996   2-465   SN54ALS635   SN74ALS635   2-81   SN74ALS996   2-465   SN54ALS636   SN74ALS635   2-81   SN74ALS996   2-465   SN54ALS636   SN74ALS635   2-81   SN54ALS996   2-465   SN54ALS636   SN74ALS635   2-81   SN54ALS996   2-465   SN54ALS636   SN74ALS646   2-111   SN54ALS2968   SN74ALS2968   2-483   SN54ALS64   SN74ALS646   2-111   SN54ALS2968   SN74ALS2968   2-483   SN54ALS64   SN74ALS647   2-111   SN54ALS2968   SN74ALS2968   2-483   SN54ALS64   SN74ALS648   2-111   SN54ALS6301   SN74ALS6302   2-503   SN54AS64   SN74ALS648   2-111   SN54ALS6302   SN74ALS6302   2-503   SN54ALS64   SN74ALS649   2-111   SN54ALS6302   SN74ALS6302   2-503   SN54ALS64   SN74ALS649   2-111   SN54ALS2968   SN74ALS2968   2-253   SN54ALS65   SN74ALS661   2-125   SN54ALS2981   SN74ALS2981   2-533   SN54ALS65   SN74ALS65   2-125   SN54ALS2981   SN74ALS2981   2-533   SN54ALS65   SN74ALS65   2-125   SN54ALS2981   SN74ALS2981   2-533   SN54ALS65   SN74ALS65   2-125   SN54ALS2982   SN74ALS2981   2-533   SN54ALS65   SN74ALS66   2-125   SN54ALS2982   SN74ALS2982   2-545   SN54ALS66   SN74ALS66   2-125   SN54ALS2982   SN74ALS2982   2-545   SN54ALS66   SN74ALS66   2-125   SN54ALS2982   SN74ALS2982   2-556   SN54ALS66   SN74ALS66   2-137   SN54ALS2982   SN74ALS2982   2-556   SN54ALS66   SN74ALS66   2-163   SN54ALS2982   SN74ALS2982   2-556   SN54ALS84   SN74ALS84   2-163   SN54ALS2982   SN74ALS2986   2-577   SN54ALS84      | SN54LS612   | SN74LS612 2-5   | 9 SN54ALS963      | SN74ALS9632-429     |

| SN54ALS617   SN74ALS617.   2-69   SN74ALS991   2-441   SN54ALS632A   SN74ALS632A   2-81   SN74ALS992.   2-449   SN54ALS632   SN74ALS633   2-81   SN74ALS993   2-445   SN54ALS634   SN74ALS633   2-81   SN74ALS994   2-457   SN54ALS634   SN74ALS634   2-97   SN54ALS635   SN74ALS634   2-97   SN54ALS635   SN74ALS634   2-97   SN54ALS635   SN74ALS6364   2-111   SN54ALS635   SN74ALS636   2-467   SN54ALS635   SN74ALS646   2-111   SN54ALS2967   SN74ALS2967   2-483   SN54ALS646   SN74ALS646   2-111   SN54ALS2967   SN74ALS2967   2-483   SN54ALS646   SN74ALS646   2-111   SN54ALS6301   SN74ALS6301   2-503   SN54ALS647   SN74ALS647   2-111   SN54ALS6301   SN74ALS6301   2-503   SN54ALS648   SN74ALS648   2-111   SN54ALS6302   SN74ALS648   2-103   SN54ALS649   2-111   SN54ALS6302   SN74ALS649   2-111   SN54ALS6302   SN74ALS649   2-111   SN54ALS6302   SN74ALS649   2-111   SN54ALS6303   SN74ALS649   2-112   SN54ALS648   SN74ALS649   2-115   SN54ALS648   SN74ALS649   2-125   SN54ALS29818   SN74ALS649   2-125   SN54ALS29818   SN74ALS649   2-125   SN54ALS29819   SN74ALS649   2-125   SN54ALS29819   SN74ALS649   2-125   SN54ALS29819   SN74ALS29818   2-533   SN54AS652   SN74ALS665   2-125   SN54ALS29819   SN74ALS29821   2-545   SN54ALS665   SN74ALS666   2-137   SN54ALS29821   SN74ALS29822   2-545   SN54ALS29821   SN74ALS666   SN74ALS666   2-137   SN54ALS29821   SN74ALS29822   2-545   SN54ALS29823   SN74ALS666   SN7   | SN54LS613   | SN74LS613 2-5   | 9 SN54ALS964      | SN74ALS964 2-429    |

| SN54ALS632A   SN74ALS632A   2.81   SN74ALS992   2.449   SN54ALS633   SN74ALS633   2.81   SN74ALS993   2.449   SN54ALS633   SN74ALS633   2.81   SN74ALS994   2.457   SN54ALS634   SN74ALS634   2.81   SN74ALS996   2.457   SN54ALS634   SN74ALS635   2.81   SN74ALS996   2.465   SN54ALS635   SN74ALS635   2.81   SN54AS1181   SN74ALS996   2.465   SN54ALS636   SN74ALS635   2.81   SN54AS1181   SN74ALS966   2.465   SN54ALS636   SN74ALS636   2.111   SN54ALS2967   SN74ALS2967   2.483   SN54ALS646   SN74ALS646   2.111   SN54ALS2968   SN74ALS2968   2.483   SN54ALS647   SN74ALS647   2.111   SN54ALS6301   SN74ALS6301   2.503   SN54ALS648   SN74ALS647   2.111   SN54ALS6301   SN74ALS6302   2.503   SN54ALS648   SN74ALS648   2.111   SN54ALS6302   SN74ALS6300   2.509   SN54ALS649   SN74ALS649   2.111   SN54ALS6304   SN74ALS6400   2.509   SN54ALS649   SN74ALS651   2.125   SN54ALS2981   SN74ALS8834   2.513   SN54ALS651   SN74ALS651   2.125   SN54ALS29818   SN74ALS29818   2.533   SN54ALS652   SN74ALS652   2.125   SN54ALS29819   SN74ALS29819   2.533   SN54ALS652   SN74ALS652   2.125   SN54ALS29819   SN74ALS29819   2.533   SN54ALS653   SN74ALS654   2.125   SN54ALS29821   SN74ALS29821   2.545   SN54ALS664   SN74LS666   2.137   SN54ALS29823   SN74ALS29823   2.551   SN54ALS665   SN74ALS666   2.137   SN54ALS29824   SN74ALS29823   2.551   SN54ALS666   SN74ALS666   2.137   SN54ALS29824   SN74ALS29823   2.551   SN54ALS667   SN74ALS666   2.137   SN54ALS29824   SN74ALS29825   2.565   SN54ALS667   SN74ALS666   2.137   SN54ALS29826   SN74ALS29826   2.559   SN54ALS667   SN74ALS666   2.137   SN54ALS29826   SN74ALS29826   2.559   SN54ALS667   SN74ALS666   SN74ALS666   2.137   SN54ALS29826   SN74ALS29826   2.551   SN54ALS667   SN74ALS667   2.137   SN54ALS29826   SN74ALS29826   2.551   SN54ALS667   SN74ALS667   2.137   SN54ALS29826   SN74ALS29826   2.551   SN54ALS6882   SN74AS826   2.163   SN54ALS29863   SN74ALS29866   2.551   SN54ALS841   SN74ALS844   2.163   SN54ALS29861   SN74ALS29862   2.561   SN54ALS842   SN74AS844   2.163   SN54ALS29864   SN74ALS2   | SN54ALS616  | SN74ALS616 2-69 | 9                 | SN74ALS990 2-441    |

| SN54AS632         SN74AS633         2.97         SN74ALS933         2.449           SN54ALS634         SN74ALS634         2.81         SN74ALS996         2.457           SN54ALS634         SN74ALS634         2.97         SN74ALS996         2.465           SN54ALS635         SN74ALS635         2.81         SN54ALS996         2.465           SN54ALS636         SN74ALS636         2.81         SN54ALS2967         SN74ALS996         2.465           SN54ALS646         SN74ALS646         2.111         SN54ALS2967         SN74ALS2967         2.483           SN54ALS647         SN74ALS647         2.111         SN54ALS2968         SN74ALS6301         2.503           SN54ALS648         SN74ALS648         2.111         SN54ALS6302         SN74ALS6302         2.503           SN54ALS648         SN74ALS648         2.111         SN54ALS6302         SN74ALS6302         2.503           SN54ALS648         SN74ALS6648         2.111         SN54ALS6302         SN74ALS6302         2.503           SN54ALS648         SN74ALS661         2.125         SN54AS8838         SN74ALS6302         2.503           SN54ALS661         SN74ALS651         2.125         SN54ALS8838         SN74ALS632         2.513           SN54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SN54ALS617  | SN74ALS617 2-69 | 9                 |                     |

| SN54ALS633                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SN54ALS632A | SN74ALS632A 2-8 | 1                 | SN74ALS992 2-449    |

| SN54ALS634   SN74ALS634   2-81   SN74ALS995   2-465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SN54AS632   | SN74AS632 2-9   | 7                 | SN74ALS993 2-449    |

| SN54AS684         SN74ALS635         2-97         SN74ALS996         2-465           SN54ALS635         SN74ALS635         2-81         SN54AS1181         SN74AS181         2-471           SN54ALS646         SN74ALS646         2-111         SN54ALS2967         SN74ALS2968         2-483           SN5AAS646         SN74ALS647         2-111         SN54ALS6301         2-503           SN5AALS648         SN74ALS648         2-111         SN54ALS6302         SN74ALS6400         2-503           SN54ALS648         SN74ALS649         2-111         SN54ALS6302         SN74ALS640         2-503           SN54ALS649         SN74ALS661         2-125         SN54ALS6834         2-513           SN54ALS649         SN74ALS661         2-125         SN54ALS8838         SN74AS8834         2-513           SN54ALS651         SN74ALS651         2-125         SN54ALS29818         SN74ALS651         2-125           SN54ALS652         SN74ALS652         2-125         SN54ALS29818         SN74ALS691         2-533           SN54ALS661         SN74ALS662         2-125         SN54ALS29819         SN74ALS692         2-545           SN54ALS662         SN74ALS666         2-125         SN54ALS29821         SN74ALS29822         2-545                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SN54ALS633  | SN74ALS6332-8   | 1                 | SN74ALS994 2-457    |

| SN54ALS635   SN74ALS635   2-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SN54ALS634  | SN74ALS6342-8   | 1                 |                     |

| SN54ALS646         SN74ALS646         2-111         SN54ALS2967         SN74ALS2967         2-483           SN54AAS646         SN74AS646         2-111         SN54ALS2968         SN74ALS2968         2-483           SN54ALS647         2-111         SN54ALS6301         SN74ALS6302         2-503           SN54ALS648         SN74ALS648         2-111         SN54ALS6302         SN74ALS6302         2-503           SN54ALS649         SN74ALS649         2-111         SN54ALS683         SN74ALS640         2-503           SN54ALS651         SN74ALS651         2-125         SN54ALS8838         SN74AS8834         2-513           SN54ALS651         SN74ALS651         2-125         SN54ALS29818         SN74ALS29818         2-523           SN54ALS652         SN74AS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS652         SN74ALS653         2-125         SN54ALS29819         SN74ALS29812         2-545           SN54ALS665         SN74ALS663         2-125         SN54ALS29821         SN74ALS29812         2-545           SN54ALS666         SN74ALS6663         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS266         SN74ALS6667         2-137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SN54AS634   | SN74AS634 2-9   | 7                 | SN74ALS996 2-465    |

| SN54AS646         SN74ALS647         2-111         SN54ALS2968         SN74ALS2968         2-483           SN54ALS647         SN74ALS648         2-111         SN54ALS6301         SN74ALS6302         2-503           SN54ALS648         2-111         SN54ALS6302         SN74ALS640         2-503           SN54ALS649         SN74ALS649         2-111         SN54ALS834         2-513           SN54ALS651         SN74ALS651         2-125         SN54AS838         SN74AS8834         2-513           SN54ALS651         SN74ALS651         2-125         SN54ALS8388         SN74ALS8838         2-523           SN54ALS651         SN74ALS651         2-125         SN54ALS29818         SN74ALS29818         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS653         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS664         SN74ALS653         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS6653         SN74ALS6653         2-125         SN54ALS29821         SN74ALS29822         2-545           SN54ALS2666         SN74ALS666         2-137         SN54ALS29823                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SN54ALS635  | SN74ALS6352-8   | 1 SN54AS1181      | SN74AS1181 2-471    |

| SN54ALS647         SN74ALS648         2-111         SN54ALS6301         SN74ALS6302         2-503           SN54ALS648         SN74ALS648         2-111         SN54ALS6302         SN74ALS6302         2-503           SN54ALS649         SN74ALS649         2-111         SN54ALS8834         SN74AS8834         2-513           SN54ALS651         SN74ALS651         2-125         SN54AS838         SN74AS8838         2-523           SN54ALS651         SN74ALS651         2-125         SN54ALS9818         SN74ALS29818         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29818         SN74ALS29819         2-533           SN54ALS662         SN74ALS663         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS663         SN74ALS663         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS664         SN74ALS663         2-125         SN54ALS29822         SN74ALS29821         2-545           SN54ALS666         SN74ALS666         2-137         SN54ALS29823         SN74ALS29824         2-551           SN54ALS821         SN74ALS2667         2-137         SN54ALS29825         SN74ALS29826         2-559           SN54ALS282         SN74ALS29826 <td>SN54ALS646</td> <td>SN74ALS646 2-11</td> <td>1 SN54ALS2967</td> <td>SN74ALS2967</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SN54ALS646  | SN74ALS646 2-11 | 1 SN54ALS2967     | SN74ALS2967         |

| SN54ALS648         SN74ALS648         2-111         SN54ALS6302         SN74ALS6302         2-503           SN54AAS648         SN74ALS649         2-111         SN54ALS8834         SN74ALS6400         2-509           SN54ALS649         SN74ALS661         2-125         SN54AS8838         SN74AS8838         2-513           SN54ALS651         SN54ALS651         2-125         SN54ALS29818         SN74ALS29818         2-523           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29811         2-533           SN54ALS653         SN74ALS662         2-125         SN54ALS29819         SN74ALS29821         2-545           SN54ALS653         SN74ALS662         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS664         SN74ALS664         2-125         SN54ALS29823         SN74ALS29822         2-545           SN54ALS666         SN74ALS666         2-137         SN54ALS29823         SN74ALS29824         2-561           SN54ALS821         SN74ALS667         2-137         SN54ALS29826         SN74ALS29825         2-559           SN54AS822         SN74AS822 <td>SN54AS646</td> <td>SN74AS646 2-11</td> <td>1 SN54ALS2968</td> <td>SN74ALS2968 2-483</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SN54AS646   | SN74AS646 2-11  | 1 SN54ALS2968     | SN74ALS2968 2-483   |

| SN54AS648         SN74ALS649         2-111         SN74ALS8400         2-509           SN54ALS649         SN74ALS661         2-115         SN54AS834         2-513           SN54ALS651         SN74ALS651         2-125         SN54AS838         SN74AS838         2-523           SN54AS651         SN74ALS652         2-125         SN54ALS29818         SN74ALS29818         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29811         2-545           SN54ALS653         SN74ALS653         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS664         SN74ALS666         2-125         SN54ALS29822         SN74ALS29823         2-551           SN54ALS666         SN74ALS666         2-137         SN54ALS29823         SN74ALS29824         2-561           SN54ALS821         SN74AS221         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS22         SN74AS823         2-151         SN54ALS29826         SN74ALS29826         2-556           SN54AS823         SN74AS823         2-151         SN54ALS29828         S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SN54ALS647  | SN74ALS647 2-11 | 1 SN54ALS6301     | SN74ALS6301 2-503   |

| SN54ALS649         SN74ALS649         2-111         SN54AS8834         SN74AS8834         2-513           SN54ALS651         SN74ALS651         2-125         SN54AS8838         SN74AS8838         2-523           SN54ALS651         SN74AS651         2-125         SN54ALS29818         SN74ALS29819         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54ALS653         SN74ALS653         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS653         SN74ALS664         2-125         SN54ALS29823         SN74ALS29823         2-545           SN54ALS664         SN74ALS666         2-137         SN54ALS29823         SN74ALS29823         2-551           SN54ALS666         SN74ALS666         2-137         SN54ALS29824         SN74ALS29824         2-551           SN54ALS821         SN74AS821         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS821         SN74AS821         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS823         SN74AS822         2-145         SN54ALS29826         SN74ALS29826         2-555           SN54AS824         SN74AS825                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SN54ALS648  | SN74ALS648 2-11 | 1 SN54ALS6302     | SN74ALS6302 2-503   |

| SN54ALS651         SN74ALS651         2-125         SN54AS838         SN74AS8838         2-523           SN54ALS651         SN74ALS651         2-125         SN54ALS29818         SN74ALS29819         2-533           SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29821         2-533           SN54ALS652         SN74ALS663         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS663         SN74ALS664         2-125         SN54ALS29822         SN74ALS29822         2-545           SN54ALS666         SN74ALS666         2-125         SN54ALS29823         SN74ALS29823         2-551           SN54ALS667         SN74ALS666         2-137         SN54ALS29824         SN74ALS29824         2-551           SN54AS21         SN74AS821         2-145         SN54ALS29825         SN74ALS29826         2-559           SN54AS822         SN74AS822         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS823         SN74AS822         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS823         SN74AS823         2-151         SN54ALS29828         SN74ALS29827         2-5665           SN54AS824         SN74AS824                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SN54AS648   | SN74AS648 2-11  | 1                 | SN74ALS8400 2-509   |

| SN54AS651         SN74AS651         2-125         SN54ALS29818         SN74ALS29818         2-533           SN54ALS652         SN74AS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54AS652         SN74AS652         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS653         SN74ALS653         2-125         SN54ALS29822         SN74ALS29822         2-545           SN54ALS664         SN74ALS666         2-137         SN54ALS29823         SN74ALS29823         2-551           SN54ALS666         SN74ALS666         2-137         SN54ALS29824         SN74ALS29824         2-551           SN54ALS667         SN74ALS667         2-137         SN54ALS29825         SN74ALS29824         2-551           SN54AS821         SN74AS821         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS822         SN74AS822         2-145         SN54ALS29827         SN74ALS29827         2-566           SN54AS823         SN74AS822         2-151         SN54ALS29861         SN74ALS29828         2-567           SN54AS824         SN74AS824         2-151         SN54ALS29861         SN74ALS29862         2-571           SN54AS825         SN74AS826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SN54ALS649  | SN74ALS649 2-11 | 1 SN54AS8834      | SN74AS8834 2-513    |

| SN54ALS652         SN74ALS652         2-125         SN54ALS29819         SN74ALS29819         2-533           SN54AS652         SN74AS652         2-125         SN54ALS29821         SN74ALS29821         2-545           SN54ALS653         SN74ALS653         2-125         SN54ALS29822         SN74ALS29822         2-545           SN54ALS664         SN74ALS666         2-125         SN54ALS29823         SN74ALS29823         2-551           SN54ALS667         SN74ALS667         2-137         SN54ALS29825         SN74ALS29825         2-559           SN54AS821         SN74AS821         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS822         SN74AS822         2-145         SN54ALS29826         SN74ALS29826         2-559           SN54AS823         SN74AS822         2-145         SN54ALS29828         SN74ALS29826         2-559           SN54AS823         SN74AS823         2-151         SN54ALS29828         SN74ALS29826         2-555           SN54AS824         SN74AS825         2-157         SN54ALS29861         SN74ALS29861         2-571           SN54AS825         SN74AS826         2-157         SN54ALS29862         SN74ALS29862         2-571           SN54AS841         SN74AS846                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SN54ALS651  | SN74ALS651 2-12 | 5 SN54AS8838      | SN74AS8838 2-523    |