## Advanced Logic and Bus Interface Logic

Data Book

## Data Book

Advanced Logic and Bus Interface Logic

| General Information                | 1  |

|------------------------------------|----|

| ACL LSI Products                   | 2  |

| ACL Widebus™ Products              | 3  |

| BTL Transceiver Products           | 4  |

| Bus-Termination Array Products     | 5  |

| Clock Driver Products              | 6  |

| ECL/TTL Translator Products        | 7  |

| FIFO Products                      | 8  |

| Low-Impedance Line Driver Products | 9  |

| Memory Driver Products             | 10 |

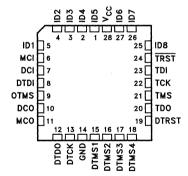

| SCOPE™ Testability Products        | 11 |

| 64BCT Series Products              | 12 |

| Mechanical Data                    | 13 |

## **Product Stage Statements**

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

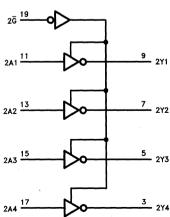

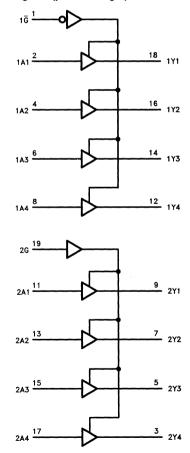

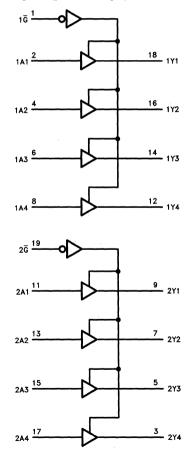

PRODUCT PREVIEW documents contain information on products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

ADVANCE INFORMATION documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

The next statements must be used in combination.

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

If any of the pages contain PRODUCT PREVIEW information, this statement must appear at the lower left on those pages.

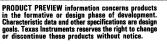

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If any of the pages contain ADVANCE INFORMATION, this statement must appear at the lower left on those pages.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

## Advanced Logic and Bus Interface Logic Data Book

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Texas Instruments products are not intended for use in life support appliances, devices or systems. Use of a TI product in such applications without the written consent of the appropriate TI officer is prohibited.

Copyright © 1991, Texas Instruments Incorporated

#### INTRODUCTION

The new advanced logic and bus interface logic solutions from Texas Instruments can help you design today's high-performance, low-power bus interface while addressing important design issues such as enhancing speed and conserving board space.

#### Solutions include:

- ACL LSI for high-speed, low-power logic requirements

- ACL Widebus™ Series doubles I/O count in the same board area

- BiCMOS and submicron BiCMOS bus-interface logic families offering drivers, transceivers, latches, registers, and registered and latched transceivers

- Bus-termination arrays for an effective termination solution

- · Clock drivers minimize skew

- ECL translators for fast, low-power ECL/TTL translations

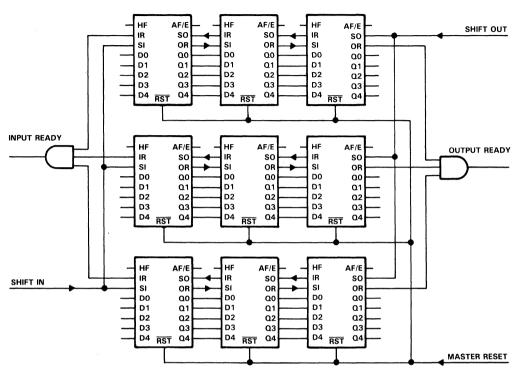

- FIFOs help accelerate overall system performance

- Futurebus+ transceivers with logic voltage levels selected to optimize bus performance

- Low-impedance line drivers with speed and power characteristics similar to those of BCT octals and drive capability of 188 mA

- SCOPE<sup>™</sup> products providing on-chip testability

- 64 Series BiCMOS designed for the telecommunications-or industrial-equipment market to withstand extended temperature ranges and hot-card insertion

This book provides pertinent technical information on available and planned advanced logic and bus interface logic devices. Additionally, the General Information Section contains an alphanumerical index, functional index, and other useful information.

For more information on Texas Instruments advanced logic and bus interface logic products, please contact your local TI field sales office or authorized distributor, or call Texas Instruments at 1-800-232-3200.

SCOPE and Widebus are trademarks of Texas Instruments Incorporated.

| General Information                | 1  |

|------------------------------------|----|

| ACL LSI Products                   | 2  |

| ACL Widebus™ Products              | 3  |

| BTL Transceiver Products           | 4  |

| Bus-Termination Array Products     | 5  |

| Clock Driver Products              | 6  |

| ECL/TTL Translator Products        | 7  |

| FIFO Products                      | 8  |

| Low-Impedance Line Driver Products | 9  |

| Memory Driver Products             | 10 |

| SCOPE™ Testability Products        | 11 |

| 64BCT Series Products              | 12 |

| Mechanical Data                    | 13 |

## **Contents**

|                                        | Page |

|----------------------------------------|------|

| Numerical Index                        |      |

| Glossary                               |      |

| Explanation of Function Tables         |      |

| Flip-Flop and Latch Signal Conventions |      |

| Thermal Information                    |      |

| Parameter Measurement Information      | 1-13 |

| Functional Index                       | 1-33 |

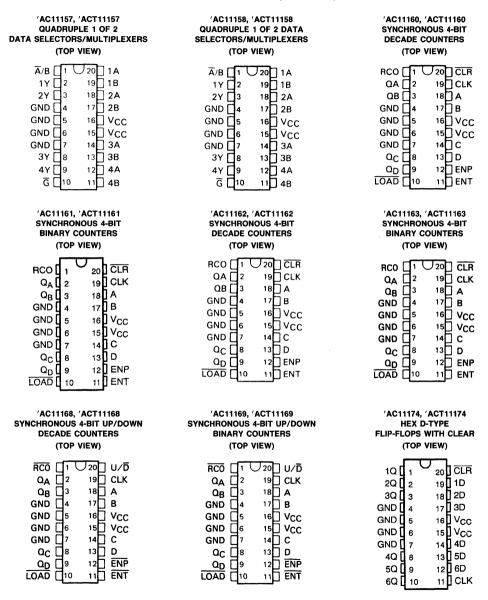

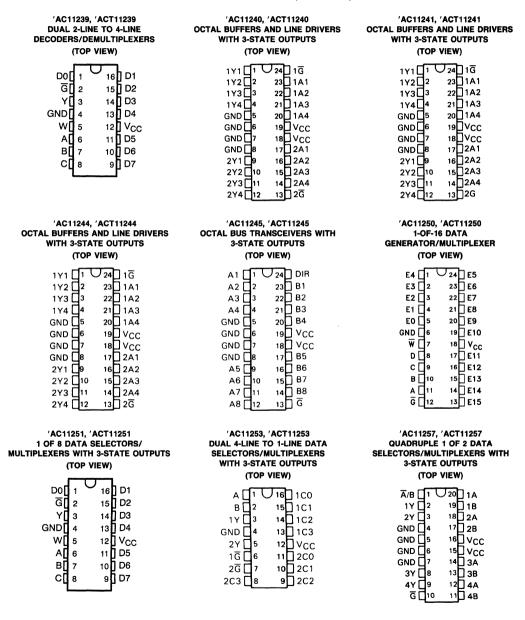

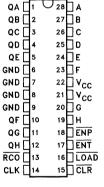

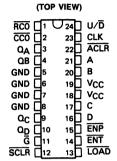

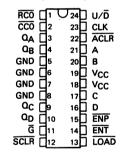

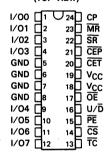

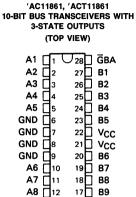

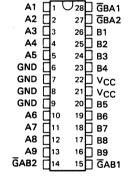

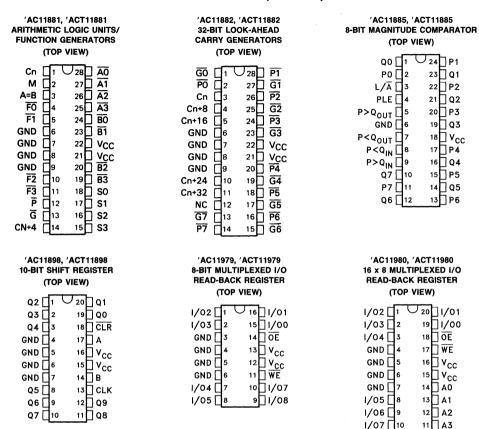

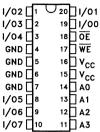

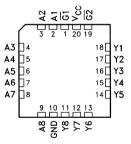

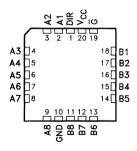

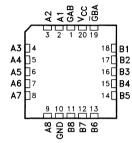

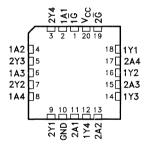

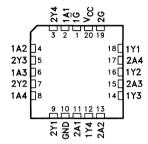

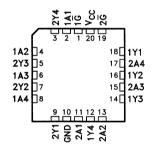

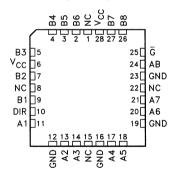

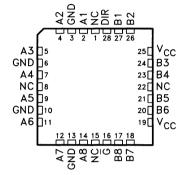

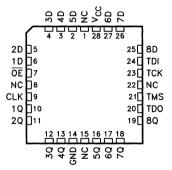

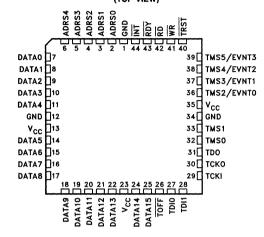

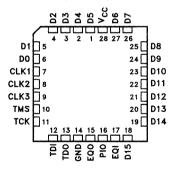

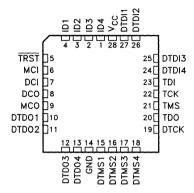

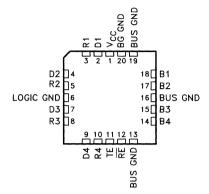

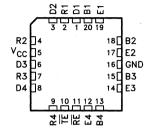

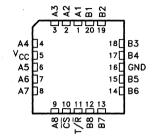

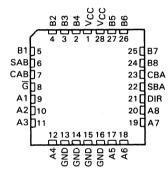

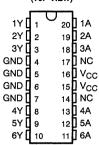

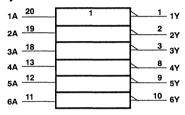

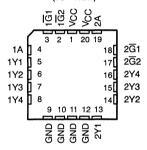

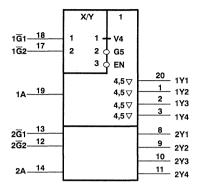

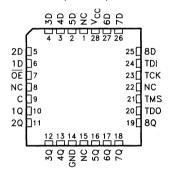

| Device Pin-Outs                        |      |

| TYPE NU                 | JMBERS                  | DATA<br>SHEET  | PIN<br>ASSIGNMENTS | TYPE NUMBERS             |                          | DATA<br>SHEET | PIN<br>ASSIGNMENTS |

|-------------------------|-------------------------|----------------|--------------------|--------------------------|--------------------------|---------------|--------------------|

| ACL LSI                 |                         |                |                    | 54AC16824                | 74AC16824                | 3-135         | 1-91               |

| 54AC11646               | 74AC11646               | 2-3            | 1-68               | 54ACT16824               | 74ACT16824               | 3-135         | 1-91               |

| 54ACT1646               | 74ACT1646<br>74ACT11646 | 2-3<br>2-11    | 1-68<br>1-68       | 54AC16827                | 74AC16827                | 3-137         | 1-92               |

|                         |                         |                |                    | 54ACT16827               | 74ACT16827               | 3-137         | 1-92               |

| 54AC11648<br>54ACT11648 | 74AC11648<br>74ACT11648 | 2-18<br>2-25   | 1-68               | 54AC16828                | 74AC16828                | 3-138         | 1-92               |

|                         |                         |                | 1-68               | 54ACT16828               | 74ACT16828               | 3-138         | 1-92               |

| 54AC11651<br>54ACT11651 | 74AC11651               | 2-31<br>2-39   | 1-68               | 54AC16833                | 74AC16833                | 3-139         | 1-92               |

| 54AC111651<br>54AC11652 | 74ACT11651<br>74AC11652 | 2-39<br>2-45   | 1-68<br>1-68       | 54ACT16833               | 74ACT16833               | 3-139         | 1-92               |

| 54ACT11652              | 74ACT1052               | 2-43           |                    | 54AC16834                | 74AC16834                | 3-141         | 1-93               |

| 54AC111833              | 74AC111632<br>74AC11833 | 2-53<br>2-60   | 1-68<br>1-71       | 54ACT16834               | 74ACT16834               | 3-141         | 1-93               |

| 54ACT11833              | 74ACT1833               | 2-66           | 1-71               | 54AC16841                | 74AC16841                | 3-143         | 1-93               |

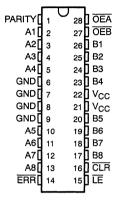

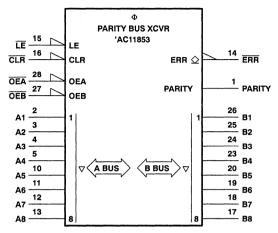

| 54AC11853               | 74AC111853              | 2-72           | 1-73               | 54ACT16841               | 74ACT16841               | 3-143         | 1-93               |

| 54ACT11853              | 74ACT1853               | 2-72           | 1-73               | 54AC16842                | 74AC16842                | 3-145         | 1-93               |

| 54AC111873              | 74AC111873              | 2-75           | 1-75               | 54ACT16842               | 74ACT16842               | 3-145         | 1-93               |

| 54ACT11873              | 74ACT1073               | 2-00           | 1-75               | 54AC16843                | 74AC16843                | 3-147         | 1-94               |

| 54AC111874              | 74AC111873              | 2-91           | 1-75               | 54ACT16843               | 74ACT16843               | 3-147         | 1-94               |

| 54ACT11874              | 74ACT1874               | 2-90           | 1-75               | 54AC16844                | 74AC16844                | 3-149         | 1-94               |

| 54AC11881               | 74AC111874<br>74AC11881 | 2-101          |                    | 54ACT16844               | 74ACT16844               | 3-149         | 1-94               |

| 54ACT1881               | 74ACT1661<br>74ACT11881 | 2-105<br>2-116 | 1-76<br>1-76       | 54AC16853                | 74AC16853                | 3-151         | 1-94               |

|                         |                         | 2-110          | 1-70               | 54ACT16853               | 74ACT16853               | 3-151         | 1-94               |

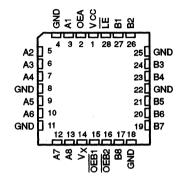

| ACL WIDEBUS             |                         |                |                    | 54AC16854                | 74AC16854                | 3-153         | 1-95               |

| 54AC16240               | 74AC16240               | 3-3            | 1-78               | 54ACT16854               | 74ACT16854               | 3-153         | 1-95               |

| 54ACT16240              | 74ACT16240              | 3-8            | 1-78               | 54AC16861                | 74AC16861                | 3-155         | 1-95               |

| 54AC16244               | 74AC16244               | 3-12           | 1-79               | 54ACT16861               | 74ACT16861               | 3-155         | 1-95               |

| 54ACT16244              | 74ACT16244              | 3-16           | 1-79               | 54AC16862                | 74AC16862                | 3-157         | 1-95               |

| 54AC16245               | 74AC16245               | 3-20           | 1-79               | 54ACT16862               | 74ACT16862               | 3-157         | 1-95               |

| 54ACT16245              | 74ACT16245              | 3-25           | 1-79               | 54AC16863                | 74AC16863                | 3-159         | 1-96               |

| 54AC16373               | 74AC16373               | 3-29           | 1-80               | 54ACT16863               | 74ACT16863               | 3-159         | 1-96               |

| 54ACT16373              | 74ACT16373              | 3-33           | 1-80               | 54AC16864                | 74AC16864                | 3-161         | 1-96               |

| 54AC16374               | 74AC16374               | 3-37           | 1-80               | 54ACT16864               | 74ACT16864               | 3-161         | 1-96               |

| 54ACT16374              | 74ACT16374              | 3-42           | 1-81               | 54AC16952                | 74AC16952                | 3-163         | 1-96               |

| 54AC16470               | 74AC16470               | 3-46           | 1-81               | 54ACT16952               | 74ACT16952               | 3-163         | 1-96               |

| 54ACT16470              | 74ACT16470              | 3-46           | 1-81               | 54AC16953                | 74AC16953                | 3-165         | 1-97               |

| 54AC16471               | 74AC16471               | 3-48           | 1-81               | 54ACT16953               | 74ACT16953               | 3-165         | 1-97               |

| 54ACT16471              | 74ACT16471              | 3-48           | 1-81               | 25-OHM LOW-II            |                          |               |                    |

| 54AC16472               | 74AC16472               | 3-50           | 1-82               | !                        |                          |               | 4.440              |

| 54ACT16472              | 74ACT16472              | 3-50           | 1-82               | 54BCT25240               | 74BCT25240               | 9-3           | 1-112              |

| 54AC16473               | 74AC16473               | 3-52           | 1-82               | 54BCT25244               | 74BCT25244               | 9-4           | 1-112              |

| 54ACT16473              | 74ACT16473              | 3-52           | 1-82               | 54BCT25245               | 74BCT25245               | 9-5           | 1-112              |

| 54AC16474               | 74AC16474               | 3-54           | 1-82               | 54BCT25641               | 74BCT25641               | 9-10          | 1-112              |

| 54ACT16474              | 74ACT16474              | 3-54           | 1-82               | 54BCT25642               | 74BCT25642               | 9-12          | 1-113              |

| 54AC16475               | 74AC16475               | 3-56           | 1-83               | 54BCT25646               | 74BCT25646               | 9-16          | 1-113              |

| 54ACT16475              | 74ACT16475              | 3-56           | 1-83               | 54BCT25648<br>54BCT25651 | 74BCT25648<br>74BCT25651 | 9-18          | 1-114              |

| 54AC16543               | 74AC16543               | 3-58           | 1-84               | 54BCT25652               |                          | 9-20<br>9-22  | 1-114              |

| 54ACT16543              | 74ACT16543              | 3-62           | 1-85               | 54BCT25756               | 74BCT25652<br>74BCT25756 | 9-22<br>9-24  | 1-114<br>1-114     |

| 54AC16620               | 74AC16620               | 3-67           | 1-86               | 54BCT25757               | 74BCT25756<br>74BCT25757 | 9-24          |                    |

| 54ACT16620              | 74ACT16620              | 3-72           | 1-85               | 54BCT25760               | 74BCT25760               | 9-25          | 1-114<br>1-114     |

| 54AC16640               | 74AC16640               | 3-77           | 1-86               | i                        | 7460123760               | 9-20          | 1-114              |

| 54ACT16640              | 74ACT16640              | 3-82           | 1-87               | SCOPE                    |                          |               |                    |

| 54AC16646               | 74AC16646               | 3-86           | 1-87               | SN54BCT8244              | SN74BCT8244              | 11-195        | 1-115              |

| 54ACT16646              | 74ACT16646              | 3-93           | 1-87               | SN54BCT8245              | SN74BCT8245              | 11-212        | 1-115              |

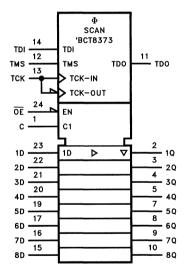

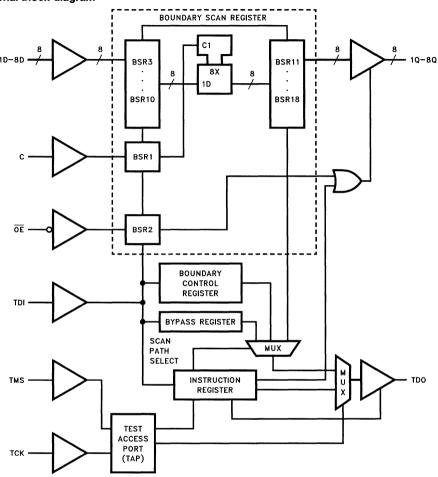

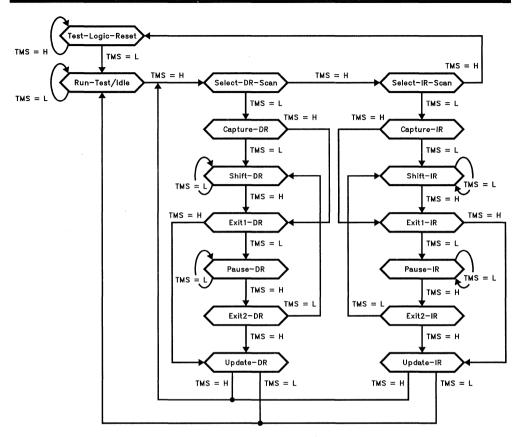

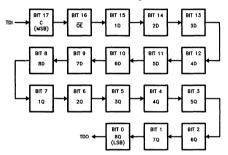

| 54AC16652               | 74AC16652               | 3-101          | 1-88               | SN54BCT8373              | SN74BCT8373              | 11-231        | 1-116              |

| 54ACT16652              | 74ACT16652              | 3-108          | 1-89               | SN54BCT8374              | SN74BCT8374              | 11-248        | 1-116              |

| 54AC16657               | 74AC16657               | 3-115          | 1-89               | SN54ACT8990              | SN74ACT8990              | 11-3          | 1-117              |

| 54ACT16657              | 74ACT16657              | 3-122          | 1-89               | SN54ACT8994              | SN74ACT8994              | 11-86         | 1-117              |

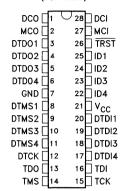

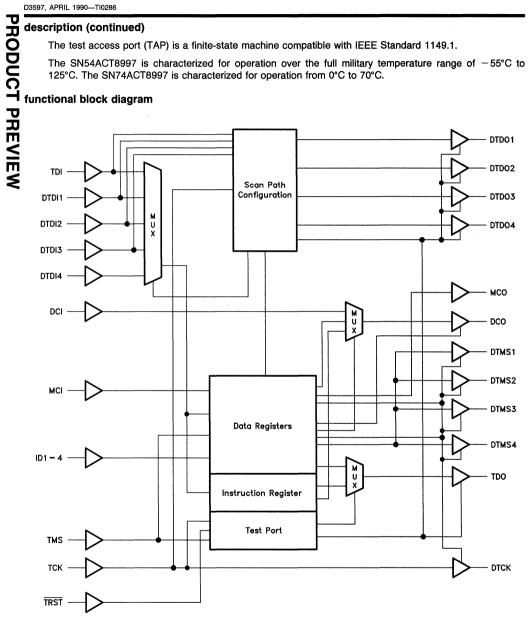

| 54AC16821               | 74AC16821               | 3-129          | 1-90               | SN54ACT8997              | SN74ACT8997              | 11-143        | 1-117              |

| 54ACT16821              | 74ACT16821              | 3-129          | 1-90               | SN54ACT8999              | SN74ACT8999              | 11-166        | 1-118              |

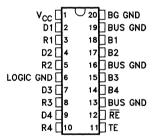

| 54AC16822               | 74AC16822               | 3-131          | 1-90               | 64BCT                    |                          |               |                    |

| 54ACT16822              | 74ACT16822              | 3-131          | 1-90               | SN64BCT125               |                          | 12-3          | 1-119              |

| 54AC16823               | 74AC16823               | 3-133          | 1-90               | SN64BCT126               |                          | 12-6          | 1-119              |

| 54ACT16823              | 74ACT16823              | 3-133          | 1-90               | 1 3.13.53.120            |                          |               |                    |

#### **NUMERICAL INDEX**

| TYPE NUMBERS 64BCT (continued) |                         | DATA<br>SHEET / | PIN<br>ASSIGNMENTS | TYPE N        | UMBERS           | DATA<br>SHEET | PIN<br>ASSIGNMENTS |

|--------------------------------|-------------------------|-----------------|--------------------|---------------|------------------|---------------|--------------------|

|                                |                         |                 |                    | ECL/TTL TRANS | SLATORS (continu | ed)           |                    |

| SN64BCT240                     |                         | 12-9            | 1-119              |               | SN10KHT5540      | 7-21          | 1-100              |

| SN64BCT241                     |                         | 12-12           | 1-119              |               | SN100KT5540      | 7-26          | 1-100              |

| SN64BCT244                     |                         | 12-15           | 1-119              |               | SN10KHT5541      | 7-31          | 1-100              |

| SN64BCT245                     |                         | 12-18           | 1-119              |               | SN100KT5541      | 7-36          | 1-100              |

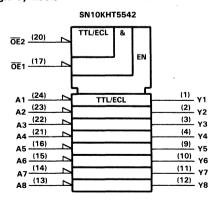

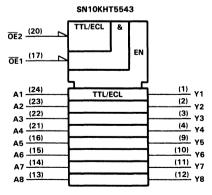

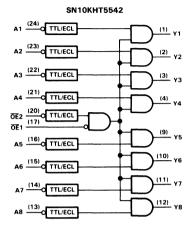

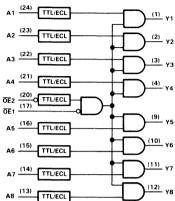

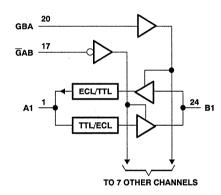

| SN64BCT306                     |                         | 12-21           | 1-120              | SN10KHT5542   | SN10KHT5543      | 7-42          | 1-100              |

| SN64BCT373                     |                         | 12-24           | 1-120              | SN10KHT5562   | SN100KT5562      | 7-47          | 1-100              |

| SN64BCT374                     |                         | 12-28           | 1-120              | SN10KHT5563   | SN100KT5563      | 7-48          | 1-101              |

| SN64BCT541                     |                         | 12-32           | 1-120              | SN10KHT5564   | SN100KT5564      | 7-49          | 1-101              |

| SN64BCT543                     |                         | 12-35           | 1-120              | SN10KHT5565   | SN100KT5565      | 7-50          | 1-101              |

| SN64BCT2240                    |                         | 12-36           | 1-120              |               | SN10KHT5573      | 7-51          | 1-101              |

| SN64BCT2241                    |                         | 12-37           | 1-121              |               | SN100KT5573      | 7-57          | 1-101              |

| SN64BCT2244                    |                         | 12-38           | 1-121              |               | SN10KHT5574      | 7-62          | 1-101              |

| SN64BCT25245                   |                         | 12-39           | 1-121              |               | SN100KT5574      | 7-68          | 1-101              |

| BTL TRANSCE                    | VFRS                    |                 |                    |               | SN10KHT5575      | 7-74          | 1-101              |

| SN54F776                       | SN74F776                | 4-40            | 1-122              |               | SN10KHT5576      | 7-76          | 1-102              |

| SN54F776<br>SN54BCT979         | SN74F776<br>SN74BCT979  | 4-40            | 1-122              |               | SN10KHT5578      | 7-78          | 1-102              |

| SN34BC1979                     |                         |                 |                    |               | SN100KT5578      | 7-83          | 1-102              |

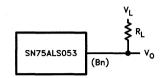

| SN55ALS056                     | SN75ALS053              | 4-3<br>4-10     | 1-122              | FIFOs         |                  |               |                    |

| SINDOALSUOD                    | CNIZE AL COEC           | 4-10<br>4-21    | 1-123<br>1-123     | SN54ACT2235   | CNIZAACTOOOF     | 8-3           | 4 407              |

| ONIEE AL COE7                  | SN75ALS056              |                 |                    |               | SN74ACT2235      |               | 1-107              |

| SN55ALS057                     | ONIZE AL COEZ           | 4-10            | 1-123              | SN54ACT7801   | SN74ACT7801      | 8-13          | 1-105              |

|                                | SN75ALS057              | 4-21            | 1-123              | SN54ACT7802   | SN74ACT7802      | 8-27          | 1-106              |

| BUS TERMINAT                   | ION ARRAYS DEVI         | CE              |                    | SN54ALS229B   | SN74ALS229B      | 8-36          | 1-103              |

|                                | SN74S1050               | 5-3             | 1-125              | SN54ALS232B   | SN74ALS232B      | 8-42          | 1-103              |

|                                | SN74S1051               | 5-8             | 1-125              | SN54ALS233A   | SN74ALS233B      | 8-46          | 1-103              |

|                                | SN74S1052               | 5-13            | 1-125              | SN54ALS234    | SN74ALS234       | 8-52          | 1-103              |

|                                | SN74S1053               | 5-18            | 1-125              | SN54ALS235    | SN74ALS235       | 8-60          | 1-103              |

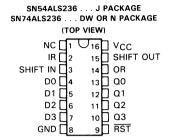

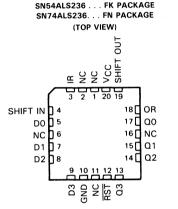

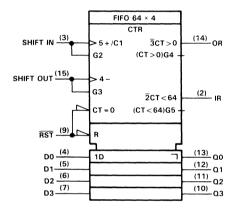

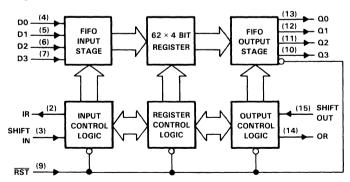

|                                | SN74S1056               | 5-23            | 1-125              | SN54ALS236    | SN74ALS236       | 8-72          | 1-104              |

| CLOCK DRIVER                   | ns.                     |                 |                    |               | SN74ALS2232A     | 8-80          | 1-104              |

| SN54ABT337                     | SN74ABT337              | 6-3             | 1-98               |               | SN74ALS2233A     | 8-85          | 1-104              |

| 3N34AB1337                     | 74AC11204               | 6-8             | 1-98               | SN54ALS2238   | SN74ALS2238      | 8-91          | 1-104              |

| 54AC11208                      | 74AC11204<br>74AC11208  | 6-13            | 1-98               | MEMORY DRIVE  | ERS              |               |                    |

| 54ACT1208                      |                         | 6-20            | 1-98               | SN54ALS2240   |                  | 10-3          | 1-108              |

| 54AC111206<br>54AC11800        | 74AC11800               | 6-28            | 1-98               | SN54ALS2244   |                  | 10-6          | 1-108              |

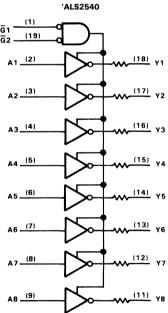

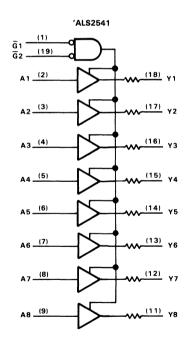

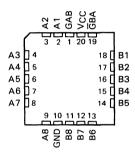

| 54ACT1800                      |                         | 6-30            | 1-98               | SN74ALS2540   | SN74ALS2541      | 10-9          | 1-108              |

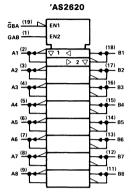

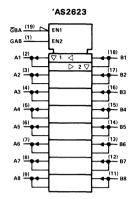

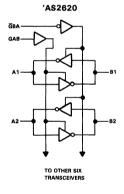

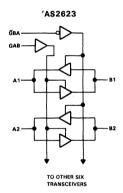

| 54AC111800<br>54AC11802        |                         |                 |                    | SN74AS2620    | SN74AS2623       | 10-13         | 1-109              |

| 54ACT11802<br>54ACT11802       | 74AC11802<br>74ACT11802 | 6-33<br>6-37    | 1-99<br>1-99       | SN74AS2640    | SN74AS2645       | 10-17         | 1-109              |

| 54AC111602                     |                         |                 | 1-99               | SN74BCT2240   |                  | 10-21         | 1-109              |

|                                | SN74AS303               | 6-40            |                    | SN74BCT2241   |                  | 10-25         | 1-110              |

|                                | SN74AS304               | 6-45            | 1-99               | SN74BCT2244   |                  | 10-29         | 1-110              |

|                                | SN74AS305               | 6-50            | 1-99               | SN74BCT2410   |                  | 10-33         | 1-111              |

| ECL/TTL TRAN                   | SLATORS                 |                 |                    | SN74BCT2411   |                  | 10-34         | 1-111              |

|                                | SN10KHT5538             | 7-3             | 1-100              | SN54BCT2827A  | 74BCT2827A       | 10-35         | 1-110              |

|                                | SN100KT5538             | 7-7             | 1-100              | SN54BCT2828A  |                  | 10-35         | 1-110              |

|                                | SN10KHT5539             | 7-11            | 1-100              | 3.10.20.20207 |                  |               |                    |

|                                | SN100KT5539             | 7-16            | 1-100              |               |                  |               |                    |

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

#### C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device.

#### Co Output capacitance

The internal capacitance at an output of the device.

#### C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{pd} V_{CC}^2 f + I_{CC} V_{CC}$ .

#### fmax Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

#### ICC Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit.

#### ΔICC Supply current change (ACT devices only)

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or VCC.

#### I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input.

#### IIL Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

#### IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

#### IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

#### IOZ Off-state (high-impedance-state) output current (of a three-state output)

The current flowing into\* an output having three-state capability with input conditions established that, according to the production specification, will establish the high-impedance state at the output.

<sup>\*</sup>Current out of a terminal is given as a negative value.

#### ta Access time

The time interval between the application of a specified input pulse and the availability of valid signals at an output.

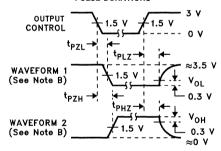

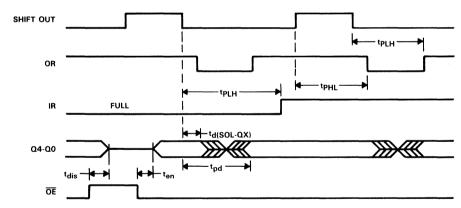

#### Disable time (of a three-state or open-collector output) tdis

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

NOTE: For 3-state outputs, tdis = tpHz or tpl z. Open-collector outputs will change only if they are low at the time of disabling so this = tpl H.

#### ten Enable time (of a three-state or open-collector output)

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low).

NOTE: In the case of memories, this is the access time from an enable input (e.g., G). For 3state outputs, ten = tpzH or tpzL. Open-collector outputs will change only if they are responding to data that would cause the output to go low so, for them, ten = tpHI.

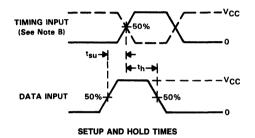

#### Hold time th

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is quaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

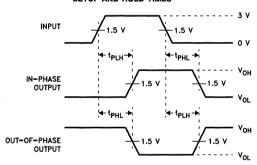

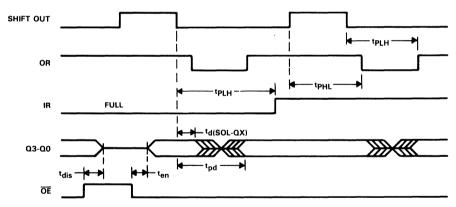

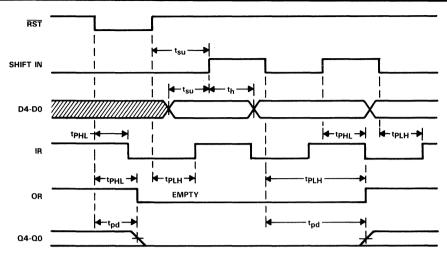

#### Propagation delay time tpd

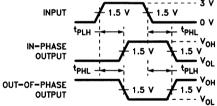

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. (tpd = tpHI or tpi H).

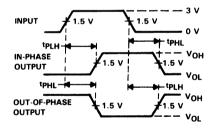

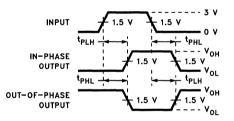

#### **tPHL** Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

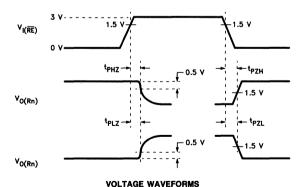

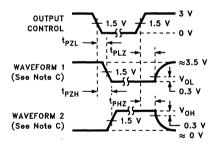

#### tPHZ Disable time (of a three-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

#### tpLH Propagation delay time, low-to-high-level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

#### tpLZ Disable time (of a three-state output) from low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

#### tрун Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

#### tpzL Enable time (of a three-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

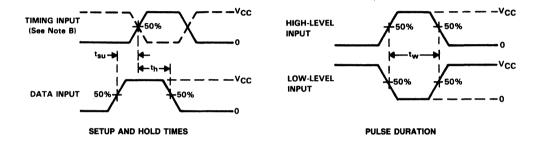

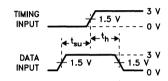

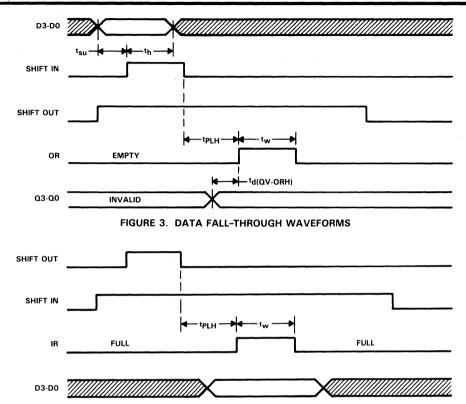

#### t<sub>SU</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

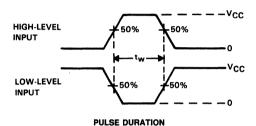

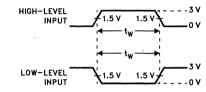

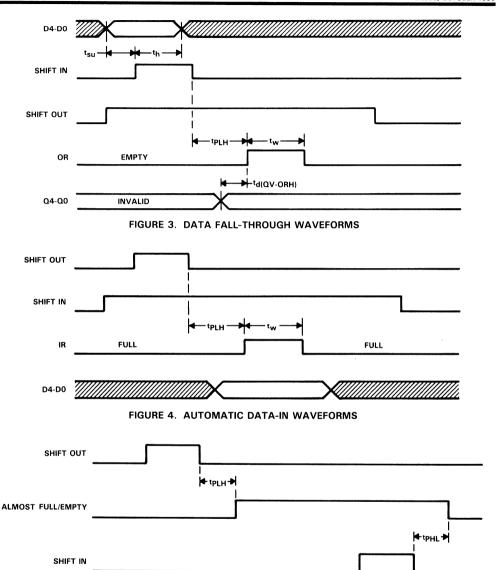

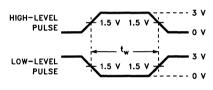

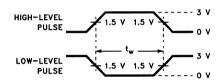

#### t<sub>w</sub> Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

#### VIH High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### V<sub>IL</sub> Low-level input voltage

An input voltage level within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

#### GLOSSARY SYMBOLS, TERMS, AND DEFINITIONS

#### VOH High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

#### VOL Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

#### V<sub>T+</sub> Positive-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage,  $V_{T-}$ .

#### V<sub>T</sub> — Negative-going threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{\rm T}$  +.

#### **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

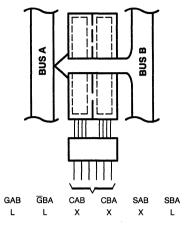

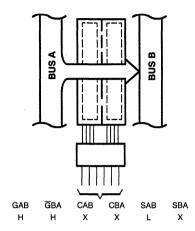

H = high level (steady state)

L = low level (steady state)

= transition from low to high level

→ = value/level or resulting value/level is routed to indicated destination

= value/level is re-entered

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state-output

a..h = the level of steady-state inputs at inputs A through H respectively

Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

$\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input conditions were established

$Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

□ = one low-level pulse

TOGGLE = each output changes to the complement of its previous level on each active transition indicated by  $\downarrow$  or  $\uparrow$ .

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L,  $Q_0$ , or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\Box$  or  $\Box$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

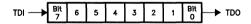

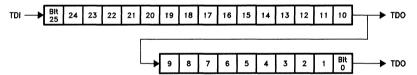

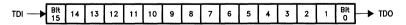

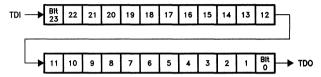

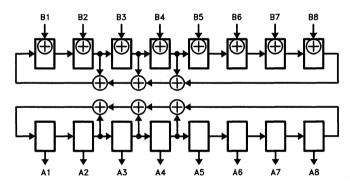

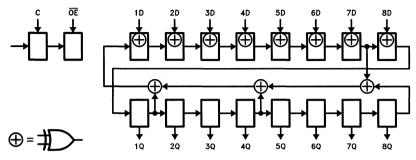

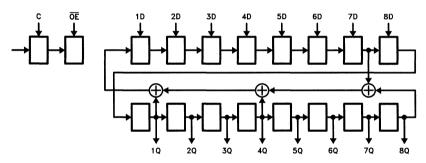

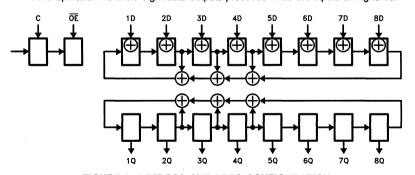

Among the most complex function tables in this book are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

#### **FUNCTION TABLE**

|       | INPUTS |    |       |      |       |   |     |     | OUT | PUTS            |                 |          |          |

|-------|--------|----|-------|------|-------|---|-----|-----|-----|-----------------|-----------------|----------|----------|

| CLEAD | MO     | DE | CLOCK | SE   | RIAL  | P | ARA | LLE | L   | ٥.              | Λ-              | ^-       | ^-       |

| CLEAR | S1     | SO | CLOCK | LEFT | RIGHT | Α | В   | С   | D   | QA              | QB              | QC       | QD       |

| L     | Х      | Х  | Х     | Х    | Х     | Х | Х   | Х   | Х   | L               | L               | L        | L        |

| Н     | Х      | Х  | L     | Х    | Х     | Х | Х   | Χ   | Х   | Q <sub>A0</sub> | Q <sub>B0</sub> | $Q_{C0}$ | $Q_{D0}$ |

| н     | Н      | Н  | 1     | х    | X     | а | b   | С   | d   | а               | b               | С        | ď        |

| н     | L      | Н  | 1     | х    | н     | Х | Х   | Χ   | Х   | Н               | QAn             | $Q_{Bn}$ | QCn      |

| н     | L      | Н  | 1     | ×    | L     | Х | Χ   | Χ   | Χ   | L               | $Q_{An}$        | $Q_{Bn}$ | QCn      |

| н     | н      | L  | 1     | н    | X     | Х | Х   | Χ   | Χ   | QBn             | QCn             | $Q_{Dn}$ | Н        |

| н     | н      | L  | . 1   | L    | X     | Х | Х   | Χ   | Х   | QBn             | QCn             | $Q_{Dn}$ | L        |

| н     | L      | L  | ×     | ×    | Х     | Х | Х   | Х   | Х   | Q <sub>A0</sub> | $Q_{B0}$        | $Q_{C0}$ | $Q_{D0}$ |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output QA, data entered at B will be at QB, and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$  respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is not at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

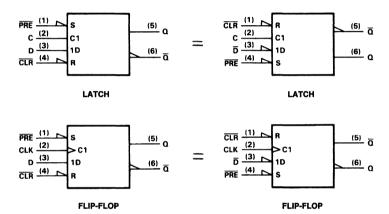

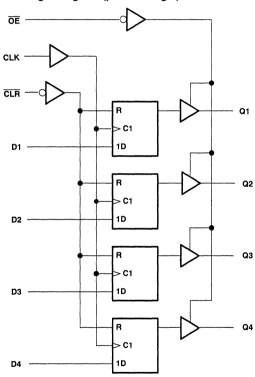

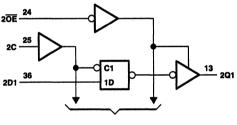

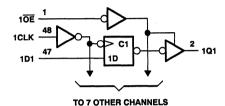

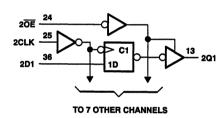

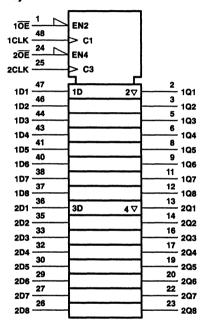

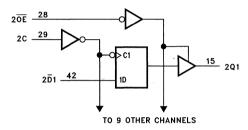

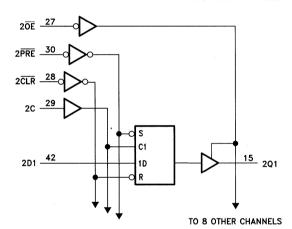

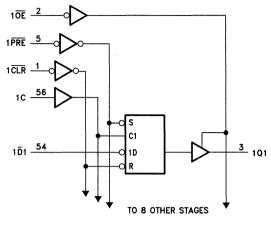

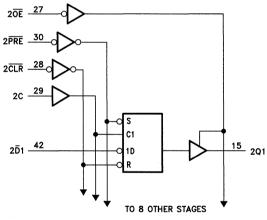

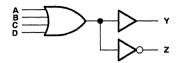

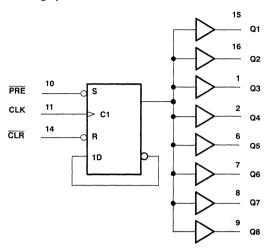

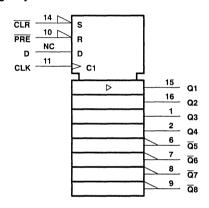

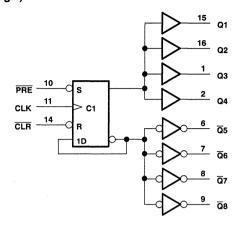

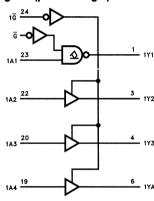

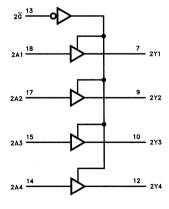

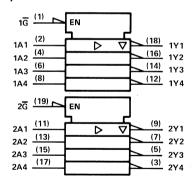

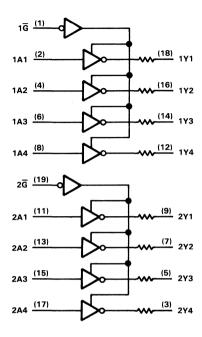

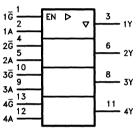

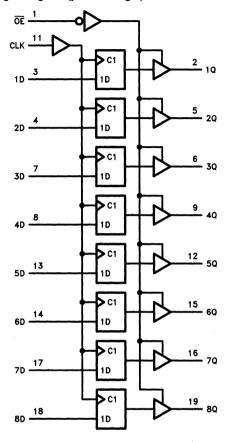

#### D flip-flop and latch signal conventions

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called  $\overline{Q}$  and those producing complementary data are called  $\overline{Q}$ . An input that causes a  $\overline{Q}$  output to go high or a  $\overline{Q}$  output to go low is called Preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a  $\overline{Q}$  output to go low is called Clear (CLR). Bars are used over these pin names (PRE and CLR) if they are active-low.

The devices on several data sheets are second-source designs, and the pin-name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits  $\overline{D}$  and Q.

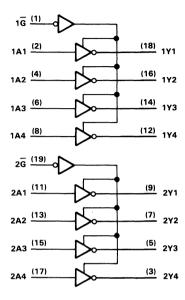

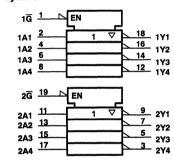

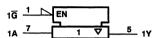

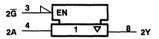

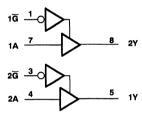

In some applications, it may be advantageous to redesignate the data input from D to  $\overline{D}$  or vice versa. In that case, all the other inputs and outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown in parentheses.

The figures show that when Q and  $\overline{Q}$  exchange names, the Preset and Clear pins also exchange names. The polarity indicators ( $\blacktriangleright$ ) on  $\overline{PRE}$  and  $\overline{CLR}$  remain, as these inputs are still active-low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

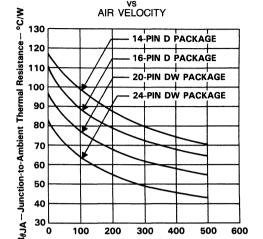

In digital system design, consideration must be given to thermal management of components. The small size of the "small outline" package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the EPIC™ ACL family. In general, the junction temperature for any device can be calculated using Equation 1.

$$T_{.I} = R_{\theta.IA} \times P_T + T_A \tag{1}$$

#### where

T.i virtual junction temperature

$R_{\theta,1A}$  = thermal resistance, junction to free air

total power dissipation of the device

ТΔ free-air temperature

The total power consumption can be determined from Equation 2 for an AC device and Equation 3 for an ACT device.

JUNCTION-TO-AMBIENT THERMAL RESISTANCE

FIGURE 1

300

Air Velocity - Feet/Min

400

500

600

$$P_{T} = V_{CC} \times I_{CC} + (C_{pd} \times V_{CC}^{2} \times f_{i}) + \Sigma (C_{L} \times V_{CC}^{2} \times f_{o})$$

(2)

30

100

$$P_{T} = V_{CC} \times [I_{CC} + (N \times \Delta I_{CC} \times dc)] + (C_{pd} \times V_{CC}^{2} \times f_{i}) + \Sigma (C_{L} \times V_{CC}^{2} \times f_{o})$$

(3)

#### where

V<sub>CC</sub> = supply voltage (5 V for typical, 5.5 V for maximum) see Note 1

ICC = quiescent supply current (specified on device data sheet)

C<sub>nd</sub> = Power dissipation capacitance (from the device data sheet)

fi = input frequency

C<sub>I</sub> = output load capacitance

f<sub>0</sub> = output frequency

N = number of inputs driven by a TTL device

dc = duty cycle

$\Delta I_{CC}$  = increase in supply current (specified on device data sheet)

NOTE 1: In system applications I<sub>CC</sub> can be minimized by keeping input voltage levels less than 1 V for V<sub>IL</sub> and greater than V<sub>CC</sub> – 1 V for V<sub>IH</sub> and input rise and fall times less than 15 ns.

EPIC is a trademark of Texas Instruments Incorporated.

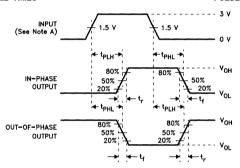

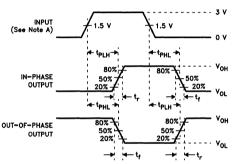

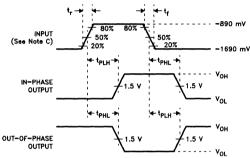

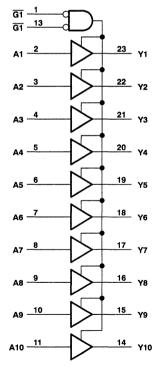

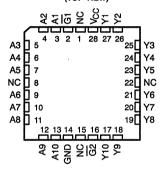

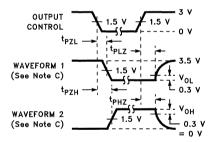

#### SERIES 54AC11XXX AND 74AC11XXX DEVICES SERIES 54AC16XXX AND 74AC16XXX DEVICES

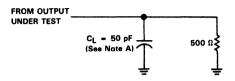

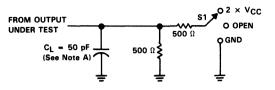

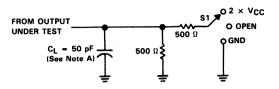

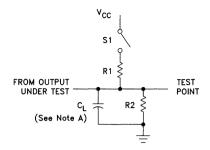

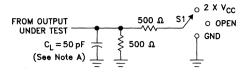

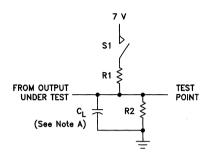

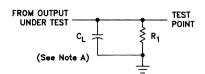

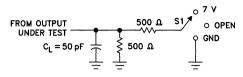

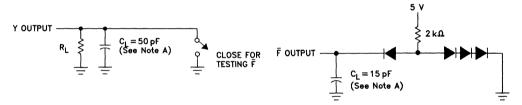

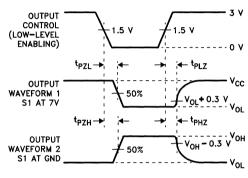

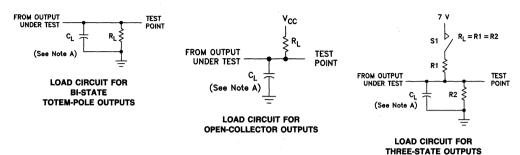

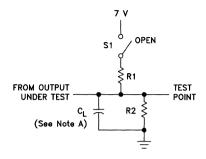

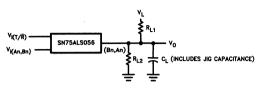

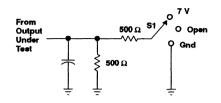

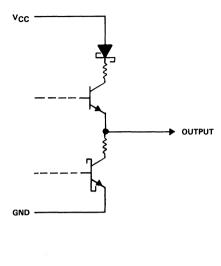

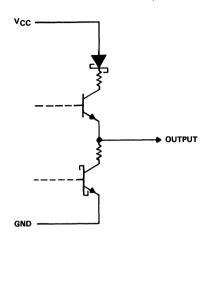

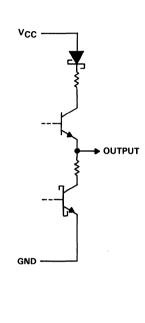

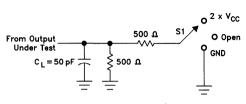

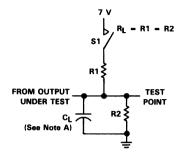

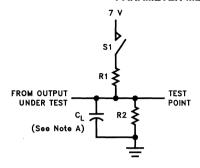

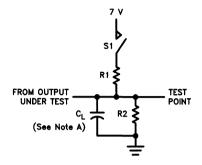

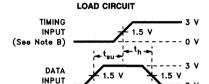

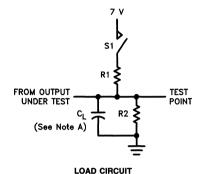

#### LOAD CIRCUIT FOR TOTEM-POLE OUTPUTS

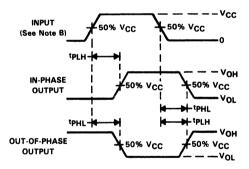

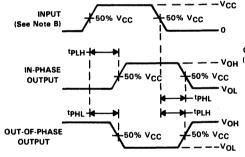

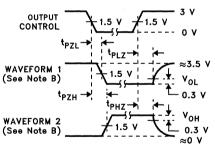

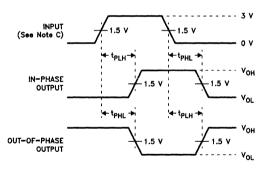

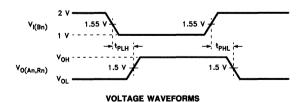

#### PROPAGATION DELAY TIMES

NOTES: A. CL includes probe and jig capacitance.

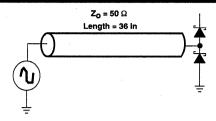

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50~\Omega$ ,  $t_f = 3~ns$ ,  $t_f = 3~ns$ . For testing pulse duration:  $t_f = 1$  to 3 ns,  $t_f = 1$  to 3 ns. Pulse polarity can be either a high-to-low-to-high or low-to-high-to-low. C. The outputs are measured one at a time with one input transition per measurement.

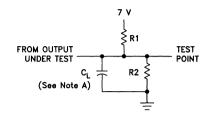

## SERIES 54AC11XXX AND 74AC11XXX DEVICES SERIES 54AC11XXX AND 74AC11XXX DEVICES

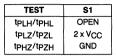

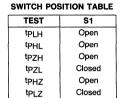

| TEST      | S1                  |

|-----------|---------------------|

| tPLH/tPHL | OPEN                |

| tPLZ/tPZL | 2 × V <sub>CC</sub> |

| tPHZ/tPZH | GND                 |

|           |                     |

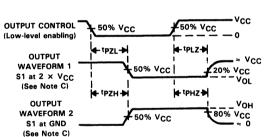

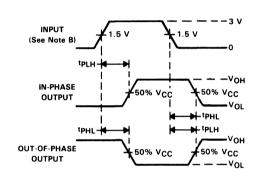

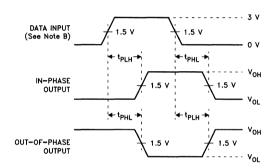

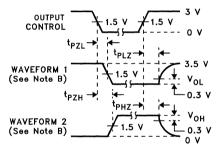

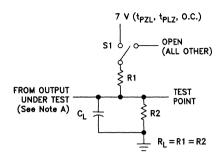

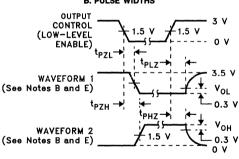

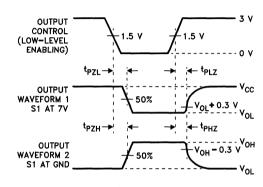

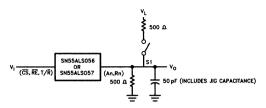

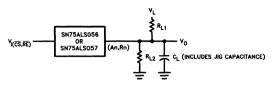

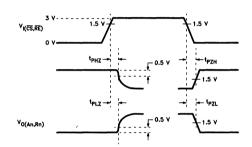

#### LOAD CIRCUIT FOR THREE-STATE OUTPUTS

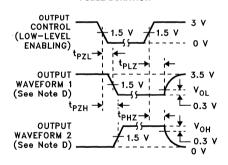

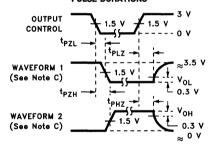

#### PROPAGATION DELAY TIMES

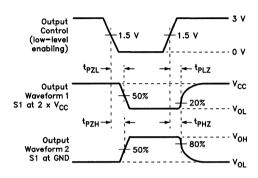

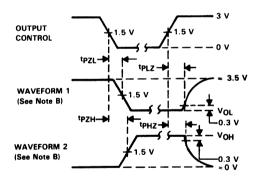

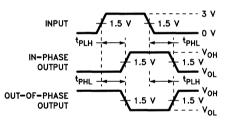

#### ENABLE AND DISABLE TIMES

NOTES: A. Cl includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f = 3$  ns,  $t_f = 3$  ns. For testing pulse duration:  $t_f = 1$  to 3 ns,  $t_f = 1$  to 3 ns. Pulse polarity can be either a high-to-low-to-high or low-to-high-to-low.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

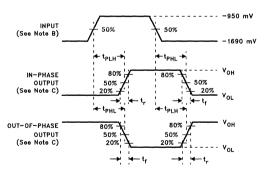

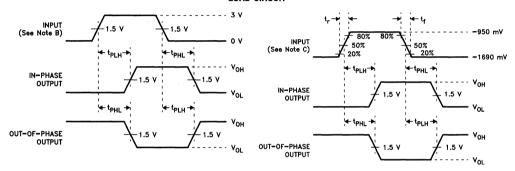

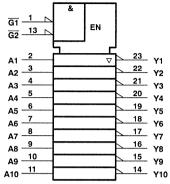

## SERIES 54ACT11XXX AND 74ACT11XXX DEVICES SERIES 54ACT16XXX AND 74ACT16XXX DEVICES

LOAD CIRCUIT FOR TOTEM-POLE OUTPUTS

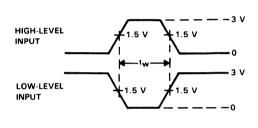

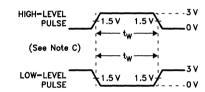

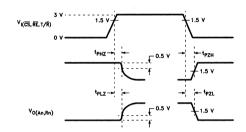

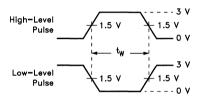

#### **PULSE DURATION**

PROPAGATION DELAY TIMES

NOTES: A. C. includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \ \Omega$ ,  $t_f = 3 \ ns$ ,  $t_f = 3 \ ns$ . For testing pulse duration:  $t_f = 1 \ to 3 \ ns$ ,  $t_f = 1 \ to 3 \ ns$ . Pulse polarity can be either a high-to-low-to-high or low-to-high-to-low.

- C. The outputs are measured one at a time with one input transition per measurement.

## SERIES 54ACT11XXX AND 74ACT11XXX DEVICES SERIES 54ACT16XXX AND 74ACT16XXX DEVICES

| TEST      | S1      |

|-----------|---------|

| tplH/tpHL | OPEN    |

| tPLZ/tPZL | 2 × VCC |

| tPHZ/tPZH | GND     |

|           |         |

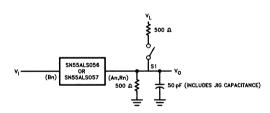

**ENABLE AND DISABLE TIMES**

#### LOAD CIRCUIT FOR THREE-STATE OUTPUTS

NOTES: A. C. includes probe and jig capacitance.

PROPAGATION DELAY TIMES

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f = 3$  ns,  $t_f = 3$  ns. For testing pulse duration:  $t_f = 1$  to 3 ns,  $t_f = 1$  to 3 ns. Pulse polarity may be either a high-to-low-to-high or low-to-high-to-low.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

--Val

OUTPUT

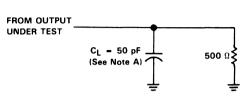

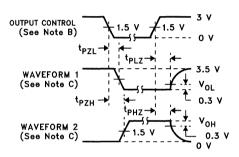

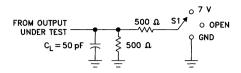

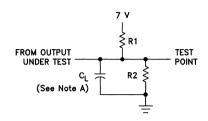

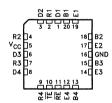

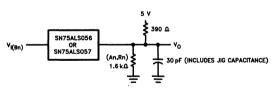

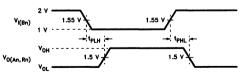

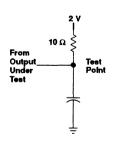

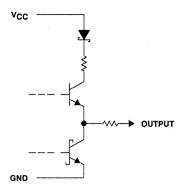

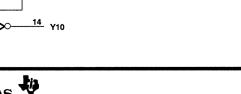

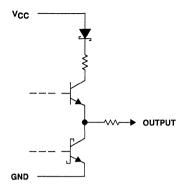

#### SERIES SN54BCT25XXX AND SN74BCT25XXX DEVICES

#### LOAD CIRCUIT

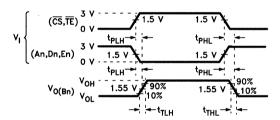

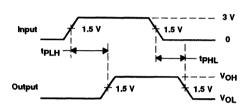

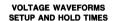

## VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

NOTES: A. CL includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f = 3 \text{ ns}$ ,  $t_f = 1 \text{ to } 3 \text{ ns}$ . For testing pulse duration:  $t_f = 1 \text{ to } 3 \text{ ns}$ ,  $t_f = 1 \text{ to } 3 \text{ ns}$ . Pulse polarity can be either a high-to-low-to-high or low-to-high-to-low.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

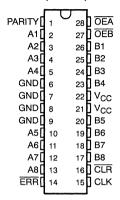

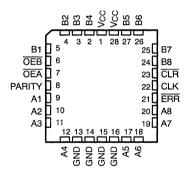

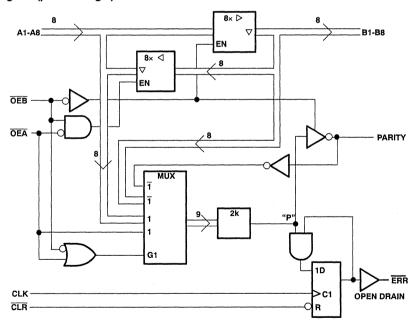

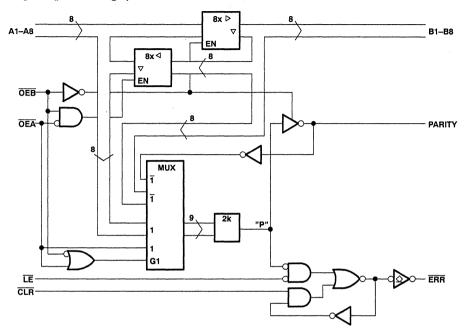

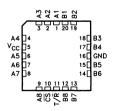

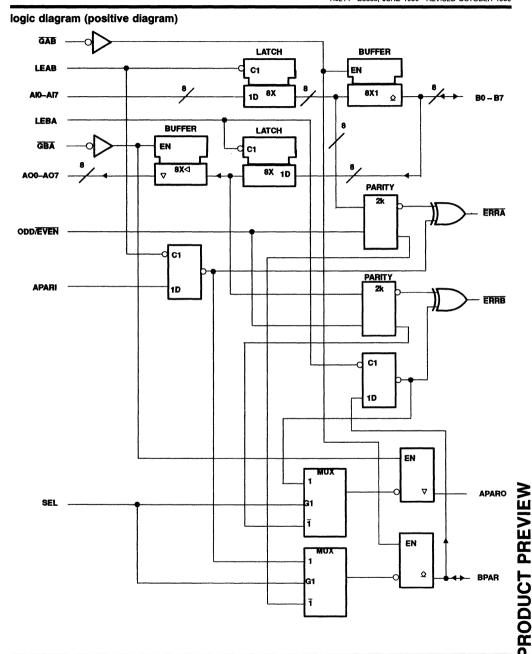

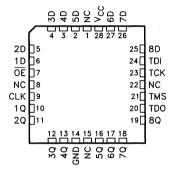

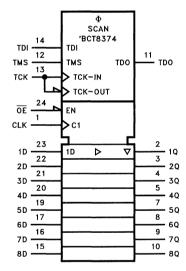

#### SERIES SN54BCT8XXX AND SN74BCT8XXX DEVICES

#### LOAD CIRCUIT 1 ALL OUTPUTS EXCEPT FOR ERROR FLAG

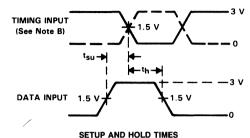

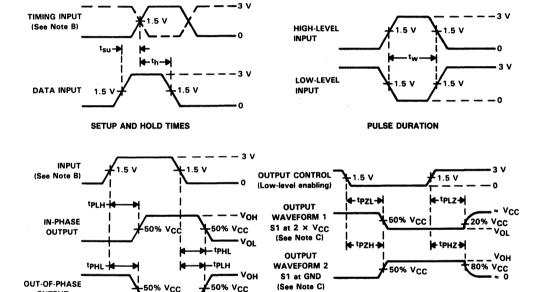

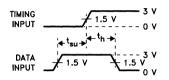

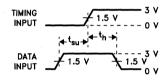

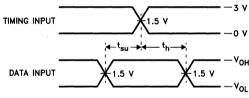

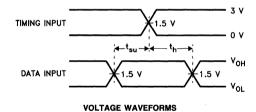

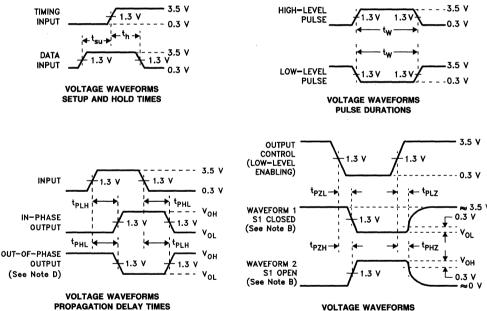

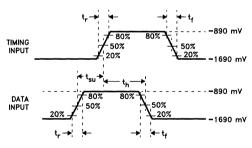

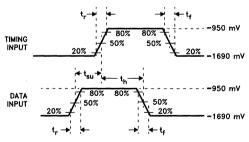

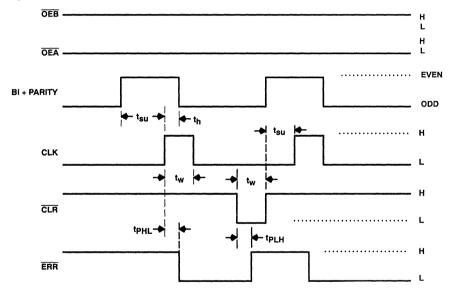

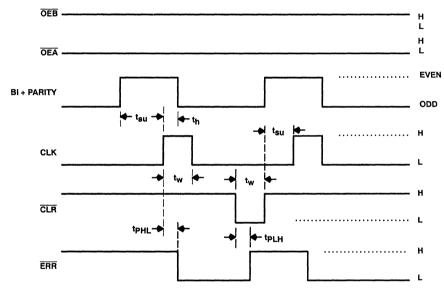

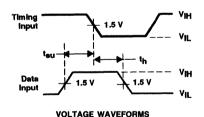

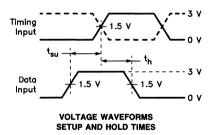

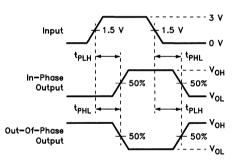

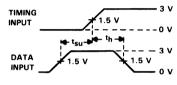

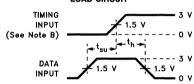

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

## VOLTAGE WAVEFORMS PULSE DURATIONS

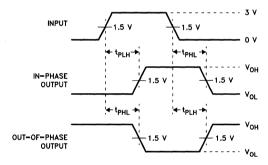

## VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

NOTES: A. CL includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0=50~\Omega$ ,  $t_f\leq$  2.5 ns,  $t_f\leq$  2.5 ns.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

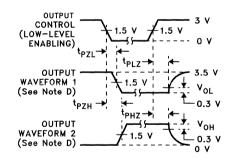

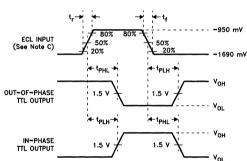

#### SERIES SN54ACT8XXX AND SN74ACT8XXX DEVICES

#### LOAD CIRCUIT

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

## VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

#### SWITCH POSITION TABLE

| TEST      | S1                  |

|-----------|---------------------|

| tPLH/tPHL | Open                |

| tPLZ/tPZL | 2 x V <sub>CC</sub> |

| tPHZ/tPZH | GND                 |

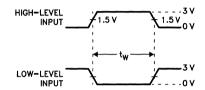

## VOLTAGE WAVEFORMS PULSE DURATIONS

VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz, Z $_{O}$  = 50  $\Omega,$  tr $_{f}$  = 3 ns, tf $_{f}$  = 3 ns.

- D. The outputs are measured one at a time with one input transition per measurement.

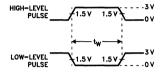

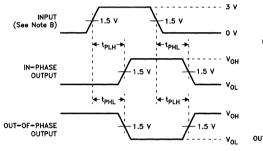

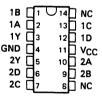

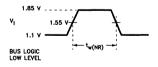

#### **SERIES SN64BCT8XXX DEVICES**

#### LOAD CIRCUIT 1 ALL OUTPUTS EXCEPT FOR ERROR FLAG

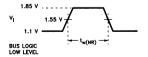

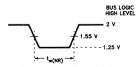

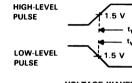

## LOW-LEVEL 1.5 V 1.

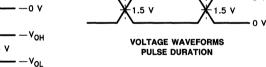

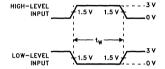

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

#### VOLTAGE WAVEFORMS PULSE DURATIONS

## VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

## VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES, 3-STATE OUTPUTS

- NOTES: A. CL includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq$  2.5 ns,  $t_f \leq$  2.5 ns.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

VOH

VOL

D. The outputs are measured one at a time with one input transition per measurement.

OUT-OF-PHASE

OUTPUT

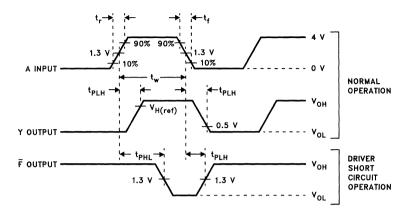

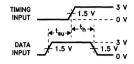

#### SERIES SN54FXXX AND SN74FXXX DEVICES

FIGURE 1. LOAD CIRCUIT FOR TOTEM-POLE OUTPUTS

## FIGURE 2. LOAD CIRCUIT FOR THREE STATE AND OPEN-COLLECTOR OUTPUTS

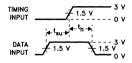

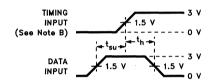

#### A. SETUP AND HOLD TIMES

1.5

nν

TIMING

INPUT

DATA

INPUT

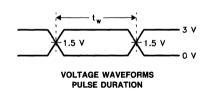

#### B. PULSE WIDTHS

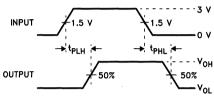

#### C. PROPAGATION DELAY TIMES

#### D. THREE-STATE OUTPUT ENABLE TIMES

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics; PRR = 1 MHz,  $t_f=t_f\leq 2.5$  ns, duty cycle = 50%.

- D. When measuring propagation delay times of three-state outputs, switch S1 is open.

- E. The outputs are measured one at a time with one input transition per measurement.

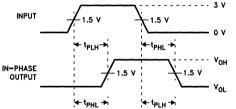

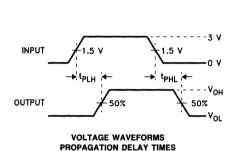

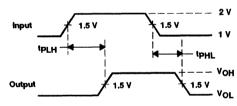

#### SERIES SN54BCTXXX AND SN74BCTXXX DEVICES

#### LOAD CIRCUIT FOR OUTPUTS

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES

- 3 V

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

- NOTES: A. CL includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O=50~\Omega$ ,  $t_f=2.5~ns$ ,  $t_f=2.5~ns$ .

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

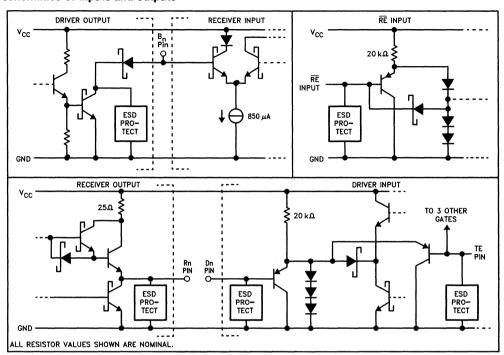

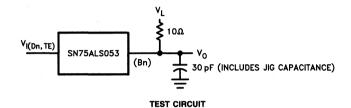

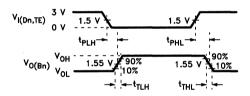

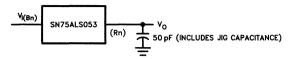

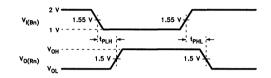

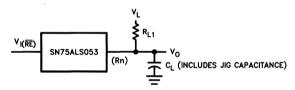

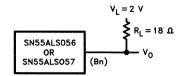

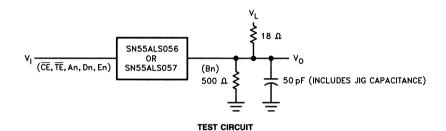

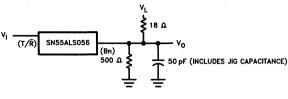

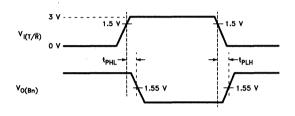

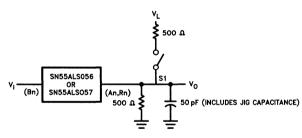

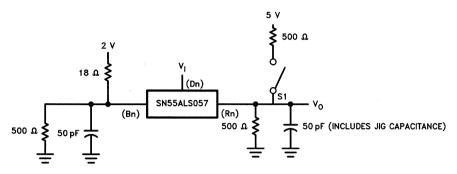

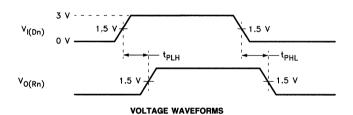

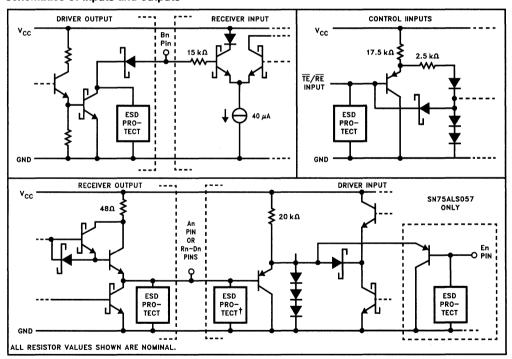

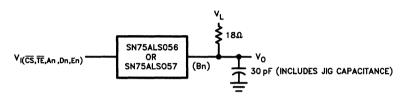

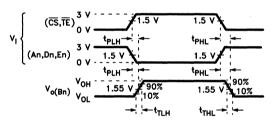

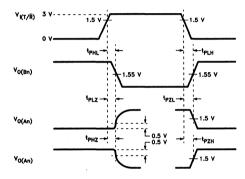

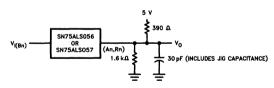

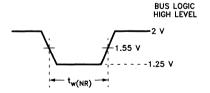

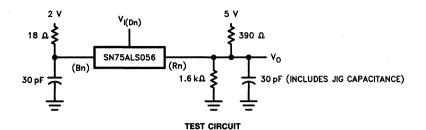

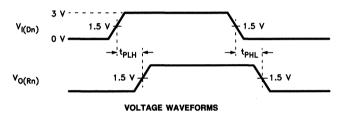

#### SERIES SN55ALSXXX AND SN75ALSXXX DEVICES

NOTE: A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, duty cycle = 50%,  $t_{\text{f}} \le 6$  ns,  $t_{\text{f}} \ge 6$  ns,  $t_{\text{f}} \le 6$  ns,  $t_{\text{f}} \ge 6$  ns,  $t_{f$

NOTE: A. CL includes probe and stray capacitance.

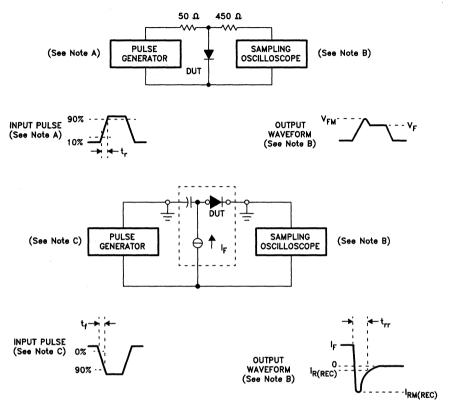

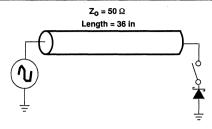

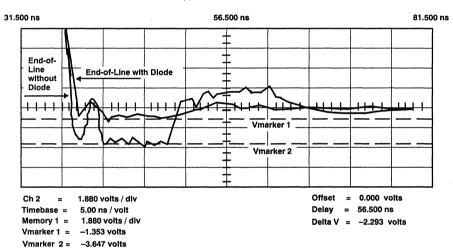

#### SERIES SN54S10XX AND SN74S10XX DEVICES

NOTES: A. The input pulse is supplied by a pulse generator having the following characteristics:  $t_r = 20$  ns,  $Z_{OUt} = 50 \Omega$ ,  $f_{PR} = 500$  Hz, duty cycle = 0.01.

B. The output waveform is monitored by an oscilloscope having the following characteristics:  $t_r \le 350$  ps,  $R_{in} = 50 \Omega$ ,  $C_{in} = \le 5$  pF.

C. The input pulse is supplied by a pulse generator having the following characteristics: t<sub>f</sub> = 0.5 ns, Z<sub>out</sub> = 50 Ω, t<sub>w</sub> = ≤ 50 ns, duty cylce ≤ 0.01.

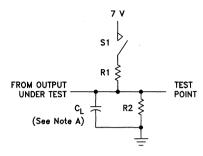

#### SERIES SN54ABTXXX AND SN74ABTXXX DEVICES

| TEST      | S1   |

|-----------|------|

| tPLH/tPHL | OPEN |

| tPLZ/tPZL | 7 V  |

| tPHZ/tPZH | GND  |

LOAD CIRCUIT FOR OUTPUTS

VOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES

SETUP AND HOLD TIMES

### NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. Input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O=50~\Omega$ ,  $t_f=2.5~ns$ ,  $t_f=2.5~ns$ .

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. The outputs are measured one at a time with one input transition per measurement.

#### SERIES SN54ASXXX AND SN74ASXXX DEVICES

NOTE: A. C<sub>1</sub> includes probe and jig capacitance.

### ENABLE AND DISABLE TIMES, THREE-STATE OUTPUTS

NOTES: B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_{\Gamma} = t_{\Gamma} = 2$  ns, duty cycle = 50%.

- D. When measuring propagation delay items of 3-state outputs, switch S1 is open.

- E. The outputs are measured one at a time with one input transition per measurement.

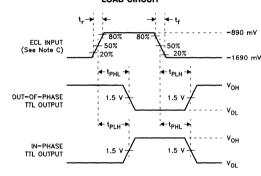

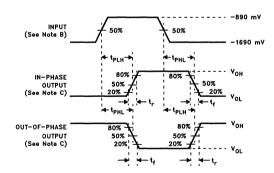

#### SERIES SN10KHT ECL-TO-TTL TRANSLATOR

#### SWITCH POSITION TABLE

| TEST | S1     |

|------|--------|

| tPLH | Open   |

| tPHL | Open   |

| tPZH | Open   |

| tPZL | Closed |

| tPHZ | Open   |

| tPLZ | Closed |

#### LOAD CIRCUIT

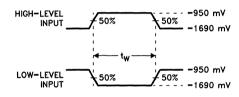

# HIGH-LEVEL 50% -890 mV -1690 mV LOW-LEVEL 50% 50% -890 mV -1690 mV

#### VOLTAGE WAVEFORMS PULSE DURATION

## VOLTAGE WAVEFORMS ECL-INPUT PROPAGATION DELAY TIMES

## VOLTAGE WAVEFORMS TTL ENABLE AND DISABLE TIMES

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

NOTES: A. CL includes probe and jig capacitance.

- B. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq$  2.5 ns.  $t_f \leq$  2.5 ns.

- C. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq$  1.5 ns,  $t_f \leq$  1.5 ns.

- D. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- E. The outputs are measured one at a time with one transition per measurement.

#### SERIES SN100KT ECL-TO-TTL TRANSLATOR

## SWITCH POSITION TABLE

| TEST             | \$1    |

|------------------|--------|

| tPLH             | Open   |

| tPHL             | Open   |

| tPZH             | Open   |

| tPZL             | Closed |

| t <sub>PHZ</sub> | Open   |

| tPLZ             | Closed |

#### LOAD CIRCUIT

## VOLTAGE WAVEFORMS PULSE DURATION

## VOLTAGE WAVEFORMS ECL-INPUT PROPAGATION DELAY TIMES

VOLTAGE WAVEFORMS

TTL ENABLE AND DISABLE TIMES

#### VOLTAGE WAVEFORMS SETUP AND HOLD TIMES

- NOTES: A. CL includes probe and jig capacitance.

- B. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq 2.5 \text{ ns.}$  tf  $\leq 2.5 \text{ ns.}$

- C. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq$  0.7 ns,  $t_f \leq$  0.7 ns.

- D. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- E. The outputs are measured one at a time with one transition per measurement.

#### SERIES SN100KT TTL-TO-ECL TRANSLATOR

#### **OUTPUT LOAD CIRCUIT**

#### SETUP AND HOLD TIMES

#### **PULSE DURATION**

#### TTL-INPUT PROPAGATION DELAY TIMES

#### **ECL-INPUT PROPAGATION DELAY TIMES**

NOTES: A. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq 2.5 \text{ ns}$ ,  $t_f \leq 2.5 \text{ ns}$ .

- B. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq 0.7$  ns,  $t_f \leq 0.7$  ns.

- C. Waveform 1 is for an output with internal conditions such that the output is high except when disabled by OE.

- D. The outputs are measured one at a time with one input transition per measurement.

#### SERIES SN10KHT OCTAL TTL-TO-ECL TRANSLATOR

#### **OUTPUT LOAD CIRCUIT**

#### SETUP AND HOLD TIMES

#### **PULSE DURATION**

#### TTL-INPUT PROPAGATION DELAY TIMES

#### **ECL-INPUT PROPAGATION DELAY TIMES**

NOTES: A. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z<sub>0</sub> = 50 Ω,  $t_r \le 2.5$  ns,  $t_f \le 2.5$  ns.

- B. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_{\Gamma} \leq$  1.5 ns,  $t_{f} \leq$  1.5 ns.

- C. Waveform 1 is for an output with internal conditions such that the output is high except when disabled by OE.

- D. The outputs are measured one at a time with one input transition per measurement.

#### SERIES SN10KHT ECL-TO-TTL TRANSLATORS WITH OPEN-COLLECTOR OUTPUTS

#### LOAD CIRCUIT

#### TTL-INPUT PROPAGATION DELAY TIMES

#### **ECL-INPUT PROPAGATION DELAY TIMES**

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq 2.5 \text{ ns. } t_f \leq 2.5 \text{ ns.$

- C. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_f \leq$  1.5 ns,  $t_f \leq$  1.5 ns.

- D. The outputs are measured one at a time with one transition per measurement.

#### SERIES SN10KT ECL-TO-TTL TRANSLATORS WITH OPEN-COLLECTOR OUTPUTS

#### LOAD CIRCUIT

#### **VOLTAGE WAVEFORMS** TTL-INPUT PROPAGATION DELAY TIMES

#### **VOLTAGE WAVEFORMS ECL-INPUT PROPAGATION DELAY TIMES**

NOTES: A. CL includes probe and jig capacitance.

- B. For TTL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_r \le 2.5$  ns,  $t_f \le 2.5$  ns.

- C. For ECL inputs, input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_{f} \leq$  0.7 ns,  $t_{f} \leq$  0.7 ns.

- D. The outputs are measured one at a time with one transition per measurement.

The following tables outline the logic functions Texas Instruments offers in a variety of technologies. The tables are organized by function type, and list all options available or planned of that function. The technology columns identify the appropriate family and identify a particular data book, where more information can be found. The applicable literature number, composed of either seven or eight digits, can be found on the back cover at the lower right-hand corner of each publication.

#### List of Applicable Data Books:

| AC and ACT Devices         | Advanced CMOS Logic Data Book        | SCAD001B |

|----------------------------|--------------------------------------|----------|

| Advanced Logic             | Advanced Logic and Bus               | SCYD001  |

| Devices                    | Interface Logic Data Book            |          |

| AS and ALS Devices         | ALS/AS Logic Data Book               | SDAD001B |

| BCT Devices                | BiCMOS Bus Interface Logic Data Book | SCBD001A |

| F Devices                  | F Logic (54/75F) Data Book           | SDFD001A |

| HC and HCT Devices         | High-Speed CMOS Logic Data Book      | SCLD001C |

| Std TTL, LS, and S Devices | Standard TTL Logic Data Book         | SDLD001A |

#### Contents

|                                              | Page |

|----------------------------------------------|------|

| GATES                                        | 1-35 |

| Positive-NAND Gates                          | 1-35 |

| Positive-AND Gates                           | 1-36 |

| Positive-OR/NOR Gates                        | 1-36 |

| OR/NOR Gates                                 | 1-37 |

| AND/NOR Gates                                | 1-37 |

| Hex Inverters/noninverters                   | 1-37 |

| BUFFER/DRIVERS AND BUS TRANSCEIVERS          | 1-38 |

| Drivers                                      | 1-38 |

| Bus Transceivers                             | 1-39 |

| MOS Memory Drivers/Transceivers              | 1-41 |

| TESTABILITY BUS INTERFACE CIRCUITS           | 1-42 |

| SCOPE™ Testability Circuits (3-State Output) | 1-42 |

| FLIP-FLOPS/LATCHES                           | 1-42 |

| Filip-Flops                                  | 1-42 |

| Latches                                      | 1-44 |

# Contents (continued)

|                                                              | Page |

|--------------------------------------------------------------|------|

| REGISTERS                                                    | 1-46 |

| Shift Registers                                              | 1-46 |

| Register Files                                               | 1-46 |

| COUNTERS                                                     | 1-47 |

| Synchronous Counters-Positive-Edge Triggered                 | 1-47 |

| Asynchronous Counters (Ripple Clock)-Negative-Edge Triggered | 1-48 |

| 8-Bit Binary Counters with Registers                         | 1-48 |

| DECODERS, ENCODERS, DATA SELECTORS/MULTIPLEXERS              | 1-49 |

| Encoders/Data Selectors/Multiplexers                         | 1-49 |

| Decoders/Demultiplexers                                      | 1-50 |

| Shifters                                                     | 1-50 |

| COMPARATORS AND PARITY GENERATORS                            | 1-51 |

| Comparators                                                  | 1-51 |

| Address Comparators                                          | 1-52 |

| Parity Generators/Checkers                                   | 1-52 |

| Fuse-Programmable Comparators                                | 1-52 |

| ARITHMETIC CIRCUITS AND FIFO MEMORIES                        | 1-53 |

| Parallel Binary Adders                                       | 1-53 |

| Accumulators, Arithmetic Logic Units, Look-Ahead Carry       |      |

| Generators                                                   | 1-53 |

| First-In First-Out Memories (FIFOs)                          | 1-53 |

| CLOCK DRIVER CIRCUITS                                        | 1-54 |

| Clock Driver                                                 | 1-54 |

| ECL TRANSLATORS                                              | 1-54 |

| ECL-to-TTL or TTL-to-ECL Translators                         | 1-54 |

#### **GATES**

#### **Positive-NAND Gates**

| DECODIDETON    |        |        |     |    |                                                  |    | TECHNOL | .OGY     |          |     |     |

|----------------|--------|--------|-----|----|--------------------------------------------------|----|---------|----------|----------|-----|-----|

| DESCRIPTION    | OUTPUT | TYPE   | ALS | AS | F                                                | HC | HCT     | AC       | ACT      | BCT | ABT |

| 8-Input        |        | ′30    | •   | •  | •                                                | •  |         |          |          |     |     |

|                |        | 11030  |     |    |                                                  |    |         | •        | •        |     |     |

| 13-Input       |        | ′133   | •   |    |                                                  | •  |         |          |          |     |     |

| Dual 2-Input   |        | '8003  | •   |    |                                                  |    |         |          |          |     |     |

| Dual 4-Input   |        | ′11013 |     |    |                                                  |    | •       |          | <b>A</b> |     |     |

|                |        | ′20    | •   | •  | •                                                | •  |         |          |          |     |     |

|                |        | ′40    | •   |    | •                                                |    |         |          |          |     |     |

|                |        | ′1020  | •   |    |                                                  |    |         |          |          |     |     |

|                |        | ′11020 |     |    | <del>                                     </del> |    |         | •        | •        |     |     |

| Triple 3-Input |        | ′10    | •   | •  | •                                                | •  |         |          |          |     |     |

|                |        | ′1010  | •   |    |                                                  |    |         |          |          |     |     |

|                |        | ′11010 |     |    |                                                  |    |         | •        | •        |     |     |

| Quad 2-Input   |        | ′00    | •   | •  | •                                                | •  | •       |          |          |     |     |

|                |        | ′11000 |     |    |                                                  |    |         | •        | •        |     |     |

|                |        | '37    | •   |    | •                                                |    |         |          | <u> </u> |     |     |

|                | oc     | '38    | •   |    | •                                                |    |         |          | <u> </u> |     |     |

|                |        | ′132   |     |    |                                                  | •  |         |          |          |     |     |

|                |        | 111132 |     |    |                                                  |    |         | <b>A</b> | <b>A</b> |     |     |

|                |        | ′1000  | •   | •  |                                                  |    |         |          |          |     |     |

| Hex 2-Input    |        | '804   | •   | •  |                                                  |    |         |          |          |     |     |

|                |        | ′1804  | •   | •  |                                                  |    |         |          |          |     |     |

| Dual 4-Input   | ОС     | '22    | •   |    |                                                  |    |         |          |          |     |     |

| Triple 3-Input | ОС     | ′12    | •   |    |                                                  |    |         |          |          |     |     |

| Quad 2-Input   | oc     | ′01    | •   |    |                                                  | •  |         |          |          |     |     |

|                | ОС     | ′03    | •   |    | 1                                                | •  |         |          |          |     |     |

|                | ОС     | ′1003  | •   |    |                                                  |    |         |          |          |     |     |

|                |        |        |     |    |                                                  |    |         |          |          |     |     |

- Product available in technology indicated

New Product planned in technology indicated

# **GATES** (continued)

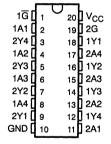

#### **Positive-AND Gates**

| DECODIDATION   | OUTDUT | TVDE   |     |    |   |    | TECHNOL | .OGY |     |     |     |

|----------------|--------|--------|-----|----|---|----|---------|------|-----|-----|-----|

| DESCRIPTION    | OUTPUT | TYPE   | ALS | AS | F | HC | HCT     | AC   | ACT | BCT | ABT |

| Triple 3-Input | ОС     | ′15    | •   |    |   |    |         |      |     |     |     |

| Quad 2-Input   | ОС     | ′09    | •   |    | • | •  |         |      |     |     |     |

|                |        | ′7001  |     |    |   | •  |         |      |     |     |     |

| Dual 4-Input   |        | ′21    | •   | •  | • | •  |         |      |     |     |     |

|                |        | ′11021 |     |    |   |    |         | •    | •   |     |     |

| Triple 3-Input |        | '11    | •   | •  | • | •  |         |      |     |     |     |

|                |        | ′11011 |     |    |   |    |         | •    | •   |     |     |

| Quad 2-Input   |        | ′08    | •   | •  | • | •  | •       |      |     |     |     |

|                |        | ′1008  | •   | •  |   |    |         |      |     |     |     |

|                |        | ′11008 |     |    |   |    |         | •    | •   |     |     |

| Hex 2-Input    |        | ′808   | •   | •  |   | •  |         |      |     |     |     |

|                |        | ′1808  | •   | •  |   |    |         |      |     |     |     |

#### Positive-OR/NOR Gates

| DECODINE       |        |        |     |    |   |    | TECHNOL | .OGY |     |     |     |

|----------------|--------|--------|-----|----|---|----|---------|------|-----|-----|-----|

| DESCRIPTION    | OUTPUT | TYPE   | ALS | AS | F | HC | HCT     | AC   | ACT | ВСТ | ABT |

| Triple 3-Input |        | '4075  |     |    |   | •  |         |      |     |     |     |

| Quad 2-Input   |        | ′32    | •   | •  | • | •  | •       |      |     |     |     |

|                |        | ′1032  | •   | •  |   |    |         |      |     |     |     |

|                |        | ′11032 |     |    |   | 1  |         | •    | •   |     |     |

| Quad 2-Input   |        | ′7032  |     |    |   | •  |         |      |     |     |     |

| Hex 2-Input    |        | ′832   | •   | •  |   | •  |         |      |     |     |     |

|                |        | ′1832  | •   | •  |   |    |         |      |     |     |     |

| Dual 4-Input   |        | '4002  |     |    |   | •  |         |      |     |     |     |

| Dual 5-Input   |        | ′260   |     |    | • |    |         |      |     |     |     |

| Triple 3-Input |        | '27    | •   | •  | • | •  |         |      |     |     |     |

|                |        | ′11027 |     |    |   |    |         | •    | •   |     |     |

| Quad 2-Input   |        | ′02    | •   | •  | • | •  | •       |      |     |     |     |

|                |        | ′28    | •   |    |   |    |         |      |     |     |     |

|                | ОС     | ′33    | •   |    |   |    |         |      |     |     |     |

|                |        | ′36    |     |    | • | •  |         |      |     |     |     |

|                |        | ′1002  | •   |    |   |    |         |      |     |     |     |

|                |        | ′1036  |     | •  | İ |    |         |      |     |     |     |

|                |        | ′7002  |     |    |   | •  |         |      |     |     |     |

|                |        | ′11002 |     |    |   |    |         | •    | •   |     |     |

| Hex 2-Input    |        | ′805   | •   | •  |   | •  |         |      |     |     |     |

|                |        | ′1805  | •   | •  |   |    |         |      |     |     |     |

- Product available in technology indicated

- ▲ New Product planned in technology indicated

# **GATES** (continued)

#### **OR/NOR Gates**

| DUCCELLEGA              |        |        |     |    |   |    | TECHNO | LOGY |     |     |     |

|-------------------------|--------|--------|-----|----|---|----|--------|------|-----|-----|-----|

| DESCRIPTION             | OUTPUT | TYPE   | ALS | AS | F | HC | HCT    | AC   | ACT | BCT | ABT |

| 8-Input                 |        | ′4078  |     |    |   | •  |        |      |     |     |     |

| Quad 2-Input            |        | ′86    | •   | •  | • | •  |        |      |     |     |     |

| Exclusive OR Gates with |        | ′11086 |     |    |   |    |        | •    | •   |     |     |

| Toten-Pole Outputs      |        | ′386   |     |    |   | •  |        |      | 1   |     |     |

| Quad 2-Input            | ОС     | ′136   | •   | •  |   |    |        |      |     |     |     |

| Exclusive OR Gates      |        |        |     |    |   |    |        |      |     |     |     |

| Quad 2-Input            |        | ′810   | •   | •  |   |    |        |      |     |     |     |

| Exclusive-NOR Gates     |        | ′7266  |     |    |   | •  |        |      |     |     |     |

| Quad 2-Input            | OC     | '811   | •   | •  |   |    |        |      |     |     |     |

| Exclusive-NOR Gates     |        |        |     |    |   |    |        |      |     |     |     |

#### **AND-NOR Gates**

| DESCRIPTION      | OUTDUT | TVDE   |     |    |   |    | TECHNOL | .OGY     |          |     |     |