# **Programmable Logic**

# Data Book

**Programmable Logic**

1993

1993

**General Information**

**Data Sheets**

2

**Application Reports**

3

**Qualification Data**

4

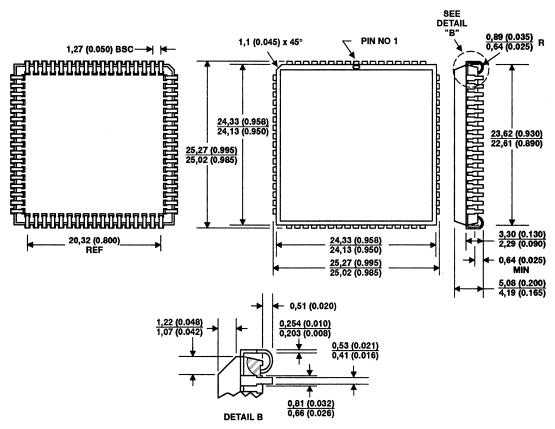

**Mechanical Data**

5

# The Programmable Logic Data Book

### IMPORTANT NOTICE

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1993, Texas Instruments Incorporated

## INTRODUCTION

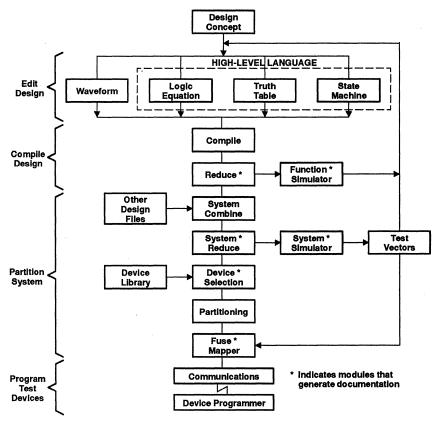

In this data book, Texas Instruments (TI) provides comprehensive information about TI's programmable logic devices (PLDs). These products have been developed to meet your performance and time to market requirements with efficient and effective products. TI offers over 40 PLD products in the standard architecture with speeds ranging from the low-power 25-ns to the high-speed 5-ns devices. TI also offers the flexible '22V10-architecture in the same speed range as the standard architecture product, including 5-ns tpd.

The 25-ns and 15-ns programmable bipolar devices utilize TI's IMPACT™ process while the high-speed bipolar devices utilize TI's IMPACT-X™ technologies. The IMPACT-X™ uses trench isolation and polysilicon emitters to increase performance. The IMPACT-XL™ process uses arsenic doped emitters and is optimized for low capacitance to achieve further improvements in performance.

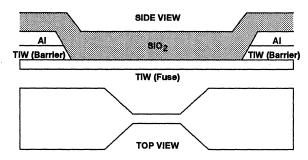

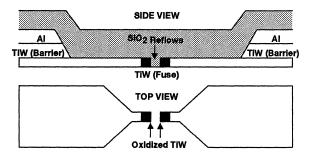

Besides the design and specifications data we have also included characterization data, packaging data, as well as process and die data to further assist you in designing with and qualifying TI's PLDs. All TI PLDs use a titanium-tungsten (TiW) fuse technology developed at TI to improve programming reliability.

Thank you for selecting Texas Instruments as your PLD supplier. If we can be of further assistance or if you require more information please contact your local TI field sales office, authorized distributor, or TI's PLD/FPGA Help Line at 214-997-5666.

IMPACT, IMPACT-X, and IMPACT-XL are trademarks of Texas Instruments Incorporated.

**General Information**

**Data Sheets**

2

**Application Reports**

3

**Qualification Data**

4

Mechanical Data

5

## **ALPHANUMERIC INDEX**

|                |                | Page  |                    |                     | Page  |

|----------------|----------------|-------|--------------------|---------------------|-------|

| EP330-12C      | EP330-25I      | 2-3   | TIBPAL20L8-15C     | TIBPAL20L8-20M      | 2-249 |

| EP330-15C      | EP330-251      | 2-3   |                    |                     |       |

|                |                |       |                    |                     |       |

| EP630-20C      | EP630-251      |       |                    |                     |       |

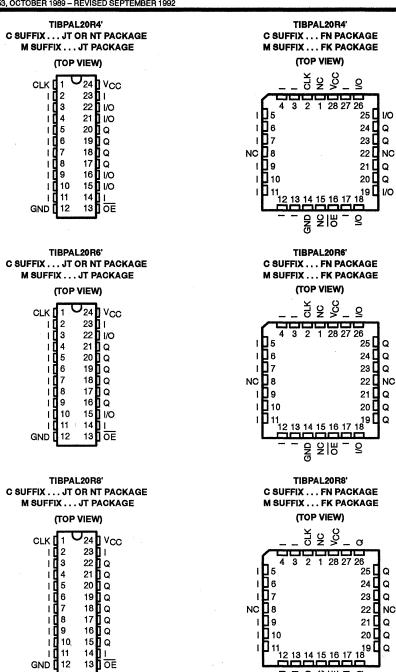

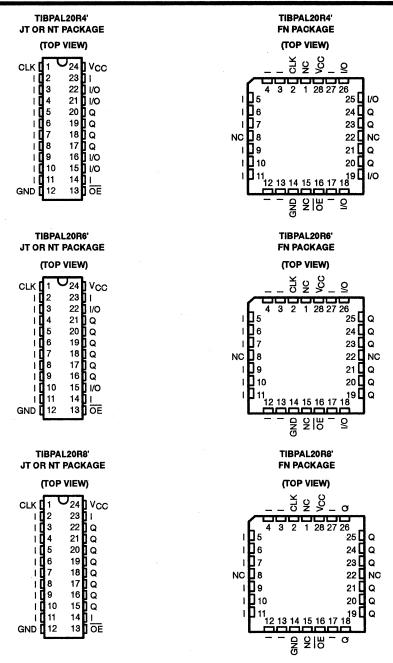

| EP1830-20C     | EP1830-25I     | 2-37  | TIBPAL20R4-5C      | TIBPAL20R4-7M       | 2-183 |

| EP1830-25C     | EP1830-30I     | 2-37  | TIBPAL20R4-7C      | TIBPAL20R4-10M      | 2-211 |

|                | PAL16L8AM      | 2-59  | TIBPAL20R4-10C     |                     | 2-231 |

|                | PAL16L8A-2M    | 2-59  | TIBPAL20R4-15C     | TIBPAL20R4-20M      | 2-249 |

|                | PAL16R4AM      | 2-59  | TIBPAL20R4-25C     |                     | 2-265 |

|                | PAL16R4A-2M    | 2-59  | TIBPAL20R4-15CNL . |                     | 2-279 |

|                | PAL16R6AM      | 2-59  | TIBPAL20R4-25CNL . |                     | 2-279 |

|                | PAL16R6A-2M    | 2-59  | TIBPAL20R6-5C      | TIBPAL20R6-7M       | 2-183 |

|                | PAL16R8AM      | 2-59  | TIBPAL20R6-7C      | TIBPAL20R6-10M      | 2-211 |

|                | PAL16R8A-2M    | 2-59  | TIBPAL20R6-10C     | TIBPAL20R6-10M      | 2-231 |

| TIBPAL16L8-5C  | TIBPAL16L8-7M  | 2-71  | TIBPAL20R6-15C     | TIBPAL20R6-20M      | 2-249 |

| TIBPAL16L8-7C  | TIBPAL16L8-10M | 2-99  | TIBPAL20R6-25C     |                     | 2-265 |

| TIBPAL16L8-10C | TIBPAL16L8-12M | 2-119 | TIBPAL20R6-15CNL . |                     | 2-279 |

|                | TIBPAL16L8-15M | 2-139 | TIBPAL20R6-25CNL . |                     | 2-279 |

| TIBPAL16L8-15C | TIBPAL16L8-20M | 2-151 | TIBPAL20R8-5C      | TIBPAL20R8-7M       |       |

| TIBPAL16L8-25C | TIBPAL16L8-30M | 2-167 | TIBPAL20R8-7C      | TIBPAL20R6-10M      | 2-211 |

| TIBPAL16R4-5C  | TIBPAL16R4-7M  | 2-71  | TIBPAL20R8-10C     | TIBPAL20R6-10M      | 2-231 |

| TIBPAL16R4-7C  | TIBPAL16R4-10M | 2-99  | TIBPAL20R8-15C     | TIBPAL20R6-20M      | 2-249 |

| TIBPAL16R4-10C | TIBPAL16R4-12M | 2-119 | TIBPAL20R8-25C     |                     | 2-265 |

|                | TIBPAL16R4-15M |       |                    |                     |       |

| TIBPAL16R4-15C | TIBPAL16R4-20M | 2-151 |                    |                     |       |

| TIBPAL16R4-25C | TIBPAL16R4-30M | 2-167 | TIBPAL22V10AC      | TIBPAL22V10AM       | 2-291 |

| TIBPAL16R6-5C  | TIBPAL16R6-7M  |       |                    |                     |       |

| TIBPAL16R6-7C  | TIBPAL16R6-10M |       | TIBPAL22V10-5C     |                     | 2-305 |

| TIBPAL16R6-10C | TIBPAL16R6-12M |       | TIBPAL22V10-7C     | TIBPAL22V10-10M     | 2-317 |

|                | TIBPAL16R6-15M |       | TIBPAL22V10-10C    |                     | 2-335 |

| TIBPAL16R6-15C | TIBPAL16R6-20M |       | TIBPAL22V10-15BC . |                     | 2-351 |

| TIBPAL16R6-25C | TIBPAL16R6-30M |       | TIBPAL22V10-20M    |                     | 2-365 |

| TIBPAL16R8-5C  | TIBPAL16R8-7M  |       |                    | TIBPAL22VP10-25M    |       |

| TIBPAL16R8-7C  | TIBPAL16R8-10M |       |                    |                     |       |

| TIBPAL16R8-10C | TIBPAL16R8-12M |       |                    |                     |       |

|                | TIBPAL16R8-15M |       |                    |                     |       |

| TIBPAL16R8-15C | TIBPAL16R8-20M |       |                    |                     |       |

| TIBPAL16R8-25C | TIBPAL16R8-30M |       |                    |                     |       |

| TIBPAL20L8-5C  | TIBPAL20L8-7M  |       |                    |                     |       |

| TIBPAL20L8-7C  | TIBPAL20L8-10M |       |                    |                     |       |

| TIBPAL20L8-10C |                | 2-231 |                    |                     |       |

|                |                |       | TICPAL 22V10 7-25C | TICPAL 22V/10 7-30L | 2-450 |

## INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical commission (IEC) for international use.

### PART 1 — GENERAL CONCEPTS AND CLASSIFICATIONS OF CIRCUIT COMPLEXITY

## **Chip-Enable Input**

A control input that when active permits operation of the integrated circuit for input, internal transfer, manipulation, refreshing, and/or output of data and when inactive causes the integrated circuit to be in reduced-power standby mode.

NOTE: See chip-select input.

## **Chip-Select Input**

A gating input that when inactive prevents input or output of data to or from the integrated circuit. NOTE: See chip-enable input.

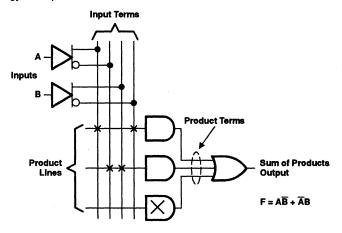

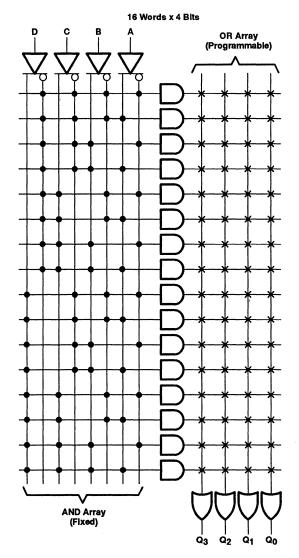

## Field-Programmable Logic Array (FPLA)

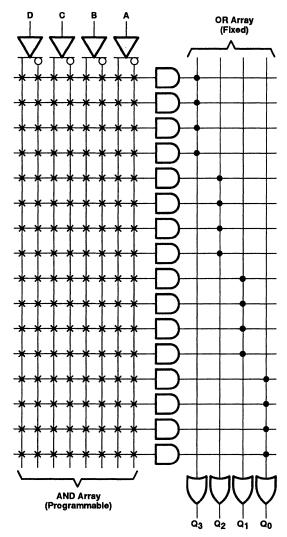

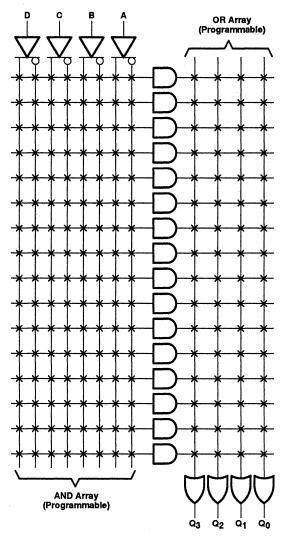

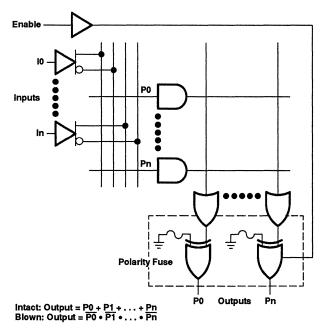

A user-programmable integrated circuit whose basic structure consists of a programmable AND array and whose outputs feed a programmable OR array.

## **Gate Equivalent Circuit**

A basic unit-of-measure of relative digital-circuit complexity. The number of gate-equivalent circuits is that number of individual logic gates that would have to be interconnected to perform the same function.

## Large-Scale Integration (LSI)

A concept whereby a complete major subsystem or system function is fabricated as a single microcircuit. In this context, a major subsystem or system, whether digital or linear, is considered to be one that contains 100 or more equivalent gates or circuitry of similar complexity.

## Medium-Scale Integration (MSI)

A concept whereby a complete subsystem or system function is fabricated as a single microcircuit. The subsystem or system is smaller than for LSI, but whether digital or linear, is considered to be one that contains 12 or more equivalent gates or circuitry of similar complexity.

## **Output-Enable Input**

A gating input that when active permits the integrated circuit to output data and when inactive causes the integrated circuit output(s) to be at a high impedance (off).

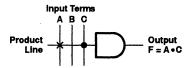

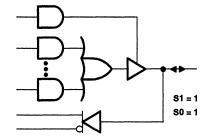

## Programmable Array Logic (PAL®)

A user-programmable integrated circuit which utilizes proven fuse link technology to implement logic functions. Implements sum of products logic by using a programmable AND array whose outputs feed a fixed OR array.

PAL is a registered trademark of Advanced Micro Devices Inc.

## Small-Scale Integration (SSI)

Integrated circuits of less complexity than medium-scale integration (MSI).

## Typical (TYP)

A calculated value representative of the specified parameter at nominal operating conditions ( $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ), based on the measured value of devices processed, to emulate the process distribution.

## **Very-Large-Scale Integration (VLSI)**

A concept whereby a complete system function is fabricated as a single microcircuit. In this context, a system, whether digital or linear, is considered to be one that contains 3000 or more gates or circuity of similar complexity.

## PART 2 — OPERATING CONDITIONS AND CHARACTERISTICS (IN SEQUENCE BY LETTER SYMBOLS)

## C<sub>I</sub> Input capacitance

The internal capacitance at an input of the device.

## Co Output capacitance

The internal capacitance at an output of the device.

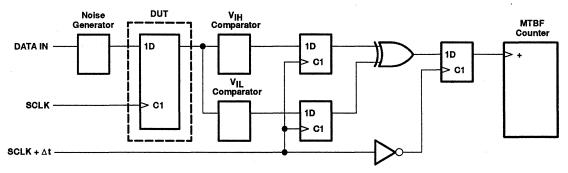

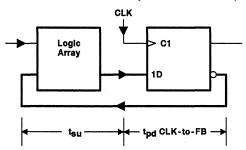

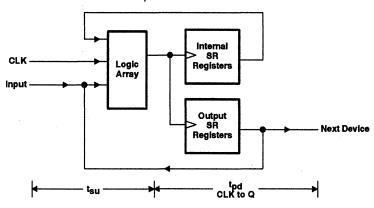

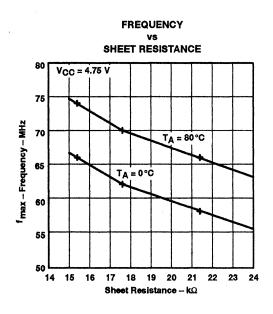

## f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

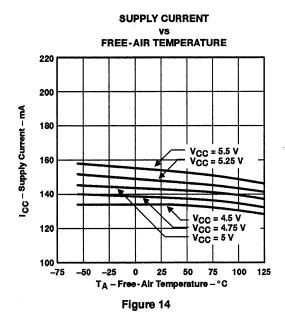

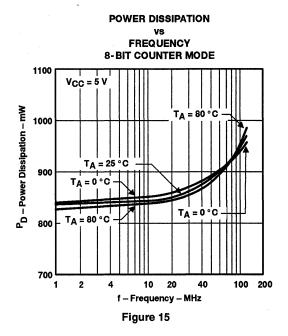

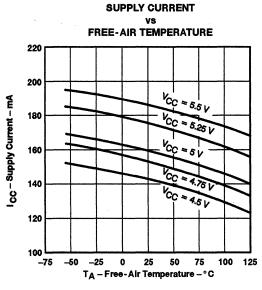

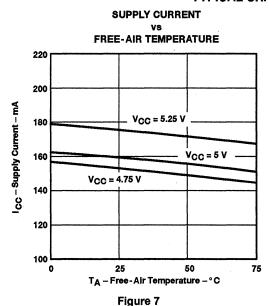

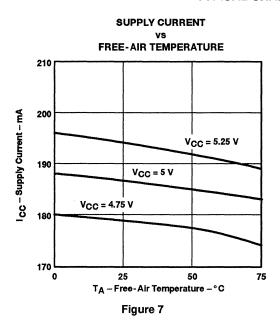

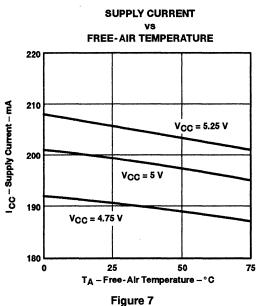

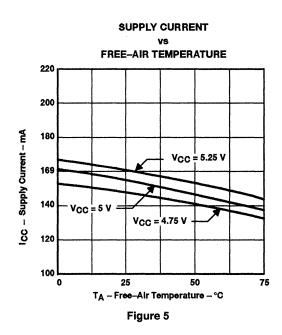

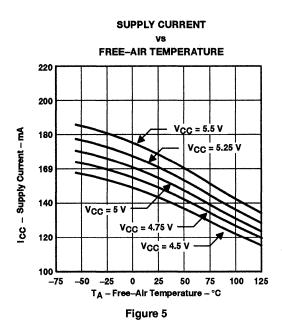

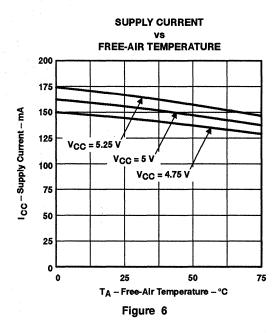

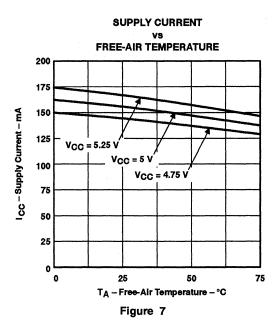

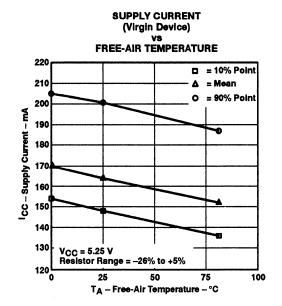

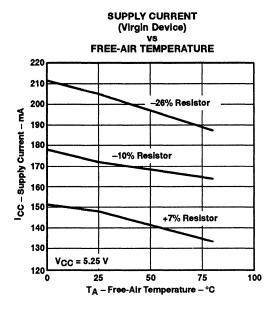

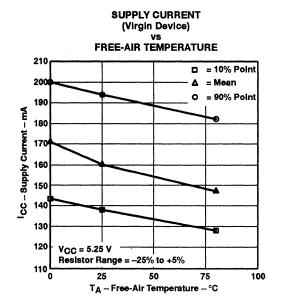

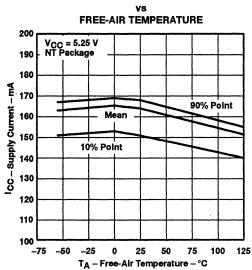

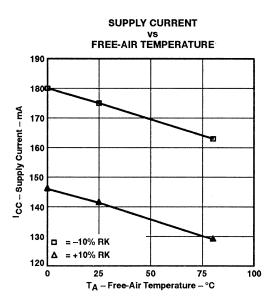

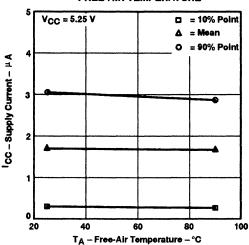

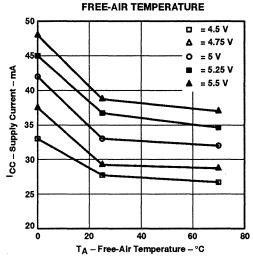

## I<sub>CC</sub> Supply current

The current into\* the VCC supply terminal of an integrated circuit.

## I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input.

## I<sub>IL</sub> Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

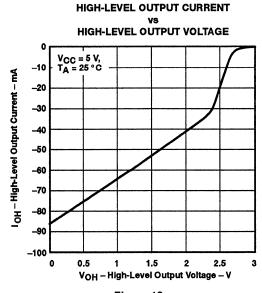

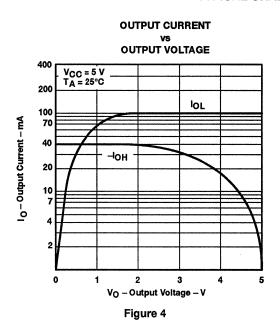

## IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

## IOL Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

### los (lo) Short-circuit output current

The current into\* an output when that output is short-circuited to ground (or other specified potential) with input conditions applied to establish the output logic level farthest from ground potential (or other specified potential).

## I<sub>OZH</sub> Off-state (high-impedance-state) output current (of a three-state output) with high-level voltage applied

The current flowing into\* an output having three-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a high-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a low level if it were enabled.

## I<sub>OZL</sub> Off-state (high-impedance-state) output current (of a three-state output) with low-level voltage applied

The current flowing into\* an output having three-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output and with a low-level voltage applied to the output.

NOTE: This parameter is measured with other input conditions established that would cause the output to be at a high level if it were enabled.

<sup>\*</sup> Current out of a terminal is given as a negative value.

## V<sub>IH</sub> High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is guaranteed.

## V<sub>IK</sub> Input clamp voltage

An input voltage in a region of relatively low differential resistance that serves to limit the input voltage swing.

## V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is guaranteed.

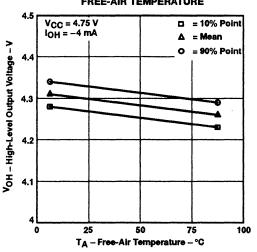

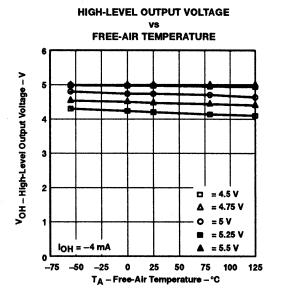

## V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

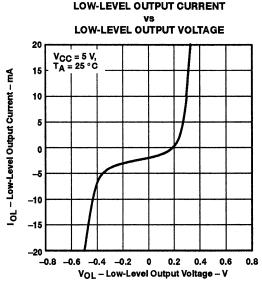

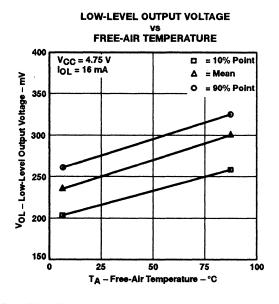

## V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

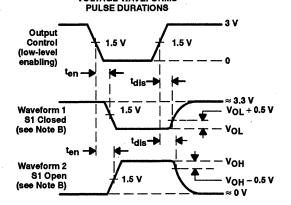

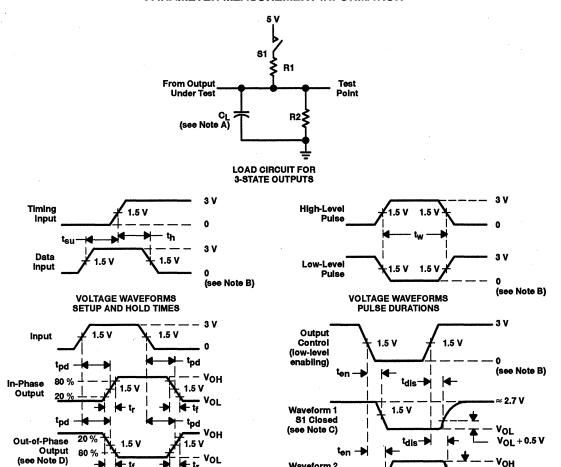

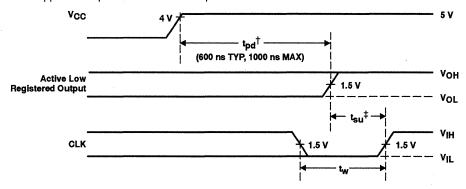

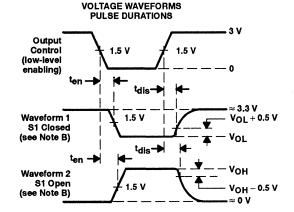

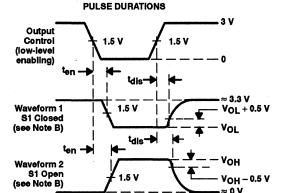

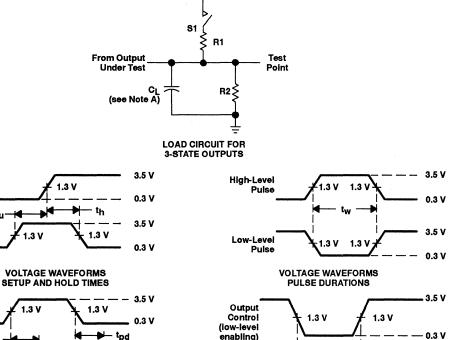

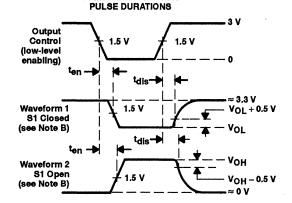

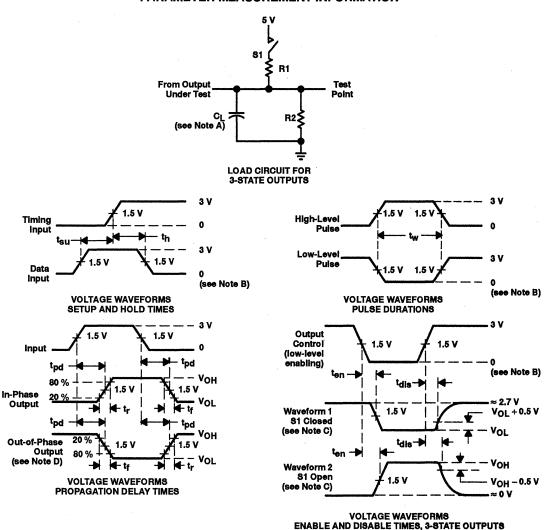

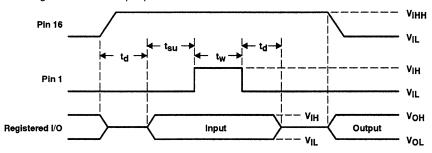

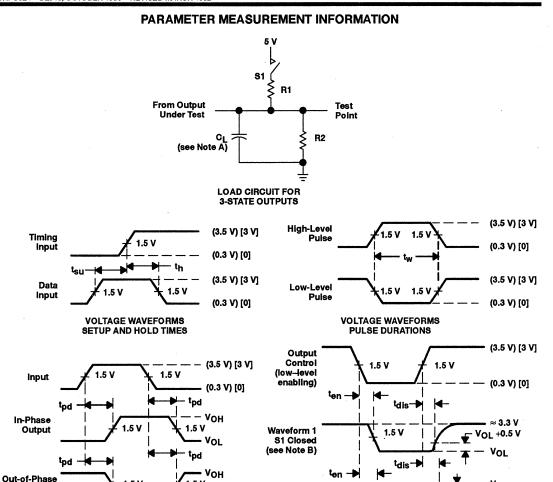

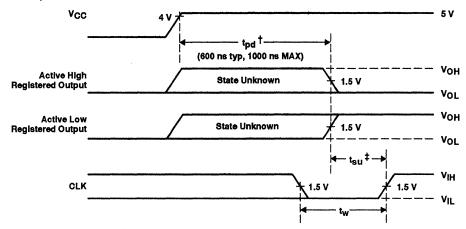

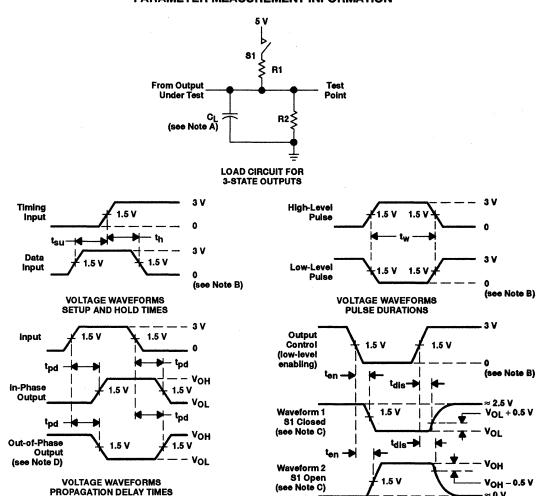

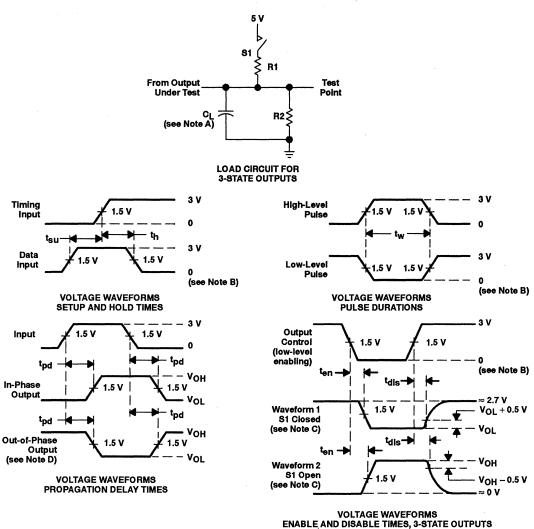

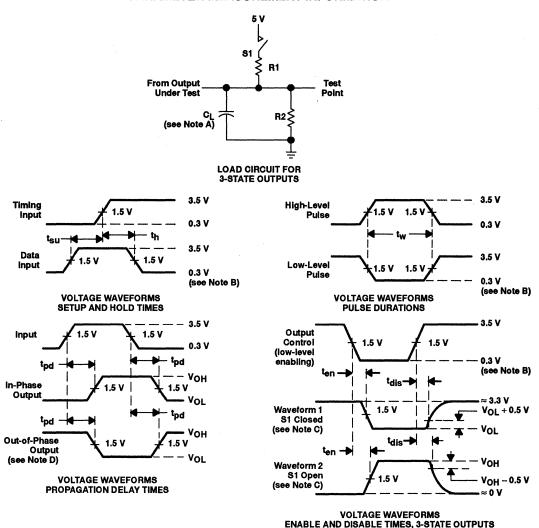

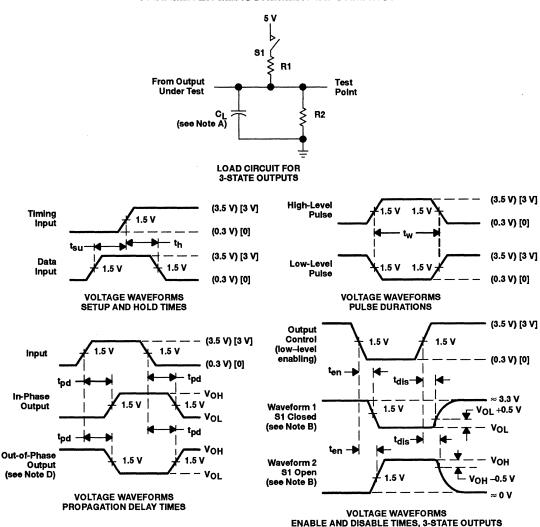

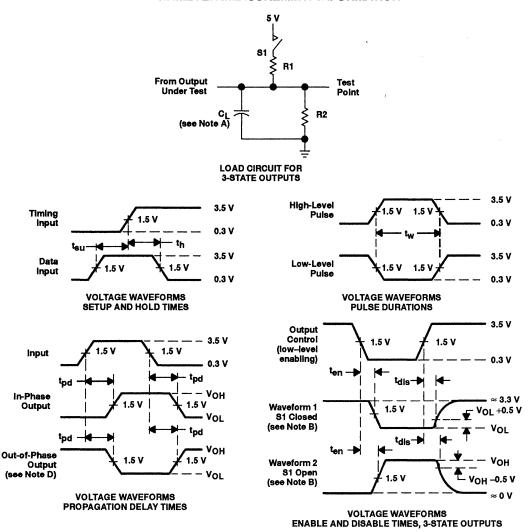

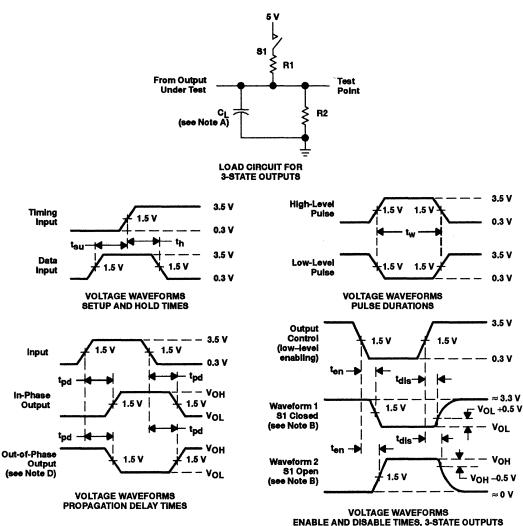

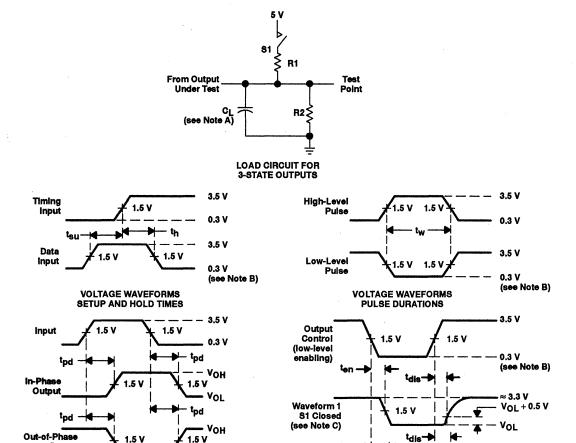

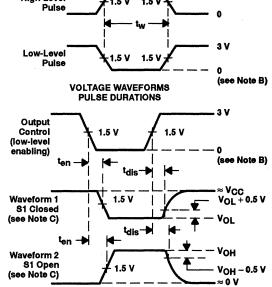

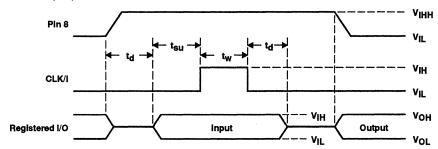

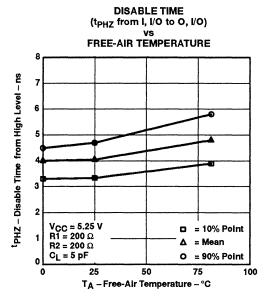

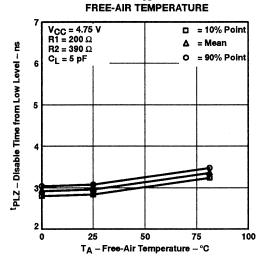

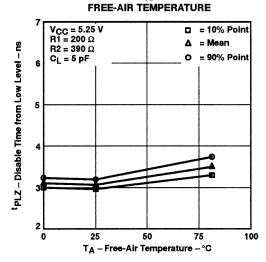

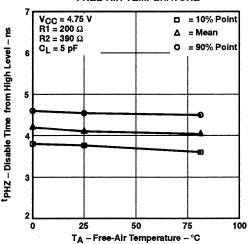

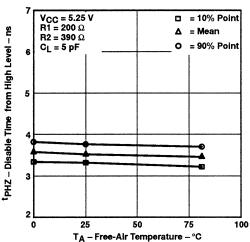

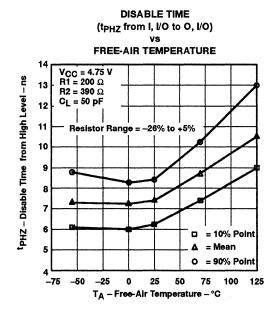

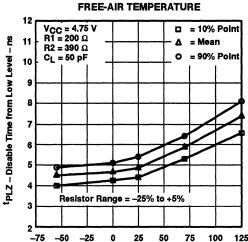

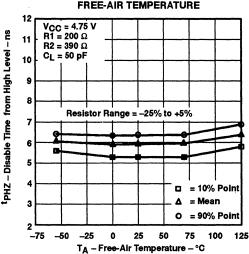

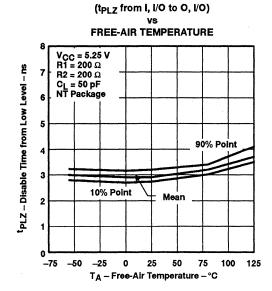

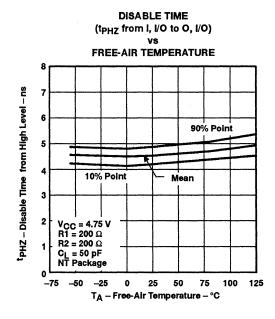

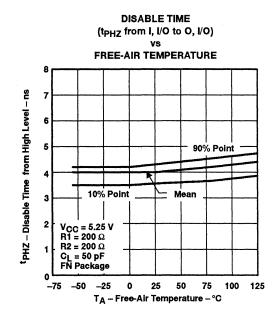

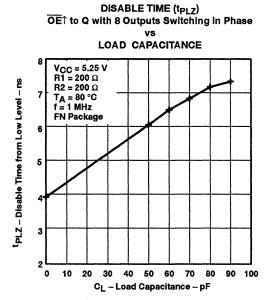

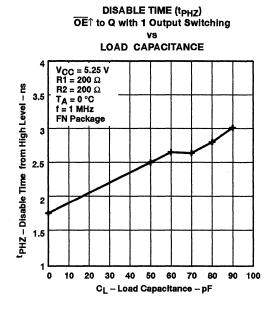

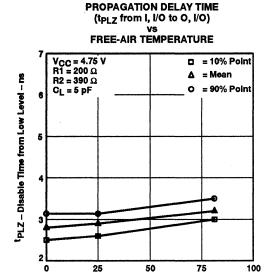

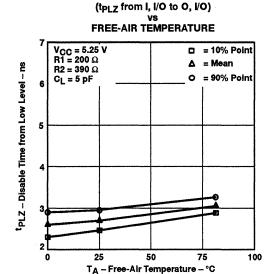

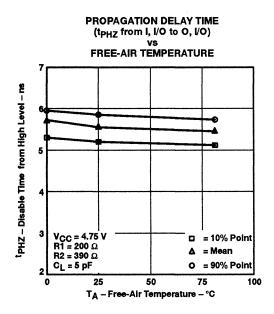

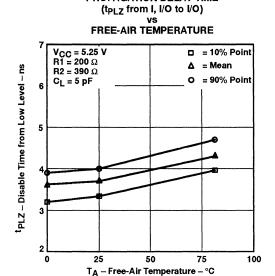

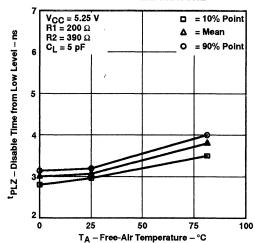

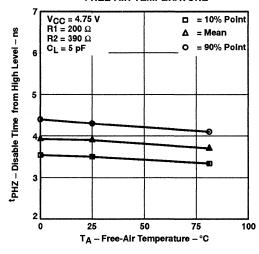

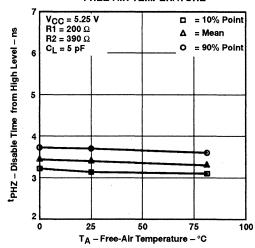

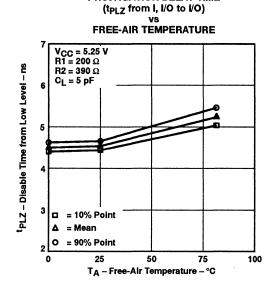

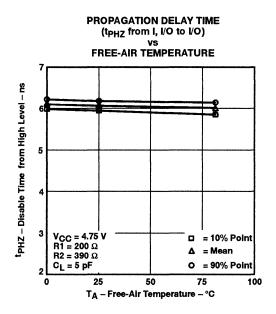

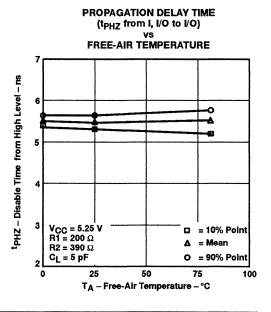

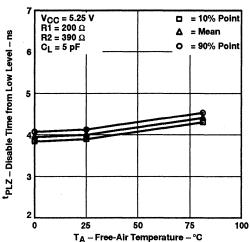

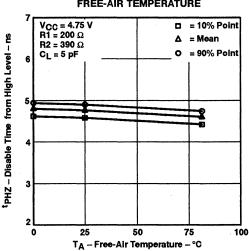

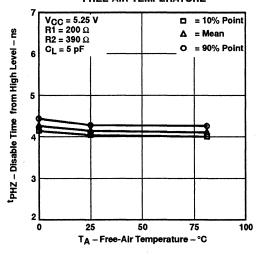

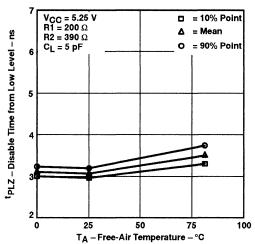

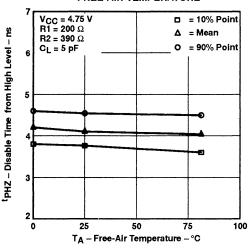

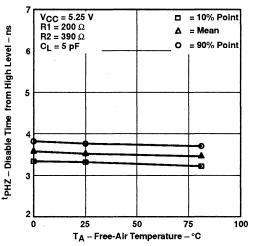

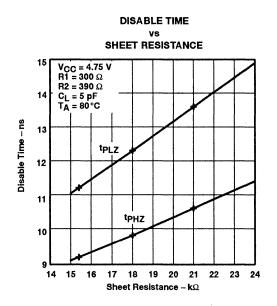

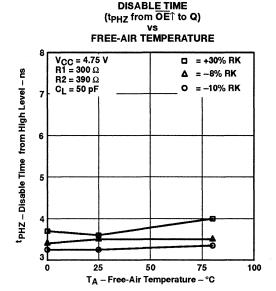

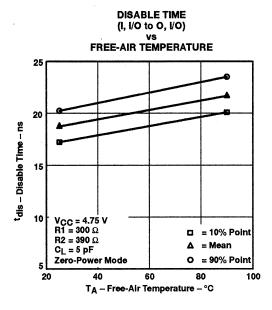

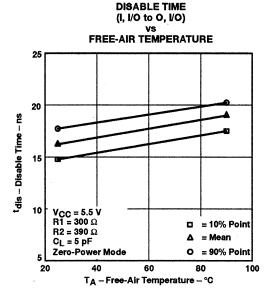

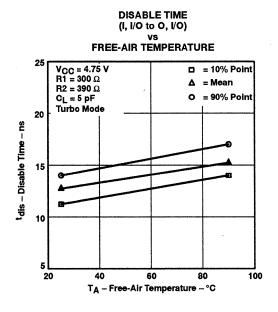

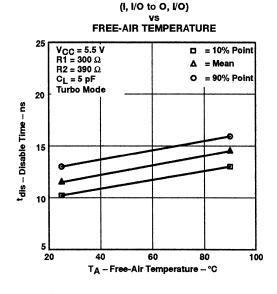

## t<sub>dis</sub> Disable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from either of the defined active levels (high or low) to a high-impedance (off) state. ( $t_{dis} = t_{PHZ}$  or  $t_{PLZ}$ ).

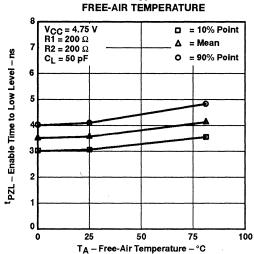

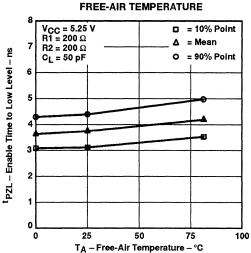

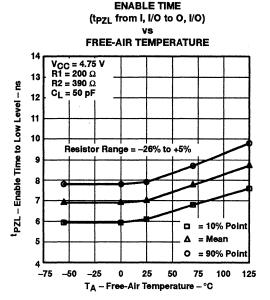

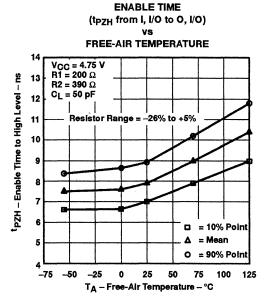

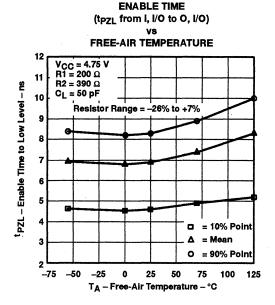

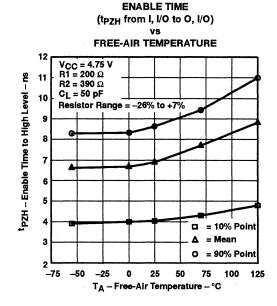

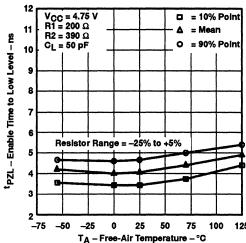

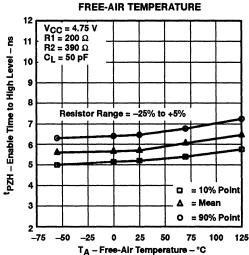

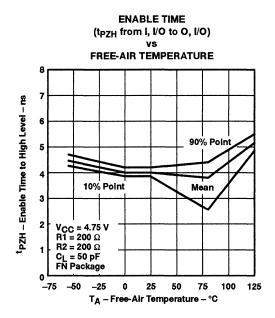

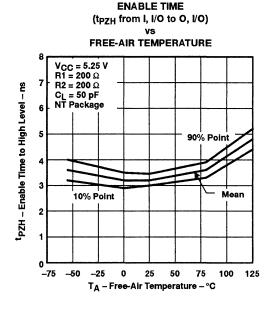

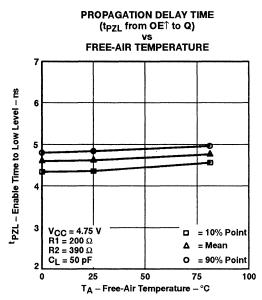

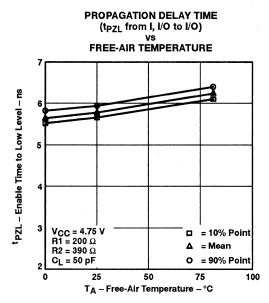

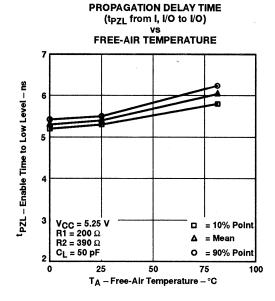

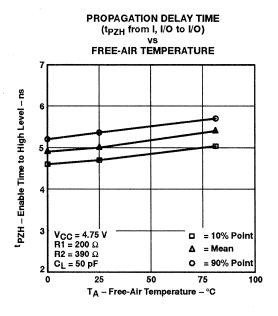

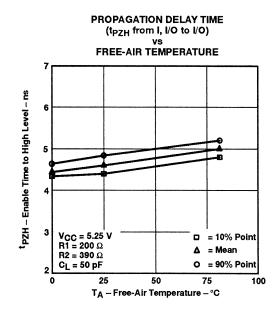

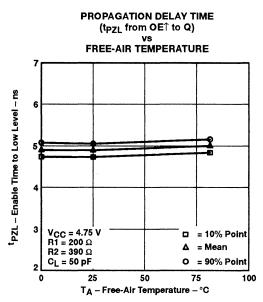

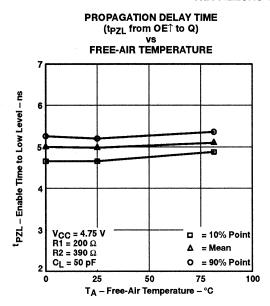

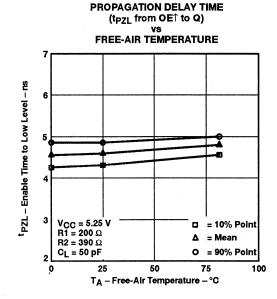

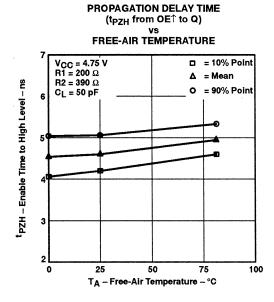

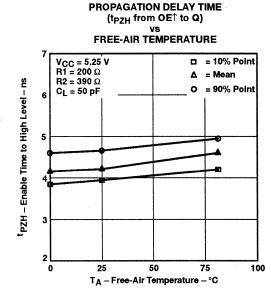

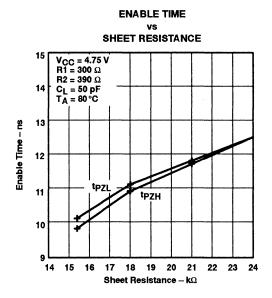

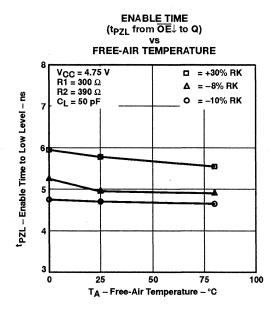

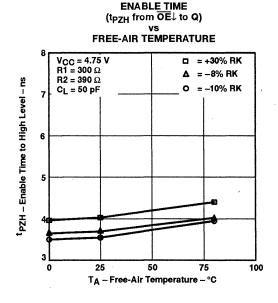

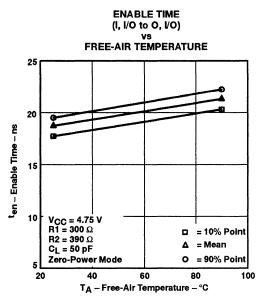

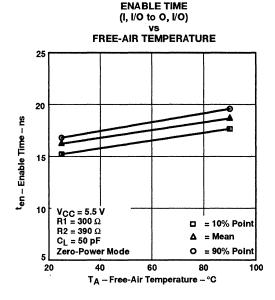

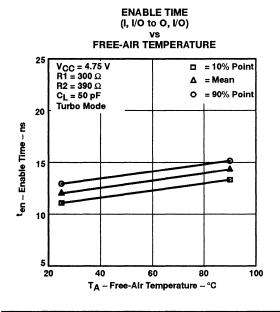

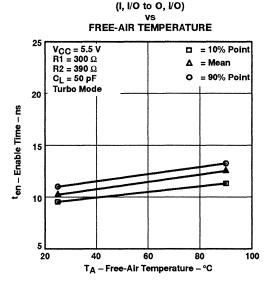

## ten Enable time (of a three-state output)

The time interval between the specified reference points on the input and output voltage waveforms, with the three-state output changing from a high-impedance (off) state to either of the defined active levels (high or low). ( $t_{en} = t_{PZH}$  or  $t_{PZL}$ ).

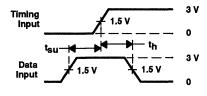

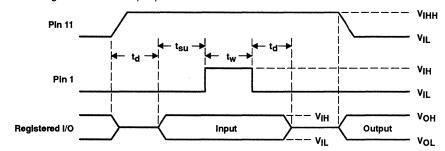

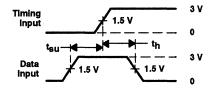

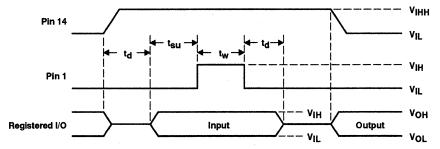

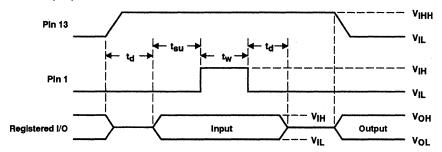

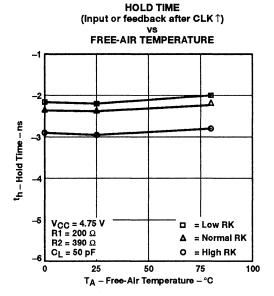

## th Hold time

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

- NOTES 1: The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is guaranteed.

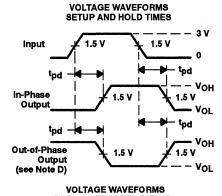

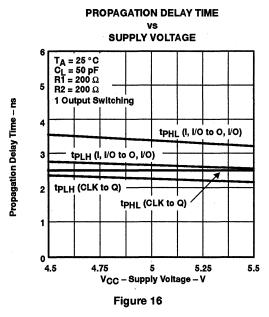

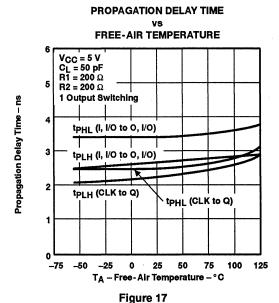

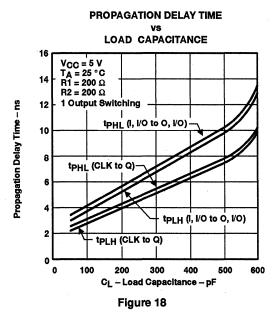

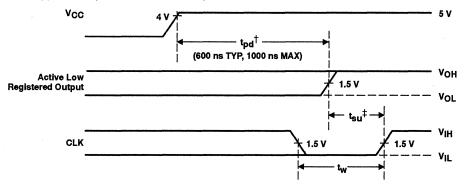

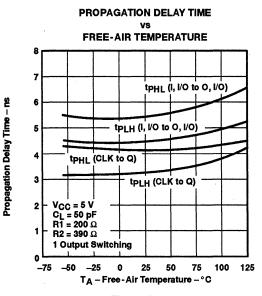

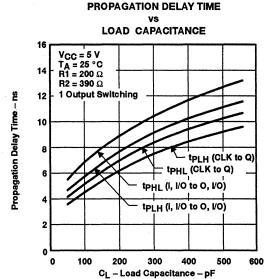

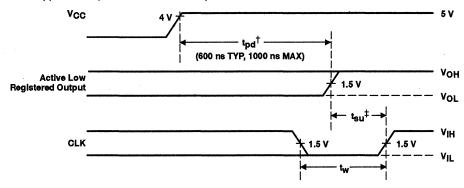

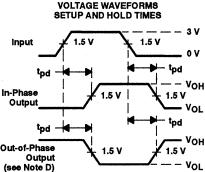

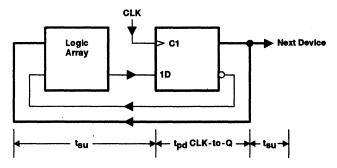

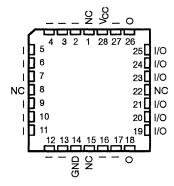

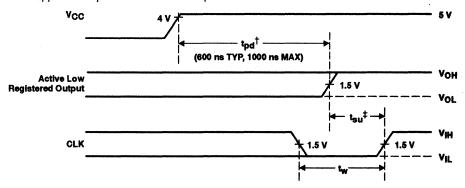

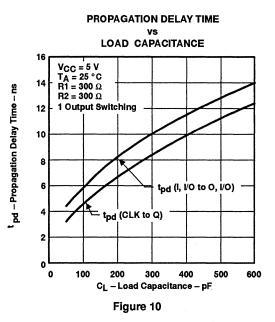

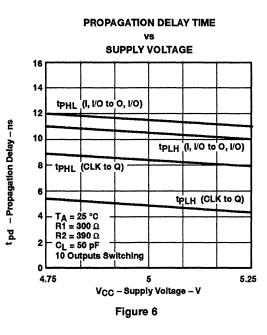

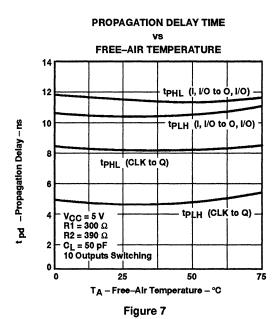

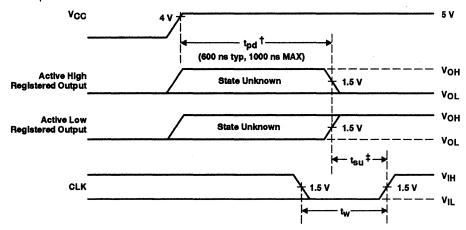

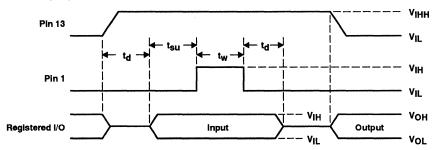

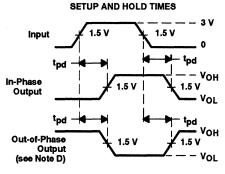

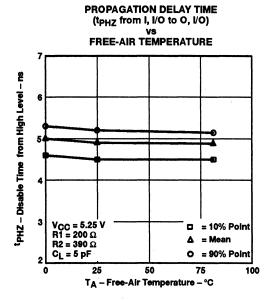

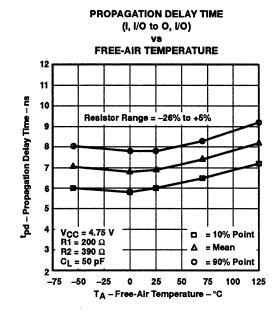

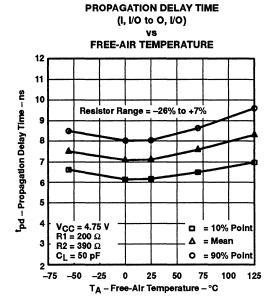

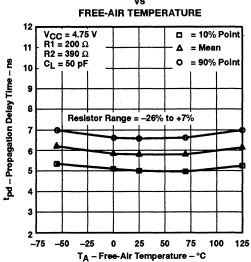

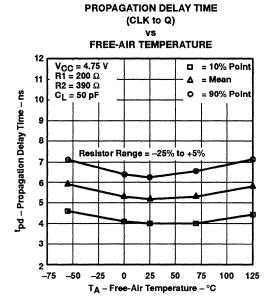

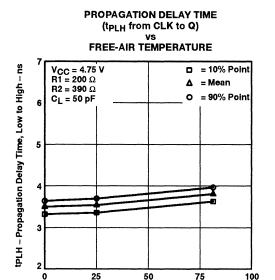

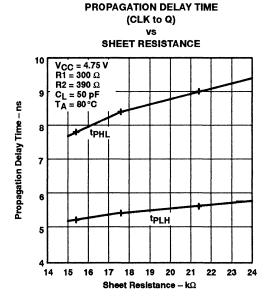

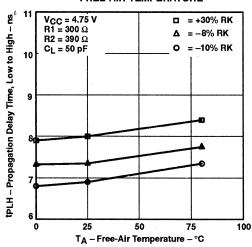

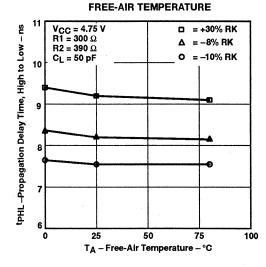

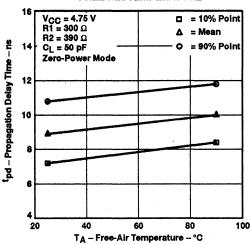

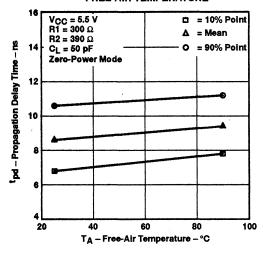

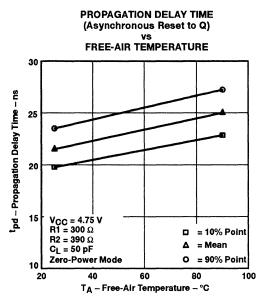

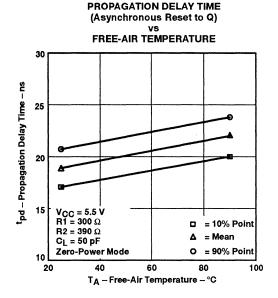

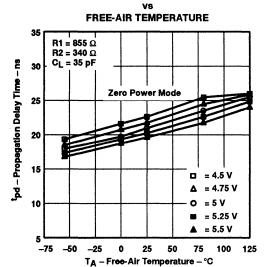

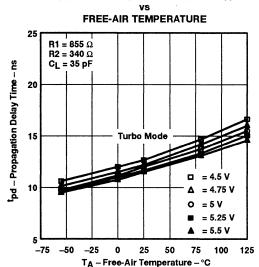

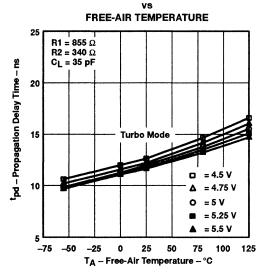

## t<sub>pd</sub> Propagation delay time

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level. ( $t_{pd} = t_{PHL}$  or  $t_{PLH}$ ).

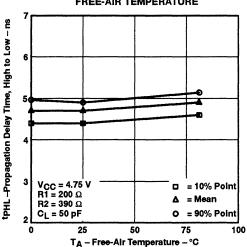

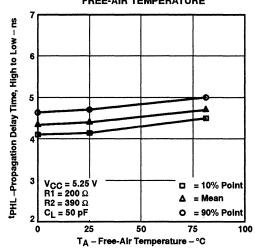

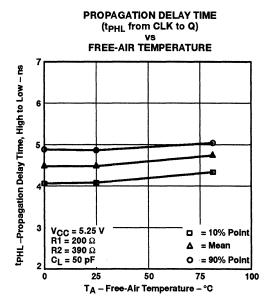

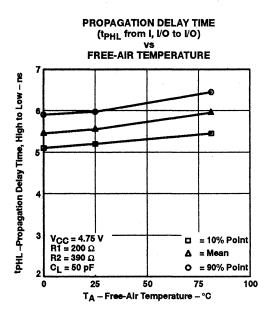

#### Propagation delay time, high-to-low level output tpHL

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level.

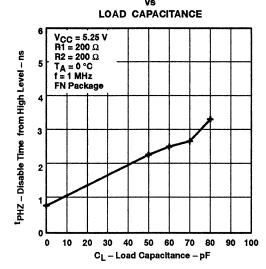

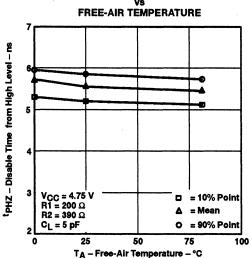

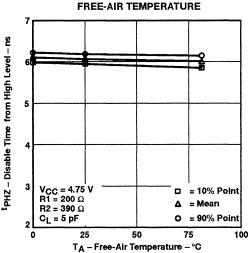

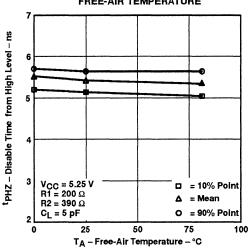

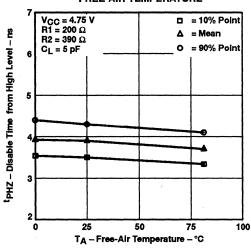

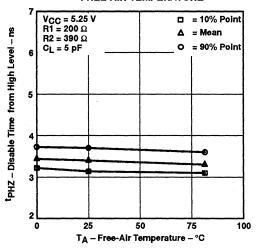

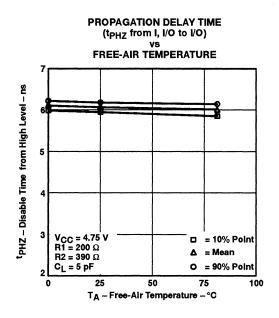

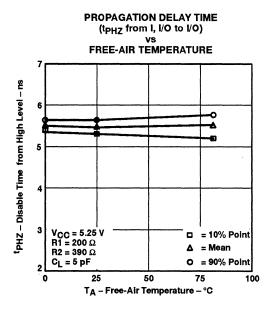

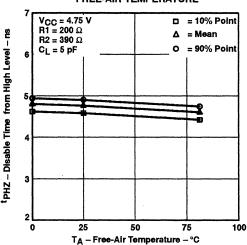

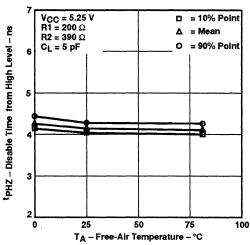

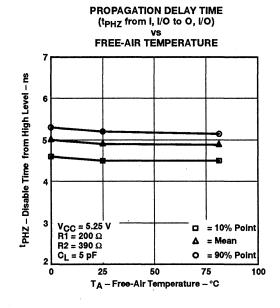

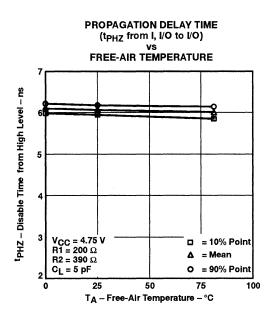

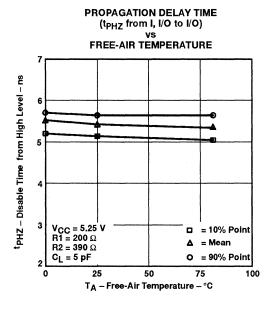

#### Disable time (of a three-state output) from high level **tpHZ**

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined high level to a high-impedance (off) state.

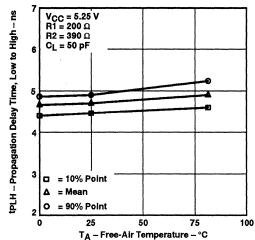

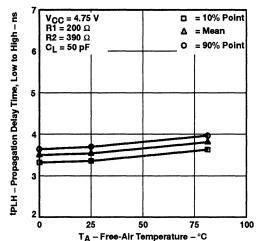

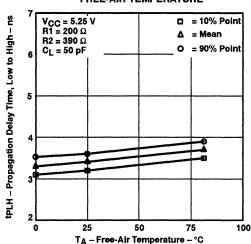

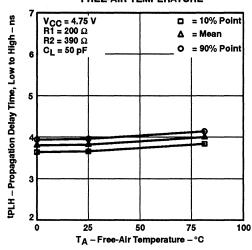

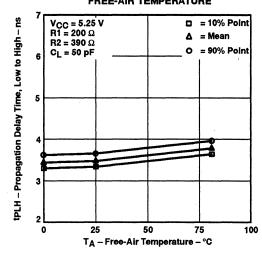

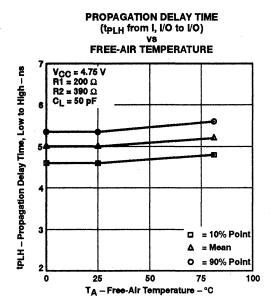

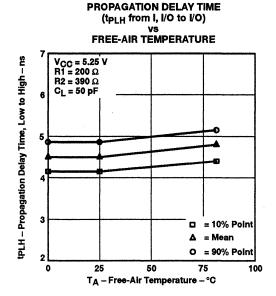

#### Propagation delay time, low-to-high level output **t**PLH

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level.

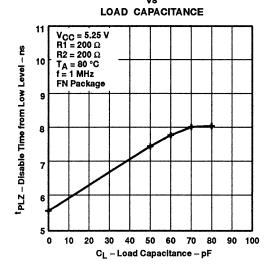

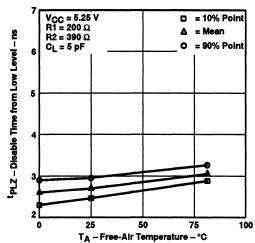

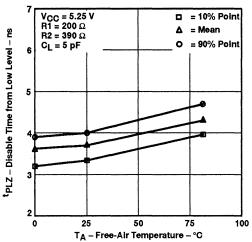

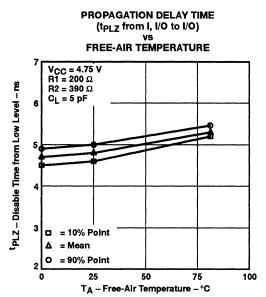

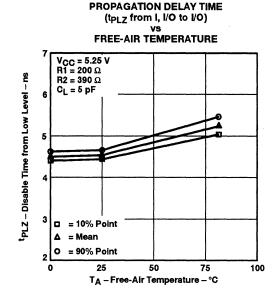

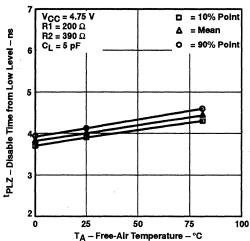

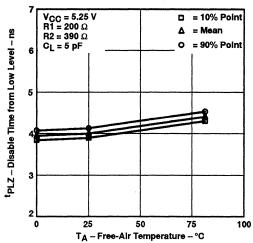

#### Disable time (of a three-state output) from low level tpLZ

The time interval between the specified reference points on the input and the output voltage waveforms with the three-state output changing from the defined low level to a high-impedance (off) state.

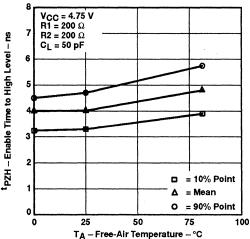

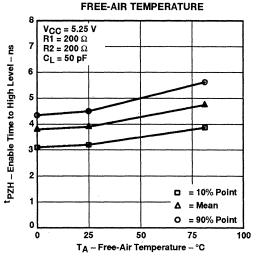

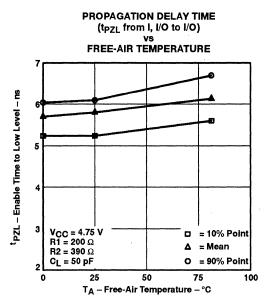

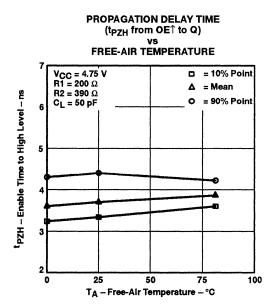

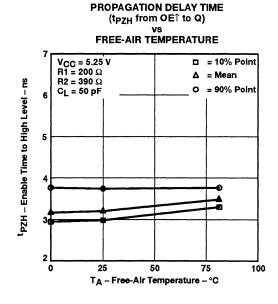

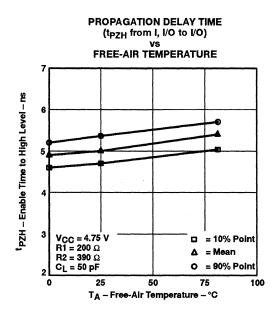

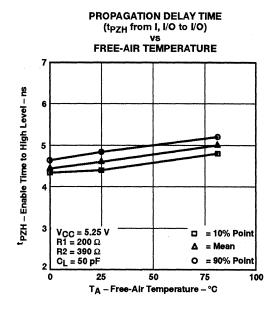

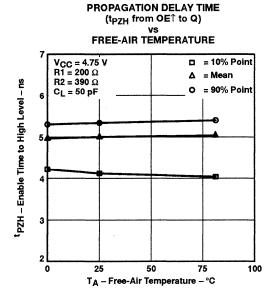

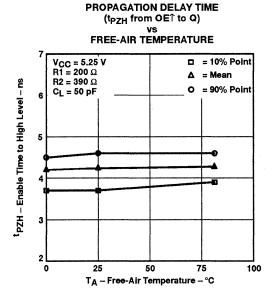

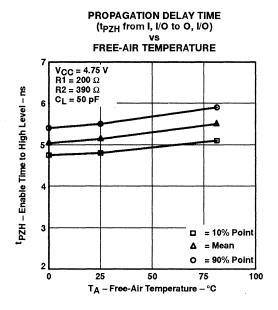

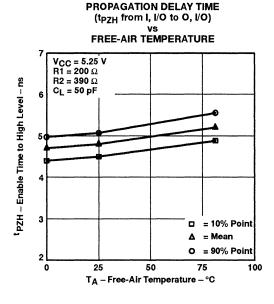

#### tpzH Enable time (of a three-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined high level.

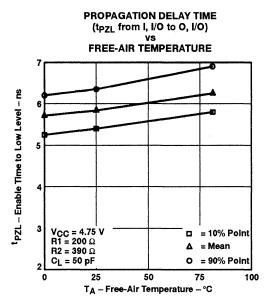

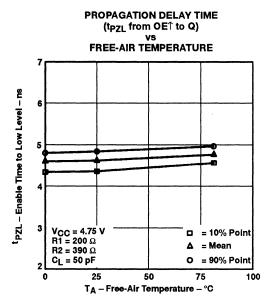

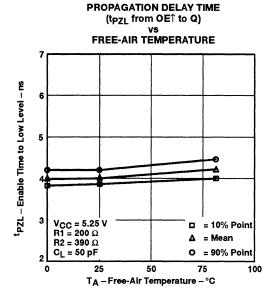

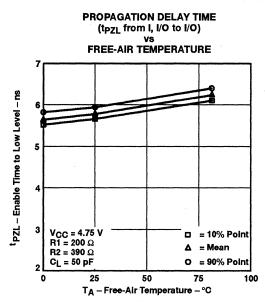

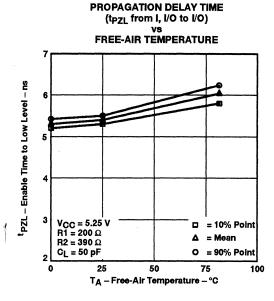

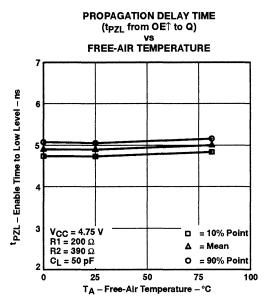

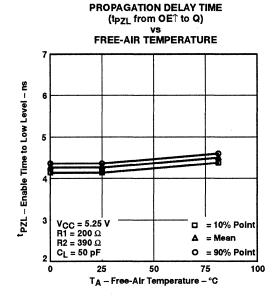

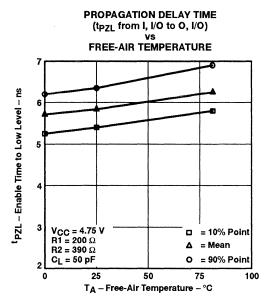

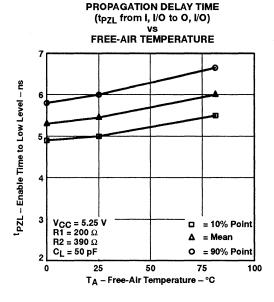

#### Enable time (of a three-state output) to low level **t**PZL

The time interval between the specified reference points on the input and output voltage waveforms with the three-state output changing from a high-impedance (off) state to the defined low level.

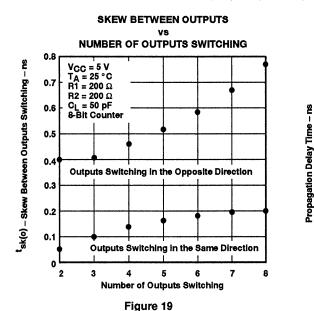

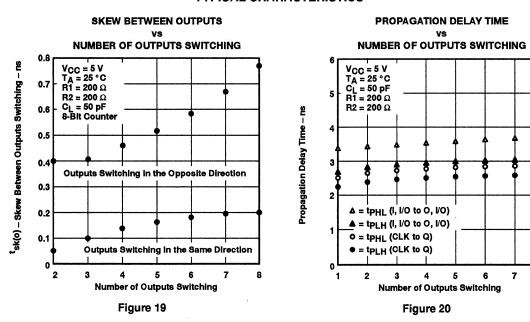

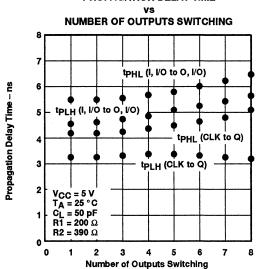

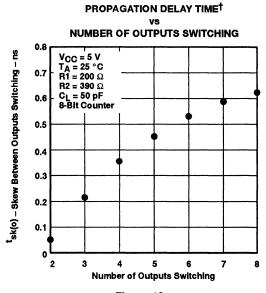

#### t<sub>sk(o)</sub> **Output Skew**

The time interval between any two propagation delay times when a single switching input or multiple inputs switching simultaneously causes multiple outputs to switch, as observed across all switching outputs.

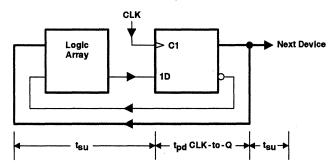

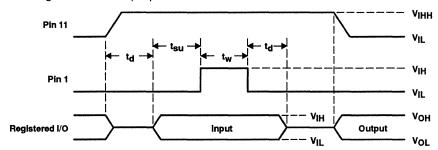

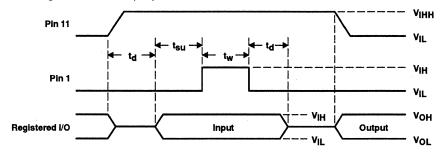

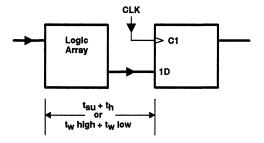

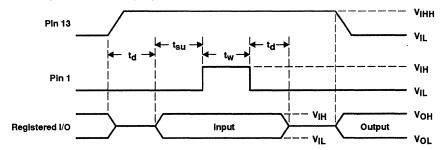

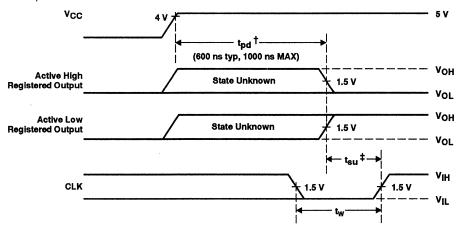

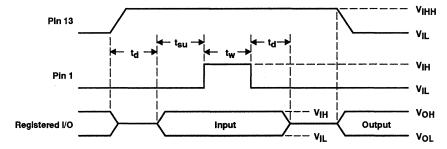

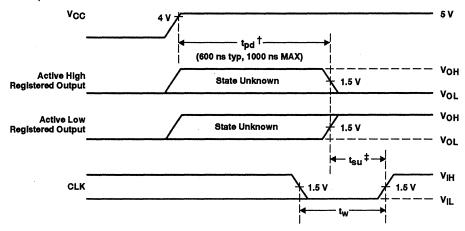

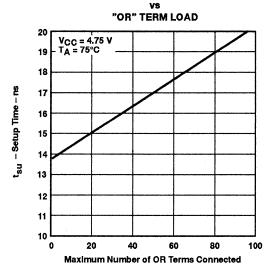

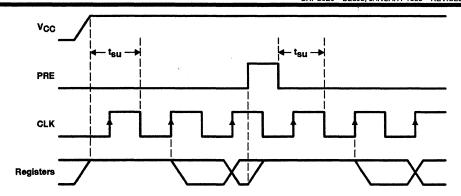

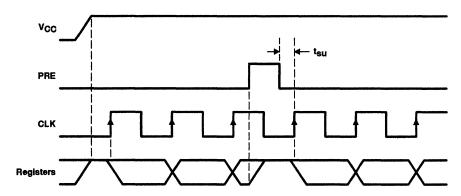

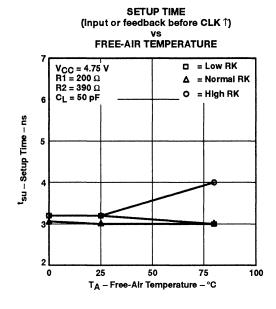

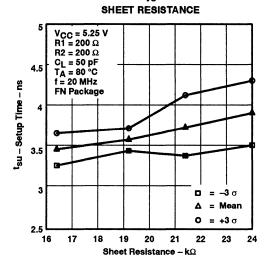

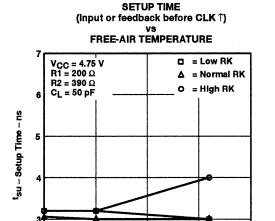

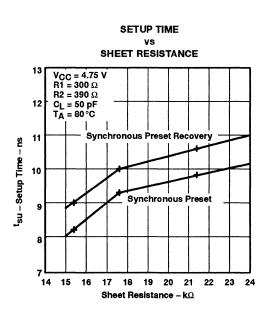

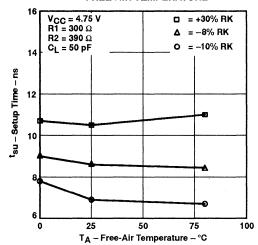

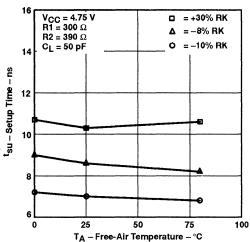

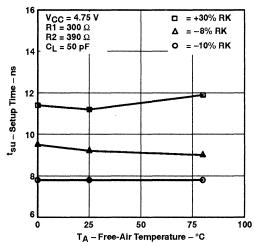

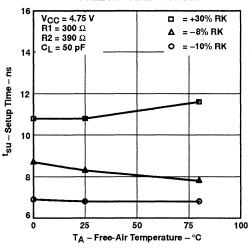

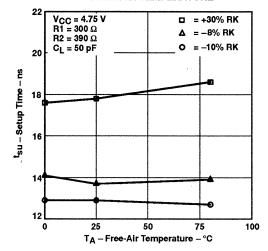

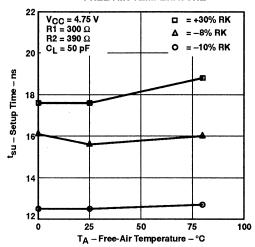

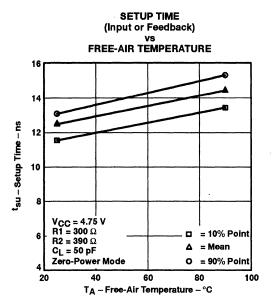

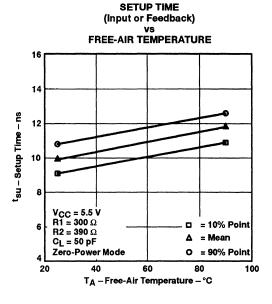

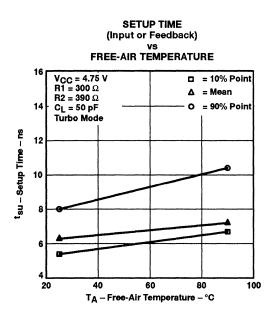

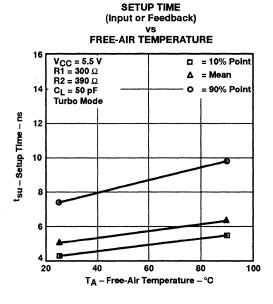

#### Setup time tsu

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

- NOTES 1: The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

- 2. The setup time may have a negative value in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

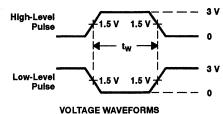

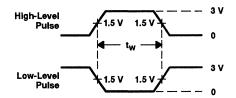

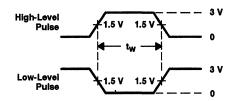

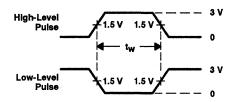

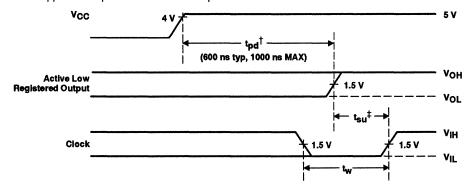

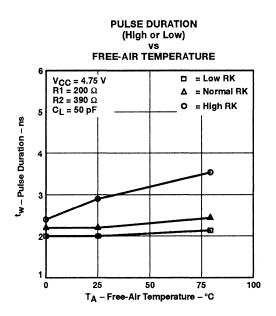

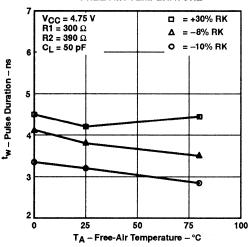

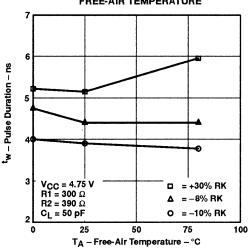

#### Pulse duration (width) tw

The time interval between specified reference points on the leading and trailing edges of the pulse waveform.

## **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets. high level (steady state) L low level (steady state) 1 transition from low to high level transition from high to low level  $\rightarrow$ value/level or resulting value/level is routed to indicated destination value/level is reentered Х irrelevant (any input, including transitions) Z off (high impedance) state of a 3-state output a ... h the level of steady-state inputs A through H respectively

the level of Q before the indicated steady-state input conditions were established  $\overline{Q}_0$ complement of Q<sub>0</sub> or level Q before the indicated steady-state input conditions were established

$Q_n$ level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

one high-level pulse one low-level pulse

$Q_0$

TOGGLE = each output changes to the complement of its previous level on each transition indicated by  $\downarrow$  or  $\uparrow$

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with ↑ or ↓, this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L,  $Q_0$ , or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse, Inc. or Inc., the pulse follows the indicated input transition and persists for an interval dependent on the circuit.

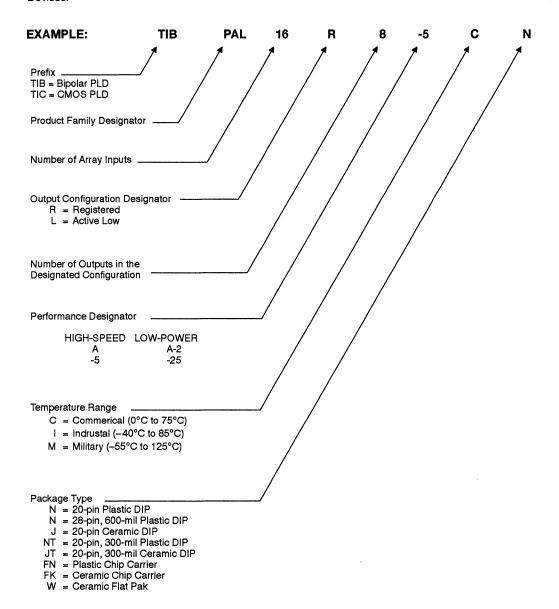

## PLD NUMBERING SYSTEM AND ORDERING INSTRUCTIONS

Factory orders for leadership PLD circuits described in this catalog should include a nine-part type number as explained in the example below. Exclude the prefix when ordering standard PLDs or One-Time Programmable Logic Devices.

## PROGRAMMER AND SOFTWARE MANUFACTURERS

## ADDRESSES FOR PLD AND FPLA PROGRAMMING AND SOFTWARE MANUFACTURERS

ACUGEN Software Inc. 427-3 Amherst St. Suite 391 Nashua, NH 03063 (603) 891-1995

Advin Systems 1050-L East Duane Ave. Sunnyvale, CA 94086 (408) 984-8600

BP Microsystems 10681 Haddington Suite 190 Houston, TX 77043 (713) 461-9430

Bytek Corporation 508 Northwest 77th St. Boca Raton, FL 33487 (407) 994-3520

Data I/O Corporation 10525 Willows Road N.E. Redmond, WA 98073 (800) 247-5700

ISDATA GmbH Daimlerstr. 51 W-5700 Karlsruhe 21 Federal Republic of Germany 0721/75 10 87

Logic Devices Inc. 1201 N.W. 65th Place Ft. Lauderdale, FL 33309 (800) 331-7766 MINC Incorporated 6755 Earl Drive Colorado Springs, CO 80918 (719) 590-1155

ProLogic Systems Inc.\* 2100-C West 6th Ave. Broomfield, CO 80020 (303) 460-0103 \* Formerly Inlab Inc.

SMS Im Morgental 13 8994 Hergatz Federal Republic of Germany (49) 755-5018

Stag Microsystems 1600 Wyatt Drive Santa Clara, CA 95054 (800) 227-8836

System General Corporation 510 South Park Victoria Drive Malpitas, CA 95035 (408) 263-6667

Texas Instruments Incorporated P.O. Box 655303, MS 3686 Dallas, TX 75265 (214) 997-5666

## IMPACT™ DESIGN AND SERVICE CENTERS

Design and programming assistance is offered by Texas Instruments IMPACT<sup>TM</sup> Design and service Centers. The centers are equipped with the latest in software and hardware tools for design, debugging, creating prototypes, and production on a local basis. Supported by a professional engineering staff, the centers provide complete code development, device programming, symbolization, functional and static (dc) parametric testing.

Anthem Electronics, Inc. 1160 Ridder Park Drive San Jose, CA 95131 (408) 453-2200

Anthem Electronics, Inc. 373 Inverness Drive South Englewood, CO 80112 (303) 790-4500

Arrow/Schweber Electronics, Inc. 17822 Gillett Avenue Irvine, CA 92714 (714) 587-0404

Arrow/Schweber Electronics, Inc. 1180 Murphy Avenue San Jose, CA 95131 (408) 441-9700

Arrow/Schweber Electronics, Inc. 4250 River Green Parkway Suite E Duluth, GA 30131 (404) 497-1300

Arrow/Schweber Electronics, Inc. 665 Spice Island Drive Sparks, NV 89431 (800) 777-Arrow

Hall-Mark Electronics Corp. 1 Mauchly Irvine, CA 92715 (714) 727-6000

Hall-Mark Electronics Corp. 2105 Lundy Avenue San Jose, CA 95131 (408) 432-4000

Hall-Mark Electronics Corp. 6 Cook Street Pinehurst Park Billerica, MA 01821 (508) 667-0902 Hall-Mark Electronics Corp. 11420 Pagemill Road Dallas, TX 75243 (214) 553-4300

Marshall Industries 9320 Telestar El Monte, CA 91731 (818) 307-6208

Marshall Industries 336 Los Coches Street Milpitas, CA 95035 (408) 942-4600

Marshall Industries 33 Upton Drive Wilmington, MA 01887 (508) 658-0810

Marshall Industries 2045 Chenault Street Carrollton, TX 75008 (214) 233-5200

Wyle Electronics Marketing Group 5191 Oceanus Huntington Beach, CA 92649 (714) 863-9953

Wyle Electronics Marketing Group 3000 Bowers Avenue Santa Clara, CA 95051 (408) 727-2500

Wyle Electronics Marketing Group 452 East 124th Avenue Thornton, CO 80241 (303) 457-9953

Wyle Electronics Marketing Group 1810 Greenville Avenue Dallas, TX 75081 (214) 235-9953

IMPACT is a trademark of Texas Instruments Incorporated.

| General Information | 1 |

|---------------------|---|

|                     |   |

|                     |   |

| Data Sheets         | 2 |

|                     |   |

|                     |   |

| Application Reports | 3 |

|                     |   |

|                     |   |

| Qualification Data  | 4 |

|                     | • |

|                     |   |

| Mechanical Data     | 5 |

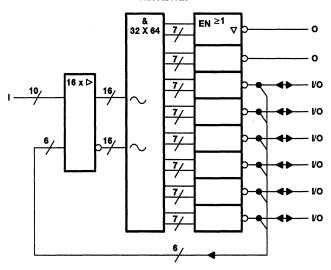

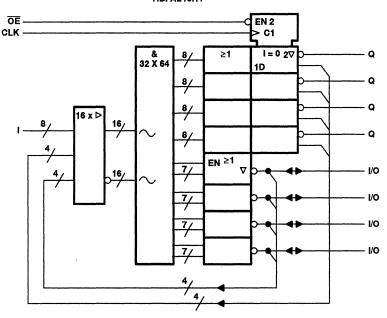

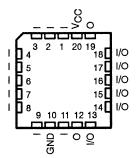

## EP330 SERIES HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

- Programmable Replacement for Conventional TTL, 74HC, and 20-Pin PLD Family

- High-Voltage EPIC™ Process Allows for Higher Performance as Follows: Maximum t<sub>pd</sub>: -12C...12 ns

-15C . . . 15 ns

-251 ... 25 ns

User-Programmable Output Logic Macrocells Provide Flexibility in Output Types With:

Selectable for Registered or Combinational Operation Output Polarity Control Independently User Programmable Feedback Path

- Programmable Design-Security Bit Prevents Copying of Logic Stored in Device

- Third-Party Advanced Software Support Featuring Schematic Capture, Interactive Netlist, Boolean Equations, and State-Machine Design Entry

- Package Options Include:

20-pin Plastic Dual-In-Line (N)

20-pin Plastic Chip Carrier (FN)

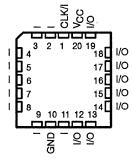

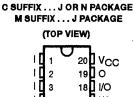

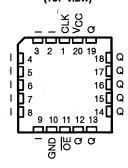

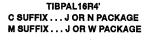

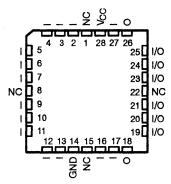

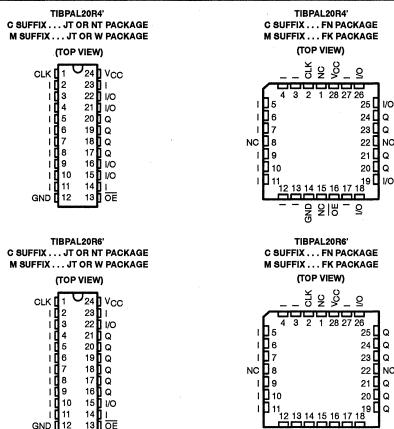

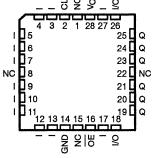

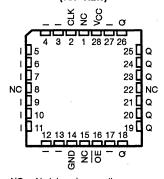

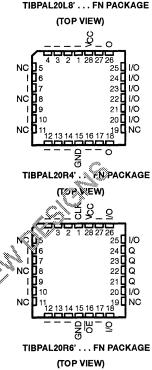

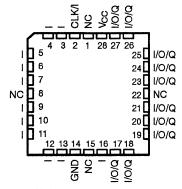

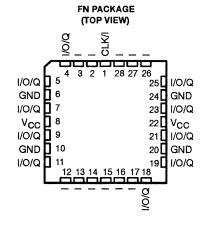

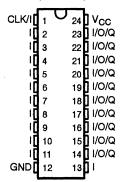

## N PACKAGE (TOP VIEW)

## FN PACKAGE (TOP VIEW)

Pin assignments in operating mode

## description

## general

The EP330 features advanced-CMOS speed and very low power utilizing Texas Instruments High-Voltage Enhanced-Processed Implanted CMOS (HVEPIC) process. Each output has an Output-Logic-Macrocell (OLM) configuration that allows user definition of the output type. The EP330 provides a reliable low-power substitute for numerous high-performance TTL PLDs.

The EP330 can accommodate up to 18 inputs and up to eight outputs. The 20-pin 300-mil package contains eight macrocells each using a programmable AND/fixed-OR structure. This AND-OR structure yields eight product terms for the logic function as well as an individual term for Output Enable.

## AVAILABLE OPTIONS

|                         |                | PACKAC                         | GE TYPE                         |

|-------------------------|----------------|--------------------------------|---------------------------------|

| T <sub>A</sub><br>RANGE | SPEED<br>CLASS | PLASTIC<br>DUAL-IN-LINE<br>(N) | PLASTIC<br>CHIP CARRIER<br>(FN) |

| 2001 7000               | 12 ns          | EP330-12CN                     | EP330-12CFN                     |

| 0°C to 70°C             | 15 ns          | EP330-15CN                     | EP330-15CFN                     |

| -40°C to 85°C           | 25 ns          | EP330-25IN                     | EP330-25IFN                     |

EPIC is a trademark of Texas Instruments Incorporated.

# EP330 SERIES HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## description (continued)

The EP330 output-logic macrocell allows the user to configure output and feedback paths for combinational or registered operation either active high or active low. With propagation delays of 12 and 15 ns, the EP330 may be configured as a low-power substitute for popular fast PLD devices such as the PAL16XXB series or the 'PAL16XX-12 and 'PAL16XX-15 series.

The CMOS EPROM technology makes it possible for the EP330 to operate at an active power-consumption level that is less than 75% of equivalent bipolar devices without sacrificing speed performance. This technology also facilitates 100% generic wafer testability using the UV-light erasable capability. As a result, designs and design modification can be quickly effected with a given EP330 without the need for post-programming testing.

Programming the EP330 is made easy by the availability of extensive third-party support for design entry, design processing, and device programming.

The EP330C is characterized for operation from 0°C to 70°C. The EP330I is characterized for operation from -40°C to 85°C.

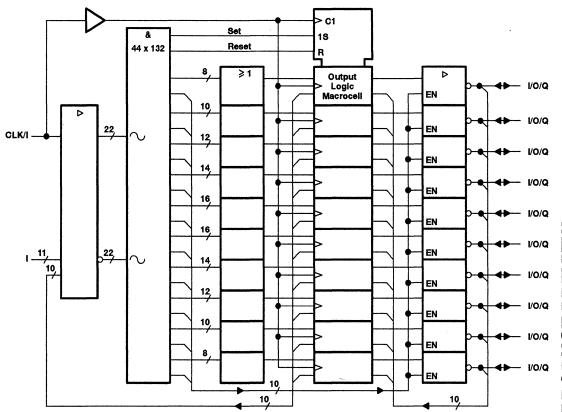

## functional description

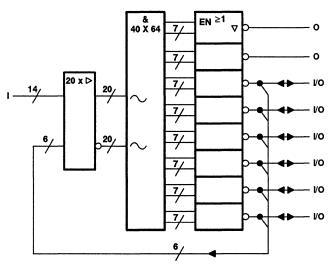

Externally, the EP330 provides ten dedicated inputs (one of which may be used as a synchronous clock input) and eight I/O pins that may be configured for input, output, or bidirectional operation.

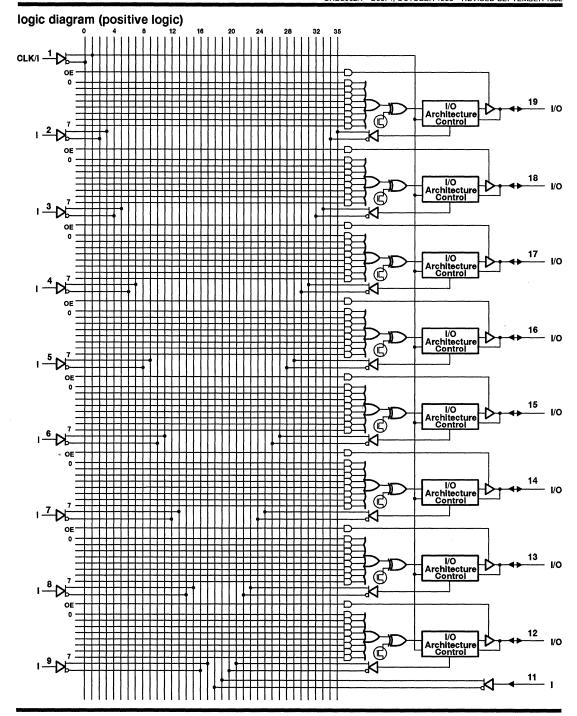

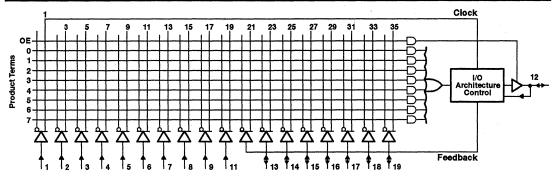

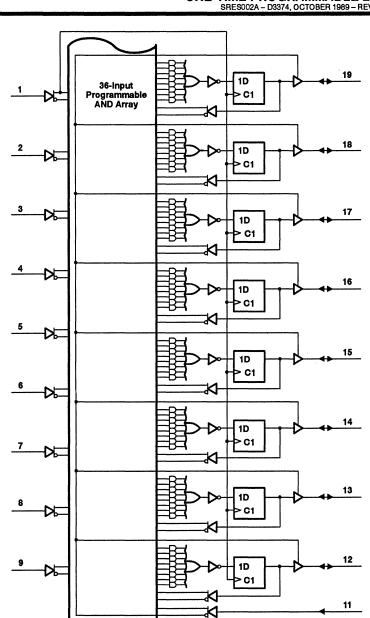

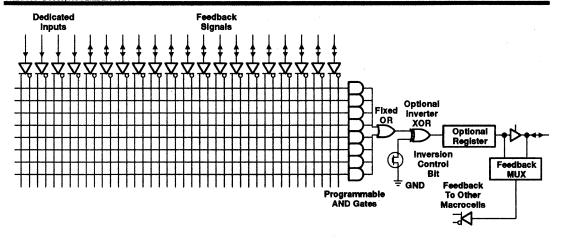

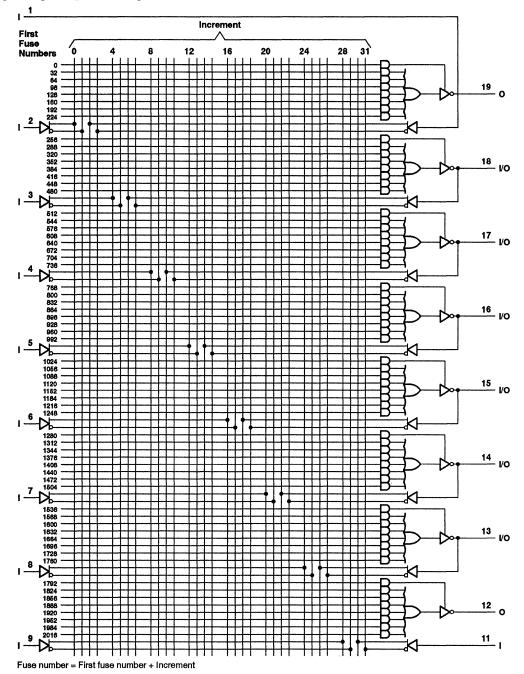

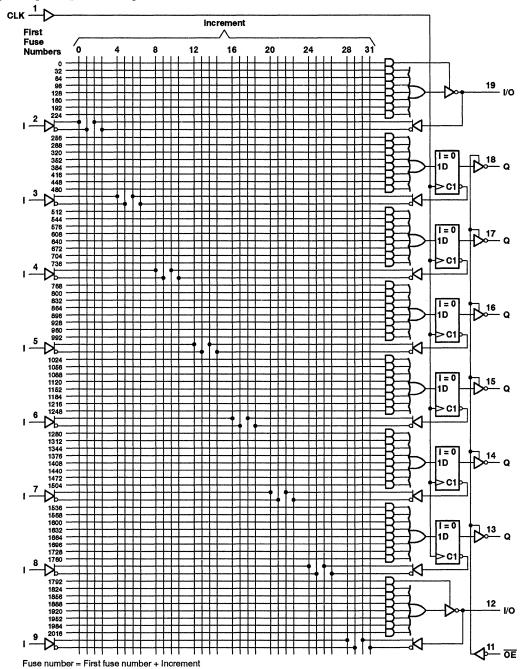

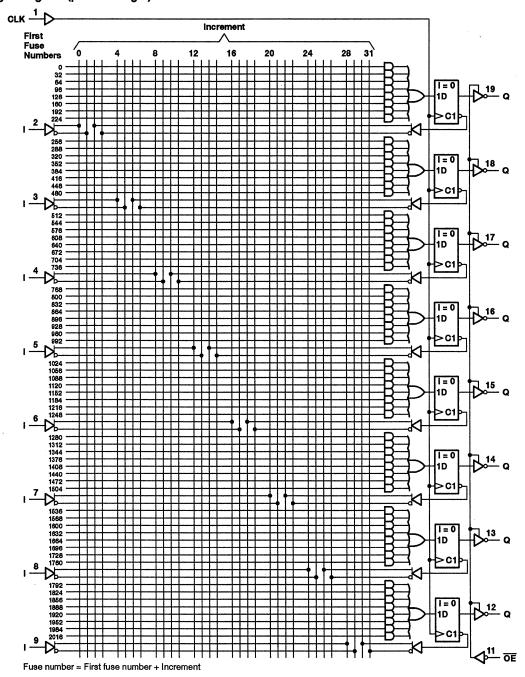

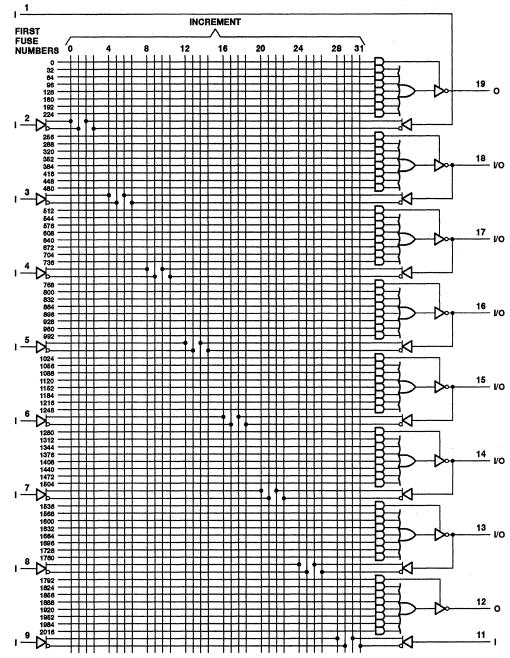

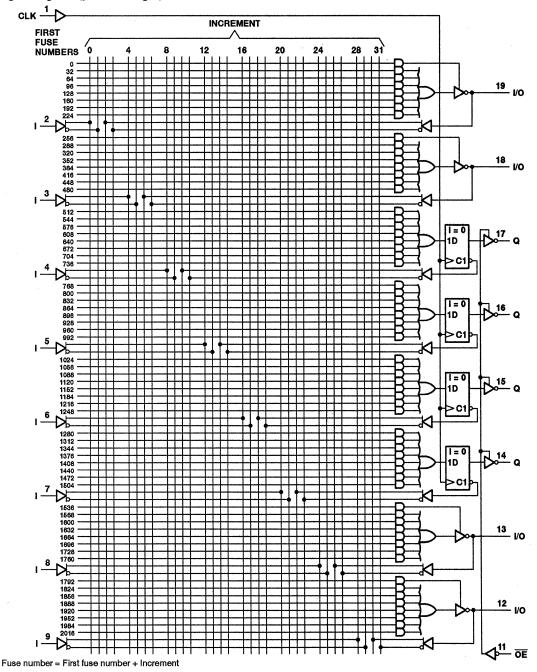

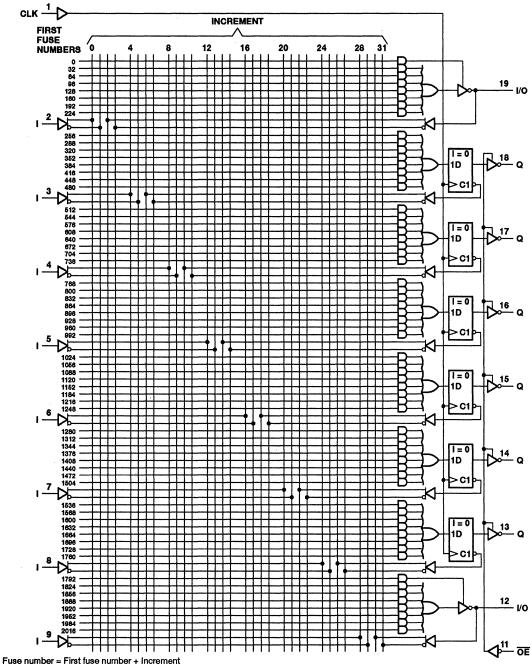

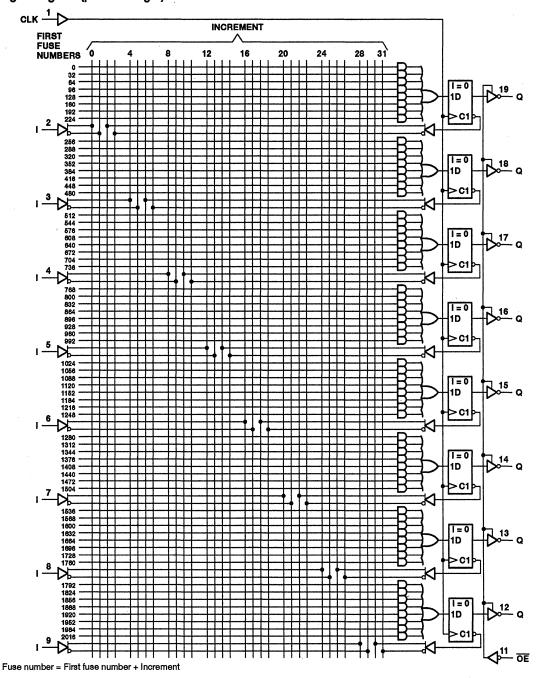

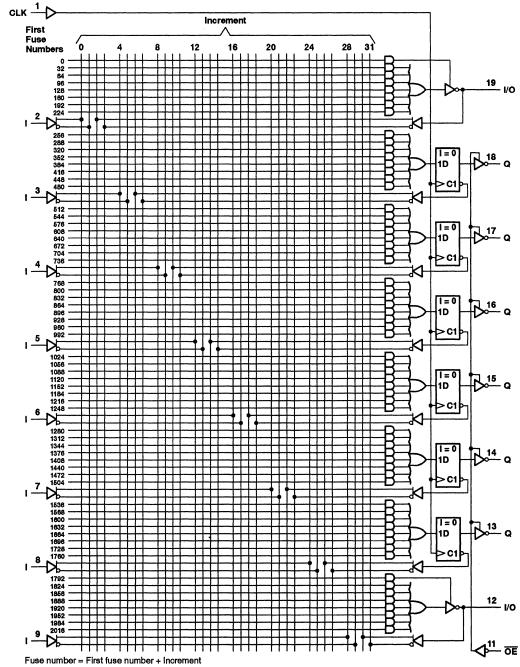

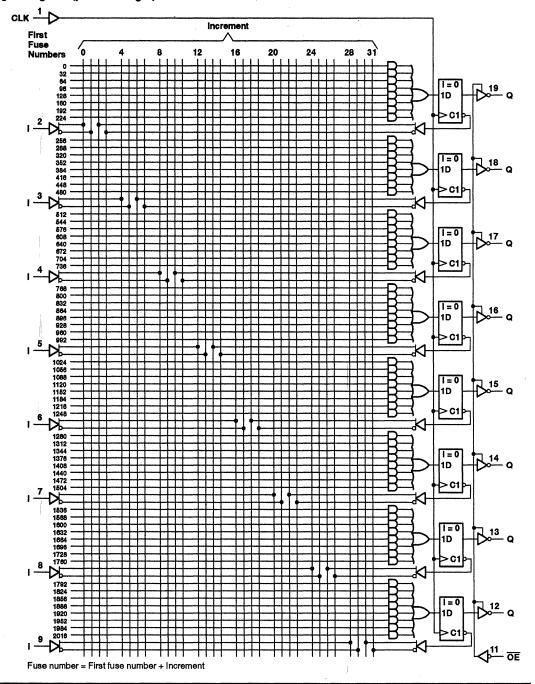

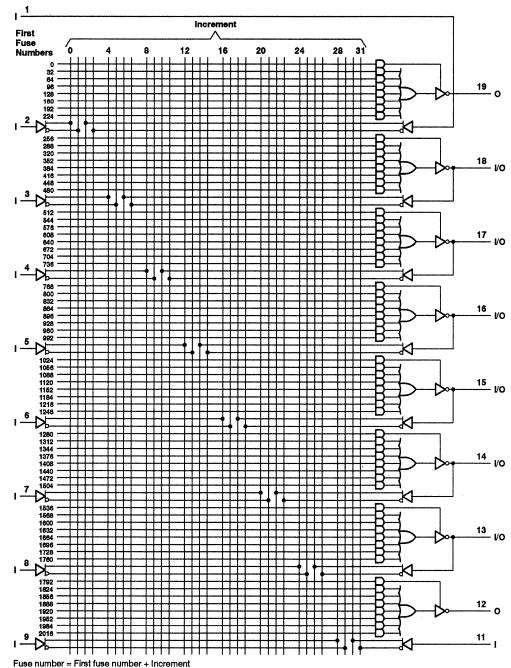

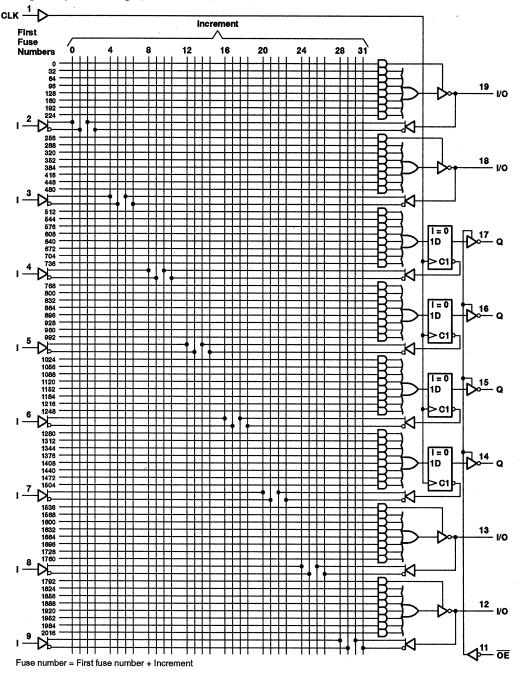

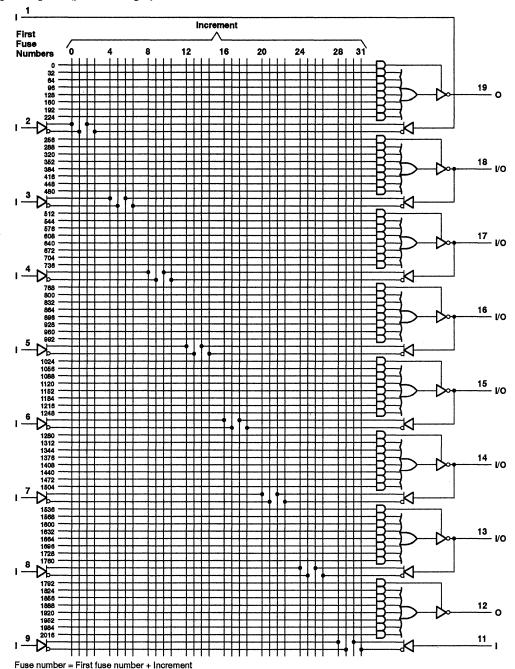

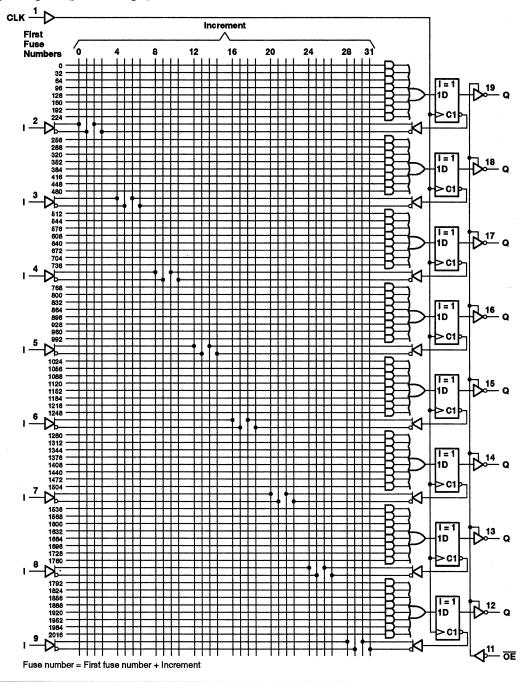

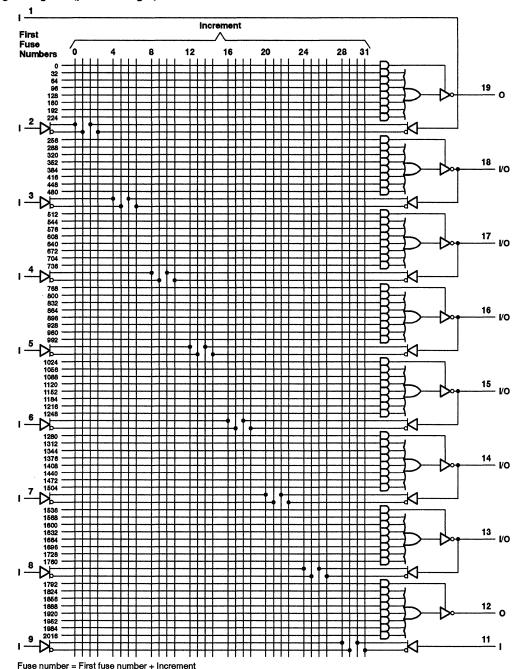

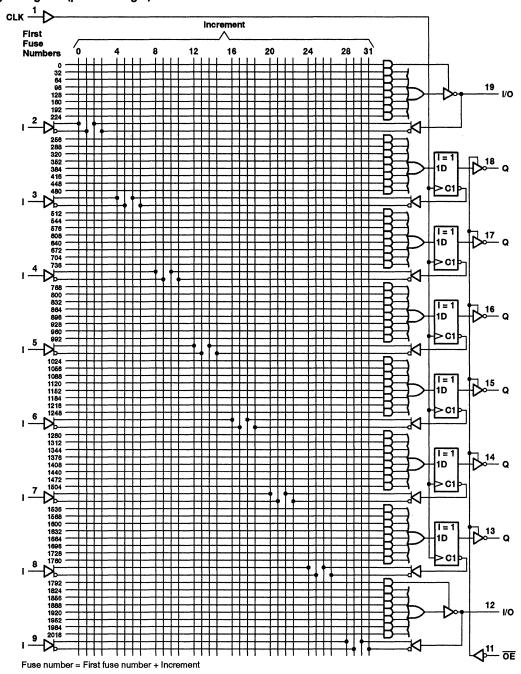

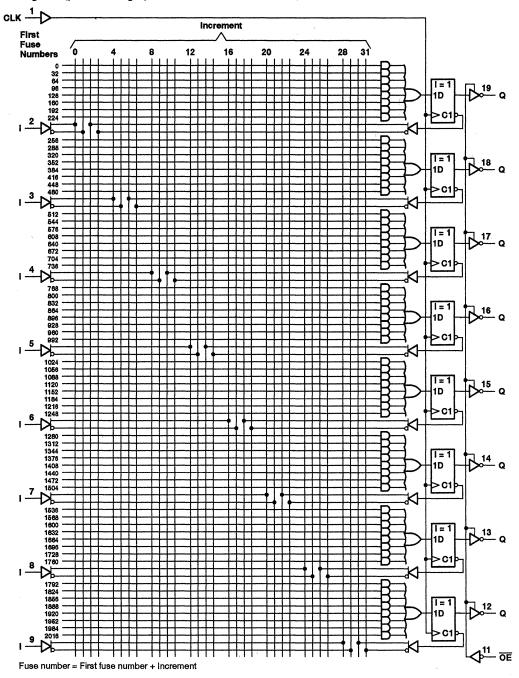

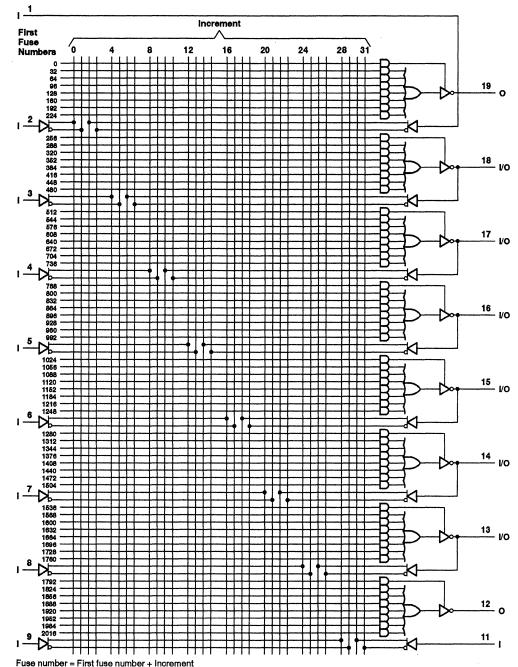

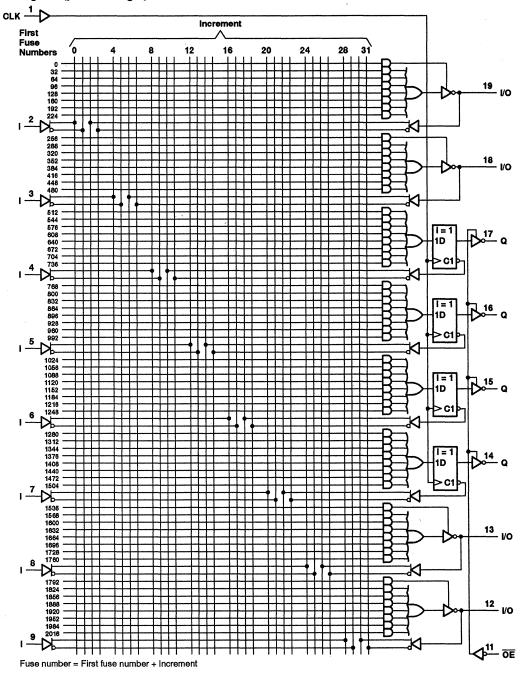

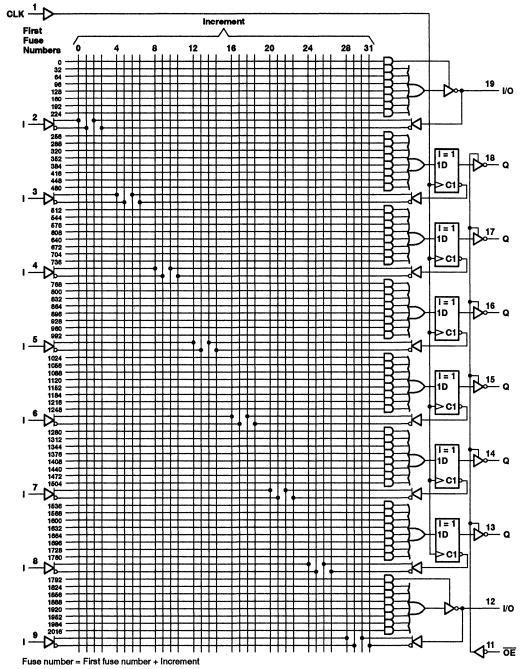

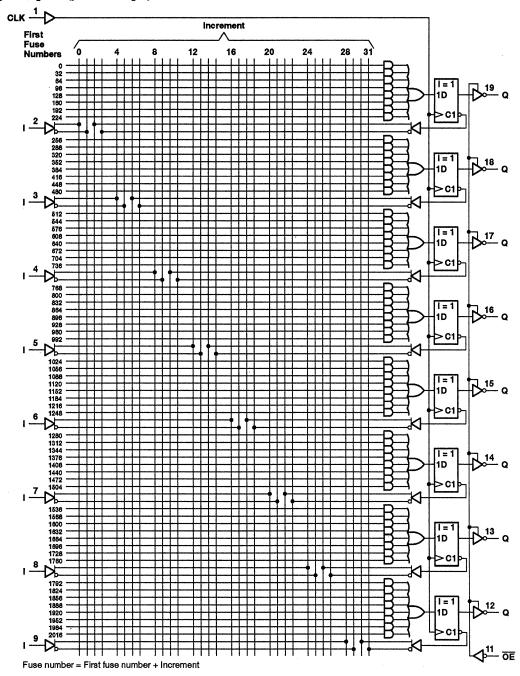

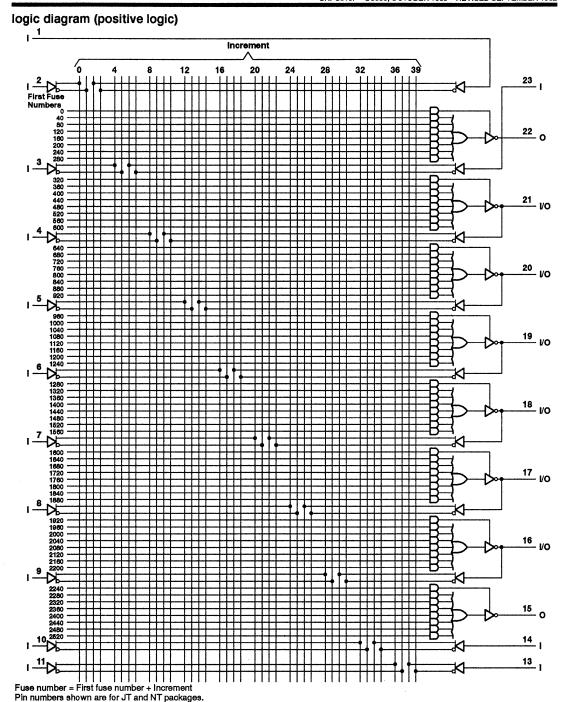

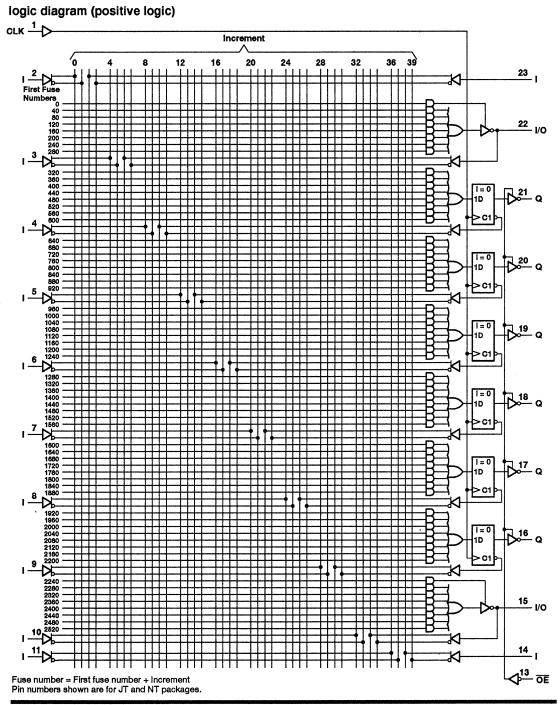

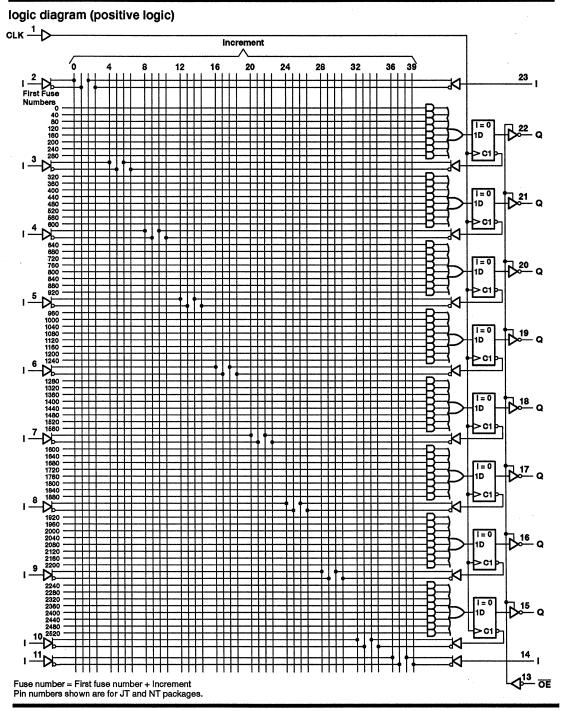

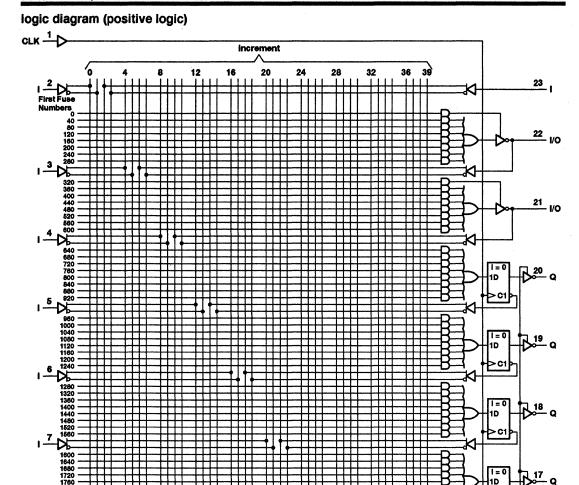

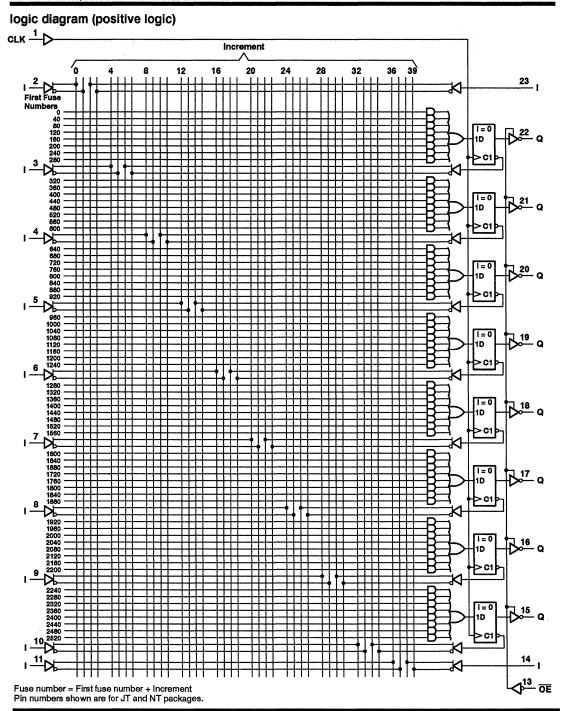

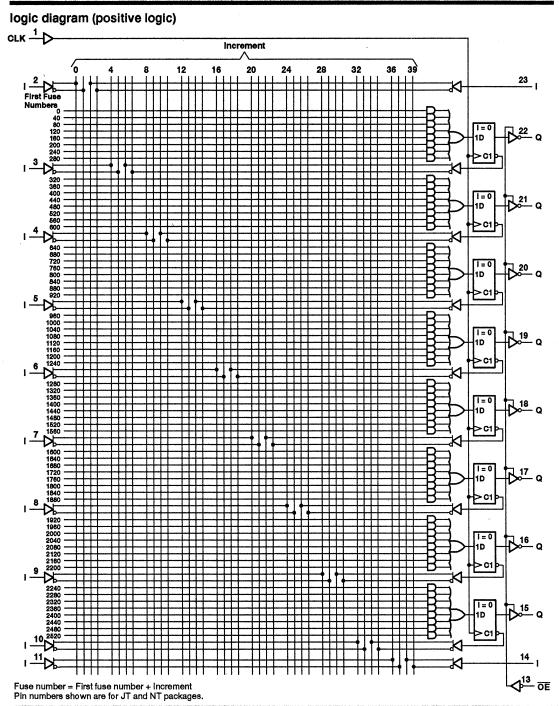

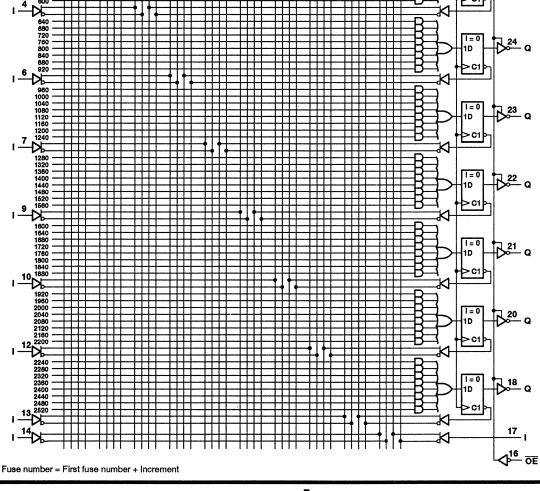

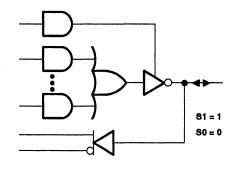

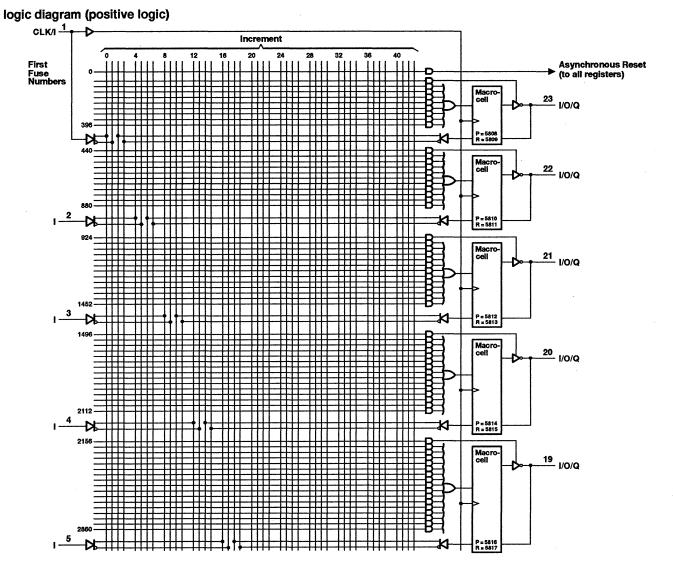

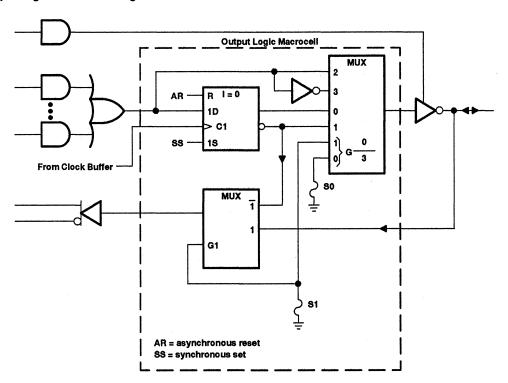

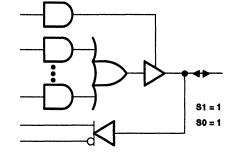

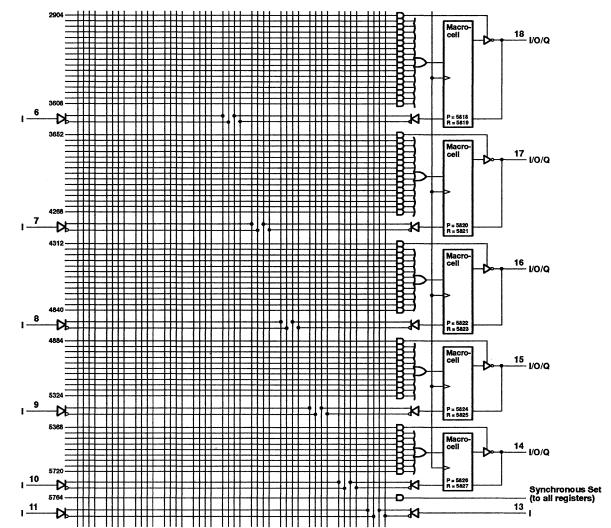

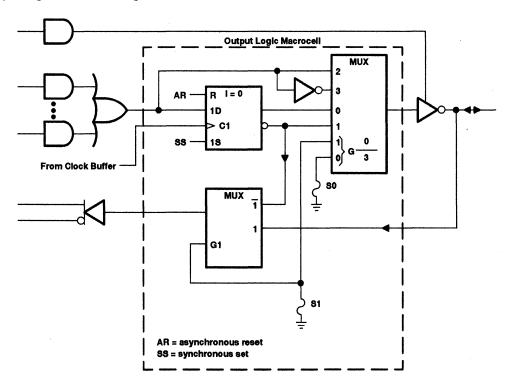

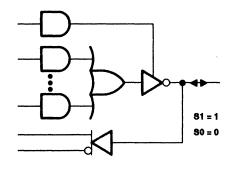

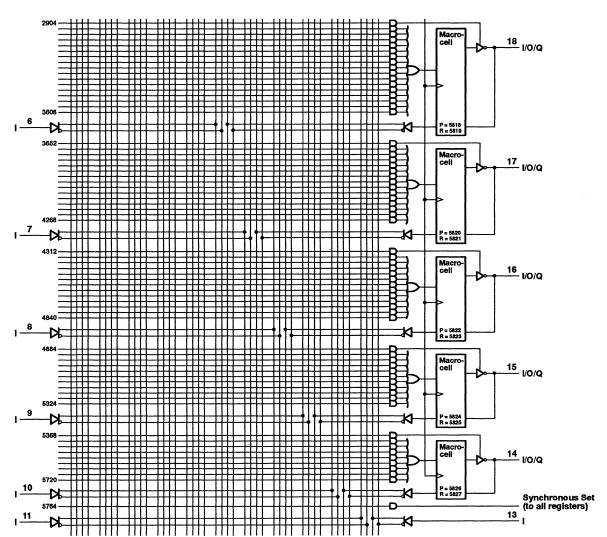

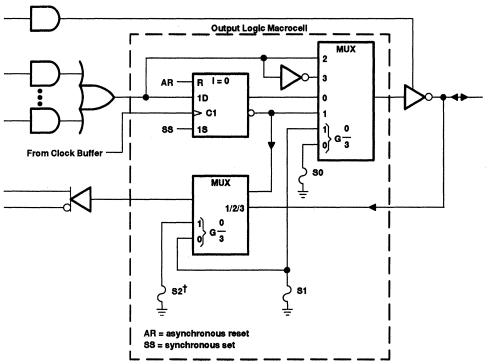

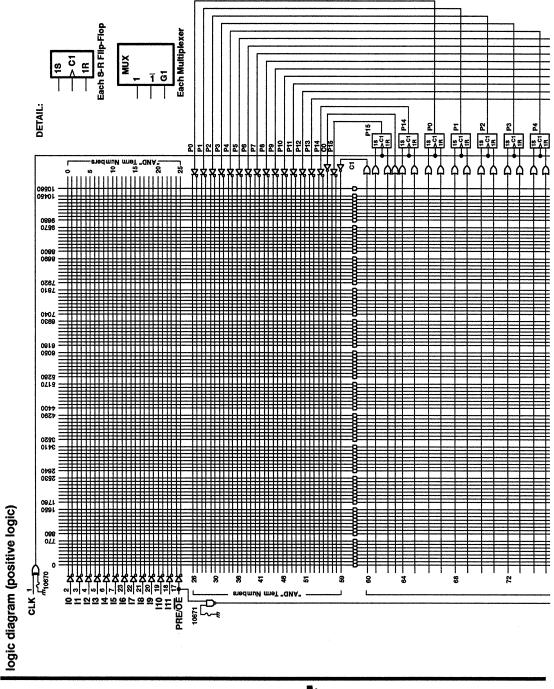

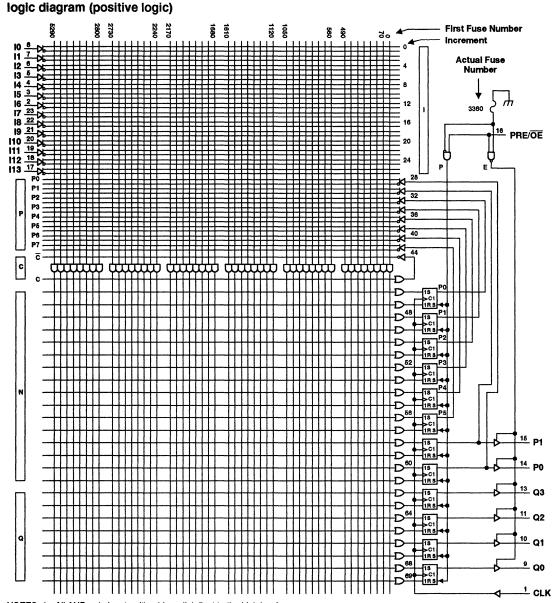

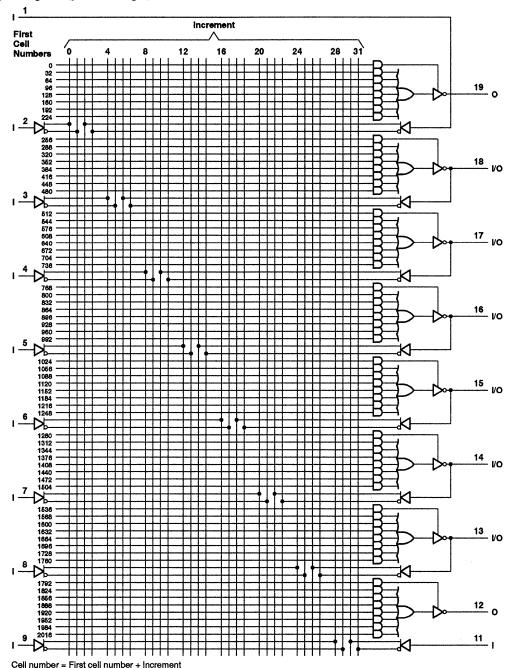

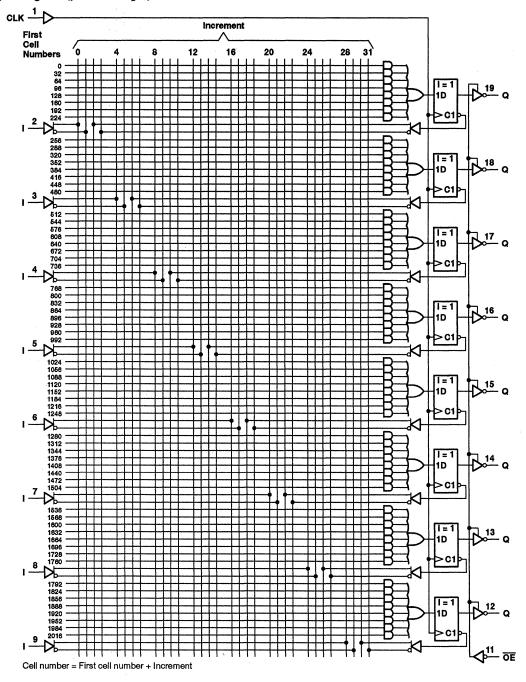

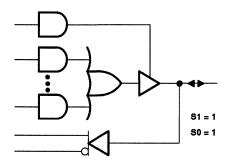

The logic diagram shows the complete EP330, while Figure 1 shows the basic EP330 macrocell. The internal architecture is organized with the familiar sum of products (AND-OR) structure. Inputs to the programmable AND array (shown running vertically in Figure 1) come from two sources: first, the true and complement of the ten dedicated input pins and second, the true and complement of the eight feedback signals, each one originating from an I/O architecture-control block. The 36-input AND array encompasses a total of 72 product terms distributed equally among the eight macrocells. Each product term (shown running horizontally in the logic diagram) represents a 36-input AND gate.

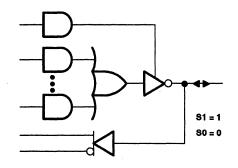

As shown in the logic diagram, the outputs of eight product terms are ORed together, then the output of the OR gate is sent as an input to an exclusive-OR gate. The purpose of this exclusive-OR gate is to allow the user to specify the polarity of the output signal by using the invert-select EPROM cell (active high if the EPROM cell is programmed and active low if it is not programmed).

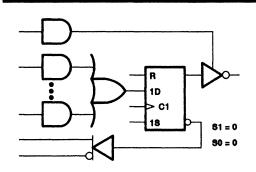

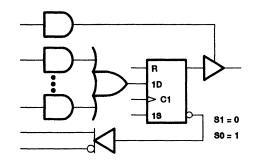

The exclusive-OR output then feeds the I/O architecture control block. The control block configures the output for registered or combinational operation. In the registered configuration, the output is registered via a positive edge-triggered D-type flip-flop. In this condition, the feedback signal going to the array is also registered and comes directly from the output of the D-type flip-flop. In the combinational configuration, the output is nonregistered and the feedback signal comes directly from the I/O pin. In the erased state, the EP330 contains the same architectural characteristics as the 'PAL16L8.

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

- NOTES: A. This diagram shows one of the eight macrocells within the EP330.

- B. The double-arrow lines (\$) show I/O feedback from a macrocell.

Figure 1. Logic Array Macrocell

## output-enable product term

The output enable (OE) product term determines whether an output signal is allowed to propagate to the output pin. If the output of the OE product term is low, then the output buffer becomes a high-impedance node, thus inhibiting the output signal from reaching the output pin. For combinational configurations, this OE product term can be used to allow for true bidirectional operation.

The EP330 contains eight separate OE product terms, one per I/O pin. If it is desired that all outputs be enabled or disabled simultaneously, use an identically programmed product term at each of the outputs. If different outputs are to be enabled under different conditions, different OE product terms for each specific output may be defined.

## I/O architecture

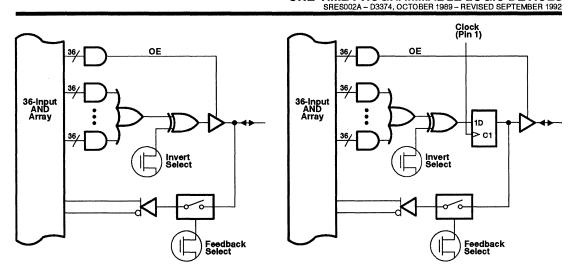

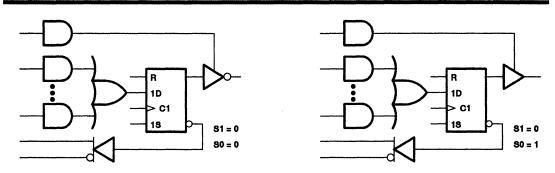

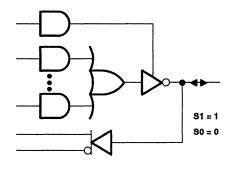

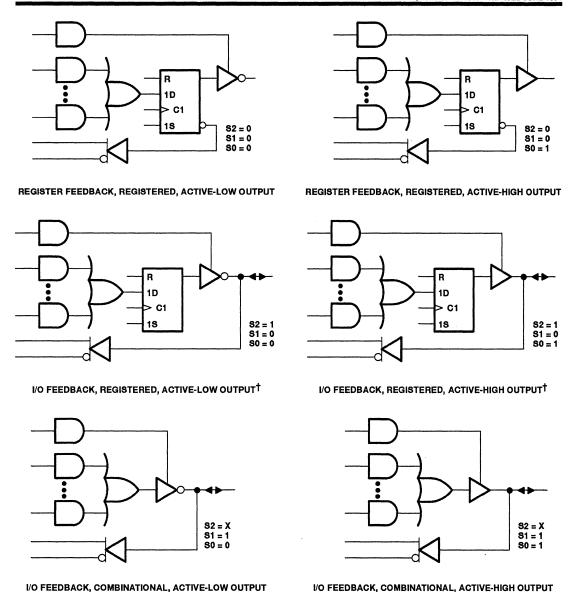

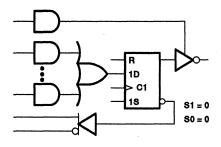

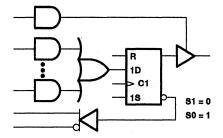

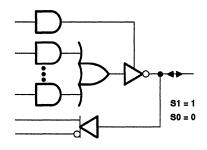

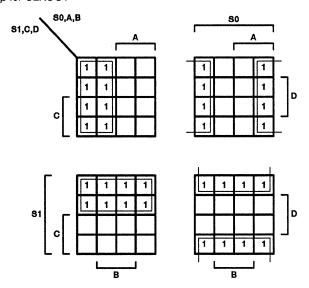

Figure 2 shows the different output configurations that can be chosen for any of the eight I/O pins on the EP330. Because of the individuality of each I/O architecture control block, both registered and combinational output can be chosen on a given EP330 device.

In the combinational configuration, either active-high or active-low output polarity can be chosen. Pin feedback or no feedback is also optional. In the registered configuration, the user has control over output polarity and may choose to use the internal feedback path or no feedback. Any I/O pin can be configured as a dedicated input by choosing no output and no feedback from the array. In the erased state, the I/O architecture is configured for a combinational active-low output with pin feedback.

| OUTPUT/POLARITY    | FEEDBACK  |

|--------------------|-----------|

| Combinational/High | Pin, None |

| Combinational/Low  | Pin, None |

| None               | Pin       |

| OUTPUT/POLARITY | FEEDBACK         |

|-----------------|------------------|

| D Register/High | D Register, None |

| D Register/Low  | D Register, None |

| None            | D Register       |

(a) COMBINATIONAL CONFIGURATION

(b) REGISTERED CONFIGURATION

Figure 2. I/O Configurations

## **PLD** compatibility

Figures 2(a) and 2(b) show how an EP330 can be configured as a drop-in replacement for two commonly used members of the 20-pin PLD family: the 'PAL16L8 and the 'PAL16R8. When configured in these manners, the EP330 is both a functional replacement, as well as a pin-to-pin replacement, for the 'PAL16L8 and 'PAL16R8.

Tables 1 and 2 provide additional information concerning the EP330 as a replacement for the 20-pin PLD family of devices.

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

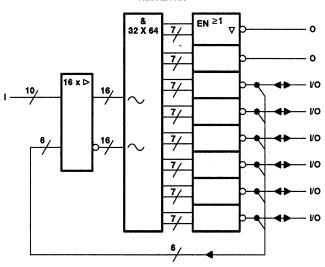

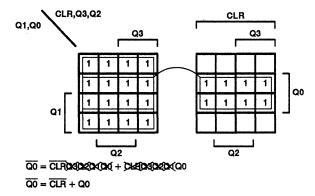

- Invert Select EPROM cell is in the erased state providing active-low outputs.

- Combinational Mode is chosen providing Combinational Output with Input (Pin) Feedback.

- 8-product-term OR gate compared to 7-product-term OR gate on 'PAL16L8.

- Pin feedback to the array at 12 through 19 is not available in 'PAL16L8.

Figure 3. EP330 Configuration for Replacing a 'PAL16L8

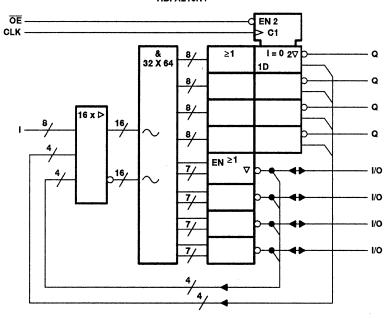

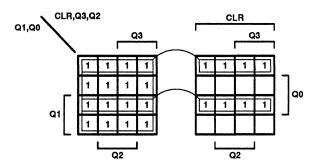

- Invert Select EPROM cell is in the erased state providing active-low outputs.

- Registered Mode is chosen providing Registered Output with Registered Feedback.

- Complement of pin 11 is used as common OE term for all eight output pins.

Figure 4. EP330 Configuration for Replacing a 'PAL16R8

## **EP330 SERIES** HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

Table 1. Configurations for 20-Pin PLD Replacement

| PLD         | EP330      | EP330            | I/O                | OUTPUT/       | FEEDBACK |

|-------------|------------|------------------|--------------------|---------------|----------|

| PART NUMBER | PIN NUMBER | MACROCELL NUMBER | CONFIGURATION MODE | POLARITY      | PEEDBAOK |

| 10H8        | 12-19      | 1-8              | Combinational      | Comb/High     | None     |

| 10L8        | 12-19      | 1-8              | Combinational      | Comb/Low      | None     |

|             | 12         | 8                | Combinational      | None          | Pin      |

| 12H6        | 13-18      | 2-7              | Combinational      | Comb/High     | None     |

|             | 19         | 1                | Combinational      | None          | Pin      |

|             | 12         | 8                | Combinational      | None          | Pin      |

| 12L6        | 13-18      | 2-7              | Combinational      | Comb/Low      | None     |

|             | 19         | 1                | Combinational      | None          | Pin      |

|             | 12-13      | 7-8              | Combinational      | None          | Pin      |

| 14H4        | 14-17      | 3-6              | Combinational      | Comb/High     | None     |

|             | 18-19      | 1-2              | Combinational      | None          | Pin      |

|             | 12-13      | 7-8              | Combinational      | None          | Pin      |

| 14L4        | 14-17      | 3-6              | Combinational      | Comb/Low      | None     |

|             | 18-19      | 1-2              | Combinational      | None          | Pin      |

|             | 12-14      | 6-8              | Combinational      | None          | Pin      |

| 16C1        | 15         | 5                | Combinational      | Comb/Low      | None     |

| 1001        | 16         | 4                | Combinational      | Comb/High     | None     |

|             | 17-19      | 1-3              | Combinational      | None          | Pin      |

|             | 12-14      | 6-8              | Combinational      | None          | Pin      |

| 16H2        | 15-16      | 4-5              | Combinational      | Comb/High     | None     |

|             | 17-19      | 1-3              | Combinational      | None          | Pin      |

|             | 12-14      | 6-8              | Combinational      | None          | Pin      |

| 16L2        | 15-16      | 4-5              | Combinational      | Comb/Low      | None     |

|             | 17-19      | 1-3              | Combinational      | None          | Pin      |

| 16H8        | 12         | 8                | Combinational      | Comb/High/Z   | None     |

| &           | 13-18      | 2-7              | Combinational      | Comb/High/Z   | Comb     |

| 16HD8       | 19         | 1                | Combinational      | Comb/High/Z   | None     |

| 16L8        | 12         | 8                | Combinational      | Comb/Low/Z    | None     |

| &           | 13-18      | 2-7              | Combinational      | Comb/Low/Z    | Comb     |

| 16LD8       | 19         | 1                | Combinational      | Comb/Low/Z    | None     |

|             | 12-13      | 7-8              | Combinational      | Comb/Low/Z    | Comb     |

| 16R4        | 14-17      | 3-6              | Registered         | Reg/Low/Z     | Reg      |

|             | 18-19      | 1-2              | Combinational      | Comb/Low/Z    | Comb     |

|             | 12         | 8                | Combinational      | Comb/Low/Z    | Comb     |

| 16R6        | 13-18      | 2-7              | Registered         | Reg/Low/Z     | Reg      |

|             | 19         | 1                | Combinational      | Comb/Low/Z    | Comb     |

| 16R8        | 12-19      | 1-8              | Registered         | Reg/Low/Z     | Reg      |

|             | 12         | 8                | Combinational      | Comb/Option/Z | None     |

| 16P8        | 13-18      | 2-7              | Combinational      | Comb/Option/Z | Comb     |

|             | 19         | 1                | Combinational      | Comb/Option/Z | None     |

|             | 12-13      | 7-8              | Combinational      | Comb/Option/Z | Comb     |

| 16RP4       | 14-17      | 3-6              | Registered         | Reg/Option/Z  | Reg      |

|             | 18-19      | 1-2              | Combinational      | Comb/Option/Z | Comb     |

|             | 12         | 8                | Combinational      | Comb/Option/Z | Comb     |

| 16RP6       | 13-18      | 2-7              | Registered         | Re/Option/Z   | Reg      |

|             | 19         | 1                | Combinational      | Comb/Option/Z | Comb     |

| 16RP8       | 12-19      | 1-8              | Registered         | Reg/Option/Z  | Reg      |

## **EP330 SERIES HIGH-PERFORMANCE 8-MACROCELL** ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## Table 2. Device Specifications<sup>†</sup>

| SYMBOL           | PARAMETER                     | HIGH-SPI  | ED EPLD   | HIGH-SPEED PLD | SERIES '16XXB/-15 |

|------------------|-------------------------------|-----------|-----------|----------------|-------------------|

| STMBUL           | PARAMETER                     | EP330-12C | EP330-15C | 'PAL16L8B/-15  | 'PAL16R8B/-15     |

| lcc              | Supply current active         | 75 mA     | 75 mA     | 180 mA         | 180 mA            |

| t <sub>pd</sub>  | Input to nonregistered output | 12 ns     | 15 ns     | 15 ns          | N/A               |

| tCO1             | Clock to output delay         | 8 ns      | 10 ns     | N/A            | 12 ns             |

| t <sub>su</sub>  | Input setup time              | 6 ns      | 8 ns      | N/A            | 15 ns             |

| f <sub>max</sub> | Max frequency                 | 125 MHz   | 100 MHz   | N/A            | 37 MHz            |

<sup>†</sup> Over commercial temperature range

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                          |                   |

|-----------------------------------------------------------------------------|-------------------|

| Instantaneous supply voltage range, V <sub>CC</sub> (t ≤ 20 ns)             | –2 V to 7 V       |

| Programming supply voltage range, Vpp                                       | 0.3 V to 14 V     |

| Instantaneous programming supply voltage range, V <sub>PP</sub> (t ≤ 20 ns) | –2 V to 14 V      |

| Input voltage range, V <sub>1</sub>                                         | 0.3 V to 7 V      |

| Instantaneous input voltage range, V <sub>I</sub> (t ≤ 20 ns)               | –2 V to 7 V       |

| V <sub>CC</sub> or GND current range                                        | –160 mA to 160 mA |

| Operating free-air temperature range, T <sub>A</sub>                        | –65°C to 135°C    |

| Storage temperature range                                                   | 65°C to 150°C     |

NOTE 1: All voltage values are with respect to GND terminal.

# EP330-12C, EP330-15C HIGH-PERFORMANCE 8-MACROCELL **ONE-TIME PROGRAMMABLE LOGIC DEVICES**

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## recommended operating conditions

|                 | -                                    |     | EP3 | 30-12C               | EP330-15C |                      | UNIT  |

|-----------------|--------------------------------------|-----|-----|----------------------|-----------|----------------------|-------|

|                 |                                      | M   | IN  | MAX                  | MIN       | MAX                  | Civil |

| Vcc             | Supply voltage                       | 4.7 | 75  | 5.25                 | 4.75      | 5.25                 | V     |

| ٧į              | Input voltage                        |     | 0   | Vcc                  | 0         | Vcc                  | V     |

| VIH             | High-level input voltage             |     | 2   | V <sub>CC</sub> +0.3 | 2         | V <sub>CC</sub> +0.3 | V     |

| VIL             | Low-level input voltage (see Note 2) | -0  | .3  | 0.8                  | -0.3      | 0.8                  | ٧     |

| ٧o              | Output voltage                       |     | 0   | Vcc                  | 0         | Vcc                  | ٧     |

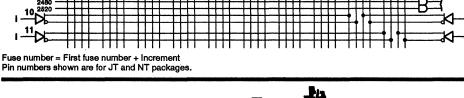

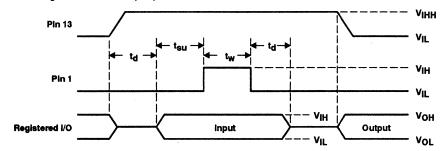

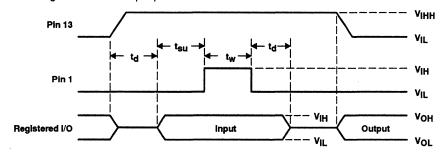

| t <sub>W</sub>  | Pulse duration, CLK high or low      |     | 4   |                      | 5         |                      | ns    |

| t <sub>su</sub> | Setup time, input                    |     | 6   |                      | 8         |                      | ns    |

| th              | Hold time, input                     |     | 0   |                      | 0         |                      | ns    |

| t <sub>r</sub>  | Rise time, input                     |     |     | 20                   |           | 20                   | ns    |

| t <sub>f</sub>  | Fall time, input                     |     |     | 20                   |           | 20                   | ns    |

| TA              | Operating free-air temperature       |     | 0   | 70                   | 0         | 70                   | °C    |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels

## electrical characteristics over recommended ranges of supply voltage and free-air temperature (unless otherwise noted)

| PARAMETER        |                           | TEST CONDITIONS                                      |               | EP330-12C<br>EP330-15C |                  |     | UNIT |

|------------------|---------------------------|------------------------------------------------------|---------------|------------------------|------------------|-----|------|

|                  |                           |                                                      |               | MIN                    | TYP <sup>†</sup> | MAX |      |

| Vон              | High-level output voltage | CC = 4.75 V, IOH = -12 mA                            |               | 2.4                    |                  |     | ٧    |

| VoL              | Low-level output voltage  | CC = 4.75 V, I <sub>OL</sub> = 24 mA                 |               |                        |                  | 0.5 | ٧    |

| II               | Input current             | / <sub>I</sub> = 5.25 V or GND                       |               |                        |                  | ±10 | μА   |

| loz              | Off-state output current  | CC = 5.25 V, VO = VCC or GND                         |               |                        |                  | ±10 | μА   |

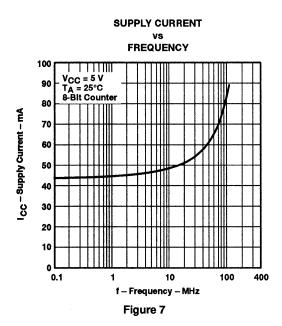

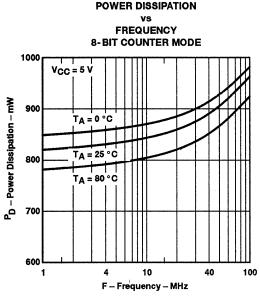

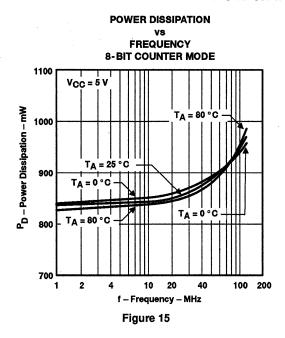

| Icc              | Supply current            | = 1 MHz, No load, Programmed as an 8                 | 8-bit counter |                        | 45               | 75  | mA   |

| Ci‡              | Input capacitance         | CC = 5 V, V <sub>I</sub> = 0, f = 1 MHz              |               |                        |                  | 10  | pF   |

| Co               | Output capacitance        | / <sub>CC</sub> = 5 V, V <sub>O</sub> = 0, f = 1 MHz |               |                        |                  | 15  | pF   |

| C <sub>clk</sub> | Clock capacitance         | CC = 5 V, V <sub>CLK</sub> = 0, f = 1 MHz            |               |                        |                  | 10  | pF   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C. ‡ The input capacitance at pin 11 is 20 pF maximum when used as a programming pin and with Vpp = 14 V.

## EP330-12C, EP330-15C HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 5)

|                    |                          | PARAMETER <sup>†</sup>      | EP330 | )-12C | EP330 | )-15C | UNIT |

|--------------------|--------------------------|-----------------------------|-------|-------|-------|-------|------|

|                    |                          | PARAMETER                   | MIN   | MAX   | MIN   | MAX   | UNIT |

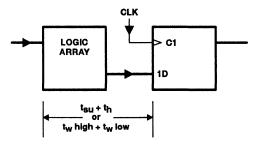

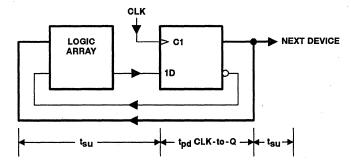

| f <sub>max</sub> ‡ |                          | With no feedback            | 125   |       | 100   |       |      |

|                    | Maximum frequency        | With internal feedback      | 100   |       | 100   |       | MHz  |

|                    |                          | With external feedback      | 71.4  |       | 55.6  |       | 1    |

| <sup>t</sup> pd1   | Input to nonregistered   | output delay (see Note 3)   |       | 12    |       | 15    | ns   |

| <sup>t</sup> pd2   | I/O to nonregistered ou  | tput delay (see Note 3)     |       | 13    |       | 16    | ns   |

| tio                | I/O input and buffer del | ay (see Note 3)             |       | 1     |       | 1     | ns   |

| t <sub>co</sub>    | Clock input to registere | d output delay (see Note 3) |       | 8     |       | 10    | ns   |

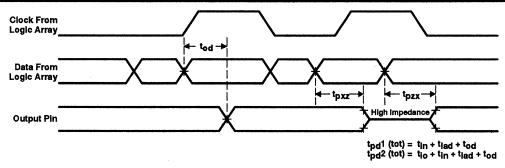

| tPZX               | Output enable time (se   | e Note 4)                   |       | 12    |       | 15    | ns   |

| <sup>t</sup> PXZ   | Output disable time (se  | ee Note 4)                  |       | 12    |       | 15    | ns   |

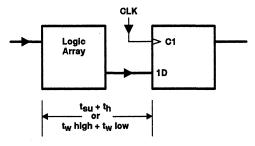

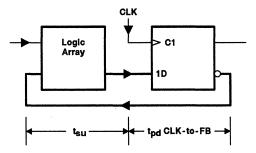

| tont               | Minimum clock period (   | internal)                   |       | 10    |       | 12    | ns   |

<sup>†</sup> Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other TI data sheets or to those shown in glossaries in TI data books is coincidental. The meanings may not be the same.

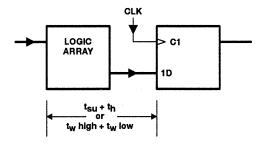

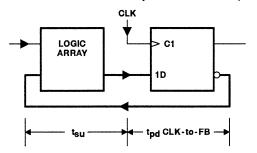

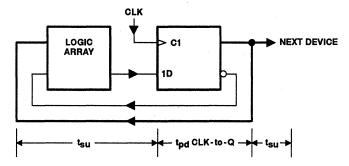

‡

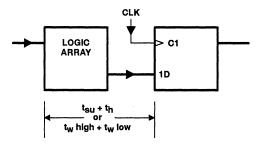

$$f_{max}$$

with no feedback =  $\frac{1}{t_W \ high \ + \ t_W \ low}$ ,  $f_{max}$  with internal feedback =  $\frac{1}{t_{cnt}}$ ,

$$f_{max}$$

with external feedback =  $\frac{1}{t_{su} + t_{co}}$ .

$f_{\mbox{max}}$  with internal feedback is programmed as an 8-bit counter.

NOTES: 3. This parameter is measured with only one output switching.

4. This is for an output voltage change of 500 mV.

# EP330-251 HIGH-PERFORMANCE 8-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES002A - D3374, OCTOBER 1989 - REVISED SEPTEMBER 1992

## recommended operating conditions

|                 |                                      | MIN  | MAX                 | UNIT |

|-----------------|--------------------------------------|------|---------------------|------|

| Vcc             | Supply voltage                       | 4.5  | 5.5                 | ٧    |

| Vi              | Input voltage                        | 0    | Vcc                 | ٧    |

| VIH             | High-level input voltage             | 2    | V <sub>CC+0.3</sub> | ٧    |

| VIL             | Low-level input voltage (see Note 2) | -0.3 | 0.8                 | ٧    |

| ۷o              | Output voltage                       | 0    | Vcc                 | V    |

| t <sub>w</sub>  | Pulse duration, CLK high or low      | 12   |                     | ns   |

| t <sub>su</sub> | Setup time, input                    | 15   |                     | ns   |

| th              | Hold time, input                     | 0    |                     | ns   |

| t <sub>r</sub>  | Rise time, input                     |      | 20                  | กร   |

| tf              | Fall time, input                     |      | 20                  | ns   |

| TA              | Operating free-air temperature       | -40  | 85                  | °C   |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels only.

# electrical characteristics over recommended ranges of supply voltage and free-air temperature (unless otherwise noted)

| ,                | PARAMETER                 |                             | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|------------------|---------------------------|-----------------------------|-----------------------------------------|-----|-----|-----|------|

| Vон              | High-level output voltage | V <sub>CC</sub> = 4.5 V,    | I <sub>OH</sub> = -12 mA                | 2.4 |     |     | ٧    |

| VOL              | Low-level output voltage  | $V_{CC} = 4.5 \text{ V},$   | I <sub>OL</sub> = 24 mA                 |     |     | 0.5 | ٧    |

| 11               | Input current             | V <sub>I</sub> = 5.5 V or G | ND                                      |     |     | ±10 | μА   |

| loz              | Off-state output current  | V <sub>CC</sub> = 5.5 V,    | VO = VCC or GND                         |     |     | ±10 | μΑ   |

| Icc              | Supply current            | f = 1 MHz,                  | No load, Programmed as an 8-bit counter |     | 45  | 75  | mA   |

| Ci               | Input capacitance         | V <sub>CC</sub> = 5 V,      | V <sub>I</sub> = 2 V, f = 1 MHz         |     |     | 10  | pF   |

| Co               | Output capacitance        | V <sub>CC</sub> = 5 V,      | $V_O = 2 V$ , $f = 1 MHz$               |     |     | 15  | рF   |

| C <sub>clk</sub> | Clock capacitance         | V <sub>CC</sub> = 5 V,      | V <sub>CLK</sub> = 2 V, f = 1 MHz       |     |     | 10  | pF   |

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 5)

| PARAMETER <sup>‡</sup> |                                                     |                        |      | MAX | UNIT |  |

|------------------------|-----------------------------------------------------|------------------------|------|-----|------|--|

| f <sub>max</sub> §     | Maximum frequency                                   | With no feedback       | 41.6 |     |      |  |

|                        |                                                     | With internal feedback | 41.6 |     | MHz  |  |

|                        |                                                     | With external feedback | 28.5 |     |      |  |

| <sup>t</sup> pd1       | Input to nonregistered output delay (see Note 3)    |                        |      | 25  | ns   |  |

| tpd2                   | I/O to nonregistered output delay (see Note 3)      |                        |      | 26  | ns   |  |

| tio                    | I/O input and buffer delay (see Note 3)             |                        |      | 1   | ns   |  |

| t <sub>co</sub>        | Clock input to registered output delay (see Note 3) |                        |      | 15  | ns   |  |

| tPZX                   | Output enable time (see Note 4)                     |                        |      | 25  | ns   |  |

| tpxz                   | Z Output disable time (see Note 4)                  |                        |      | 25  | ns   |  |

| t <sub>cnt</sub>       | nt Minimum clock period (internal)                  |                        |      | 24  | ns   |  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

§ f<sub>max</sub> with no feedback =

$$\frac{1}{t_W \text{ high } + t_W \text{ low}}$$

, f<sub>max</sub> with internal feedback =  $\frac{1}{t_{cnt}}$ ,

fmax with external feedback =

$$\frac{1}{tsu + tco}$$

f<sub>max</sub> with internal feedback is programmed as an 8-bit counter.

NOTES: 3. This parameter is measured with only one output switching.

4. This is for an output voltage change of 500 mV.

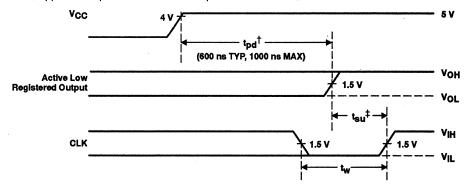

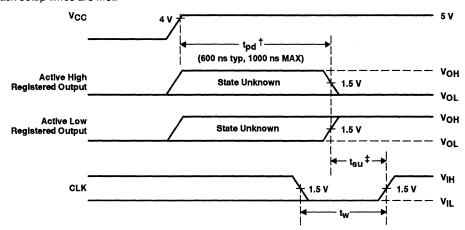

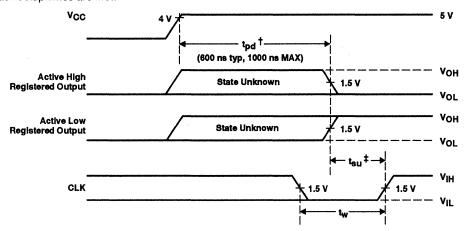

PRODUCT PREVIEW Information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Exass instruments reserves the right to change or discontinue these products without notice.

<sup>&</sup>lt;sup>‡</sup> Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other TI data sheets or to those shown in glossaries in TI data books is coincidental. The meanings may not be the same.

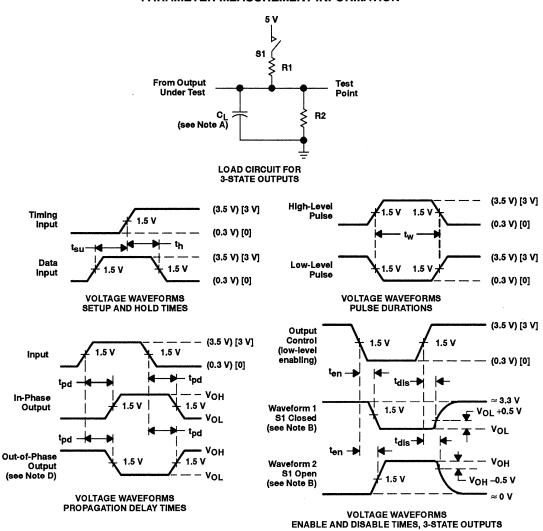

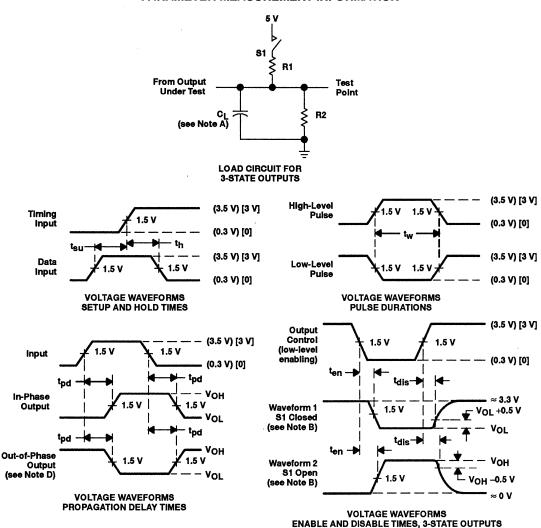

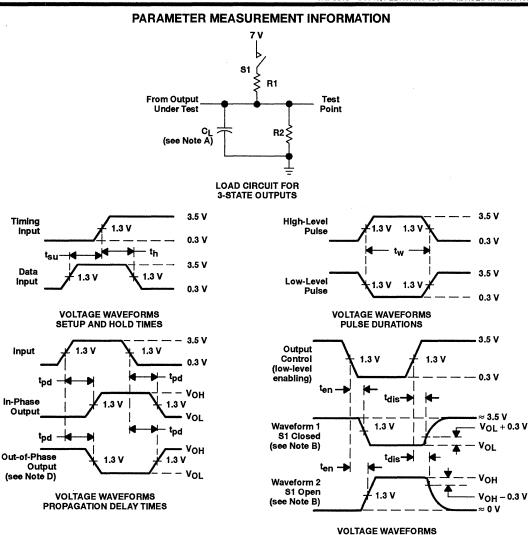

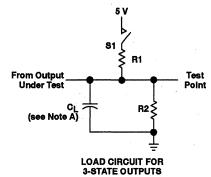

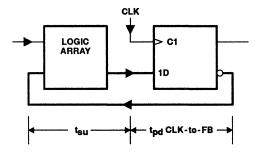

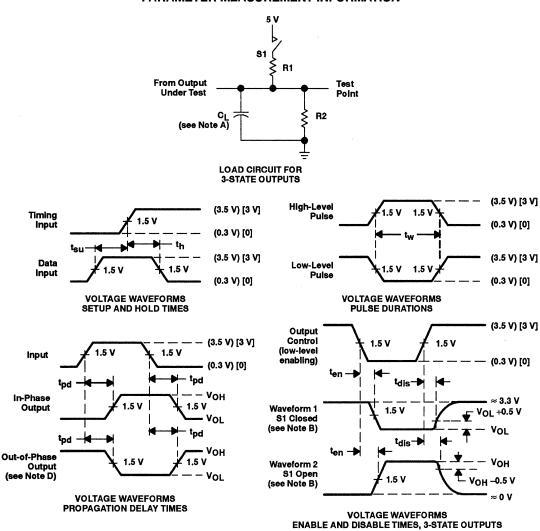

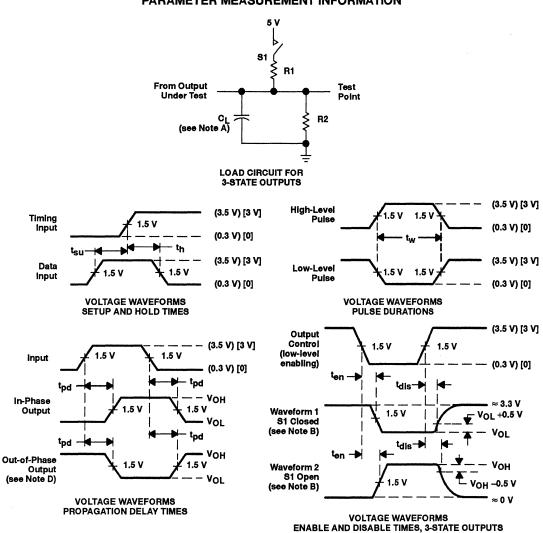

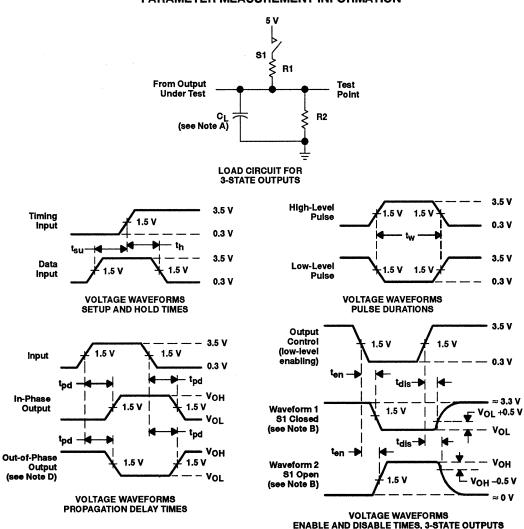

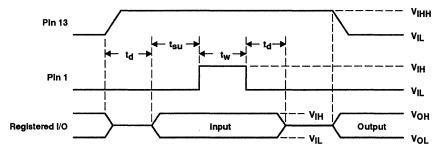

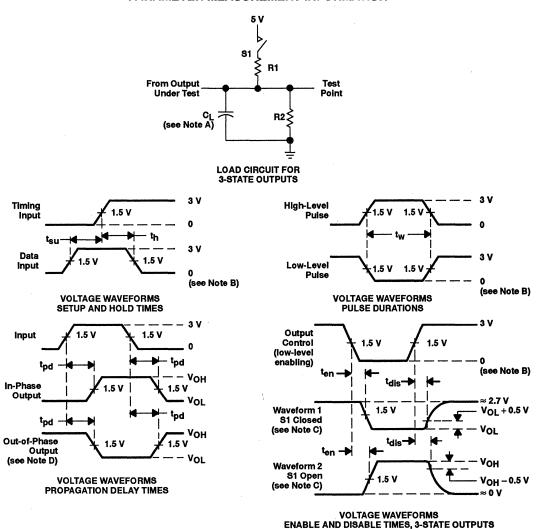

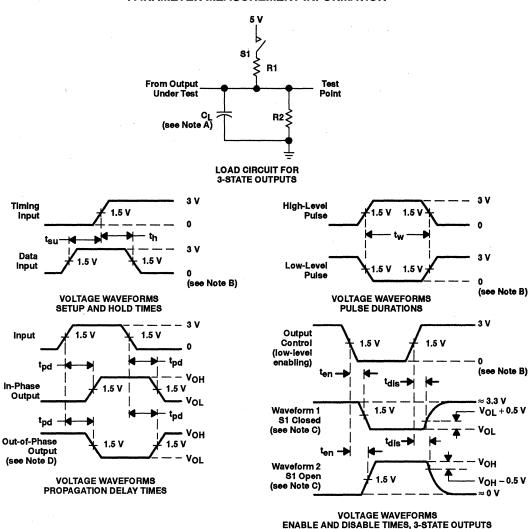

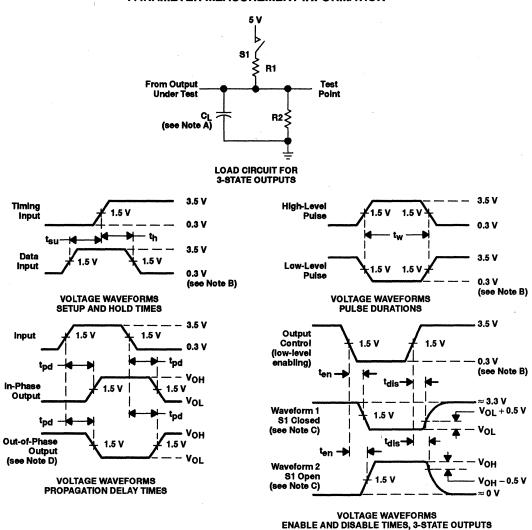

## PARAMETER MEASUREMENT INFORMATION

## functional testing

The EP330 is functionally tested through complete testing of each programmable EPROM bit and all internal logic elements, thus ensuring 100% programming yield.

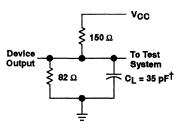

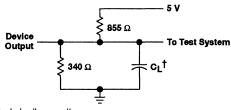

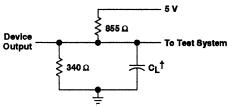

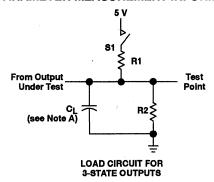

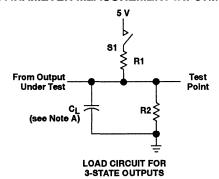

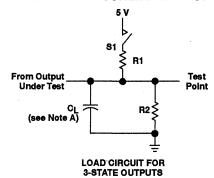

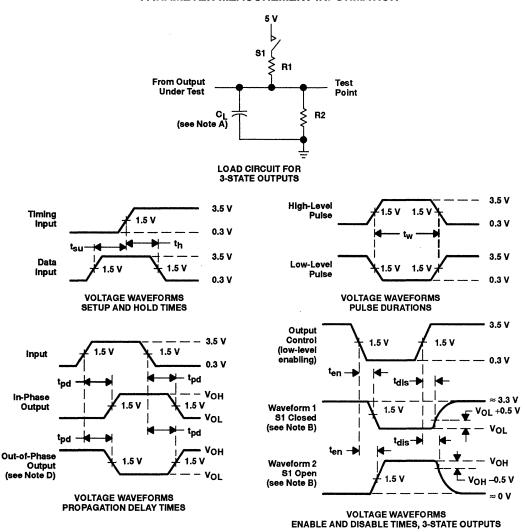

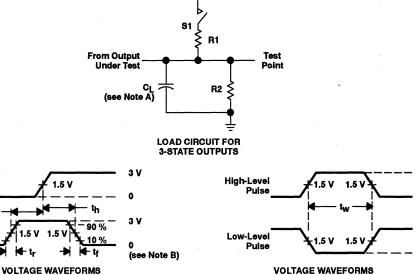

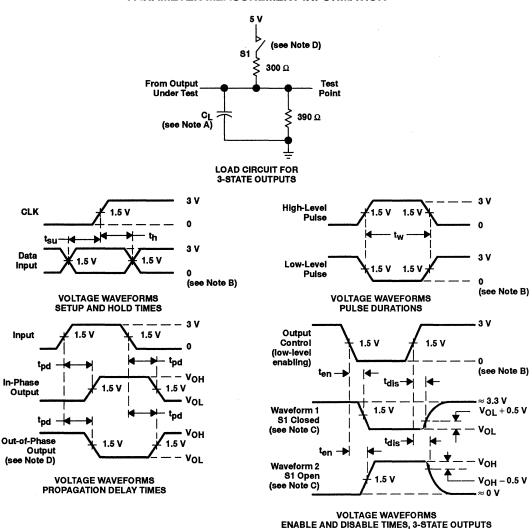

<sup>†</sup> Includes probe and circuit capacitance. Equivalent loads may be used for testing.

Figure 5. Dynamic Test Circuit

## design security

The EP330 contains a programmable design-security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied or retrieved. Therefore, a very high level of design control is achieved since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset by erasing the cells in the device.

## latch-up

The EP330 input, I/O, and clock pins have been carefully designed to resist the latch-up that is inherent in CMOS structures. The EP330 pins will not latch up for input voltages between -1 V and  $V_{CC}$  + 1 V with currents up to 250 mA. During transitions, the inputs may undershoot to -2 V for periods of less than 20 ns.

Although the programming pin (pin 11) is designed to resist latch-up to the 13.5-V limit, during positive-current latch-up testing, the verify mode (pin 1) and program mode (pin 11) can be inadvertently entered into, causing current flow in the pins. This should not be construed as latch-up.

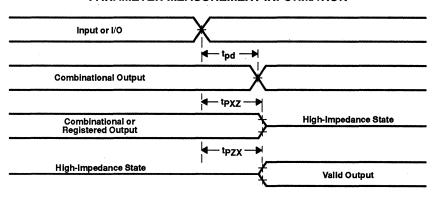

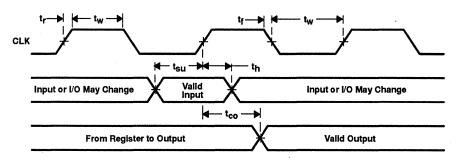

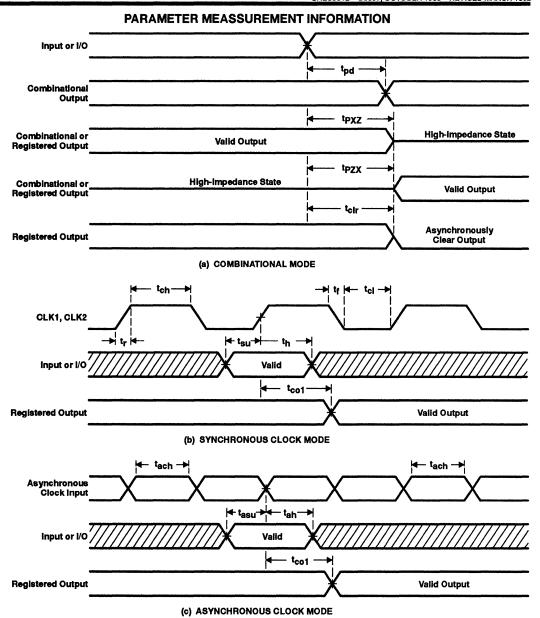

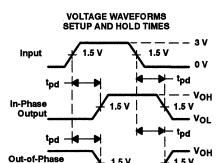

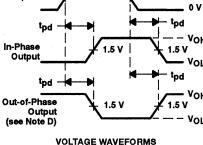

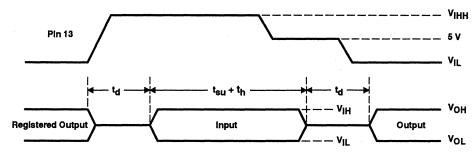

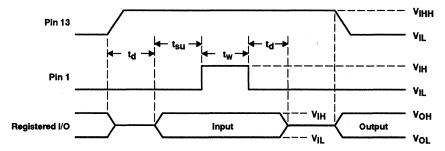

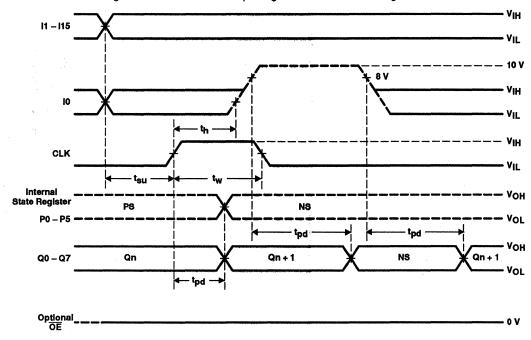

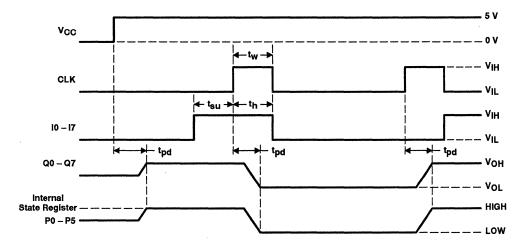

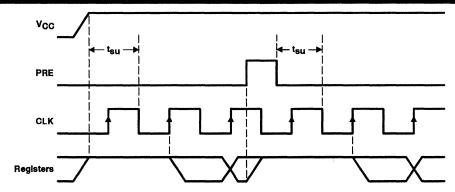

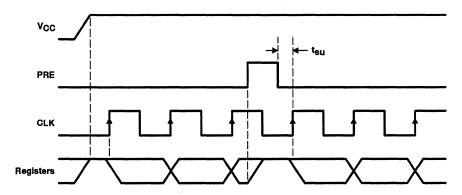

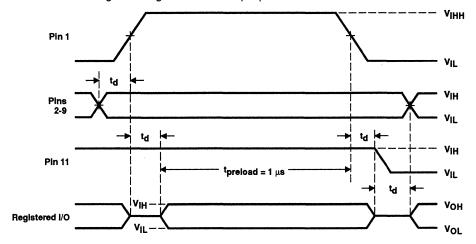

#### PARAMETER MEASUREMENT INFORMATION

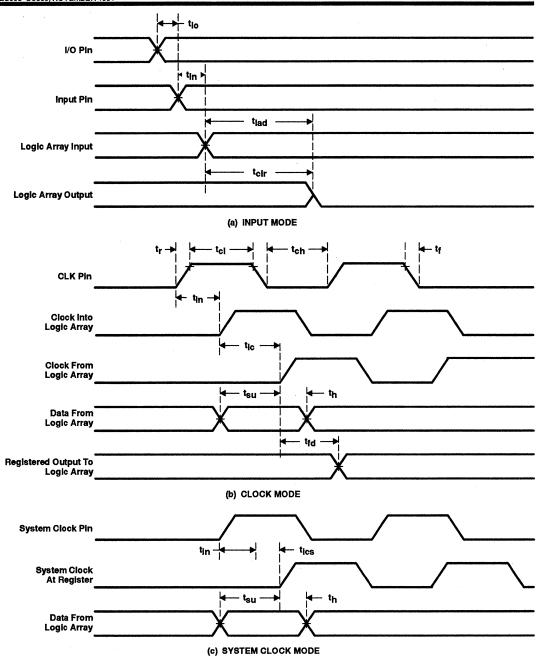

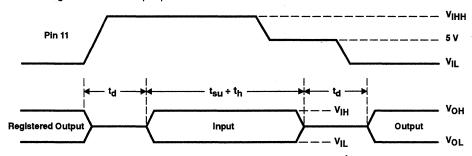

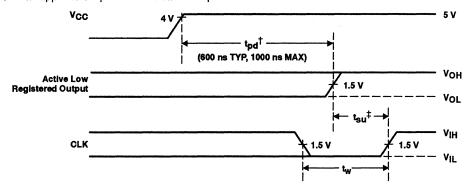

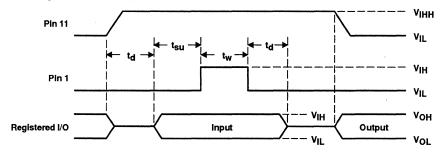

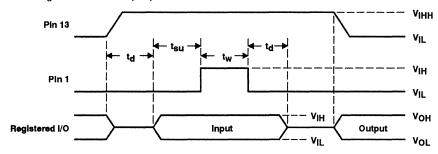

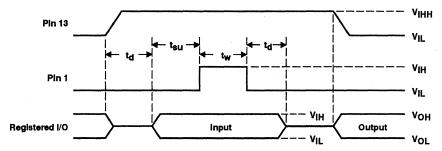

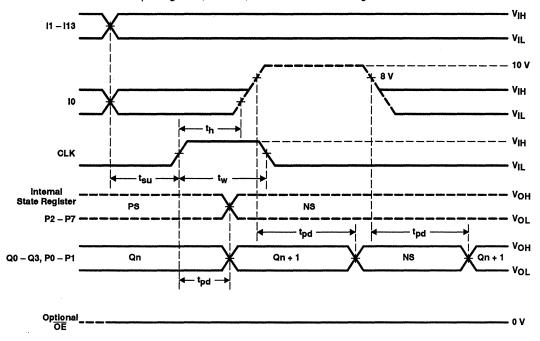

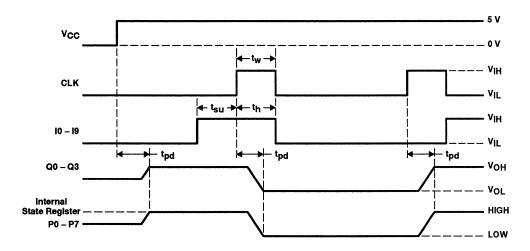

#### (a) COMBINATIONAL MODE

#### (b) SYNCHRONOUS CLOCK MODE

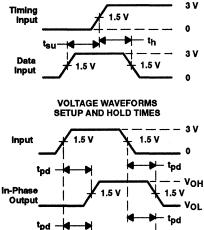

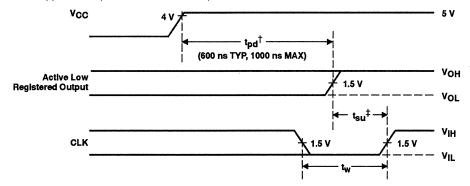

NOTES: A. Rise time  $(t_r)$  and fall time  $(t_f) < 3$  ns

- B. tw is measured at 0.3 V and 2.7 V. All other timing is measured at 1.5 V, except tpzx and tpxz which are measured for an output voltage change of 500 mV.

- C. Input voltage levels at 0 V and 3 V

Figure 6. Voltage Waveforms

#### TYPICAL CHARACTERISTICS

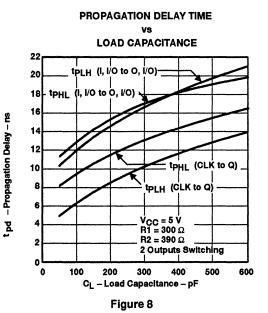

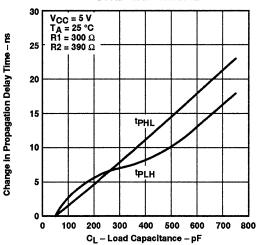

**CHANGE IN PROPAGATION DELAY TIME** ٧s LOAD CAPACITANCE 13 V<sub>CC</sub> = 5 V 12 T<sub>A</sub> = 25°C R1 = 150 Ω Change in Propagation Delay Time - ns 11  $R2 = 82 \Omega$ 10 tpHI 8 7 5 **tPLH** 3 2 0 100 200 300 400 500 600 700 800 900 0 CL - Load Capacitance - pF

Figure 8

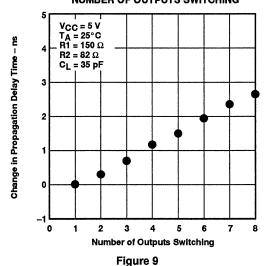

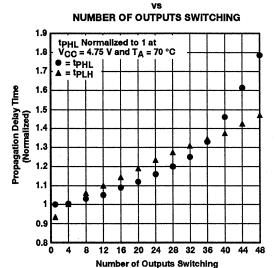

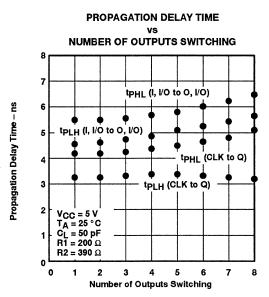

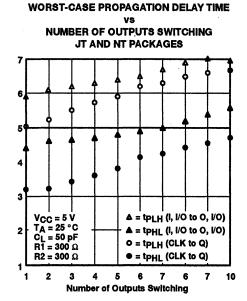

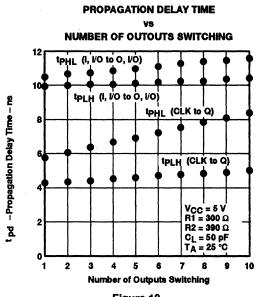

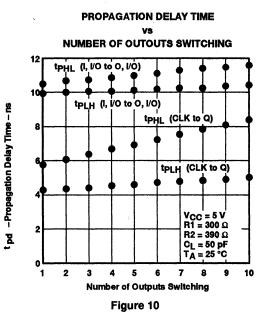

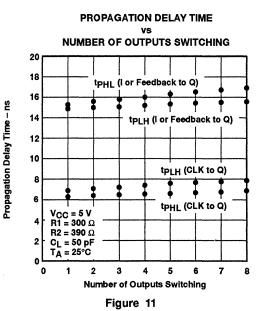

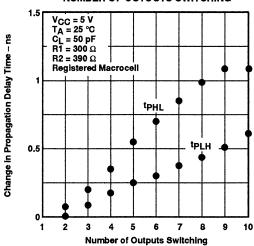

# CHANGE IN PROPAGATION DELAY TIME

### NUMBER OF OUTPUTS SWITCHING

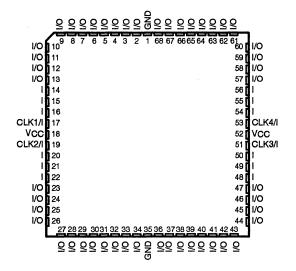

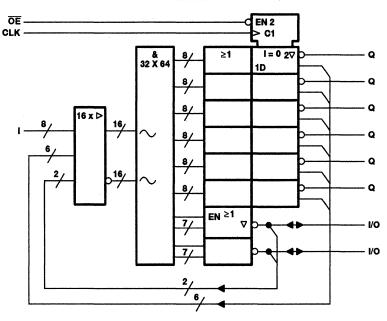

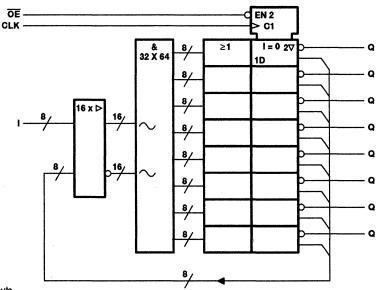

# EP630 SERIES HIGH-PERFORMANCE 16-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES001B - D3357, OCTOBER 1989 - REVISED MARCH 1992

- Programmable Replacement for Conventional TTL and 74HC Devices

- Virtually Zero Standby Current

Typ 20 μA

- Low Operating Current:

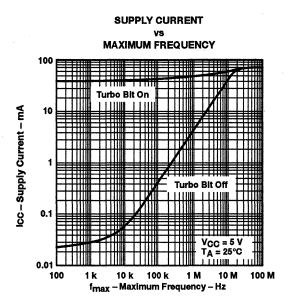

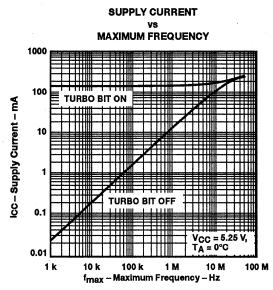

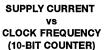

I<sub>CC</sub> max (turbo bit on) . . . 90 mA I<sub>CC</sub> max (turbo bit off) . . . 10 mA

High Performance CMOS Process Allows:

Maximum t<sub>pd</sub>: - 15C . . . 15 ns - 20C . . . 20ns - 25I . . . 25 ns

- Asynchronous Clocking of All Registers or Banked Register Operation From 2 Synchronous Clocks

- Sixteen Macrocells With Configurable I/O Architecture Allowing for up to 20 Inputs and 16 Outputs

- User-Programmable Output Logic Macrocells Provide Flexibility in Output Types with:

Selectable for Registered or Combinational Operation Output Polarity Control Independently User Programmable Feedback Path

- Programmable Design Security Bit Prevents Copying of Logic Stored in Device

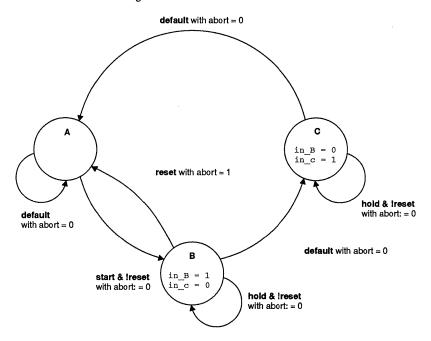

- Third-Party Advanced Software Support Featuring Schematic Capture, Interactive Netlist, Boolean Equations, and State Machine Design Entry

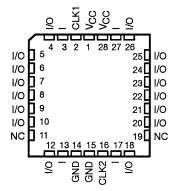

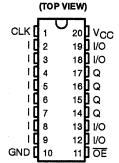

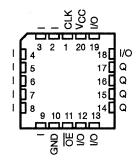

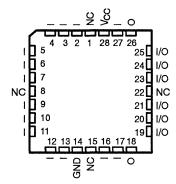

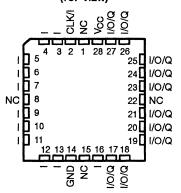

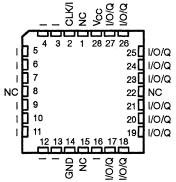

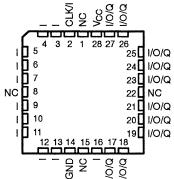

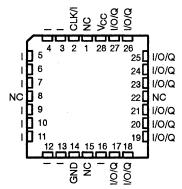

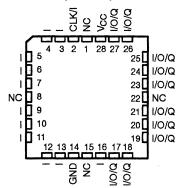

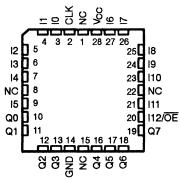

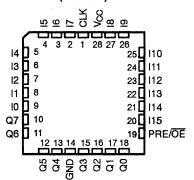

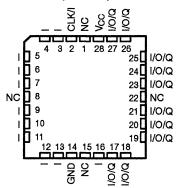

NC-No internal connection

#### **AVAILABLE OPTIONS**

|                | PACKA          | GE TYPE        |

|----------------|----------------|----------------|

| T <sub>A</sub> | PLASTIC        | PLASTIC        |

| RANGE          | DUAL-IN-LINE   | CHIP CARRIER   |

|                | PACKAGE (PDIP) | PACKAGE (PLCC) |

| 0°C to 70°C    | EP630-15CNT    | EP630-15CFN    |

| 0-0 10 70-0    | EP630-20CNT    | EP630-20CFN    |

| -40°C to 85°C  | EP630-25INT    | EP630-25IFN    |

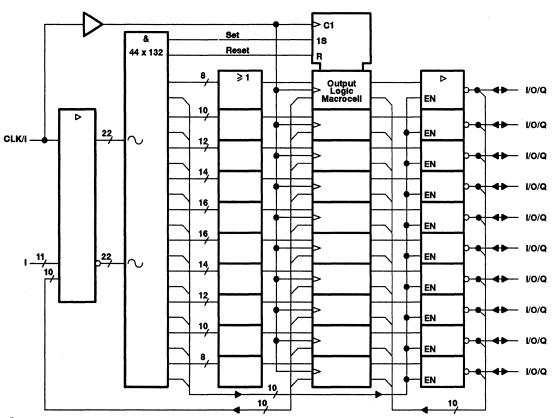

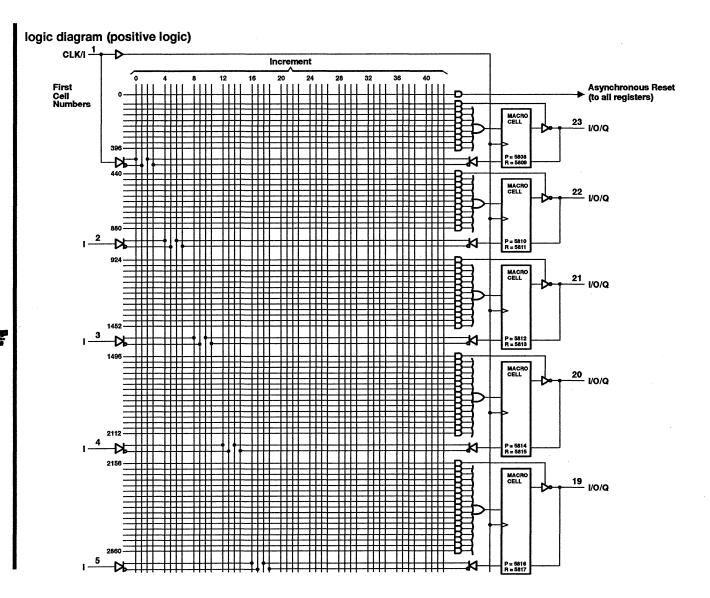

# **EP630 SERIES HIGH-PERFORMANCE 16-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES**

#### description

#### general

The Texas Instruments EP630 is capable of implementing over 600 equivalent gates of SSI and MSI logic functions all in plastic and ceramic space-saving 24-pin, 300-mil dual-in-line (DIP) packages and 28-pin chip-carrier packages. It uses the familiar sum-of-products logic, providing a programmable AND with a fixed OR structure. The device accommodates both combinational and sequential (registered) logic functions with up to 20 inputs and 16 outputs. The EP630 has a user programmable output logic macrocell that allows each output to be configured as a combinational or registered output and feedback signals active high or active low.

A unique feature of the EP630 is the ability to program D, T, SR, or JK flip-flop operation individually for each output without sacrificing product terms. In addition, each register can be individually clocked from any of the input or feedback paths available in the AND array. These features allow a variety of logic functions to be simultaneously implemented.

The CMOS EPROM technology reduces the power consumption to less than 55% of equivalent bipolar devices without sacrificing speed performance. Erasable EPROM bits allow for enhanced factory testing.

Programming the EP630 is made easy by the availability of extensive third-party support for design entry, design processing and device programming.

The EP630-15C and EP630-20C devices are characterized for operation from 0°C to 70°C. The EP630-25I is characterized for operation from -40°C to 85°C.

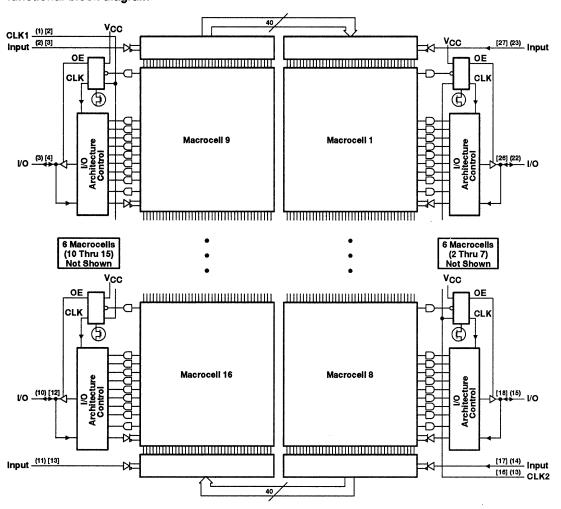

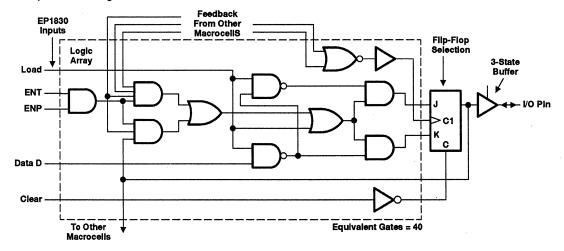

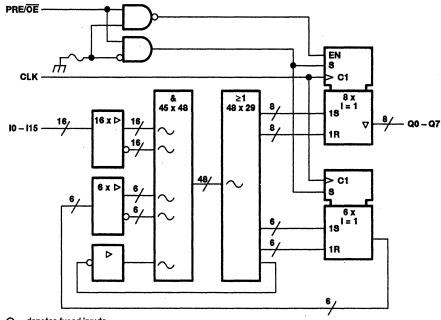

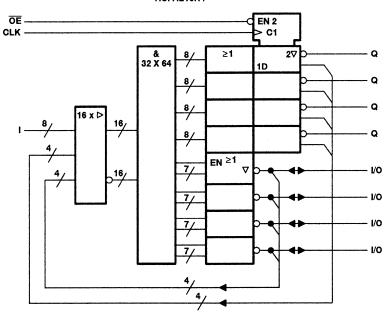

#### functional

The EP630 uses a CMOS EPROM technology to implement logic designs in a programmable AND logic array. The device contains a revolutionary programmable I/O architecture that provides advanced functional capability for user programmable logic.

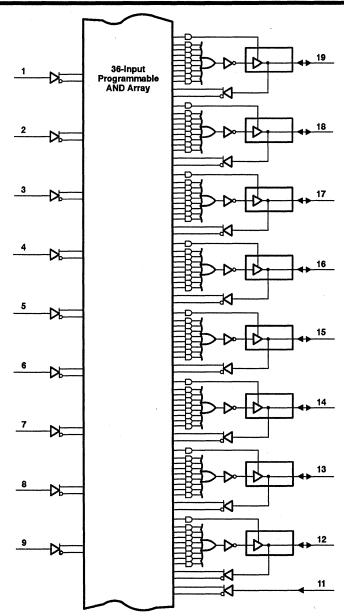

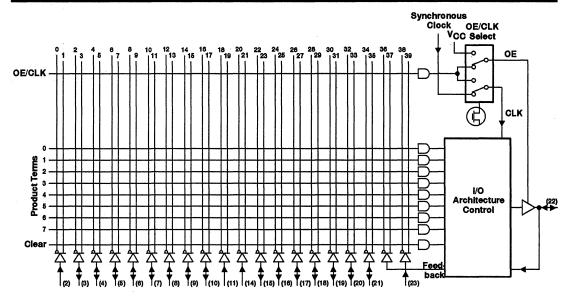

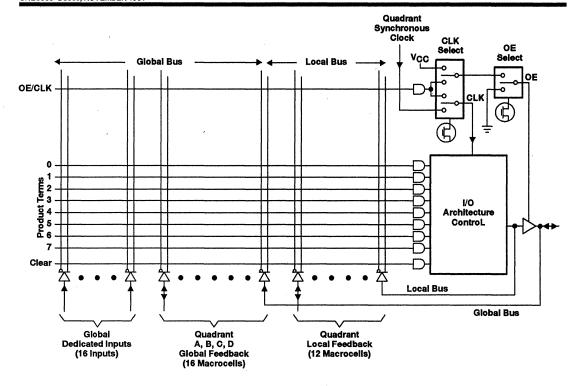

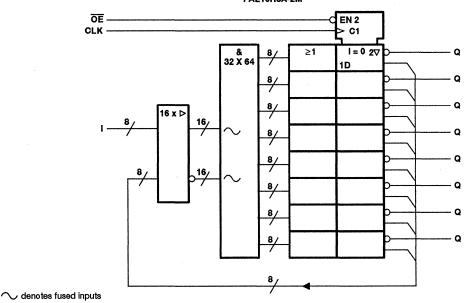

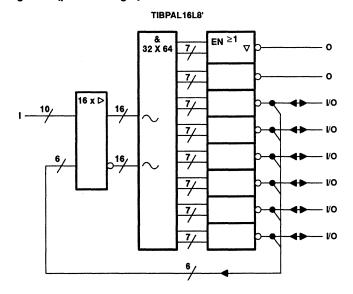

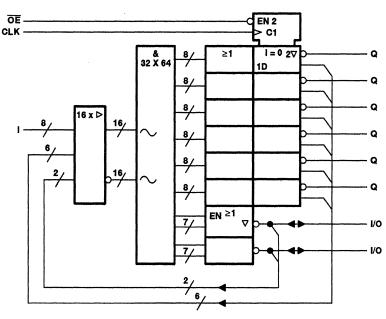

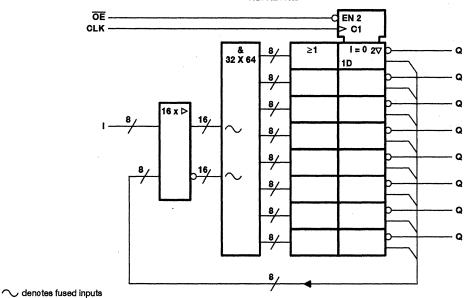

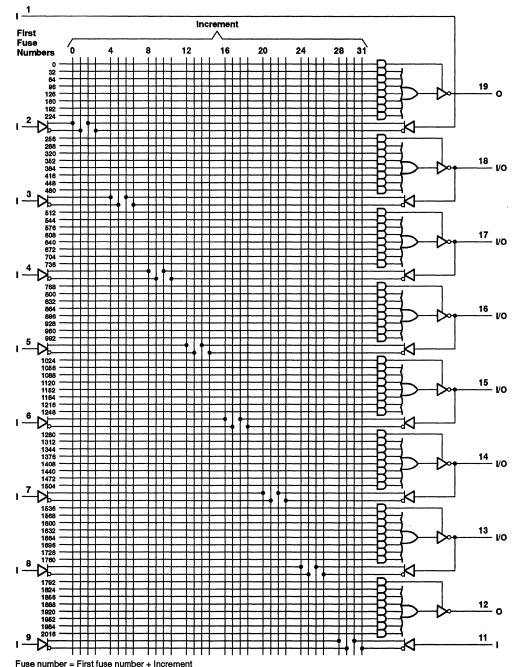

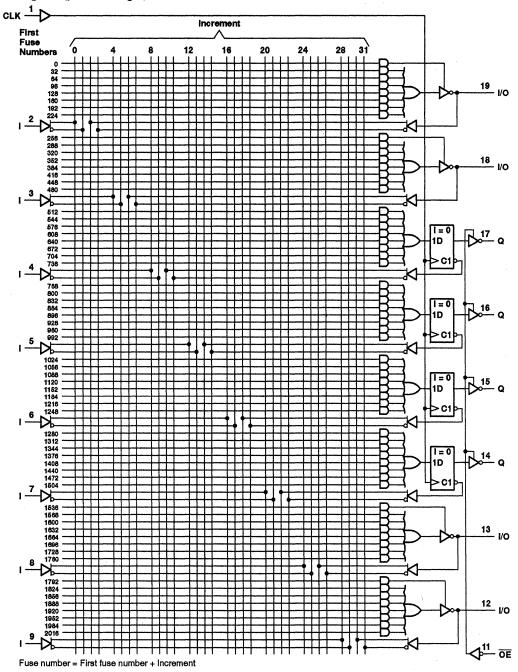

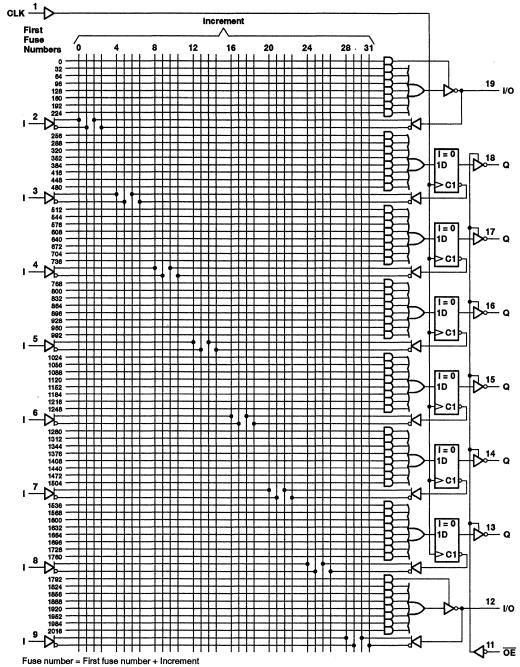

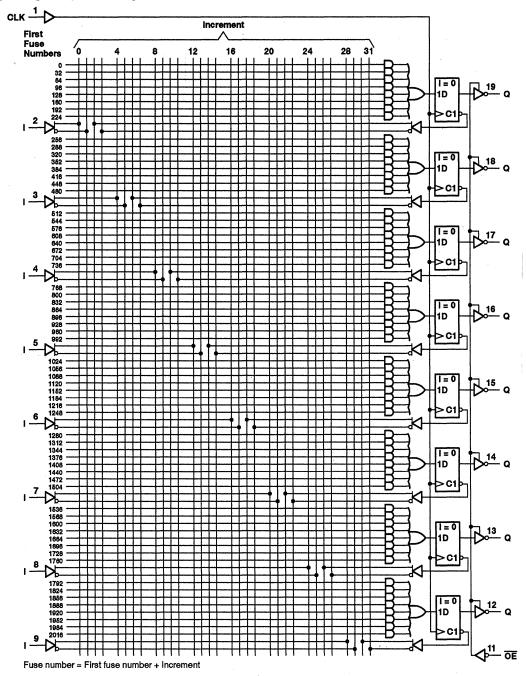

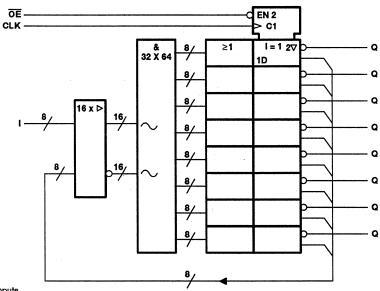

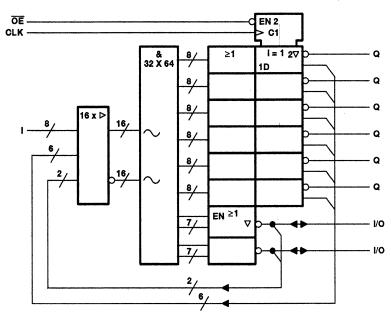

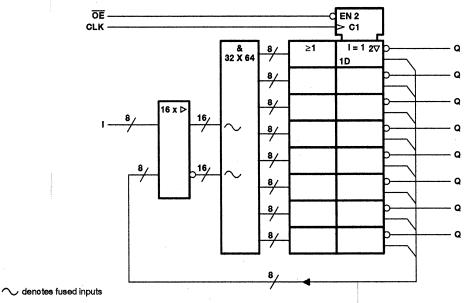

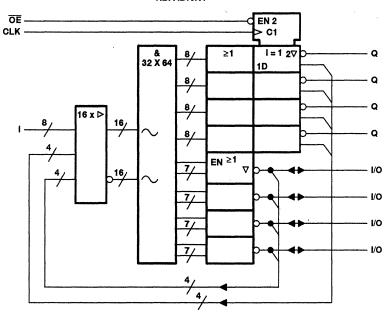

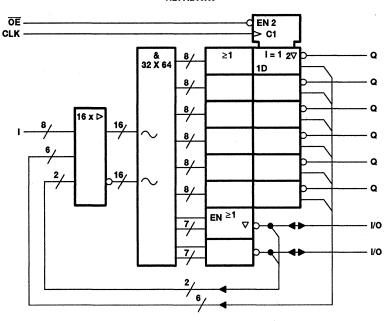

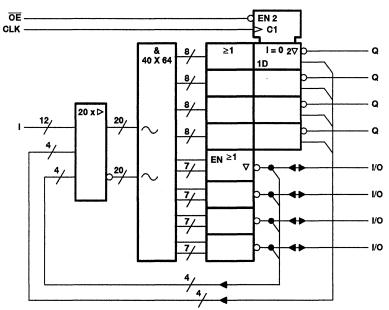

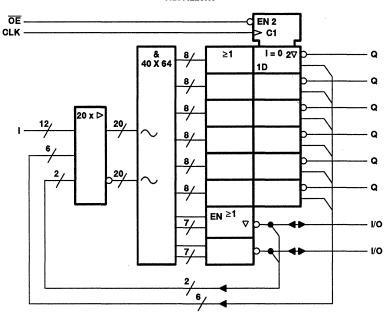

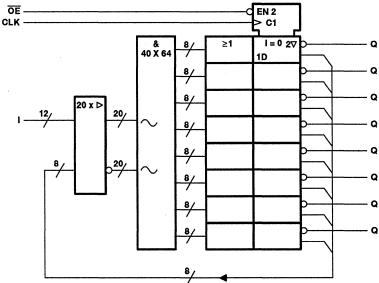

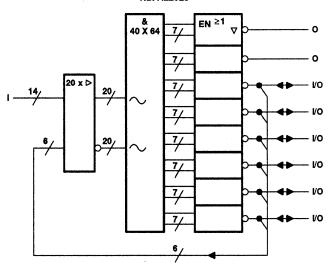

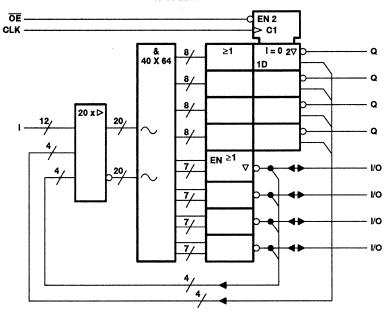

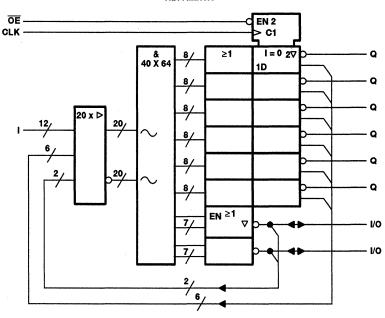

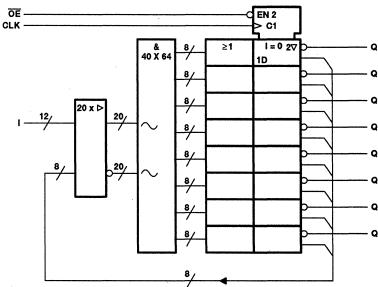

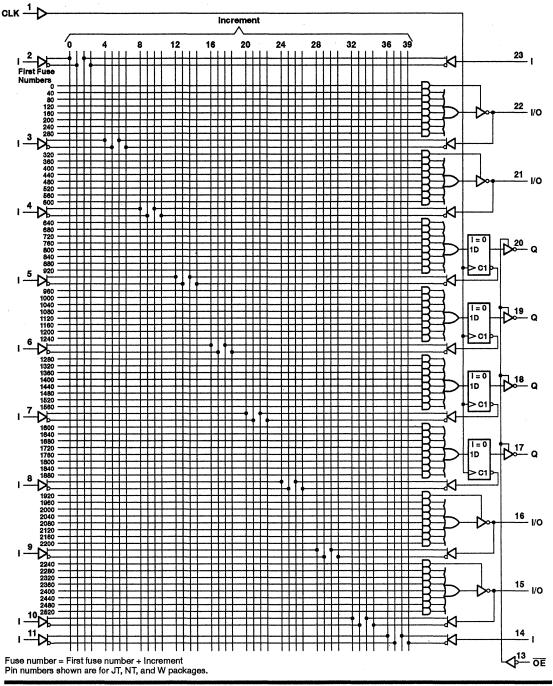

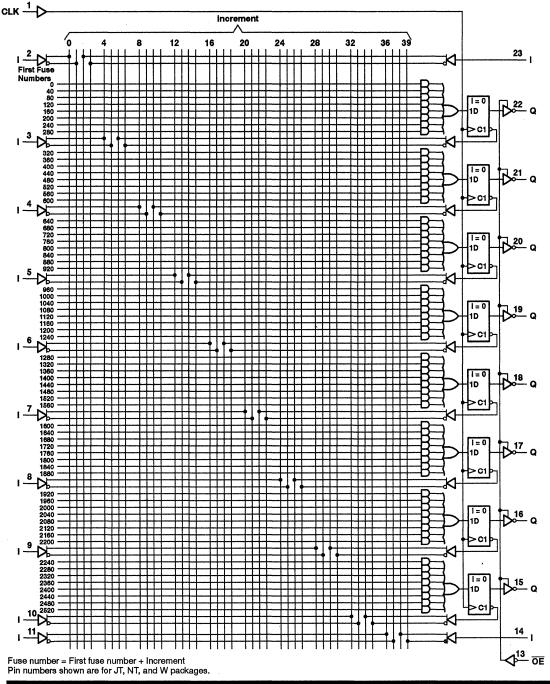

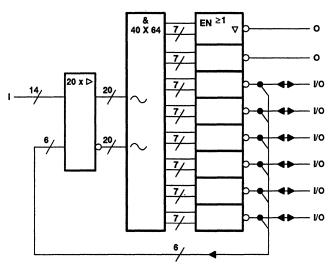

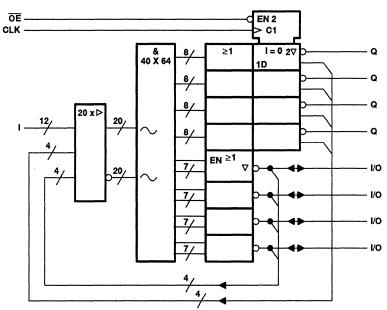

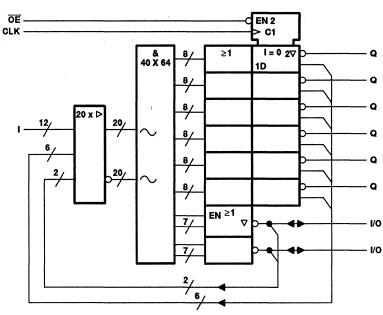

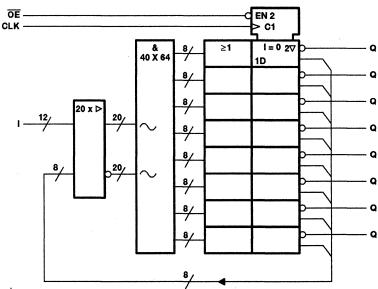

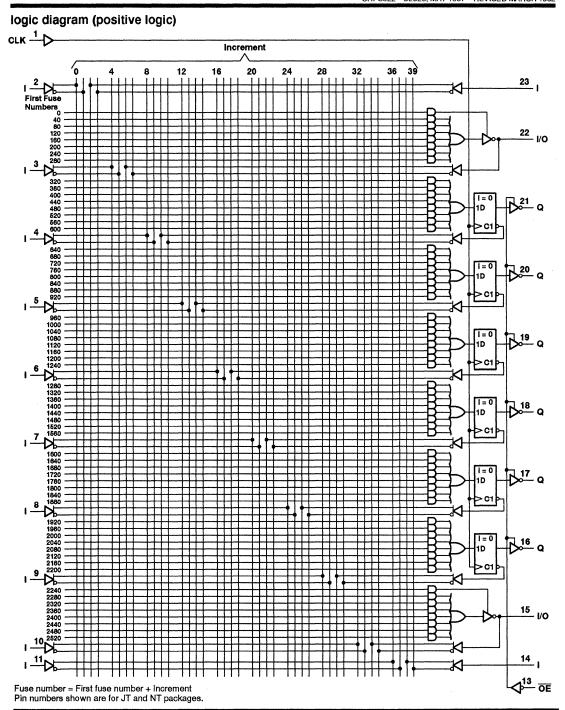

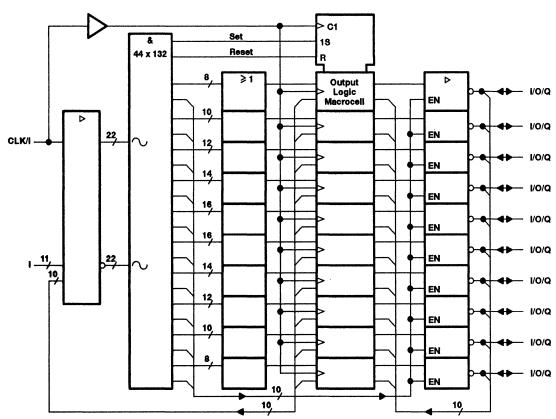

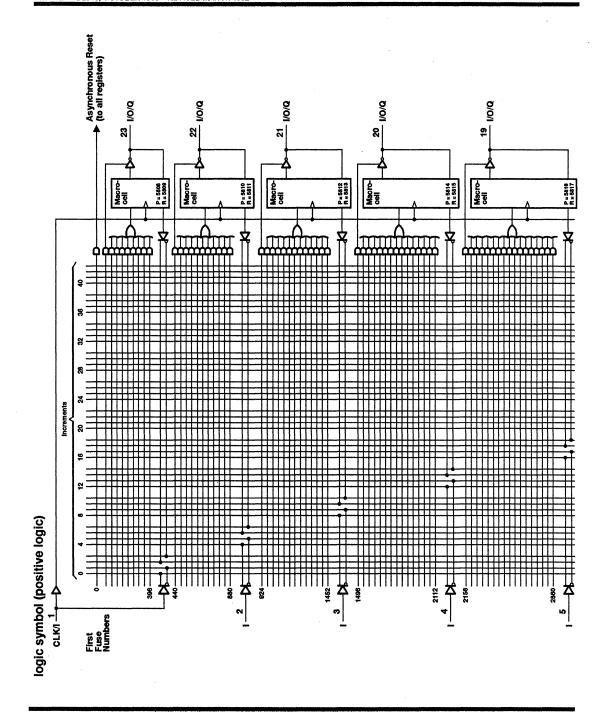

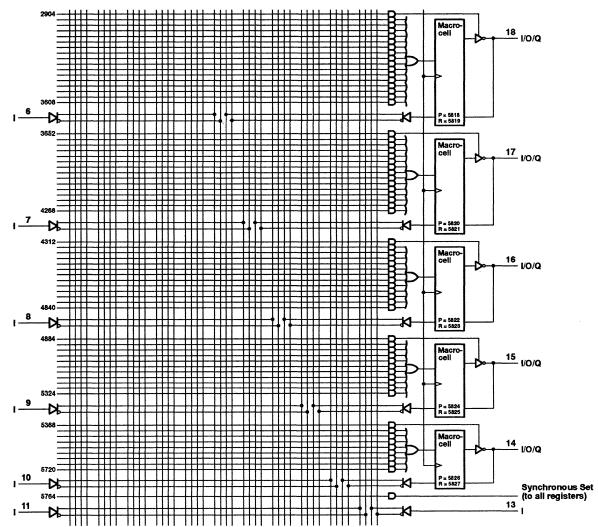

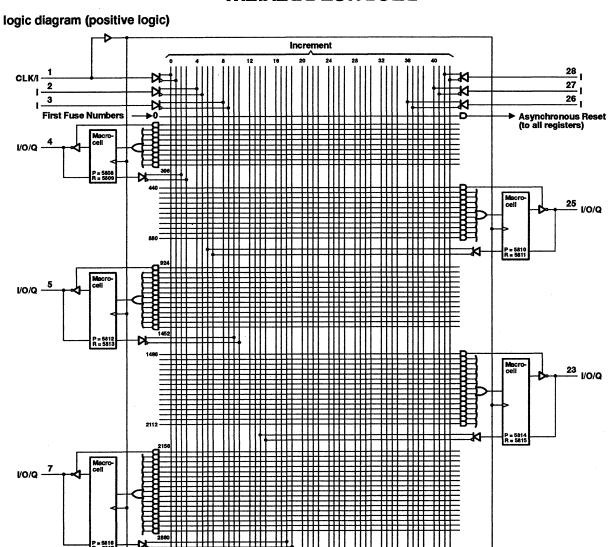

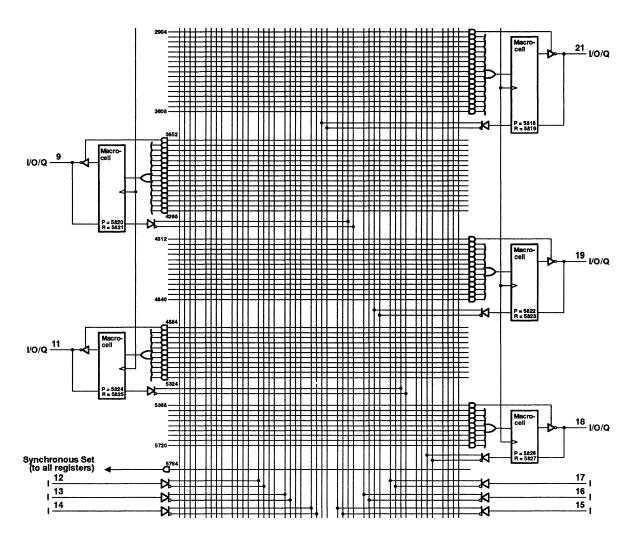

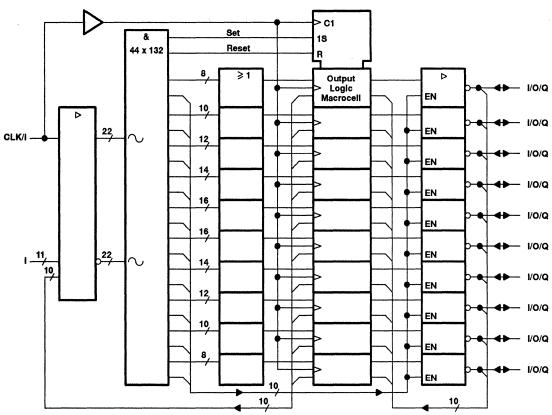

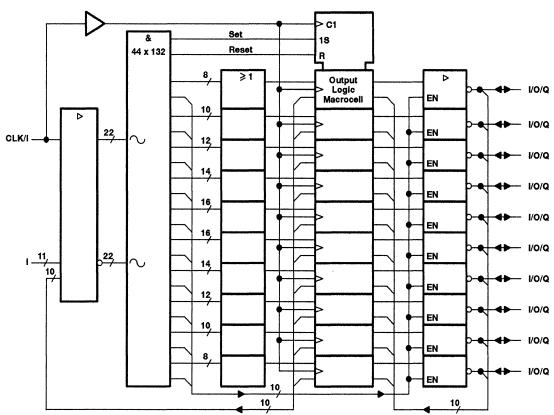

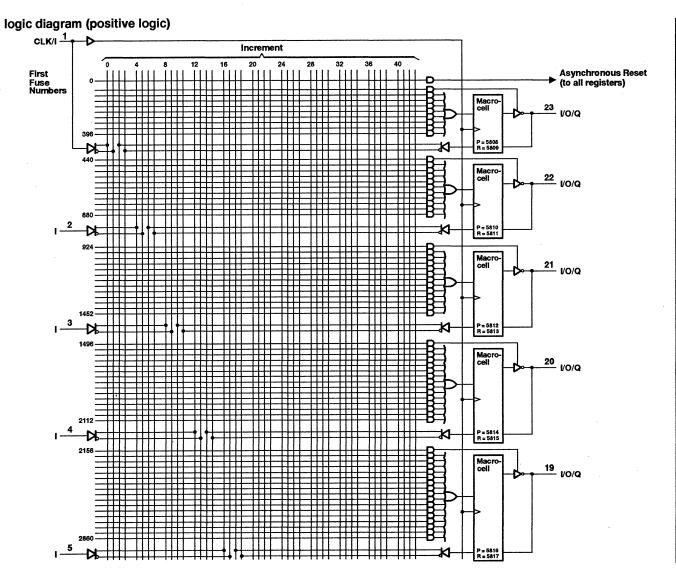

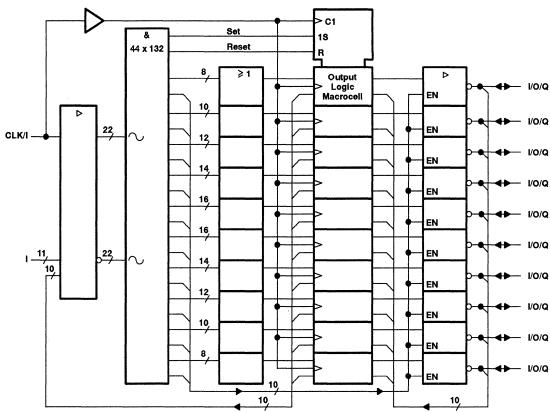

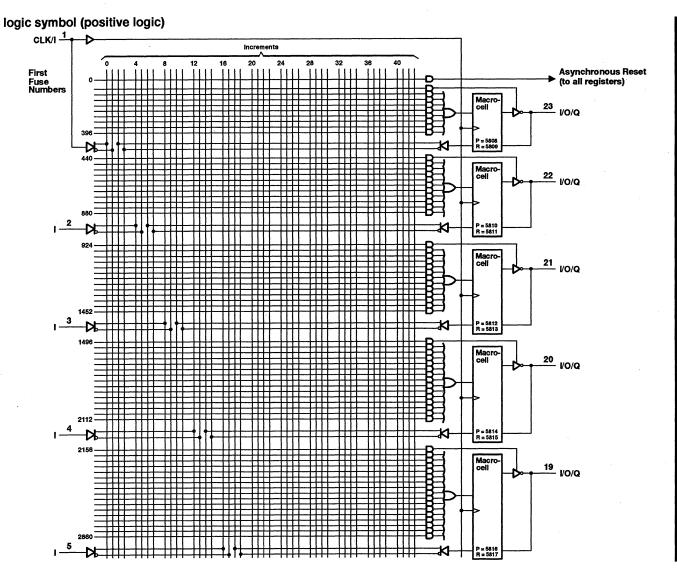

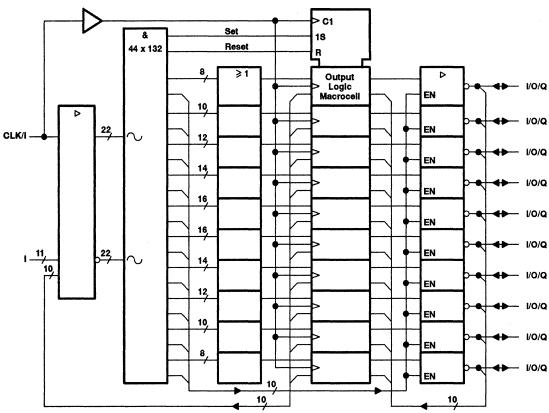

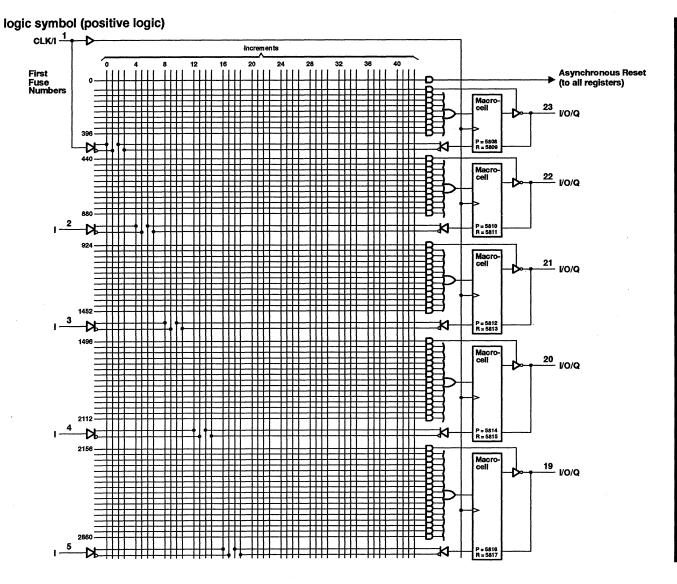

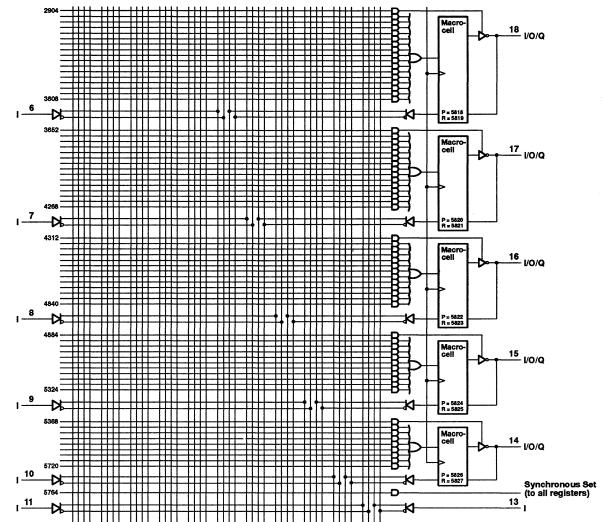

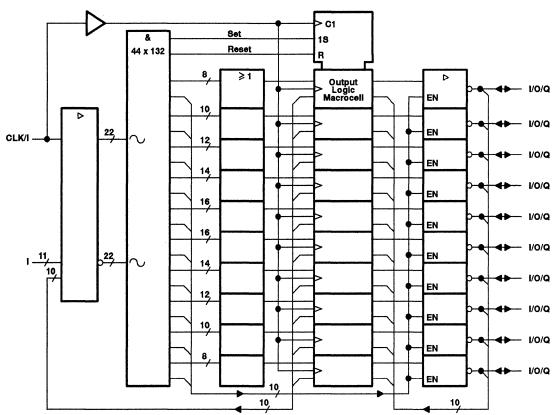

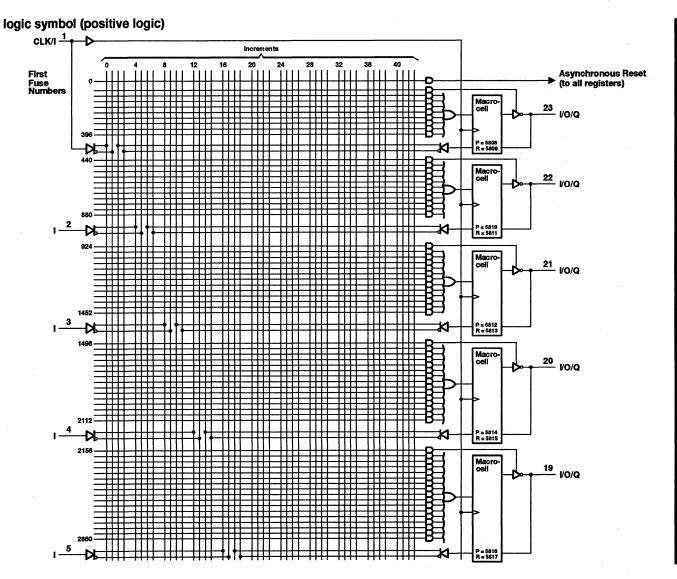

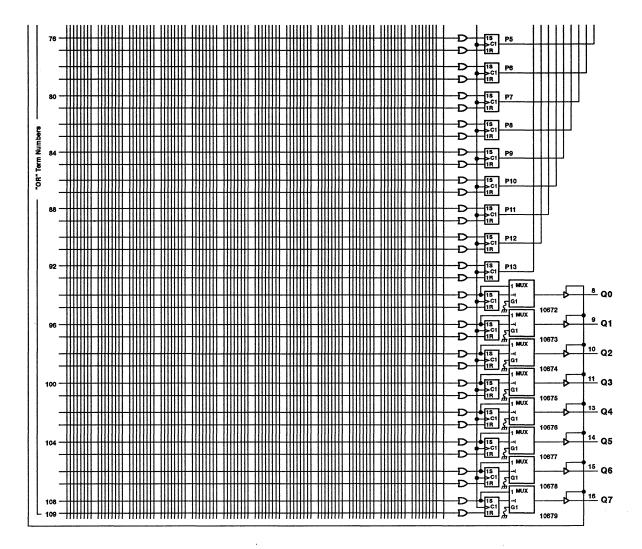

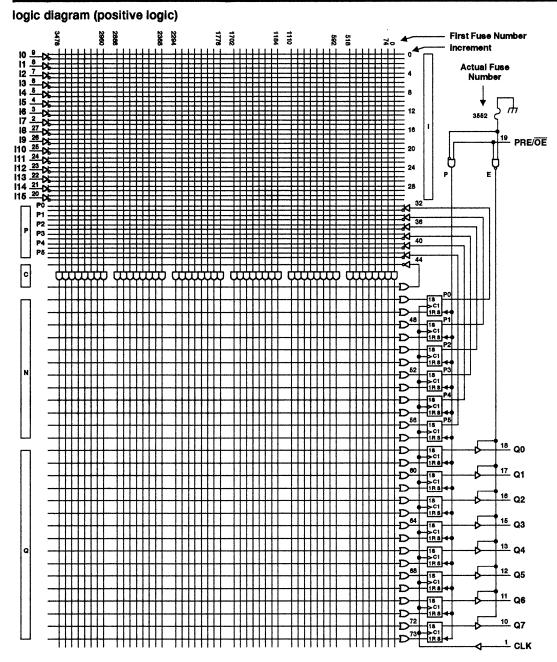

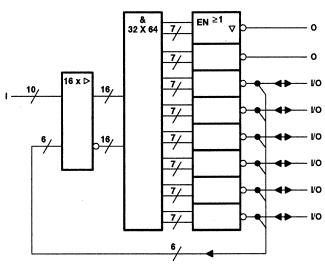

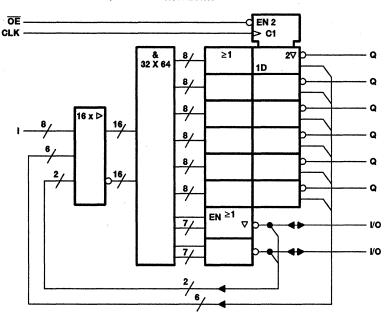

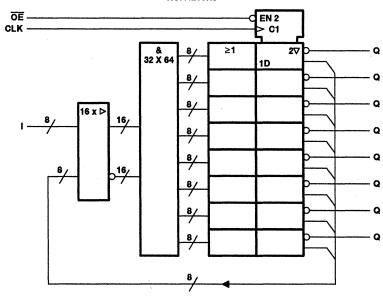

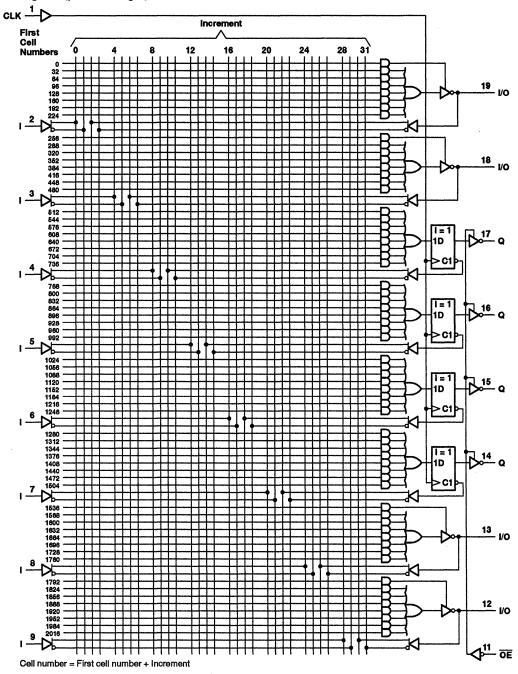

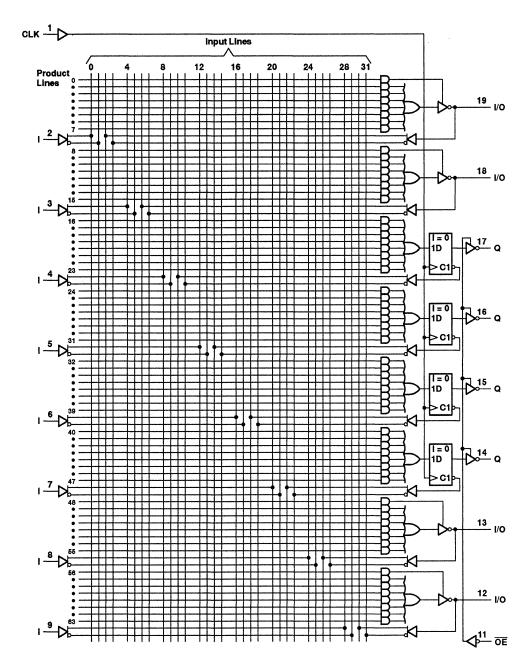

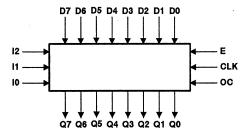

Externally, the EP630 provides 4 dedicated data inputs and 16 I/O pins, which may be configured for input, output, or bidirectional operation. Figure 1 shows the EP630 basic logic array macrocell. The internal architecture is organized with familiar sum-of-products (AND-OR) structure. Inputs to the programmable AND array come from true and complement signals from the 4 dedicated data inputs and the 16 I/O architecture-control blocks. The 40-input AND array encompasses 160 product terms, which are distributed among 16 available macrocells. Each EP630 product term represents a 40-input AND gate.

Each macrocell contains 10 product terms, 8 of which are dedicated for logic implementation. One product term is used for clear control of the macrocell internal register. The remaining product term is used for output enable/asynchronous clock implementation.

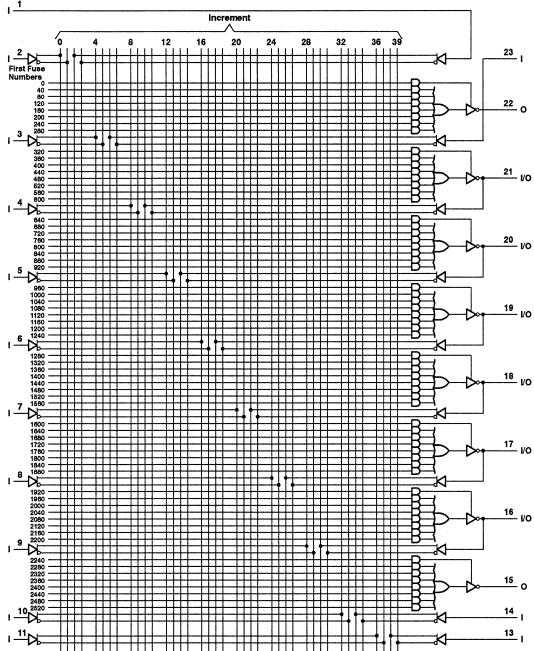

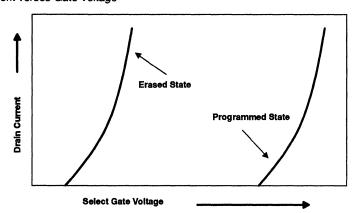

There is an EPROM connection at the intersection point of each input signal and each product term. In the erased state, all connections are made. This means both the true and complement forms of all inputs are connected to each product term. Connections are opened during the programming process. Therefore, any product term may be connected to the true or complement form of any array input signal.

When both the true and complement forms of any signal are left intact, a logical false state results on the output of the AND gate. If both the true and complement connections are open, then a logical "don't care" applies for that input. If all inputs for the product term are programmed open, then a logical true state results on the output of the AND gate.

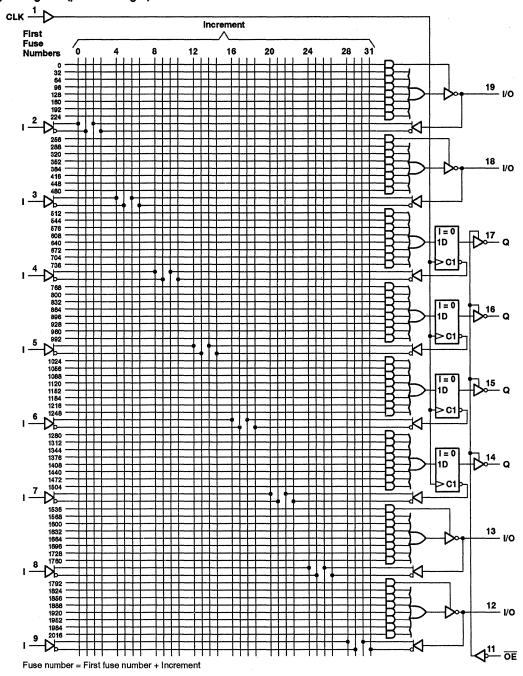

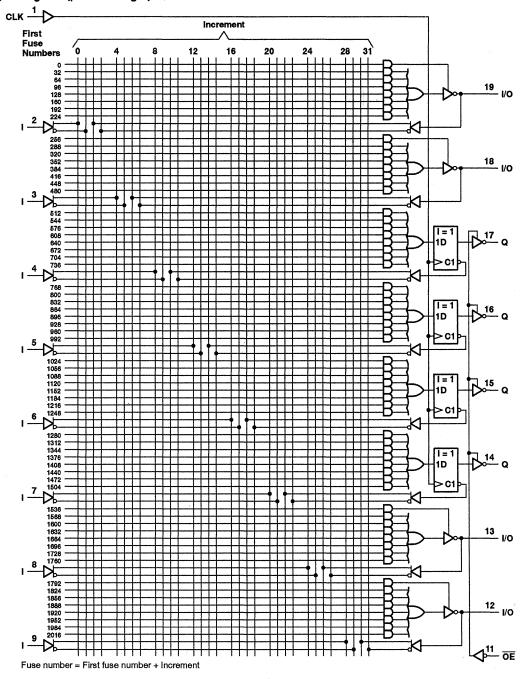

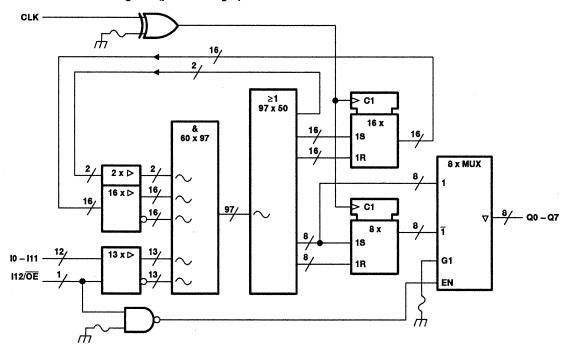

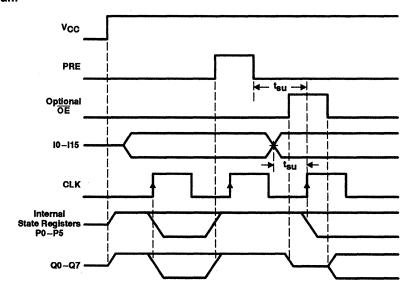

Two dedicated clock inputs provide synchronous clock signals to the EP630 internal registers. Each of the clock signals controls a bank of 8 registers, CLK1 controls registers associated with macrocells 9-16, and CLK2 controls registers associated with macrocells 1-8. The EP630 advanced I/O architecture allows the number of synchronous registers to be user defined, from one to sixteen. Both dedicated clock inputs are positive-edge-triggered.

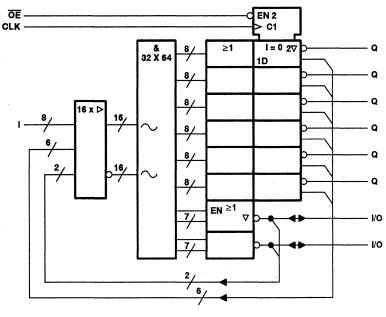

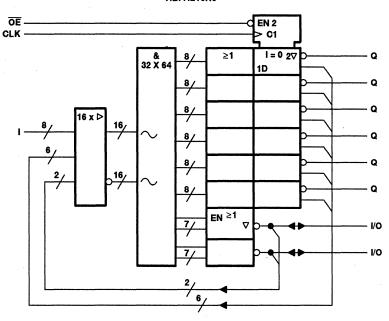

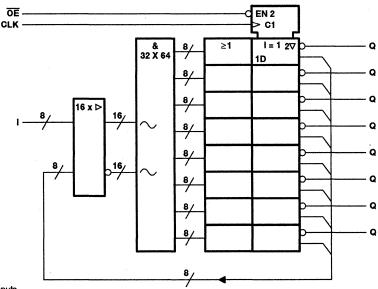

#### functional block diagram

Pin numbers in ( ) are for DIP packages; pin numbers in [ ] are for the chip-carrier package.

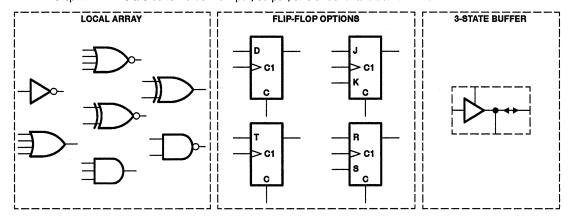

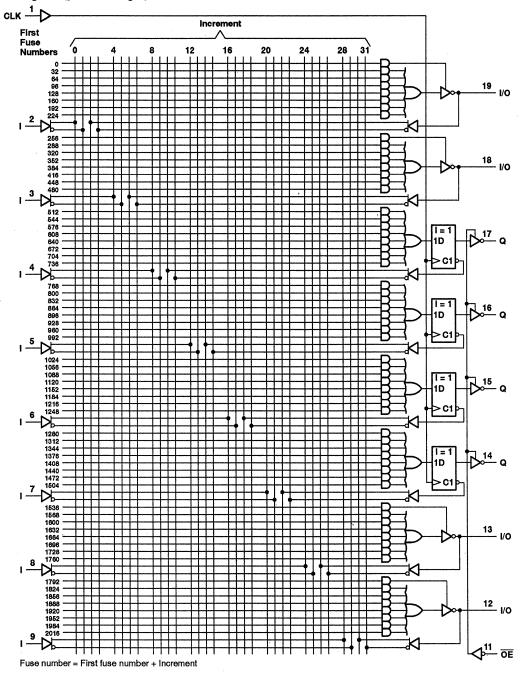

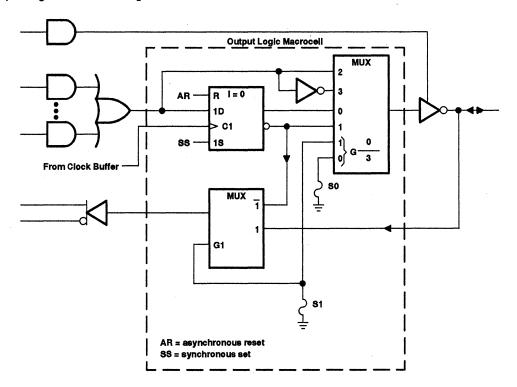

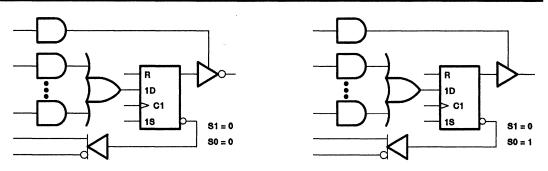

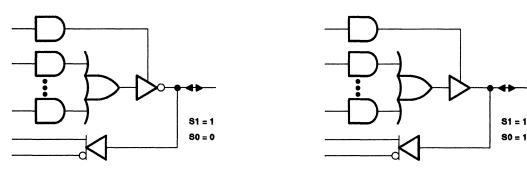

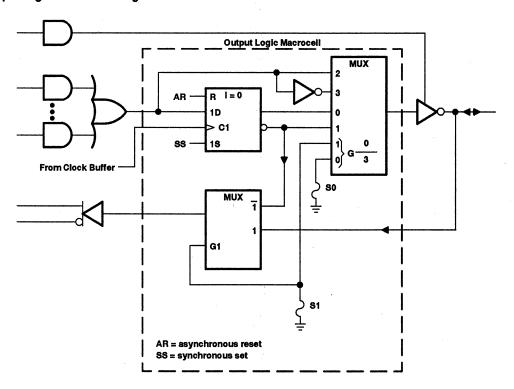

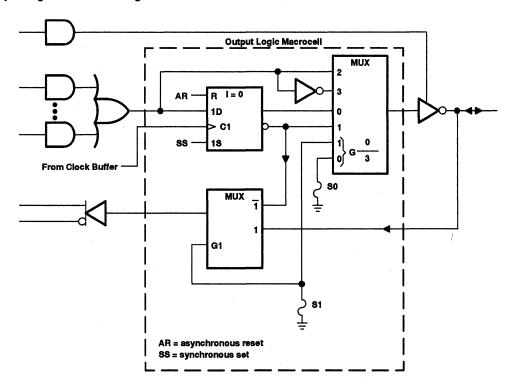

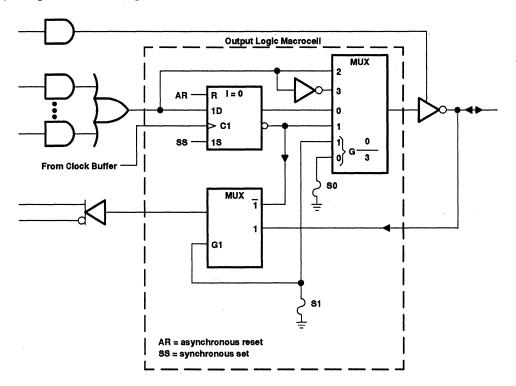

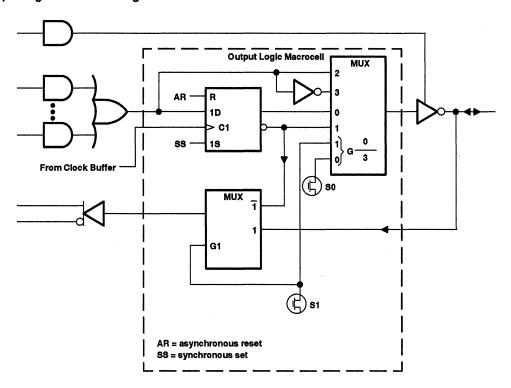

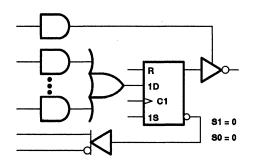

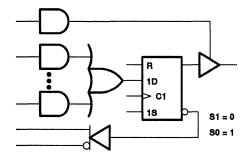

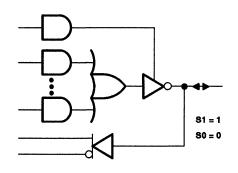

#### I/O architecture

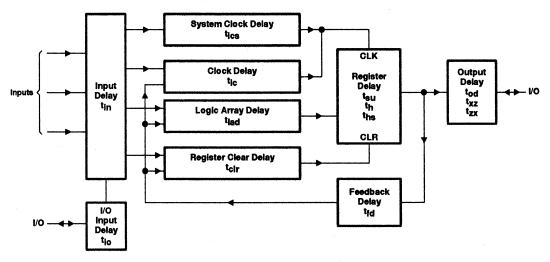

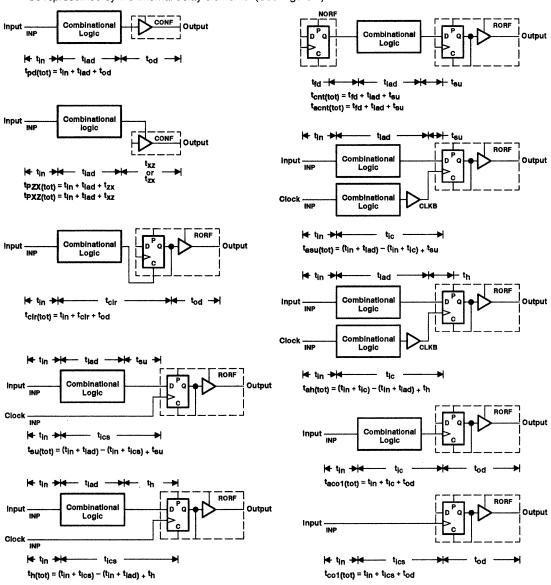

The EP630 input/output architecture provides each macrocell with over 50 possible I/O configurations. Each I/O can be configured for combinational or registered output, with programmable output polarity. Four different types of registers (D, T, JK, and SR) can be implemented into every I/O without any additional logic requirements. I/O feedback selection can also be programmed for registered or input (pin) feedback. Another benefit of the EP630 I/O architecture is its ability to individually clock each internal register from asynchronous clock signals.

Pin numbers are for the NT package.

Figure 1. Logic Array Macrocell (Macrocell 1 Illustrated)

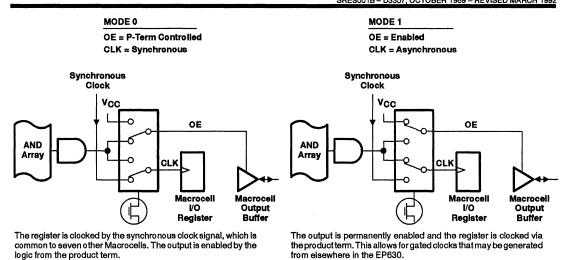

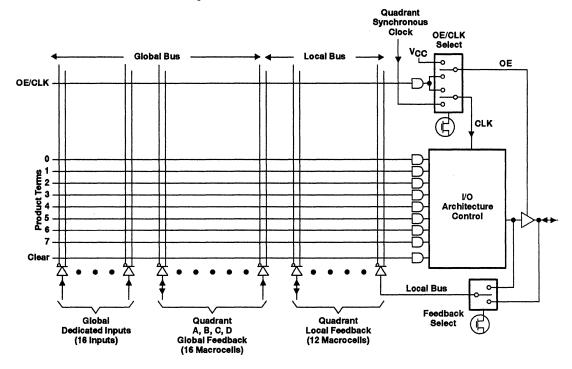

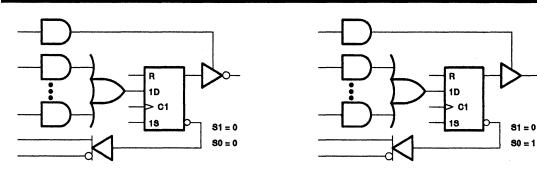

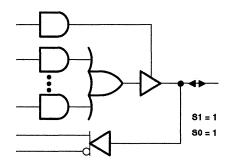

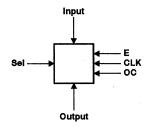

#### **OE/CLK** selection

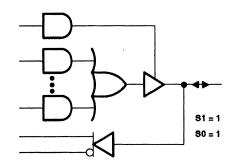

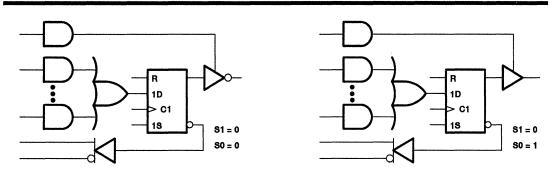

Figure 2 shows the two modes of operation that are provided by the OE/CLK select multiplexer. The operation of this multiplexer is controlled by a single EPROM bit and may be individually configured for each EP630 I/O pin. In Mode 0, the 3-state output buffer is controlled by a single product term. If the output of the AND gate is true, the output buffer is enabled. If the output of the AND gate is false, the output buffer is in the high-impedance state. In this mode, the macrocell flip-flop may be clocked by its respective synchronous clock input. After erasure, the OE/CLK select multiplexer is configured in Mode 0.

In Mode 1, the output-enable buffer is always enabled. The macrocell flip-flop may now be triggered from an asynchronous clock signal generated by the OE/CLK multiplexable product term. This mode allows individual clocking of flip-flops from any available signal in the AND array. Because both true and complement signals reside in the AND array, the flip-flop may be configured for positive- or negative-edge-triggered operation. With the clock now controlled by a product term, gated clock structures are also possible.

Figure 2. OE/CLK Select Multiplexer

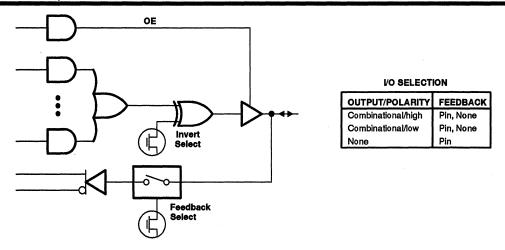

#### output/feedback selection

logic from the product term.

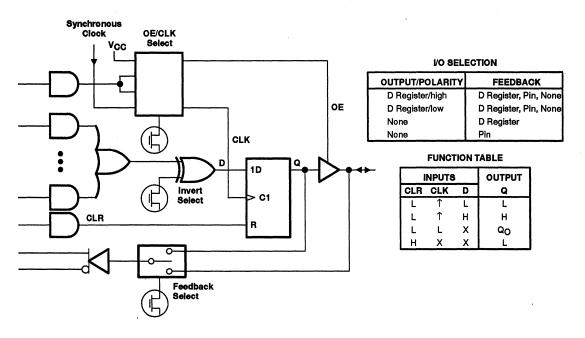

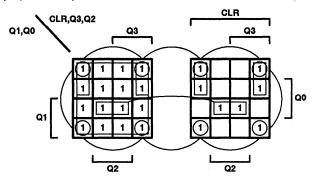

Figure 3 shows the EP630 basic output configurations. Along with combinational output, four register types are available. Each macrocell I/O may be independently configured. All registers have individual asynchronous clear control from a dedicated product term. When the product term is asserted, the macrocell register will immediately be loaded with a zero independent of the clock. On power-up, The EP630 performs the clear function automatically.

When the D or T register is selected, eight product terms are ORed together and made available to the register input. The invert select EPROM bit determines output polarity. The feedback-select multiplexer enables register, I/O (pin), or no feedback to the AND array.

If the JK or SR registers are selected, the eight product terms are shared between two OR gates. The invert select EPROM bit configures output polarity. The feedback-select multiplexer enables registered or no feedback to the AND array.

Any I/O pin may be configured as a dedicated input by selecting no output and pin feedback. No output is obtained by disabling the macrocell output buffer. In the erased state, each I/O is configured for combinational active-low output with input (pin) feedback.

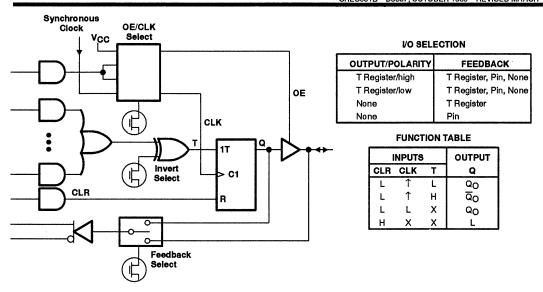

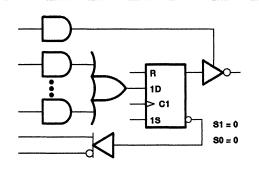

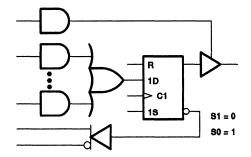

## (a) COMBINATIONAL

(b) D-TYPE FLIP-FLOP

Figure 3. I/O Configurations

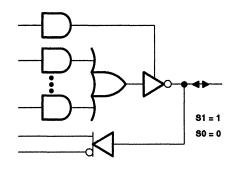

(c) TOGGLE FLIP-FLOP

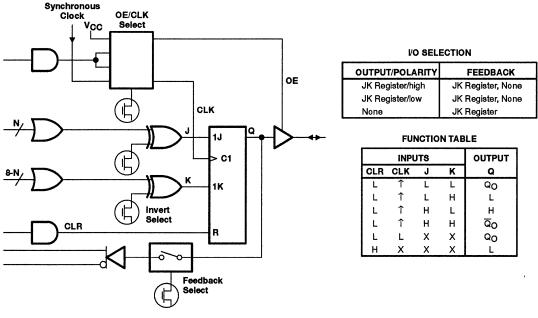

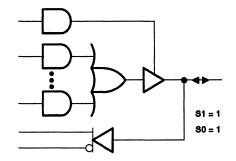

(d) J-K FLIP-FLOP

Figure 3. I/O Configurations (Continued)

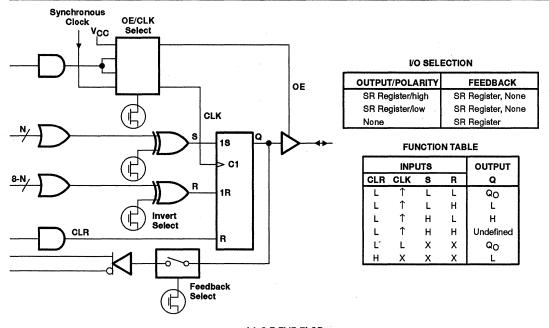

(e) S-R FLIP-FLOP

Figure 3. I/O Configurations (Continued)

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                          | –0.3 V to 7 V     |

|-----------------------------------------------------------------------------|-------------------|

| Instantaneous supply voltage range, V <sub>CC</sub> (t ≤ 20 ns)             | –2 V to 7 V       |

| Programming supply voltage range, V <sub>pp</sub>                           | 0.3 V to 14 V     |

| Instantaneous programming supply voltage range, V <sub>pp</sub> (t ≤ 20 ns) |                   |

| Input voltage range, V <sub>1</sub>                                         |                   |

| Instantaneous input voltage range, V <sub>I</sub> (t ≤ 20 ns)               | –2 V to 7 V       |

| V <sub>CC</sub> or GND current range                                        | –175 mA to 175 mA |

| Operating free-air temperature range, T <sub>A</sub>                        | 65°C to 135°C     |

| Storage temperature range                                                   | 65°C to 150°C     |

NOTE 1: All voltage values are with respect to GND terminal.

# EP630-15C, EP630-20C HIGH-PERFORMANCE 16-MACROCELL ONE-TIME PROGRAMMABLE LOGIC DEVICES SRES001B - D3357, OCTOBER 1989 - REVISED MARCH 1992

## recommended operating conditions

|                 |                                      |                          |  | MIN  | MAX                  | UNIT |  |

|-----------------|--------------------------------------|--------------------------|--|------|----------------------|------|--|

| Vcc             | Supply voltage                       |                          |  | 4.75 | 5.25                 | ٧    |  |

| VI              | Input voltage                        |                          |  | 0    | Vcc                  | ٧    |  |

| VIH             | High-level input voltage             | High-level input voltage |  |      | V <sub>CC</sub> +0.3 | V    |  |

| ٧ <sub>IL</sub> | Low-level input voltage (see Note 2) |                          |  | -0.3 | 0.8                  | ٧    |  |

| Vο              | Output voltage                       |                          |  | 0    | Vcc                  | ٧    |  |

|                 | Rise time                            | CLK input                |  |      | 20                   |      |  |

| τ <sub>r</sub>  | Rise ume                             | Other inputs             |  |      | 40                   | ns   |  |

| •               | Fall time                            | CLK input                |  |      | 20                   |      |  |

| tf              | raii ume                             | Other inputs             |  |      | 40                   | ns   |  |

| TA              | Operating free-air temperature       |                          |  | 0    | 70                   | ့င   |  |

NOTE 2: The algebraic convention, in which the more negative value is designated minimum, is used in this data sheet for logic voltage levels

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| [                | PARAMETER                 |          | TEST CON                       | DITIIONS                                | MIN  | MAX    | UNIT |

|------------------|---------------------------|----------|--------------------------------|-----------------------------------------|------|--------|------|

|                  | 111-1-1                   | TTL      | V <sub>CC</sub> = 4.75 V,      | IOH = -4 mA                             | 2.4  |        | V    |

| VOH              | High-level output voltage | CMOS     | V <sub>CC</sub> = 4.75 V,      | IOH = -2 mA                             | 3.84 |        | •    |

| VOL              | Low-level output voltage  |          | V <sub>CC</sub> = 4.75 V,      | I <sub>OL</sub> = 4 mA                  |      | · 0.45 | ٧    |

| 11               | Input current             |          | V <sub>CC</sub> = 5.25 V,      | V <sub>I</sub> = V <sub>CC</sub> or GND |      | ±10    | μА   |

| loz              | Off-state output current  |          | V <sub>CC</sub> = 5.25 V,      | Vo = Vcc or GND                         |      | ±10    | μА   |

|                  |                           | Standby  | V <sub>CC</sub> = 5.25 V,      | See Note 3                              |      | 150    | μΑ   |

| Icc              | Supply current            | Nonturbo | $V_I = V_{CC}$ or GND,         | See Note 4                              |      | 10     | mA   |

|                  |                           | Turbo    | No load                        | See Note 4                              |      | 90     | ША   |

| Ci               | Input capacitance         |          | V <sub>j</sub> = 0, f = 1 MHz, | T <sub>A</sub> = 25°C                   |      | 10     | рF   |

| Co               | Output capacitance        |          | $V_0 = 0, f = 1 \text{ MHz},$  | T <sub>A</sub> = 25°C                   |      | 12     | pF   |

| C <sub>clk</sub> | Clock capacitance         |          | V <sub>I</sub> = 0, f = 1 MHz, | T <sub>A</sub> = 25°C                   |      | 20     | pF   |

NOTES: 3. When in nonturbo, the device automatically goes into the standby mode approximately 100 ns after the last transition.

<sup>4.</sup> These parameters are measured with the device programmed as a 16-bit counter and f = 1 MHz.

# EP630-15C, EP630-20C **HIGH-PERFORMANCE 16-MACROCELL** ONE-TIME PROGRAMMABLE LOGIC DEVICES

SRES001B - D3357, OCTOBER 1989 - REVISED MARCH 1992

switching characteristics over recommended ranges of supply voltage and operating free air temperature (unless otherwise noted)

#### combinational mode, turbo bit on

|                  |                                         |                                  | TEST CONDITIONS |     | EP630-15C |     | EP630-20C |    |

|------------------|-----------------------------------------|----------------------------------|-----------------|-----|-----------|-----|-----------|----|

|                  | PARAMETER <sup>†</sup>                  | TEST CO                          | MIN             | MAX | MIN       | MAX | UNIT      |    |

| <sup>t</sup> pd1 | Input to nonregistered output delay     |                                  |                 | 15  |           | 20  | ns        |    |

| <sup>t</sup> pd2 | I/O input to nonregistered output delay | C <sub>L</sub> = 35 pF           |                 |     | 17        |     | 22        | ns |

| tPZX             | Output enable time                      | C <sub>L</sub> = 35 pF           | 0 11.5          |     | 15        |     | 20        | ns |

| tpxz             | Output disable time                     | C <sub>L</sub> = 5 pF See Note 5 |                 |     | 15        |     | 20        | ns |

| tio              | I/O input buffer delay                  |                                  |                 |     | 2         |     | 2         | ns |

#### combinational mode, turbo bit off

|                  | PARAMETER <sup>†</sup>                  | TEOT 001               | TEST CONDITIONS |  | EP630-15C |     | EP630-20C |      |

|------------------|-----------------------------------------|------------------------|-----------------|--|-----------|-----|-----------|------|

|                  | PARAMETER                               | IESI CO                |                 |  | MAX       | MIN | MAX       | UNIT |

| <sup>t</sup> pd1 | Input to nonregistered output delay     | C <sub>L</sub> = 35 pF |                 |  | 35        |     | 40        | ns   |

| tpd2             | I/O input to nonregistered output delay |                        |                 |  | 37        |     | 42        | ns   |

| tPZX             | Output enable time                      | C <sub>L</sub> = 35 pF | See Note 5      |  | 35        |     | 40        | ns   |

| tpxz             | Output disable time                     | C <sub>L</sub> = 5 pF  | See Mote 5      |  | 35        |     | 40        | ns   |

| tio              | I/O input buffer delay                  |                        |                 |  | 2         |     | 2         | ns   |

#### synchronous clock mode, mode 0

|                  | PARAMETER <sup>†</sup>         |                    |                        | EP630 | EP630-15C |      | EP630-20C |      |

|------------------|--------------------------------|--------------------|------------------------|-------|-----------|------|-----------|------|

|                  | PARAMETER                      | <u>Į į</u>         | TEST CONDITIONS        | MIN   | MAX       | MIN  | MAX       | UNIT |

|                  |                                | No feedback        |                        | 83.3  |           | 62.5 |           |      |

| fmax             | Maximum frequency <sup>‡</sup> | Internal feedback  |                        | 83.3  |           | 62.5 |           | MHz  |

|                  |                                | External feedback§ |                        | 50    |           | 41.6 |           |      |

| t <sub>co1</sub> | co1 Clock to output delay time |                    |                        |       | 11        |      | 13        | ทร   |

|                  | Minimum clock period (         | register           | See Note 6             |       | 12        |      | 16        | ns   |

| t <sub>cnt</sub> | feedback to register ou        | tput)              | 266 14016 0            |       | 12        |      | 10        | 115  |

| + .              | Asynchronous output            | Turbo bit on       | C <sub>I</sub> = 35 pF |       | 15        |      | 20        | ns   |

| <sup>t</sup> clr | clear time                     | Turbo bit off      | OL - 35 bi             |       | 35        |      | 40        |      |

<sup>†</sup> Letter symbols for switching characteristics and timing requirements in this data sheet have been chosen for compatibility with those used in other documentation previously prepared by another supplier for similar products. Any similarity to symbols used on other TI data sheets or to those shown in glossaries in TI data books is coincidental. The meanings may not be the same.

$$f_{max}$$

with external feedback =  $\frac{1}{t_{su} + t_{co1}}$

$_{S}^{f}_{max}$  with internal feedback is programmed as a 16-bit counter. S Use  $t_{SU}$  and  $t_{OO1}$  for a device programmed with the turbo bit on.

NOTES: 5. This is for an output voltage change of 500 mV.

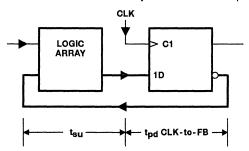

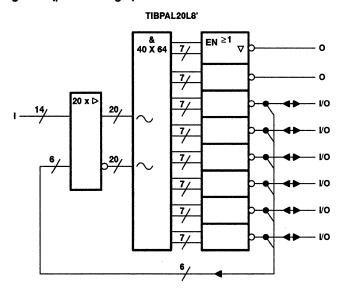

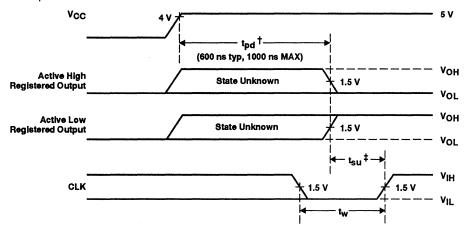

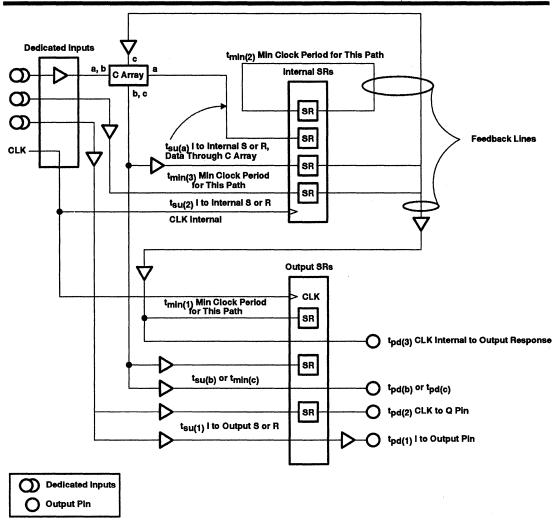

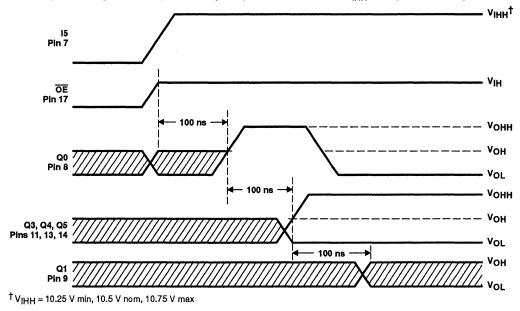

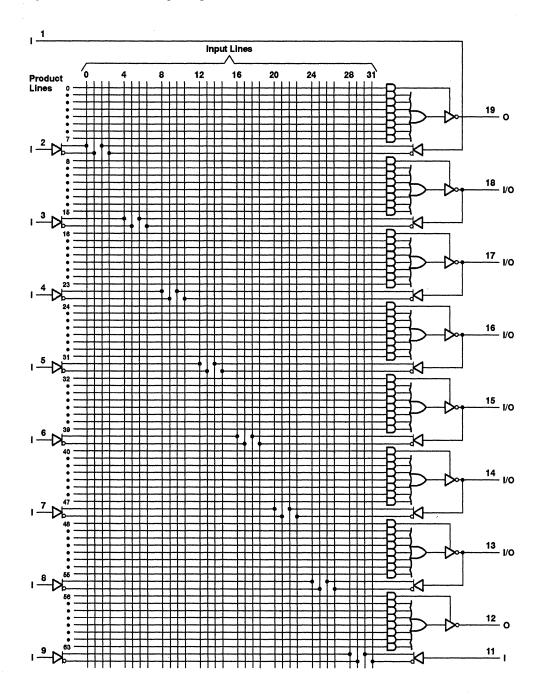

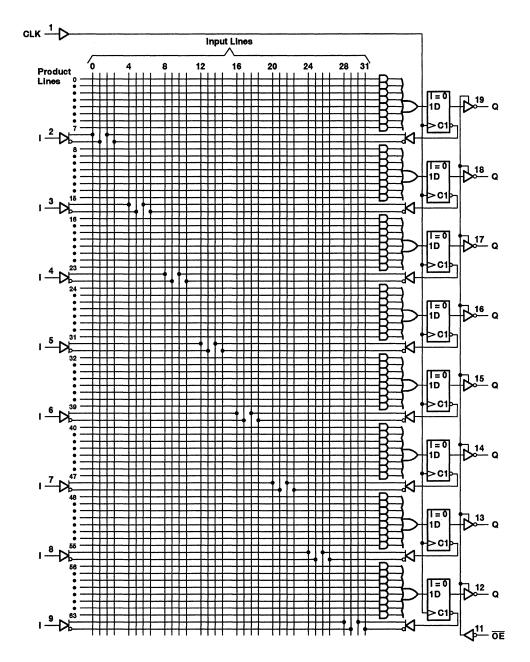

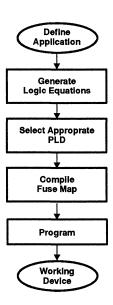

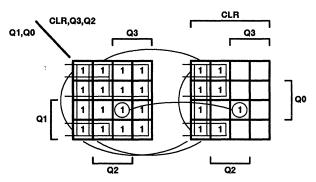

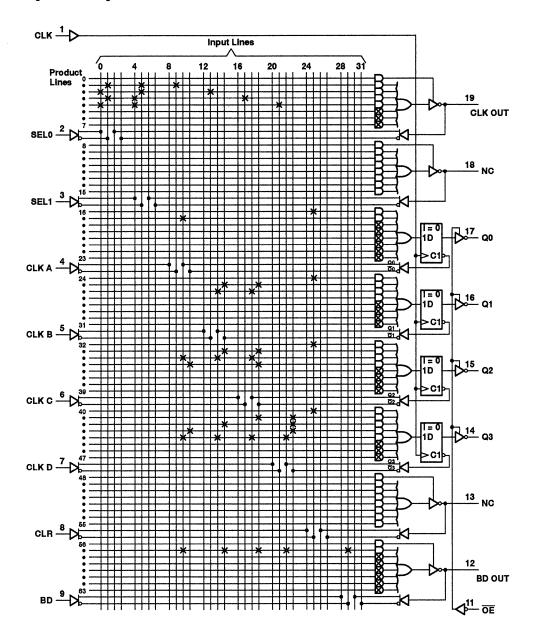

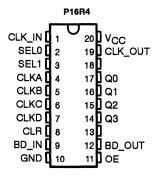

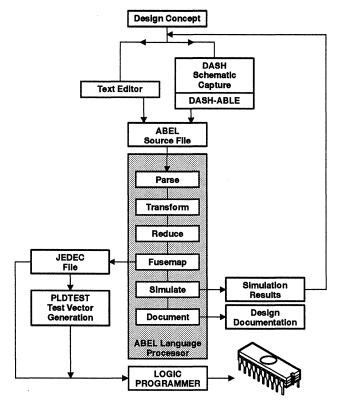

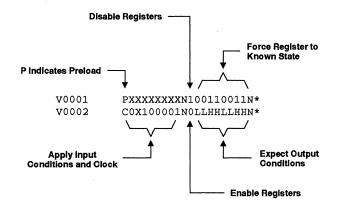

6. These parameters are measured with device programmed as a 16-bit counter.