# Low-Voltage Logic LV, LVC, LVT, LVTZ, ALVC, CBT, and GTL Families

Data Book

## Data Book

**Low-Voltage Logic**

| General Information                      | 1  |

|------------------------------------------|----|

| LVT Octals                               | 2  |

| LVTZ Octals: Power-Up, 3-State           | 3  |

| LVT Widebus™                             | 4  |

| LVT JTAG/IEEE 1149.1                     | 5  |

| GTL Transceivers and Backplane Drivers   | 6  |

| LVC MSI and Octals                       | 7  |

| LVC Widebus™                             | 8  |

| ALVC Widebus™                            | 9  |

| LV MSI and Octals                        | 10 |

| CBT Bus Switches and 5-V/3-V Translators | 11 |

| Application Notes                        | 12 |

| Characterization Information             | 13 |

| Mechanical Data                          | 14 |

## Low-Voltage Logic Data Book

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

#### INTRODUCTION

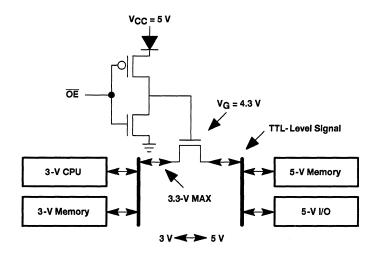

The 3.3-V era has arrived! The combination of continuous advancement in semiconductor wafer fabrication technologies and the proliferation of battery-powered computing devices has changed the system design methodologies of the past, and indeed our entire industry. This new era will bring an entirely new set of possibilities for computing and hand-held instruments. Products that will run faster, consume less power, and use fewer total system components than ever before. Products that will be smaller and lighter, yet maintain interface compatibility with existing industry standard bus architectures. Products that will in turn bring on the next era in the computer industry.

Welcome to the 1994 Texas Instruments Low-Voltage Logic Data Book. A single family of 3.3-V logic products could not possibly cover the diverse needs of all of the end equipment segments. Products ranging from hand-held point-of-sale terminals, notebook and laptop personal computers, low-power environmentally conscious desktop computers and peripherals, and high-performance RISC and CISC workstation platforms will all share the need for low-voltage technology, but will each have radically different price, performance, and feature requirements for the logic they will employ. As a response to these diverse needs, Texas Instruments has developed four independent logic families:

Low-Voltage HCMOS (LV) Low-Voltage CMOS (LVC) Low-Voltage Technology (LVT) Advanced Low-Voltage CMOS (ALVC)

These products span four generations of CMOS and BiCMOS process technologies and years of fine-pitch packaging and innovative circuit developments to deliver a set of products for each of these end-equipment segments. In addition to popular octal and Widebus™ bus-interface circuits, two of the families also include SSI and MSI logic functions to help streamline design and facilitate time to market. Voltage translators are also provided to bridge the gap between the 5-V and 3.3-V worlds as well as the CBT family of ultra high-speed bus switches which can be easily adapted to these mixed 3.3-V/5-V environments. Designers of high-speed backplane applications will have great interest in the GTL family of transceivers.

Some of the information in this data book is in product preview form. For more information on these products including availability dates, pricing, and final timing specifications, please contact your local Texas Instruments field sales representative, authorized distributor, or call our Advanced Logic hotline at (214) 997-5202.

We hope you will agree that Texas Instruments has developed the most complete line of low-voltage logic products in the industry. We also hope that these products will meet your system and design needs.

#### PRODUCT STAGE STATEMENTS

Product stage statements are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

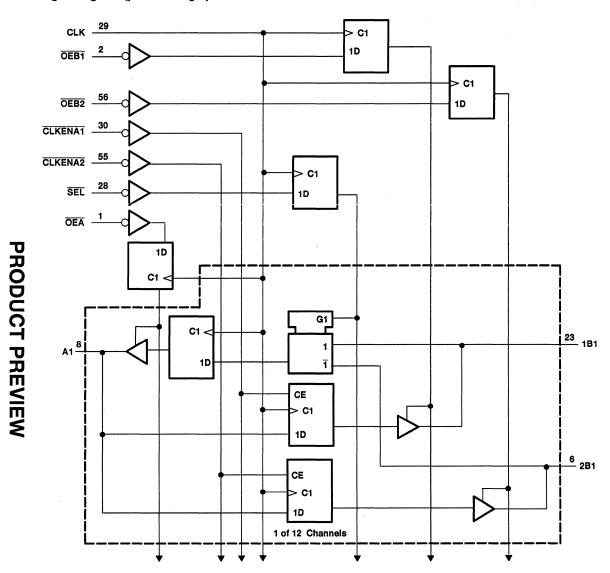

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

| General Information                      | 1  |

|------------------------------------------|----|

| LVT Octals                               | 2  |

| LVTZ Octals: Power-Up, 3-State           | 3  |

| LVT Widebus™                             | 4  |

| LVT JTAG/IEEE 1149.1                     | 5  |

| GTL Transceivers and Backplane Drivers   | 6  |

| LVC MSI and Octals                       | 7  |

| LVC Widebus™                             | 8  |

| ALVC Widebus™                            | 9  |

| LV MSI and Octals                        | 10 |

| CBT Bus Switches and 5-V/3-V Translators | 11 |

| Application Notes                        | 12 |

| Characterization Information             | 13 |

| Mechanical Data                          | 14 |

## **Contents**

|                                          | Page   |

|------------------------------------------|--------|

| Alphanumeric Index                       | . 1–3  |

| Glossary                                 | . 1–5  |

| Explanation of Function Tables           | . 1–8  |

| D Flip-Flop and Latch Signal Conventions | . 1–10 |

| Thermal Information                      | . 1–11 |

| Functional Index                         | . 1–13 |

| Parameter Measurement Information        | . 1–39 |

## **ALPHANUMERIC INDEX**

| DEVICE                           | PAGE     | DEVICE                 | PAGE  |

|----------------------------------|----------|------------------------|-------|

| Advanced Low-Voltage CMOS (ALVC) |          | SN741 V74              |       |

| SN74ALVC16240                    | 9–3      |                        |       |

| SN74ALVC16244                    | 9–7      |                        |       |

| SN74ALVC16245                    | 9–11     |                        |       |

| SN74ALVC16260                    | 9–21     |                        |       |

| SN74ALVC16269                    | 9–27     |                        |       |

| SN74ALVC16270                    | 9–31     |                        |       |

| SN74ALVC16271                    | 9–35     |                        | 10–57 |

| SN74ALVC16272                    | 9–39     |                        |       |

| SN74ALVC16373                    | 9–45     |                        |       |

| SN74ALVC16374                    | 9–49     |                        |       |

| SN74ALVC16500                    | 9–53     |                        |       |

| SN74ALVC16501                    | 9–59     | SN74LV574              |       |

| SN74ALVC16543                    | 9–65     |                        |       |

| SN74ALVC16600                    | 9–71     | Low-Voltage CMOS (LVC) |       |

| SN74ALVC16601                    | 9–75     | •                      | 7–3   |

| SN74ALVC16646                    | 9–85     | SN74LVC02              | 7–5   |

| SN74ALVC16652                    | 9–91     |                        | 7–7   |

| SN74ALVC16721                    | 9–99     |                        |       |

| SN74ALVC16820                    | 9–103    |                        |       |

| SN74ALVC16821                    | 9–107    |                        | 7–15  |

| SN74ALVC16823                    | 9–113    |                        |       |

| SN74ALVC16825                    | 9–119    |                        |       |

| SN74ALVC16827                    | 9–123    |                        |       |

| SN74ALVC16828                    | 9–127    |                        |       |

| SN74ALVC16841                    | 9–131    |                        |       |

| SN74ALVC16843                    | 9–135    |                        |       |

| SN74ALVC16952                    | 9–139    |                        |       |

| SN74ALVC162601                   | 9–79     |                        | 7–37  |

| SN74ALVC164245                   | 9–15     |                        |       |

|                                  |          |                        |       |

| Crossbar Technology (CBT)        |          |                        |       |

| SN74CBT3244                      | 11–3     |                        |       |

| SN74CBT3245                      | 11–7     | SN74LVC158             | 7–57  |

| SN74CBT3383                      | 11–11    | SN74LVC240             | 7–61  |

| SN74CBT3384                      | 11–15    | SN74LVC241             | 7–65  |

| SN74CBT6800                      |          | SN74LVC244             | 7–69  |

| SN74CBT16209                     | 11–23    | SN74LVC245             | 7–73  |

| SN74CBT16212                     | 11–27    | SN74LVC257             | 7–81  |

| SN74CBT16214                     | 11–31    | SN74LVC258             | 7–85  |

|                                  |          | SN74LVC373             |       |

| Gunning Transceiver Logic (GTL)  |          | SN74LVC374             | 7–93  |

| SN74GTL16611                     | <b>I</b> | SN74LVC540             | 7–97  |

| SN74GTL16615                     | )        | SN74LVC541             | 7–101 |

| SN74GTL16921                     | 6–15     |                        | 7–105 |

|                                  |          |                        |       |

| Low-Voltage HCMOS (LV)           |          |                        |       |

| SN74LV00                         |          |                        |       |

| SN74LV02                         |          |                        |       |

| SN74LV04                         |          |                        |       |

| SN74LVU04                        |          |                        |       |

| SN74LV08                         | •        |                        |       |

| SN74LV14                         |          |                        |       |

| SN74LV32                         | 10–27    | SN/4LVU827             | 7–143 |

## **ALPHANUMERIC INDEX**

| DEVICE                            |               | PAGE    | DEVICE        | PAGE               |

|-----------------------------------|---------------|---------|---------------|--------------------|

| LVC (continued)                   |               |         | SN54LVT646    | SN74LVT646 2–69    |

| SN74LVC828                        |               | . 7–147 | SN54LVT652    | SN74LVT652         |

| SN74LVC841                        |               | . 7–151 | SN54LVT2952   | SN74LVT2952 2–85   |

| SN74LVC843                        |               | . 7–155 | SN54LVT16244A | SN74LVT16244A      |

| SN74LVC861                        |               | . 7–159 |               |                    |

| SN74LVC863                        |               | . 7–163 | SN54LVT16245A | SN74LVT16245A 4–21 |

| SN74LVC2952                       |               | . 7–167 | SN54LVT16373  | SN74LVT16373 4–31  |

|                                   |               |         | SN54LVT16374  | SN74LVT16374 4–41  |

|                                   |               |         | SN54LVT16500  | SN74LVT16500 4–51  |

|                                   |               |         | SN54LVT16501  | SN74LVT16501 4–59  |

|                                   |               |         | SN54LVT16543  | SN74LVT16543 4–67  |

|                                   |               |         | SN54LVT16646  | SN74LVT16646 4–73  |

|                                   |               |         | SN54LVT16652  | SN74LVT16652 4–81  |

|                                   |               |         | SN54LVT16835  | SN74LVT16835 4–89  |

|                                   |               |         | SN54LVT16952  | SN74LVT16952 4–95  |

|                                   |               |         | SN54LVT18245  | SN74LVT18245 5–5   |

|                                   |               |         | SN54LVT18502  | SN74LVT18502 5–13  |

|                                   |               |         | SN54LVT18504  | SN74LVT18504 5–27  |

|                                   |               |         | SN54LVT18640  | SN74LVT18640 5–41  |

|                                   |               |         | SN54LVT18646  | SN74LVT18646 5–49  |

| SN74LVC16952.                     |               | . 8–59  |               |                    |

| I aw Valtana Taabaa               | Now (INT INT) |         | SN54LVT18652  | SN74LVT18652 5–63  |

| Low-Voltage Technol<br>SN54LVT125 | SN74LVT125    |         | SN54LVT162240 | SN74LVT162240 4–3  |

| SN54LVT 25<br>SN54LVT 240         | SN74LVT125    |         | SN54LVT162244 | SN74LVT162244 4–15 |

| SN54LVT241                        | SN74LVT240    |         | SN54LVT162245 | SN74LVT162245 4–27 |

| SN54LVT241                        | SN74LVT241    |         | SN54LVT162373 | SN74LVT162373 4–37 |

| SN54LVT244                        | SN74LVT243    |         | SN54LVT162374 | SN74LVT162374 4–47 |

| SN54LVT244A                       | SN74LVT244A   |         | SN54LVT182502 | SN74LVT182502 5–13 |

| SN54LVT245                        | SIN/4LV1244A  | i       | SN54LVT182504 | SN74LVT182504 5–27 |

| SN54LVT245                        | SN74LVT245A   |         | SN54LVT182646 | SN74LVT182646 5-49 |

| SN54LVT273                        | SN74LVT273    |         | SN54LVT182652 | SN74LVT182652 5–63 |

| SN54LVT543                        | SN74LVT543    |         | SN54LVTZ240   | SN74LVTZ240 3–3    |

| SN54LVT573                        | SN74LVT573    |         | SN54LVTZ244   | SN74LVTZ244 3–9    |

| SN54LVT574                        | SN741VT574    |         | SN541 VT7245  | SN741 VT7245 3–15  |

#### INTRODUCTION

These symbols, terms, and definitions are in accordance with those currently agreed upon by the JEDEC Council of the Electronic Industries Association (EIA) for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### operating conditions and characteristics (in sequence by letter symbols)

C<sub>i</sub> Input capacitance

The internal capacitance at an input of the device

Co Output capacitance

The internal capacitance at an output of the device

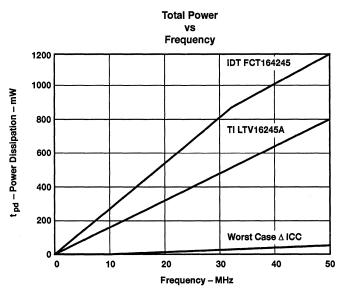

C<sub>pd</sub> Power dissipation capacitance

Used to determine the no-load dynamic power dissipation per logic function (see individual circuit pages):  $P_D = C_{\rm pd} \ V_{\rm CC}^2 \ f + I_{\rm CC} \ V_{\rm CC}$ .

f<sub>max</sub> Maximum clock frequency

The highest rate at which the clock input of a bistable circuit can be driven through its required sequence while maintaining stable transitions of logic level at the output with input conditions established that should cause changes of output logic level in accordance with the specification.

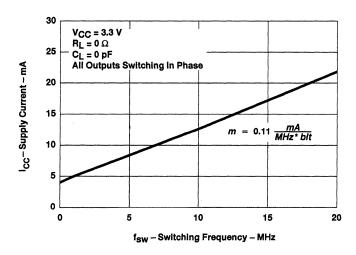

I<sub>CC</sub> Supply current

The current into\* the V<sub>CC</sub> supply terminal of an integrated circuit

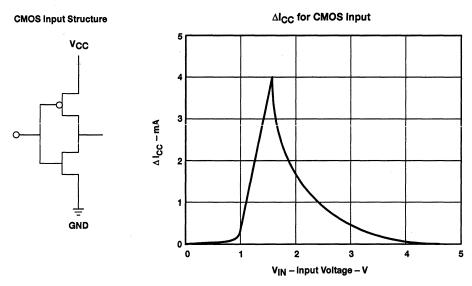

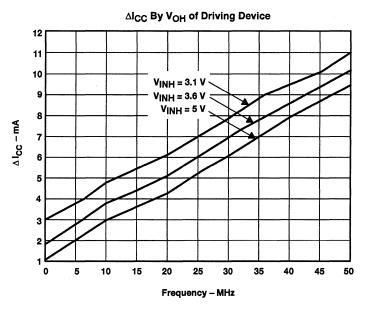

∆I<sub>CC</sub> Supply current change

The increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V or V<sub>CC</sub>.

I<sub>CEX</sub> Output high leakage current

The maximum leakage current into the collector of the pulldown output transistor when the output is high and the output forcing condition  $V_{\rm O} = 5.5 \text{ V}$ .

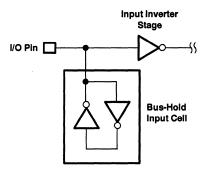

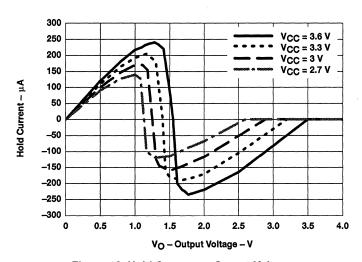

I<sub>I(hold)</sub> Input hold current

Input current that holds the input at the previous state when the driving device goes to a high-impedance state.

I<sub>IH</sub> High-level input current

The current into\* an input when a high-level voltage is applied to that input.

I<sub>IL</sub> Low-level input current

The current into\* an input when a low-level voltage is applied to that input.

Input/output power-off leakage current

The maximum leakage current into/out of the input/output transistors when forcing the input/output to 4.5 V and  $V_{\rm CC}$  = 0 V

IOH High-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a high level at the output.

I<sub>OL</sub> Low-level output current

The current into\* an output with input conditions applied that, according to the product specification, will establish a low level at the output.

<sup>\*</sup>Current out of a terminal is given as a negative value.

#### Off-state (high-impedance-state) output current (of a 3-state output) OZPU/PD

The current flowing into\* an output having 3-state capability with input conditions established that, according to the product specification, will establish the high-impedance state at the output.

#### Access time ta

The time interval between the application of a specified input pulse and the availability of valid signals at an output

#### tc Clock cycle time

Clock cycle time is 1/f<sub>max</sub>.

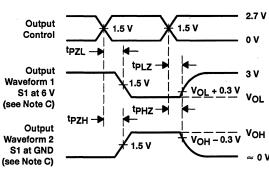

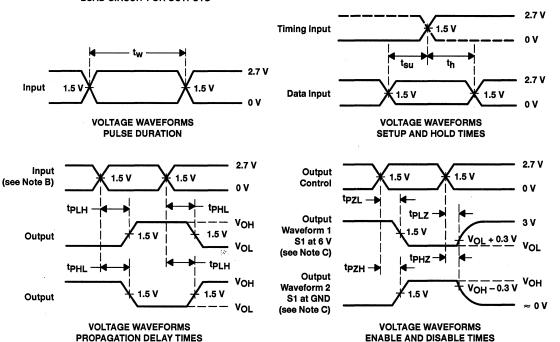

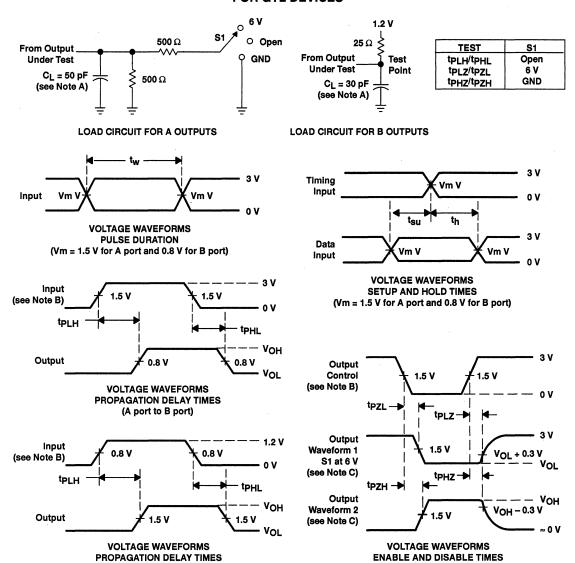

#### Disable time (of a 3-state or open-collector output) tdis

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from either of the defined active levels (high or low) to a high-impedance (off) state.

NOTE: For 3-state outputs, t<sub>dis</sub> = t<sub>PHZ</sub> or t<sub>PLZ</sub>. Open-collector outputs will change only if they are low at the time of disabling, so t<sub>dis</sub> = t<sub>PLH</sub>.

#### Enable time (of a 3-state or open-collector output) ten

The propagation time between the specified reference points on the input and output voltage waveforms with the output changing from a high-impedance (off) state to either of the defined active levels (high or low).

NOTE: In the case of memories, this is the access time from an enable input (e.g.,  $\overline{OE}$ ). For 3-state outputs, ten = tpzH or tpzL. Open-collector outputs will change only if they are responding to data that would cause the output to go low, so  $t_{en} = t_{PHI}$ .

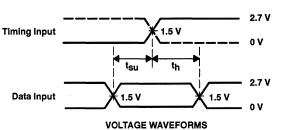

#### Hold time th

The time interval during which a signal is retained at a specified input terminal after an active transition occurs at another specified input terminal.

NOTES: 1. The hold time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is to be expected.

2. The hold time may have a negative value in which case the minimum limit defines the longest interval (between the release of the signal and the active transition) for which correct operation of the digital circuit is to be expected.

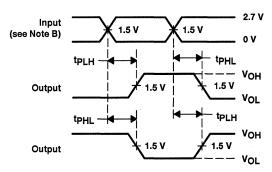

#### Propagation delay time tpd

The time between the specified reference points on the input and output voltage waveforms with the output changing from one defined level (high or low) to the other defined level (tpd = tpH or tpl H)

#### **tPHL** Propagation delay time, high-to-low level output

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined high level to the defined low level

#### **tPHZ** Disable time (of a 3-state output) from high level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined high level to the high-impedance (off) state

#### Propagation delay time, low-to-high level output **t**PLH

The time between the specified reference points on the input and output voltage waveforms with the output changing from the defined low level to the defined high level

<sup>\*</sup>Current out of a terminal is given as a negative value

#### t<sub>PLZ</sub> Disable time (of a 3-state output) from low level

The time interval between the specified reference points on the input and the output voltage waveforms with the 3-state output changing from the defined low level to the high-impedance (off) state

#### t<sub>PZH</sub> Enable time (of a 3-state output) to high level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined high level

#### t<sub>PZL</sub> Enable time (of a 3-state output) to low level

The time interval between the specified reference points on the input and output voltage waveforms with the 3-state output changing from the high-impedance (off) state to the defined low level

#### t<sub>su</sub> Setup time

The time interval between the application of a signal at a specified input terminal and a subsequent active transition at another specified input terminal.

NOTES: 1. The setup time is the actual time interval between two signal events and is determined by the system in which the digital circuit operates. A minimum value is specified that is the shortest interval for which correct operation of the digital circuit is guaranteed.

2. The setup time may have a negative value, in which case the minimum limit defines the longest interval (between the active transition and the application of the other signal) for which correct operation of the digital circuit is guaranteed.

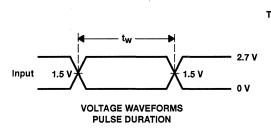

#### t<sub>w</sub> Pulse duration (width)

The time interval between specified reference points on the leading and trailing edges of the pulse waveform

#### V<sub>IH</sub> High-level input voltage

An input voltage within the more positive (less negative) of the two ranges of values used to represent the binary variables.

NOTE: A minimum is specified that is the least-positive value of high-level input voltage for which operation of the logic element within specification limits is to be expected.

#### V<sub>IL</sub> Low-level input voltage

An input voltage within the less positive (more negative) of the two ranges of values used to represent the binary variables.

NOTE: A maximum is specified that is the most-positive value of low-level input voltage for which operation of the logic element within specification limits is to be expected.

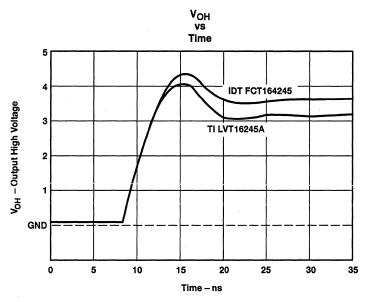

#### V<sub>OH</sub> High-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a high level at the output.

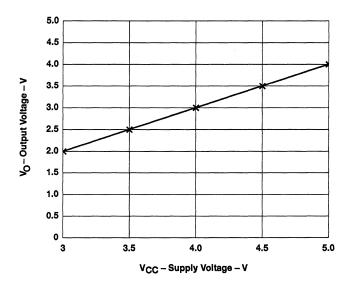

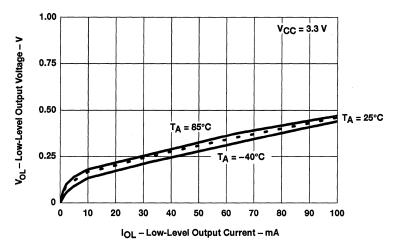

### V<sub>OL</sub> Low-level output voltage

The voltage at an output terminal with input conditions applied that, according to product specification, will establish a low level at the output.

#### V<sub>IT</sub> Positive-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage rises from a level below the negative-going threshold voltage, V<sub>IT</sub>...

#### V<sub>IT</sub> Negative-going input threshold level

The voltage level at a transition-operated input that causes operation of the logic element according to specification as the input voltage falls from a level above the positive-going threshold voltage,  $V_{\text{IT+}}$ .

#### **EXPLANATION OF FUNCTION TABLES**

The following symbols are used in function tables on TI data sheets:

H = high level (steady state)

L = low level (steady state)

↑ = transition from low to high level

↓ = transition from high to low level

= value/level or resulting value/level is routed to indicated destination

= value/level is re-entered

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state output

a . . . h = the level of steady-state inputs A through H respectively

Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

$\overline{\mathbb{Q}}_0$  = complement of  $\mathbb{Q}_0$  or level of  $\overline{\mathbb{Q}}$  before the indicated steady-state input

conditions were established

$Q_n$  = level of Q before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$

= one high-level pulse

= one low-level pulse

Toggle = each output changes to the complement of its previous level on each active transition indicated by ↓ or ↑

If, in the input columns, a row contains only the symbols H, L, and/or X, this means the indicated output is valid whenever the input configuration is achieved and regardless of the sequence in which it is achieved. The output persists so long as the input configuration is maintained.

If, in the input columns, a row contains H, L, and/or X together with  $\uparrow$  and/or  $\downarrow$ , this means the output is valid whenever the input configuration is achieved but the transition(s) must occur following the achievement of the steady-state levels. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q}_0$ ), it persists so long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. (If the output is shown as a pulse,  $\neg \neg \neg \neg \neg$ , the pulse follows the indicated input transition and persists for an interval dependent on the circuit.)

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, plus more. Below is the function table of a 4-bit bidirectional universal shift register, e.g., type SN74194.

**FUNCTION TABLE**

| INPUTS |       |    |          |        |       |   |      |      |   |                 | OUTPUTS         |                   |                 |  |

|--------|-------|----|----------|--------|-------|---|------|------|---|-----------------|-----------------|-------------------|-----------------|--|

| CLEAR  | МО    | DE | CLOCK    | SERIAL |       |   | PARA | LLEL |   | ۵.              | Ω-              |                   |                 |  |

| CLEAR  | S1 S0 | SO | CLUCK    | LEFT   | RIGHT | Α | В    | С    | D | QA              | QB              | дС                | QD              |  |

| L      | Х     | Х  | Х        | X      | Х     | Х | Х    | Х    | Х | L               | L               | L                 | L               |  |

| н      | Х     | X  | L        | ×      | X     | Х | Х    | Χ    | Χ | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub>   | Q <sub>D0</sub> |  |

| н      | Н     | Н  | 1        | ×      | Х     | a | b    | С    | d | а               | b               | С                 | d               |  |

| н      | L     | Н  | 1        | ×      | Н     | н | Н    | Н    | Н | н               | $Q_{An}$        | $Q_{Bn}$          | QCn             |  |

| н      | L     | Н  | 1        | X      | L     | L | L    | L    | L | L               | $Q_{An}$        | $\mathtt{Q}_{Bn}$ | QCn             |  |

| н      | Н     | L  | 1        | н      | X     | x | Х    | Χ    | Χ | QBn             | QCn             | $\mathtt{Q}_{Dn}$ | н               |  |

| н      | Н     | L  | <b>↑</b> | L      | X     | X | X    | Х    | Х | QBn             | $Q_{Cn}$        | $Q_{Dn}$          | L               |  |

| н      | L     | L  | Х        | X      | X     | Х | X    | X    | Χ | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>C0</sub>   | $Q_{D0}$        |  |

The first line of the table represents a synchronous clearing of the register and says that if clear is low, all four outputs will be reset low regardless of the other inputs. In the following lines, clear is inactive (high) and so has no effect.

The second line shows that so long as the clock input remains low (while clear is high), no other input has any effect and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Since on other lines of the table only the rising transition of the clock is shown to be active, the second line implicitly shows that no further change in the outputs will occur while the clock remains high or on the high-to-low transition of the clock.

The third line of the table represents synchronous parallel loading of the register and says that if S1 and S0 are both high then, without regard to the serial input, the data entered at A will be at output  $Q_A$ , data entered at B will be at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth lines represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$ , respectively, and the data previously at  $Q_D$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high and the levels at inputs A through D have no effect.

The sixth and seventh lines represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  are now at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  is no longer in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low and the levels at inputs A through D have no effect.

The last line shows that as long as both inputs are low, no other input has any effect and, as in the second line, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

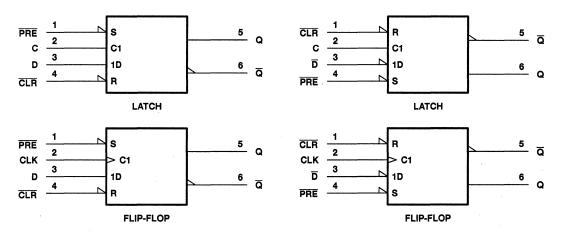

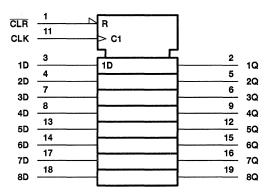

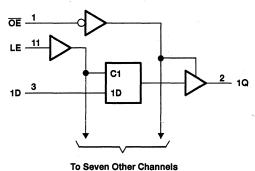

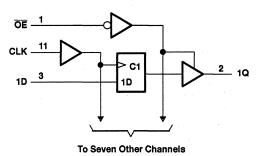

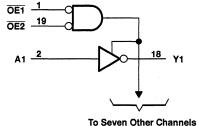

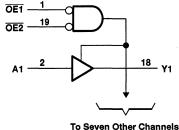

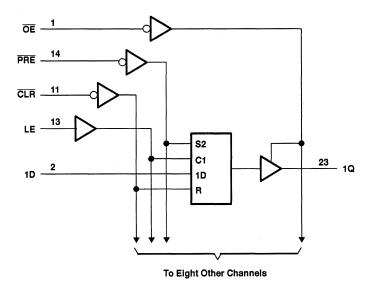

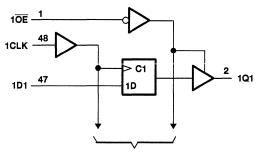

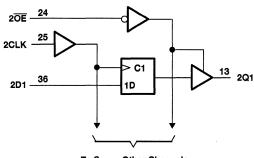

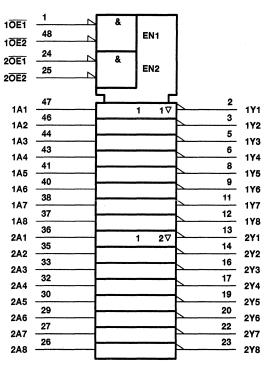

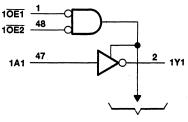

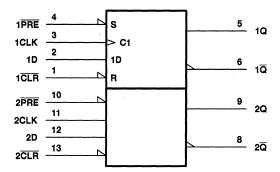

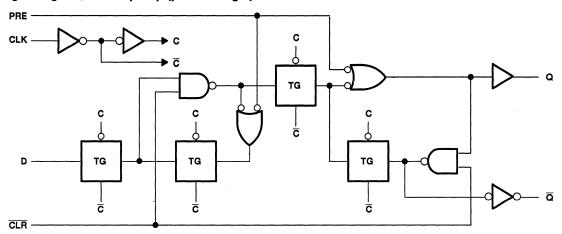

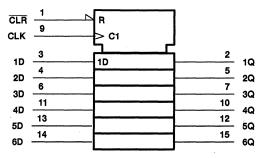

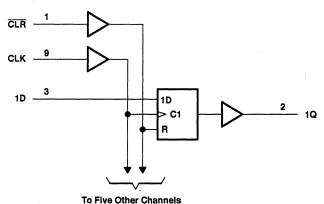

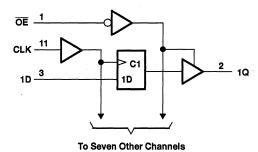

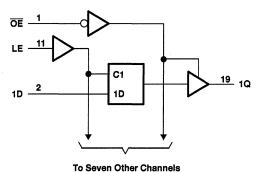

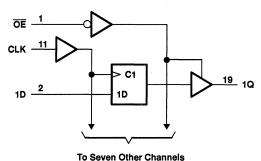

#### D FLIP-FLOP AND LATCH SIGNAL CONVENTIONS

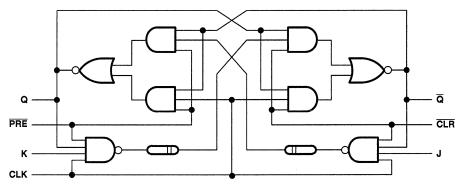

It is normal TI practice to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called Q and those producing complementary data are called  $\overline{Q}$ . An input that causes a Q output to go high or a  $\overline{Q}$  output to go low is called preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a Q output to go low is called clear (CLR). Bars are used over these pin names (PRE and CLR) if they are active low.

The devices on several data sheets are second-source designs, and the pin name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits  $\overline{D}$  and Q.

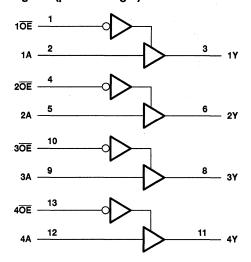

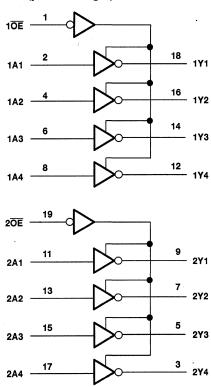

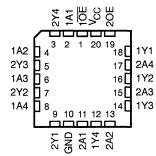

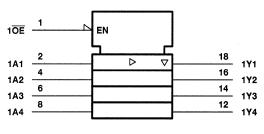

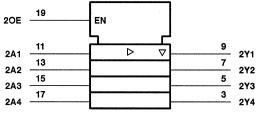

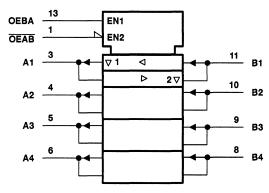

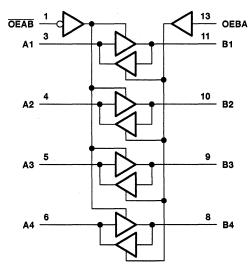

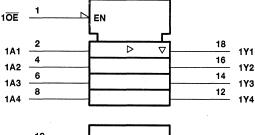

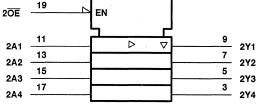

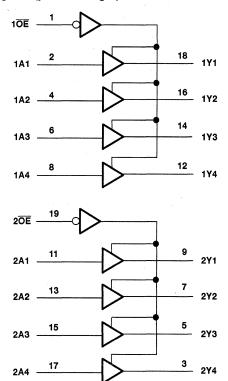

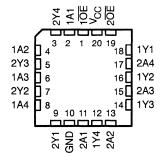

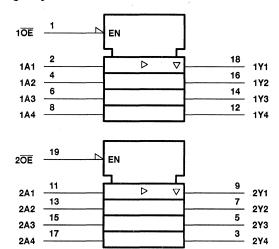

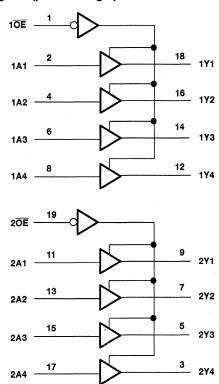

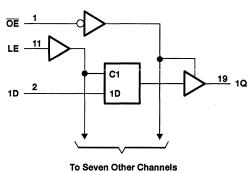

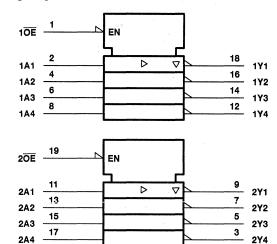

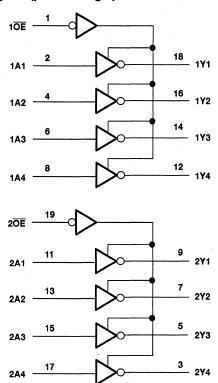

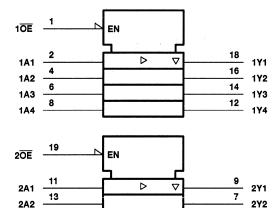

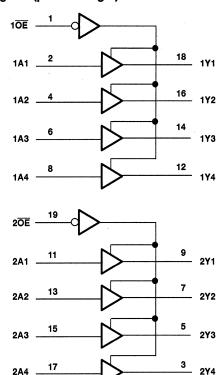

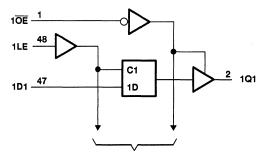

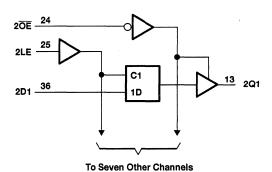

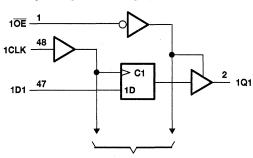

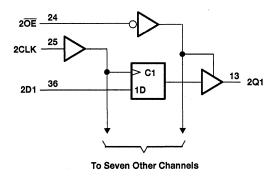

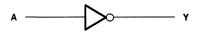

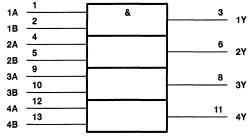

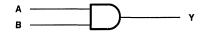

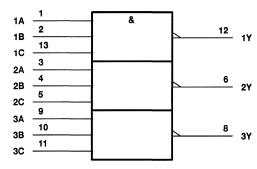

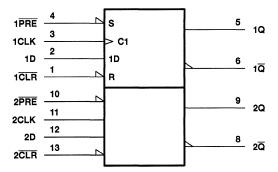

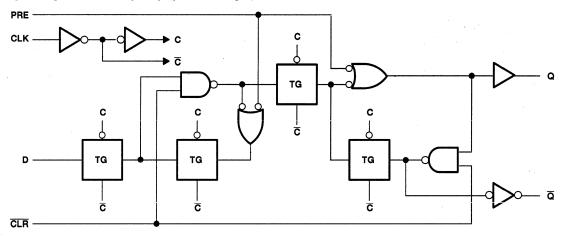

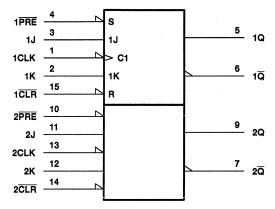

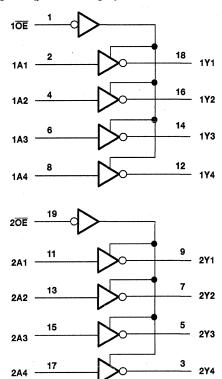

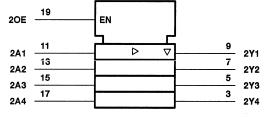

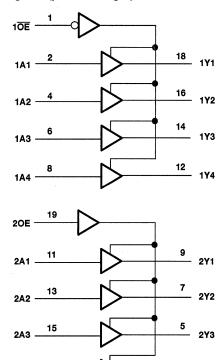

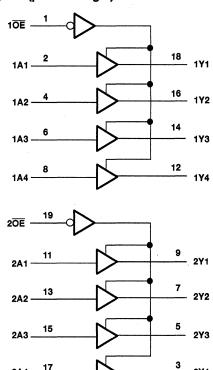

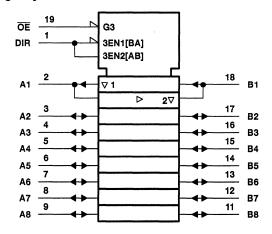

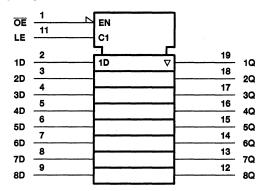

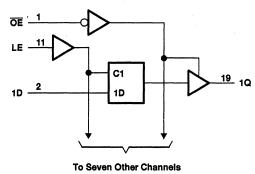

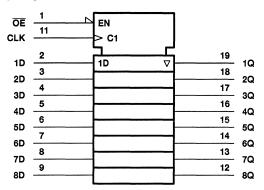

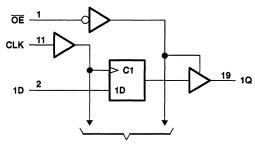

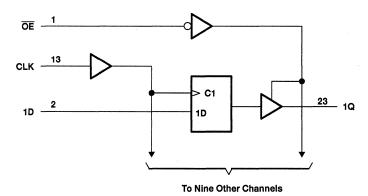

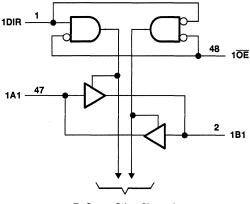

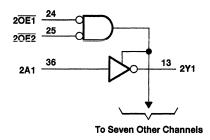

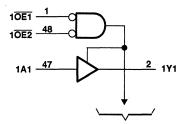

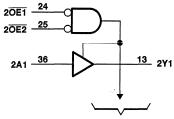

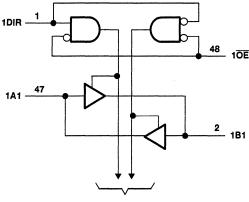

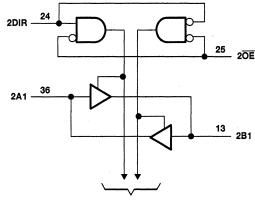

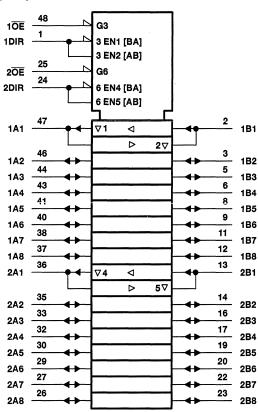

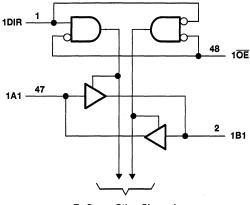

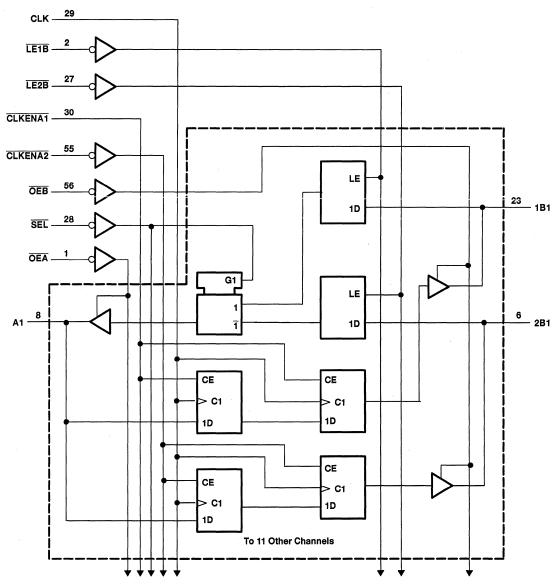

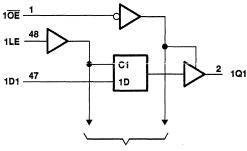

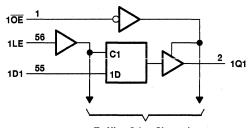

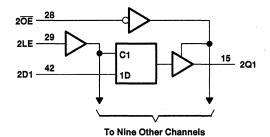

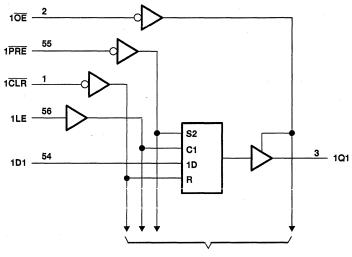

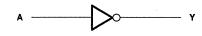

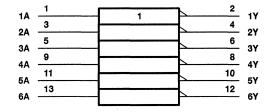

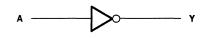

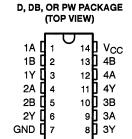

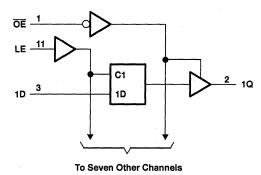

In some applications, it may be advantageous to redesignate the data input from D to  $\overline{D}$  or vice versa. In that case, all the other inputs and outputs should be renamed as shown below. Also shown are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown.

The figures show that when Q and  $\overline{Q}$  exchange names, the preset and clear pins also exchange names. The polarity indicators ( $\triangleright$ ) on  $\overline{PRE}$  and  $\overline{CLR}$  remain, as these inputs are still active low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

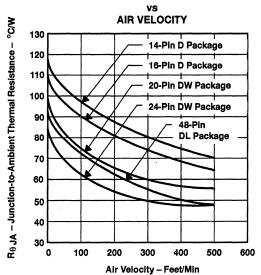

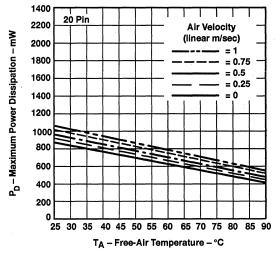

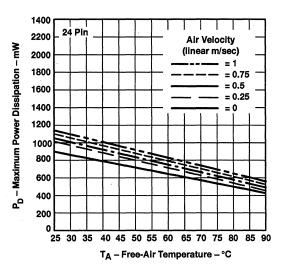

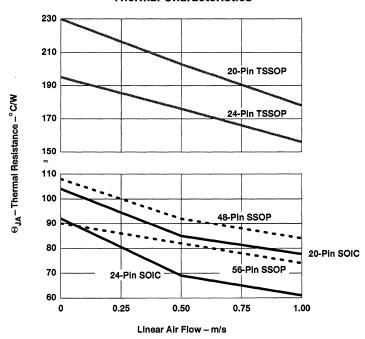

In digital system design, consideration must be given to thermal management of components. The small size of the small-outline package makes this even more critical. Figure 1 shows the thermal resistance of these packages for various rates of air flow. Figures 2, 3, 4, and 5 are derating curves for the DB package.

The thermal resistances in Figure 1 can be used to approximate typical and maximum virtual junction temperatures for the LVL family. In general, the junction temperature for any device can be calculated using using the following equation.

$$T_J = R_{\Theta JA} \times P_T + T_A$$

where:

T<sub>.1</sub> = virtual junction temperature

$R_{A,IA}$  = thermal resistance, junction to free air

P<sub>T</sub> = total power dissipation of the device (see Section 15, package thermal considerations)

$T_{\Delta}$  = free-air temperature

#### JUNCTION-TO-AMBIENT THERMAL RESISTANCE

Figure 1

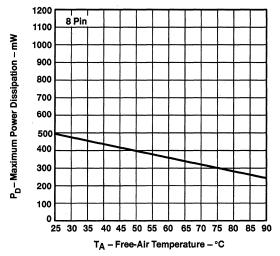

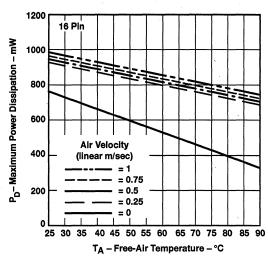

### DERATING CURVES FOR 210-MIL SHRINK SMALL-OUTLINE PACKAGE (DB)

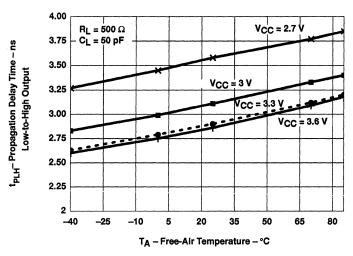

Figure 2

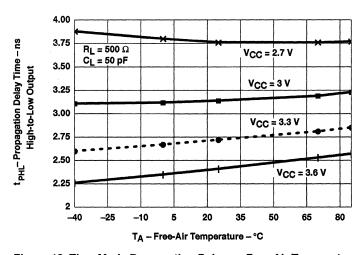

Figure 3

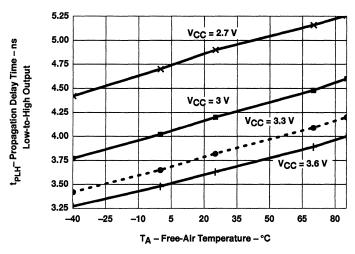

Figure 4

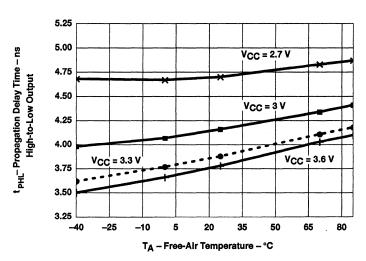

Figure 5

The following tables outline the logic functions Texas Instruments offers in a variety of technologies. The tables are organized by function type and list all available or planned options of that function. The technology columns identify the appropriate family and a particular data book where more information can be found. The applicable literature number, composed of either seven or eight alphanumeric characters, can be found at the lower right-hand corner on the back cover of each publication.

List of additional Advanced System Logic data books:

| ABT Devices†               | Advanced BiCMOS Technology                 | SCBD002A |

|----------------------------|--------------------------------------------|----------|

| AC and ACT Devices         | Advanced CMOS Logic Data Book              | SCAD001C |

| Advanced Logic Devices     | Advanced Logic and Bus-Interface Data Book | SCYD001  |

| ALS and AS Devices†        | ALS/AS Logic Data Book                     | SDAD001B |

| ATM and SONET Devices†     | ATM and SONET Product Information          | SDNS023  |

| BCT Devices                | BiCMOS Bus-Interface Logic Data Book       | SCBD001B |

| CDC Devices                | Clock-Distribution Circuits Data Book      | SCAD004  |

| F Devices                  | F Logic (SN54/74F) Data Book               | SDFD001B |

| FIFO Devices†              | High-Performance FIFO Memories Data Book   | SCAD003A |

| HC and HCT Devices         | High-Speed CMOS Logic Data Book            | SCLD001C |

| SCOPE™ Devices†            | SCOPE™ Product Information                 | SSYV001  |

| SPICE I/O Models           | Advanced Bus Interface SPICE I/O Models    | SCBD004  |

| Std TTL, LS, and S Devices | TTL Logic Data Book                        | SDLD001A |

|                            |                                            |          |

<sup>†</sup> Updated data book planned for this technology.

#### **Contents**

|      |                                                                 | Page |

|------|-----------------------------------------------------------------|------|

| GATI | ES                                                              | 1–15 |

|      | Positive-NAND Gates                                             | 1–15 |

|      | Positive-AND Gates                                              | 1–15 |

|      | Positive-OR/NOR Gates                                           | 1–16 |

|      | OR/NOR Gates                                                    | 1–16 |

|      | AND-OR Gates                                                    | 1–16 |

| INVE | RTING/NONINVERTING BUFFERS                                      | 1–17 |

|      | Hex Inverters/Noninverters                                      | 1–17 |

| BUFI | FERS/DRIVERS AND BUS TRANSCEIVERS                               | 1–18 |

|      | Buffers/Drivers                                                 | 1–18 |

|      | Universal Bus Transceivers (UBT)/Universal Bus Exchangers (UBE) | 1–19 |

|      | Bus Transceivers                                                | 1–20 |

|      | MOS Memory Drivers/Transceivers                                 | 1–23 |

|      |                                                                 |      |

## **FUNCTIONAL INDEX**

| Contents (Continued)                                              |      |

|-------------------------------------------------------------------|------|

|                                                                   | Page |

| TESTABILITY BUS-INTERFACE CIRCUITS                                |      |

| JTAG/IEEE 1149.1 Testability Circuits                             |      |

| FLIP-FLOPS AND LATCHES                                            |      |

| Flip-Flops                                                        | 1–25 |

| Latches                                                           |      |

| REGISTERS                                                         |      |

| Shift Registers                                                   |      |

| Register Files                                                    |      |

| COUNTERS                                                          | 1–30 |

| Synchronous Counters – Positive Edge Triggered                    | 1–30 |

| Asynchronous Counters (Ripple Clock) – Negative Edge Triggered    | 1–30 |

| 8-Bit Binary Counters With Registers                              | 1–30 |

| DECODERS, ENCODERS, DATA SELECTORS/MULTIPLEXERS                   | 1–31 |

| Encoders/Data Selectors/Multiplexers                              | 1–31 |

| Decoders/Demultiplexers                                           | 1–32 |

| Shifters                                                          | 1–32 |

| COMPARATORS AND PARITY GENERATORS/CHECKERS                        | 1–33 |

| Comparators                                                       | 1–33 |

| Address Comparators                                               | 1–33 |

| Parity Generators/Checkers                                        | 1–33 |

| BUS SWITCHES AND 5-V/3-V VOLTAGE TRANSLATORS                      | 1–34 |

| Crossbar Technology (CBT)                                         | 1–34 |

| ARITHMETIC CIRCUITS                                               | 1–34 |

| Parallel Binary Adders                                            | 1–34 |

| Accumulators, Arithmetic Logic Units, Look-Ahead Carry Generators | 1–34 |

| FIFO MEMORIES                                                     | 1–35 |

| First-In, First-Out Memories (FIFOs)                              | 1–35 |

| CLOCK-DISTRIBUTION CIRCUITS                                       | 1–37 |

| Clock-Distribution Circuits (CDC)                                 | 1–37 |

| ECL TRANSLATORS                                                   |      |

| ECL to TTL or TTL to ECL Translators                              |      |

#### **GATES**

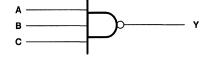

#### **Positive-NAND Gates**

| DESCRIPTION    | CUTDUT | TVDE   |     |    |   |    | TE  | CHNOL | OGY |     |     |    |     |

|----------------|--------|--------|-----|----|---|----|-----|-------|-----|-----|-----|----|-----|

| DESCRIPTION    | OUTPUT | TYPE   | ALS | AS | F | HC | HCT | AC    | ACT | ВСТ | ABT | LV | LVC |

|                |        | ′30    | ~   | ~  | ~ |    |     |       |     |     |     |    |     |

| 8-Input        |        | ′11030 |     |    |   |    |     | ~     | ~   |     |     |    |     |

| 13-Input       |        | ′133   | ~   |    |   | ~  |     |       |     |     |     |    |     |

| Dual 2-Input   |        | ′8003  | ~   |    |   |    |     |       |     |     |     |    |     |

|                |        | ′20    | ~   | ~  | ~ | ~  |     |       |     |     |     |    |     |

| Dual 4-Input   |        | ′40    | ~   |    |   |    |     |       |     |     |     |    |     |

|                | ′11020 |        |     |    |   |    | ~   | ~     |     |     |     |    |     |

| Triple 3-Input |        | ′10    | ~   | ~  | ~ | ~  |     |       |     |     |     |    | +   |

|                |        | ′1010  | ~   |    |   |    |     |       |     |     |     |    |     |

|                |        | ′11010 |     |    |   | }  |     | ~     | ~   |     |     |    |     |

|                |        | ′00    | ~   | ~  | ~ | 1  | ~   |       |     |     |     | ~  | +   |

|                |        | ′11000 |     |    |   |    |     | ~     | ~   |     |     |    |     |

|                |        | ′37    | V   |    |   |    |     |       |     |     |     |    |     |

| Quad 2-Input   | ОС     | ′38    | ~   |    | ~ |    |     |       |     |     |     |    |     |

|                |        | ′132   |     |    |   | ~  |     |       |     |     |     |    |     |

|                |        | ′11132 |     |    |   |    |     | ~     | ~   |     |     |    |     |

|                |        | ′1000  |     | ~  |   |    |     |       |     |     |     |    |     |

| Hex 2-Input    |        | ′804   | V   | ~  |   |    |     |       |     |     |     |    |     |

| Ound Oleman    | ОС     | ′01    | V   |    |   | ~  |     |       |     |     |     |    |     |

| Quad 2-Input   | 00     | ′03    | ~   |    |   | ~  |     |       |     |     |     |    | -   |

### **Positive-AND Gates**

| DESCRIPTION      | ОИТРИТ | TYPE   |     |    |   |    | TE  | CHNOLO | OGY |     |     |    |     |

|------------------|--------|--------|-----|----|---|----|-----|--------|-----|-----|-----|----|-----|

| DESCRIPTION      | COIPOI | ITPE   | ALS | AS | F | HC | нст | AC     | ACT | ВСТ | ABT | LV | LVC |

| Quad 2-Input     | oc     | ′09    | ~   |    |   | ~  |     |        |     |     |     |    |     |

| Quad 2-Input     |        | ′7001  |     |    |   | ~  |     |        |     |     |     |    |     |

| Dual 4 land      |        | ′21    | ~   | V  | ~ | ~  |     |        |     |     |     |    |     |

| Dual 4-Input     |        | ′11021 |     |    |   |    |     | ~      | ~   |     |     |    |     |

| Triple O long st | ′11    | ′11    | ~   | ~  | ~ | ~  |     |        |     |     |     |    |     |

| Triple 3-Input   |        | ′11011 |     |    |   |    |     | ~      | ~   |     |     |    |     |

|                  |        | ′08    | ~   | ~  | ~ | ~  | ~   |        |     |     |     | ~  | +   |

| Quad 2-Input     |        | ′1008  |     | V  |   |    |     |        |     |     |     |    |     |

|                  |        | ′11008 |     |    |   |    |     | ~      | ~   |     |     |    |     |

| Hex 2-Input      |        | ′808   |     | ~  |   |    |     |        |     |     |     |    |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

#### **GATES**

#### Positive-OR/NOR Gates

| DESCRIPTION    | ОИТРИТ | TVDE   |     |    |   |    | TE  | CHNOLO | OGY |     |     |    |     |

|----------------|--------|--------|-----|----|---|----|-----|--------|-----|-----|-----|----|-----|

| DESCRIPTION    | COIPOI | TYPE   | ALS | AS | F | НС | HCT | AC     | ACT | ВСТ | ABT | LV | LVC |

| Triple 3-Input |        | ′4075  |     |    |   | ~  |     |        |     |     |     |    |     |

| Quad 2-Input   |        | ′32    | ~   | ~  | ~ | ~  | ~   |        |     |     |     | ~  | +   |

|                |        | ′1032  |     | V  |   |    |     |        |     |     |     |    |     |

|                | ′11032 |        |     |    |   |    | ~   | ~      |     |     |     |    |     |

|                |        | ′7032  |     |    |   | ~  |     | ,      |     |     |     |    |     |

| Hex 2-Input    |        | ′832   | ~   | V  |   | ~  |     |        |     |     |     |    |     |

| Dual 5-Input   |        | ′260   |     |    | ~ |    |     |        |     |     |     |    |     |

| Trials O land  |        | ′27    | V   | ~  | ~ | ~  |     |        |     |     |     |    |     |

| Triple 3-Input |        | ′11027 |     |    |   |    |     | ~      | ~   |     |     |    |     |

|                |        | ′02    | ~   | ~  | ~ | ~  | ~   |        |     |     |     | ~  | +   |

| 0 101 1        | OC .   | ′33    | ~   |    |   |    |     |        |     |     |     |    |     |

| Quad 2-Input   |        | ′7002  |     |    |   | V  |     |        |     |     |     |    |     |

|                |        | ′11002 |     |    |   |    |     | ~      | ~   |     |     |    |     |

| Hex 2-Input    |        | ′805   | ~   | ~  |   | ~  |     |        |     |     |     |    |     |

#### **OR/NOR Gates**

| DECODIDION                          | OUTPUT | TYPE   |     |    |   |    | TEC | CHNOLO | OGY |     |     |    |     |

|-------------------------------------|--------|--------|-----|----|---|----|-----|--------|-----|-----|-----|----|-----|

| DESCRIPTION                         | OUIPUI | ITPE   | ALS | AS | F | НС | HCT | AC     | ACT | ВСТ | ABT | LV | LVC |

| Quad 2-Input<br>Exclusive-OR Gates  |        | ′86    | ~   | ~  | ~ | ~  |     |        |     |     |     |    | +   |

| With Totem-Pole Outputs             |        | ′11086 |     |    |   |    |     | ~      | ~   |     |     |    |     |

| Quad 2-Input<br>Exclusive-OR Gates  | ос     | ′136   | V   |    |   |    |     |        |     |     |     |    |     |

|                                     | OD     | ′266   |     |    |   | ~  |     |        |     |     |     |    |     |

| Quad 2-Input<br>Exclusive-NOR Gates |        | ′810   | ~   |    |   |    |     |        |     |     |     |    |     |

| Exolusive HOTT dates                | ОС     | ′811   | ~   |    |   |    |     |        |     |     |     |    |     |

#### **AND-OR Gates**

| DESCRIPTION                  | OUTPUT | TYPE |     |    |   | TE | CHNOLO | GY |     |     |     |

|------------------------------|--------|------|-----|----|---|----|--------|----|-----|-----|-----|

| DESCRIPTION                  | COIPOI | ITPE | ALS | AS | F | HC | HCT    | AC | ACT | ВСТ | ABT |

| Dual 2-Wide 2-Input, 3-Input |        | ′51  |     |    | ~ |    |        |    |     |     |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

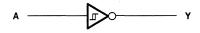

#### **INVERTING/NONINVERTING BUFFERS**

## **Hex Inverters/Noninverters**

| DECODIDATION  | CUITDUIT | TVDE   |     |    |   |    | TE  | CHNOL | OGY |     |     |    |     |

|---------------|----------|--------|-----|----|---|----|-----|-------|-----|-----|-----|----|-----|

| DESCRIPTION   | OUTPUT   | TYPE   | ALS | AS | F | НС | HCT | AC    | ACT | ВСТ | ABT | LV | LVC |

|               |          | ′04    | ~   | ~  | ~ | ~  | ~   |       |     |     |     | ~  | +   |

|               |          | ′U04   |     |    |   | ~  |     |       |     |     |     | ~  | +   |

|               |          | ′11004 |     |    |   |    |     | ~     | ~   |     |     |    |     |

| Han bereaten  | ОС       | ′05    | ~   |    |   | ~  |     |       |     |     |     |    |     |

| Hex Inverters |          | ′14    |     |    |   | ~  |     |       |     |     |     | V  | +   |

|               |          | ′11014 |     |    |   |    |     | ~     | V   |     |     |    |     |

|               |          | ′1004  | ~   | ~  |   |    |     |       |     |     |     |    |     |

|               |          | ′1005  | ~   |    |   |    |     |       |     |     |     |    |     |

|               |          | ′11034 |     |    |   |    |     | ~     | V   |     |     |    |     |

| Hex           | oc       | ′35    | ~   |    |   |    |     |       |     |     |     |    |     |

| Noninverters  |          | ′1034  | ~   | ~  |   |    |     |       |     |     |     |    |     |

|               | OC       | ′1035  | ~   |    |   |    |     |       |     |     |     |    |     |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

#### **Buffers/Drivers**

| DESCRIPTION                            | ОИТРИТ | TYPE    |     |    |     |    |     | TE | CHNOL | OGY |     |     |    |          |      |

|----------------------------------------|--------|---------|-----|----|-----|----|-----|----|-------|-----|-----|-----|----|----------|------|

| DESCRIPTION                            | COIPOI | ITPE    | ALS | AS | F   | нс | HCT | AC | ACT   | ВСТ | ABT | LVT | LV | LVC      | ALVC |

| Quad Buffers/Drivers                   | 38     | ′125    |     |    | ~   | 1  | ~   |    |       | ~   | ~   | ~   |    | +        |      |

|                                        |        | ′126    |     |    | ~   | V  |     |    |       | ~   | ~   |     |    | +        |      |

| Noninverting                           | 38     | ′365    |     |    |     | 1  |     |    |       |     |     |     |    |          |      |

| Hex Buffers/Drivers                    |        | ′367    |     |    |     | ~  |     |    |       |     |     |     |    | <u> </u> |      |

| Inverting<br>Hex Buffers/Drivers       | 38     | ′368    |     |    |     | ~  |     | ·  |       |     |     |     |    |          |      |

|                                        |        | ′241    | ~   | ~  | ~   | ~  | ~   |    |       | ~   | ~   |     |    | +        |      |

|                                        |        | ′11241  |     |    |     |    |     | ~  | ~     |     |     |     |    |          |      |

|                                        |        | ′25241  |     |    |     |    |     |    |       |     | +   |     |    |          |      |

|                                        |        | ′244    | V   | ~  | V   | V  | ~   |    |       | ~   | ~   |     | V  | +        |      |

|                                        | 38     | ′244A   |     |    |     |    |     |    |       |     |     | V   |    |          |      |

| Noninverting                           |        | ′11244  |     |    |     |    |     | ~  | ~     |     |     |     |    |          |      |

| Octal Buffers/Drivers                  | ĺ      | ′1244   | ~   |    |     |    |     |    |       |     |     |     |    |          |      |

|                                        |        | ′25244  |     |    |     |    |     |    |       | ~   | +   |     |    |          |      |

|                                        |        | ′541    | V   |    | · V | V  | ~   |    |       | ~   | V   |     |    | +        |      |

|                                        |        | ′757    |     | ~  |     |    |     |    |       | V   |     |     |    |          |      |

|                                        | ос     | ′760    | ~   | ~  |     |    |     |    |       | ~   |     |     |    |          |      |

|                                        |        | ′25760  |     |    |     |    |     |    |       | +   |     |     |    |          |      |

|                                        |        | ′240    | ~   | ~  | ~   | ~  | ~   |    |       | ~   | ~   | ~   | ~  | +        |      |

|                                        |        | ′11240  |     |    |     |    |     | ~  | V     |     |     |     |    |          |      |

|                                        |        | ′1240   | V   |    |     |    |     |    |       |     |     |     |    |          |      |

| Inverting                              | 38     | ′25240  |     |    |     |    |     |    |       | ~   |     |     |    |          |      |

| Octal Buffers/Drivers                  |        | ′466    | ~   |    |     |    |     |    |       |     |     |     |    |          |      |

|                                        | ŀ      | ′540    | ~   |    |     | ~  | ~   |    |       | ~   | ~   |     |    | +        |      |

|                                        |        | ′756    | ~   | ~  |     |    |     |    |       | ~   |     |     |    |          |      |

|                                        | oc     | ′763    | ~   | ~  |     |    |     |    |       |     |     |     |    | <b></b>  |      |

| Inverting and                          | 38     | ′230    |     | ~  |     |    |     |    |       |     |     |     |    | <u> </u> |      |

| Noninverting                           |        |         |     |    |     |    |     |    |       |     |     |     |    |          |      |

| Octal Buffers/Drivers                  | oc     | ′762    |     | ~  |     |    |     |    |       |     |     |     |    | ļ        |      |

| Triple 4-Input<br>OR/NOR Drivers       |        | ′11802  |     |    |     |    |     |    | ~     |     |     |     |    |          |      |

| Marchania Pari                         |        | ′827    |     |    |     |    |     |    |       |     | ~   |     |    | ~        |      |

| Noninverting<br>10-Bit Buffers/Drivers | 38     | ′11827  |     |    |     |    |     | ~  | ~     |     |     |     |    |          |      |

| TO DICEONO DICTOR                      |        | ′29827  | ~   |    |     |    |     |    |       | ~   |     |     |    |          |      |

|                                        |        | ′828    |     |    |     |    |     |    |       |     | +   |     |    | +        |      |

| Inverting<br>10-Bit Buffers/Drivers    | 38     | ′11828  |     |    |     |    |     | ٧  | ~     |     |     |     |    |          |      |

| . O Dit Danois/Directs                 |        | ′29828  | ~   |    |     |    |     |    |       | ~   |     |     |    |          |      |

|                                        |        | ′16241  |     |    |     |    |     |    | ~     |     | ~   |     |    | +        |      |

| Noninverting                           | 00     | ′16244  |     |    |     |    |     | ~  | 1     |     | ~   |     |    | +        | +    |

| 16-Bit Buffers/Drivers                 | 38     | ′16244A |     |    |     |    |     |    |       |     |     | 1   |    |          |      |

|                                        |        | ′16541  |     |    |     |    |     |    | V     |     | V   |     |    | +        |      |

<sup>✓</sup> Product available in technology indicated

<sup>+</sup> New product planned in technology indicated

## **Buffers/Drivers (Continued)**

| DECODIDEION                                             | ОИТРИТ | TVDE   |     |    |   |    |     | TE | CHNOL | OGY |     |     |    |     |      |

|---------------------------------------------------------|--------|--------|-----|----|---|----|-----|----|-------|-----|-----|-----|----|-----|------|

| DESCRIPTION                                             | OUIPUI | TYPE   | ALS | AS | F | нс | нст | AC | ACT   | ВСТ | ABT | LVT | LV | LVC | ALVC |

| Inverting                                               | 200    | ′16240 |     |    |   |    |     | V  | ~     |     | ~   |     |    | +   | +    |

| 16-Bit Buffers/Drivers                                  | 3S     | ′16540 |     |    |   |    |     |    | ~     |     | ~   |     |    |     |      |

| Noninverting<br>18-Bit Buffers/Drivers                  | 38     | ′16825 |     |    |   |    |     |    | ~     |     | ~   |     |    |     | +    |

| Inverting<br>18-Bit Buffers/Drivers                     | 38     | ′16826 |     |    |   |    |     |    |       |     | +   |     |    |     |      |

| Noninverting<br>20-Bit Buffers/Drivers                  | 38     | ′16827 |     |    |   |    |     |    | V     |     | V   |     |    |     | +    |

| Inverting<br>20-Bit Buffers/Drivers                     | 38     | ′16828 |     |    |   |    |     |    |       |     | +   |     |    |     | +    |

| Octal Buffers/Drivers<br>With Input Pullup<br>Resistors |        | ′746   | ~   |    |   |    |     |    |       |     |     |     |    |     |      |

### Universal Bus Transceivers (UBT™)/Universal Bus Exchangers (UBE™)

| DECODIDEION                                                     | CUTDUT | TVDE    |    |     |     | TECHNO | DLOGY |    |     |      |

|-----------------------------------------------------------------|--------|---------|----|-----|-----|--------|-------|----|-----|------|

| DESCRIPTION                                                     | OUTPUT | TYPE    | AC | ACT | ВСТ | ABT    | LVT   | LV | LVC | ALVC |

| Noninverting 18-Bit                                             | 38     | ′16500  |    |     |     |        | ~     |    |     | +    |

| Universal Bus Transceivers (UBT™)                               | 35     | ′16500B |    |     |     | V      |       |    |     |      |

|                                                                 |        | ′16501  |    |     |     | ~      | V     |    | +   | +    |

| Noninverting 18-Bit<br>Universal Bus Transceivers (UBT™)        | 38     | ′16600  |    |     |     | ~      |       |    |     | +    |

| Oniversal Dus Transceivers (ODT )                               |        | ′16601  |    |     |     | ~      |       |    |     | +    |

| Noninverting 36-Bit<br>Universal Bus Transceivers (UBT™)        | 38     | ′32501  |    |     |     | V      |       |    |     |      |

| Noninverting 16-Bit Tri-Port<br>Universal Bus Exchangers (UBE™) | 38     | ′32316  |    |     |     | v      |       |    |     |      |

| Noninverting 18-Bit Tri-Port<br>Universal Bus Exchangers (UBE™) | 38     | ′32318  |    | ,   |     | ~      |       |    |     |      |

|                                                                 |        | ′162500 |    |     |     | V      |       |    |     |      |

| 18-Bit Universal Bus Transceivers                               | 00     | ′162501 |    |     |     | ~      |       |    |     |      |

| (UBT™) With Series Resistors on B Port                          | 3S     | ′162600 |    |     |     | +      |       |    |     |      |

|                                                                 |        | ′162601 |    |     |     | ~      |       |    |     |      |

| SCOPE™ 18-Bit<br>Universal Bus Transceivers (UBT™)              | 38     | ′18502  |    |     |     | ~      | +     |    |     |      |

| SCOPE™ 20-Bit<br>Universal Bus Transceivers (UBT™)              | 3S     | ′18504  |    |     |     | ~      | +     |    |     |      |

<sup>✔</sup> Product available in technology indicated

<sup>+</sup> New product planned in technology indicated

### **Bus Transceivers**

| DESCRIPTION                         | ОИТРИТ | TYPE             |     |    |   |                                                  |          | TE | CHNOL        | OGY     |          |          |    |                                                  |                                                  |

|-------------------------------------|--------|------------------|-----|----|---|--------------------------------------------------|----------|----|--------------|---------|----------|----------|----|--------------------------------------------------|--------------------------------------------------|

| DESCRIPTION                         | JUIPUI | ITPE             | ALS | AS | F | НС                                               | HCT      | AC | ACT          | вст     | ABT      | LVT      | LV | LVC                                              | ALVC                                             |

| Noninverting<br>Quad Transceivers   | 38     | ′243             | ~   |    | ~ |                                                  |          | į, |              |         |          |          |    |                                                  |                                                  |

| Inverting                           | ОС     | ′758             | ~   |    |   |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

| Quad Transceivers                   | 38     | ′242             |     |    | ~ |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

|                                     |        | ′245             | ~   | ~  | ~ | ~                                                | V        |    |              | V       | ~        |          | ~  | +                                                |                                                  |

|                                     |        | ′245A            |     |    |   |                                                  |          |    |              |         |          | V        |    |                                                  |                                                  |

|                                     |        | ′1245            | ~   |    |   |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

|                                     | 38     | ′11245           |     |    |   |                                                  |          | V  | V            |         |          |          |    |                                                  |                                                  |

| Noninverting                        |        | ′25245           |     |    |   |                                                  |          |    |              | V       | ~        |          |    |                                                  |                                                  |

| Octal Transceivers                  |        | ′645             | ~   | ~  |   | ~                                                | ~        |    |              |         |          |          |    |                                                  |                                                  |

|                                     |        | ′1645            | ~   |    |   |                                                  |          |    |              |         |          |          |    | 1                                                |                                                  |

|                                     | 00     | ′621             | ~   | ,  | ~ |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

|                                     | oc     | ′641             | ~   | ~  |   |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

|                                     | OC/3S  | ′639             | ~   | V  |   |                                                  |          |    |              |         |          |          |    |                                                  |                                                  |

|                                     |        | <b>′620</b>      | ~   |    |   |                                                  |          |    |              | ~       | V        |          |    | ļ                                                |                                                  |

|                                     |        | <sup>′</sup> 623 | ~   | ~  | 1 | ~                                                | ~        |    |              | ~       | ~        |          |    |                                                  |                                                  |

| _                                   |        | ′11623           |     |    |   |                                                  |          |    | V            | <b></b> |          |          |    |                                                  |                                                  |

|                                     | 38     | ′640             | V   | ~  |   | 1                                                |          |    |              | ~       | 1        |          |    |                                                  |                                                  |

| Inverting                           |        | ′1640            | V   |    |   |                                                  |          |    |              |         |          |          |    |                                                  | <del></del>                                      |

| Octal Transceivers                  |        | ′11640           |     |    |   |                                                  |          |    | 1            |         |          |          |    |                                                  | <b></b>                                          |

|                                     |        | ′642             | ~   |    |   |                                                  |          |    | ٠.           |         |          |          |    | <b></b>                                          | -                                                |

|                                     | oc     | ′25642           |     |    |   | <del>                                     </del> | <b> </b> |    | <del> </del> | ~       |          |          |    | 17                                               | <del> </del>                                     |

|                                     | OC/3S  | ′638             | ~   | ~  |   | <del> </del>                                     |          |    | <u> </u>     |         | l        |          |    |                                                  | <del>                                     </del> |

| Noninverting                        |        | ′863             |     |    |   | <del>                                     </del> |          |    |              |         | V        |          |    | +                                                | <del>                                     </del> |

| 9-Bit Transceivers                  | 38     | ′29863           | ~   |    |   |                                                  |          |    |              | ~       | <u> </u> | <b></b>  |    | <del>                                     </del> | <del> </del>                                     |

| Inverting<br>9-Bit Transceivers     | 38     | ′29864           |     |    | - |                                                  |          |    |              | ~       |          |          |    |                                                  |                                                  |

| Noninverting                        |        | ′861             |     |    |   | 1                                                |          |    |              |         | +        | l        |    | <del>                                     </del> | <b></b>                                          |

| 10-Bit Transceivers                 | 38     | ′29861           |     |    |   | 1                                                |          |    |              | ~       |          | l        |    | <u> </u>                                         |                                                  |

| Inverting<br>10-Bit Transceivers    | 38     | ′29862           |     |    |   |                                                  |          |    |              | ~       |          |          |    |                                                  |                                                  |

|                                     |        | ′16245           |     |    |   |                                                  |          | ~  | V            |         | ~        |          |    | +                                                | +                                                |

| Noninverting                        | 38     | ′16245A          |     |    |   | t                                                |          |    |              |         | ~        | 1        |    | <b>†</b>                                         | <b>†</b>                                         |

| 16-Bit Transceivers                 |        | ′16623           |     |    |   |                                                  |          | ~  | ~            |         | ~        | <b> </b> |    | <b>†</b>                                         |                                                  |

| Inverting                           |        | ′16640           |     |    |   | <b>†</b>                                         |          | ~  | 1            |         | ~        |          |    | İ                                                |                                                  |

| 16-Bit Transceivers                 | 38     | ′16620           |     |    |   |                                                  |          | ~  | 1            |         | +        | <b> </b> |    | <u> </u>                                         |                                                  |

| Noninverting<br>18-Bit Transceivers | 38     | ′16863           |     |    |   |                                                  |          |    | ~            |         | ~        |          |    |                                                  |                                                  |

| Inverting<br>18-Bit Transceivers    | 38     | ′16864           |     |    |   |                                                  |          |    |              |         | +        |          |    |                                                  |                                                  |

<sup>✓</sup> Product available in technology indicated

+ New product planned in technology indicated

### **Bus Transceivers (Continued)**

| DESCRIPTION                         | ОИТРИТ | TYPE   |          |    |   |          |     | TE | CHNOL | OGY |     |     |    |     |      |

|-------------------------------------|--------|--------|----------|----|---|----------|-----|----|-------|-----|-----|-----|----|-----|------|

| DESCRIPTION                         | OUTPUT | ITPE   | ALS      | AS | F | НС       | HCT | AC | ACT   | ВСТ | ABT | LVT | LV | LVC | ALVC |

| Noninverting<br>20-Bit Transceivers | 38     | ′16861 |          |    |   |          |     |    | 1     |     | +   |     |    |     |      |

| Inverting<br>20-Bit Transceivers    | 38     | ′16862 |          |    |   |          |     |    |       |     | +   |     |    |     |      |

|                                     |        | ′11470 |          |    |   |          |     |    | ~     |     |     |     |    |     |      |

|                                     |        | ′543   |          |    | 1 |          |     |    |       | ~   | ~   | ~   |    | +   |      |

|                                     |        | ′11543 |          |    |   |          |     |    | ~     |     |     |     |    |     |      |

|                                     |        | ′646   | ~        | ~  |   | ~        | ~   |    |       | ~   | ~   | ~   |    | +   |      |

|                                     | 38     | ′646A  |          |    |   |          |     |    |       |     | ~   |     |    |     |      |

| Noninverting<br>Octal Registered    | 33     | ′11646 |          |    |   |          |     | ~  | ~     |     |     |     |    |     |      |

| Transceivers                        |        | ′652   | ~        | ~  |   | ~        | ~   |    |       | ~   | ~   | ~   |    | +   |      |

|                                     |        | ′11652 |          |    |   |          |     | V  | ~     |     |     |     |    |     |      |

|                                     |        | ′2952  |          |    |   |          |     |    |       | ~   | +   | ~   |    | +   |      |

|                                     |        | ′2952A |          |    |   |          |     |    |       |     | ~   |     |    |     |      |

|                                     | OC/3S  | ′653   | ~        |    |   |          |     |    |       |     |     |     |    |     |      |

|                                     | 00/33  | ′654   | 1        |    |   |          |     |    |       |     |     |     |    |     |      |

|                                     |        | ′544   |          |    |   |          |     |    |       | ~   | +   |     |    | +   |      |

|                                     |        | ′11544 |          |    |   |          |     |    | V     |     |     |     |    |     |      |

| Inverting<br>Octal Registered       | 38     | ′648   | 1        | ~  |   |          |     |    |       | ~   | +   |     |    |     |      |

| Transceivers                        | 00     | ′11648 |          |    |   |          |     |    | 1     |     |     |     |    |     |      |

|                                     |        | ′651   | 1        | ~  |   |          |     |    |       | ~   | ~   |     |    |     |      |

|                                     |        | ′2953  | <u> </u> |    |   | <u> </u> |     |    |       | ~   | +   |     |    |     |      |

|                                     |        | ′16470 |          |    |   |          |     |    | ~     |     | ~   |     |    |     |      |

| Noninverting                        |        | ′16543 | <u> </u> |    |   |          |     | ~  | ~     |     | ~   | ~   |    | +   | +    |

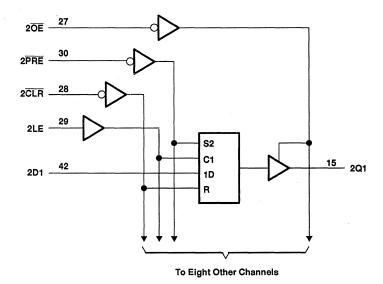

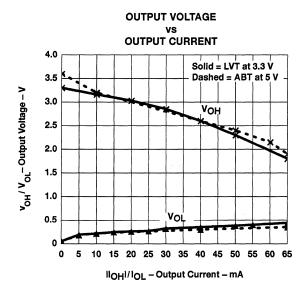

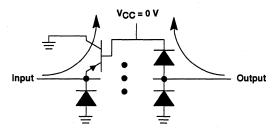

| 16-Bit Registered                   | 38     | ′16646 |          |    |   |          |     | ~  | ~     |     | ~   | ~   |    | +   | +    |