## Low-Voltage Logic ALB, ALVC, LV, LVC, LVT, LVTZ, and GTL Families

## Data Book

Low-Voltage Logic

ALB, ALVC, LV, LVC, LVT, LVTZ, and GTL Families

| General Information                    | 1  |

|----------------------------------------|----|

| ALB Widebus™                           | 2  |

| ALVC Widebus™                          | 3  |

| LVT Octals                             | 4  |

| LVTZ Octals: Power Up and 3 State      | 5  |

| LVT Widebus™                           | 6  |

| LVT JTAG/IEEE 1149.1                   | 7  |

| LVC MSI and Octals                     | 8  |

| LVC Widebus™                           | 9  |

| LV MSI and Octals                      | 10 |

| GTL Transceivers and Backplane Drivers | TE |

| Application Reports                    | 12 |

| Characteristics Information            | 13 |

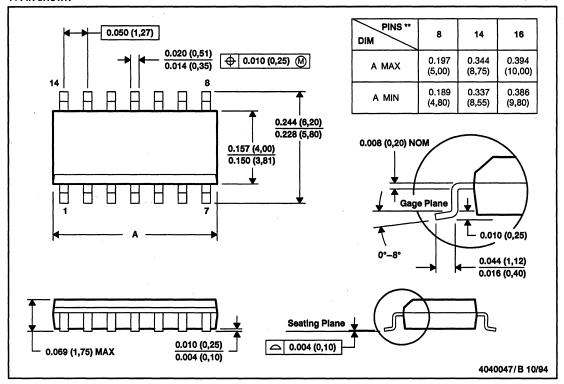

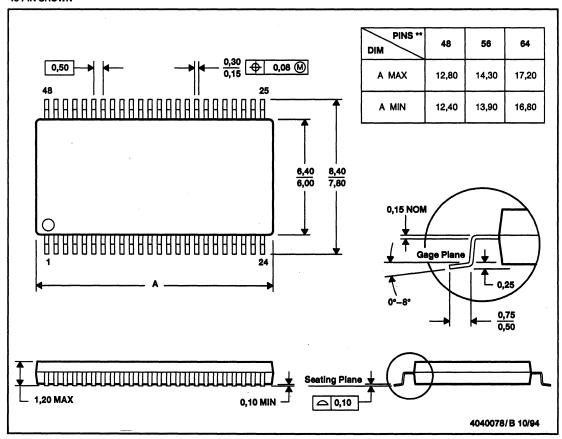

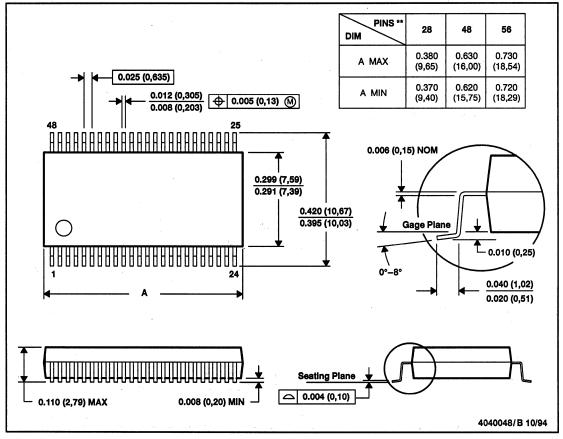

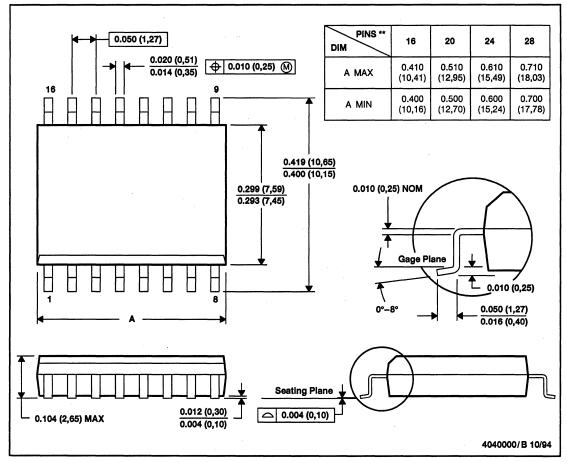

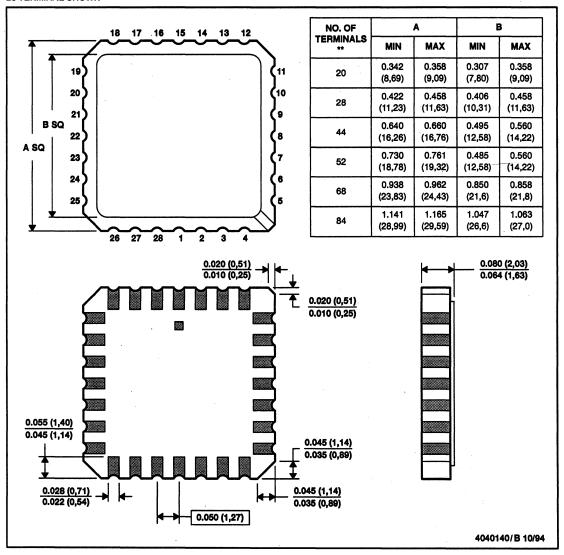

| Mechanical Data                        | 14 |

.

### Low-Voltage Logic Data Book

ALB, ALVC, LV, LVC, LVT, LVTZ, and GTL Families

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

#### INTRODUCTION

The 3.3-V era has arrived! The combination of continuous advancement in semiconductor wafer fabrication technologies and the proliferation of battery-powered computing devices has changed system-design methodologies of the past, and indeed our entire industry. This new era brings a new set of possibilities for computing and hand-held instruments: products that run faster, consume less power, and use fewer total system components than ever before; products that are smaller and lighter, yet maintain interface compatibility with existing industry standard bus architectures; and products that will bring on the next era in the computer industry.

Welcome to the 1996 Texas Instruments Low-Voltage Logic Data Book. A single family of 3.3-V logic products could not possibly cover the diverse needs of all of the end-equipment segments. Products ranging from hand-held point-of-sale terminals, notebook and laptop personal computers, low-power environmentally conscious desktop computers and peripherals, and high-performance RISC and CISC workstation platforms share the need for low-voltage technology, but have radically different price, performance, and feature requirements for the logic they employ. As a response to these diverse needs, Texas Instruments has developed four independent logic families:

Advanced Low-Voltage CMOS (ALVC) Low-Voltage HCMOS (LV) Low-Voltage CMOS (LVC) Low-Voltage Technology (LVT)

These products span four generations of CMOS and BiCMOS process technologies and years of fine-pitch packaging and innovative circuit developments to deliver a set of products for each of these end-equipment segments. In addition to popular octal and Widebus™ bus-interface circuits, two of the families also include SSI and MSI logic functions to help streamline design and facilitate time to market.

Voltage translators are provided to bridge the gap between the 5-V and 3.3-V environments. In addition to the LVT family, the LVC family also is 5 V tolerant. This creates even more flexibility in the mixed-signal environments. Also new this year is the addition of the 2.5-V specification to the ALVC family. Designers of high-speed backplane applications will have great interest in the GTL family of transceivers.

Some of the information in this data book is in product-preview or advance-information form. For more information on these products including availability dates, pricing, and final timing specifications, please contact your local Texas Instruments field sales representative, authorized distributor, or call our Advanced System Logic hotline at (903) 868-5202.

We are sure you will agree that Texas Instruments has developed the most complete line of low-voltage logic products in the industry. We hope that these products will meet your system and design needs. Texas Instruments has been and will continue to be the logic leader for bus-interface products.

OEC, SCOPE, UBE, UBT, Widebus, and Widebus+ are trademarks of Texas Instruments Incorporated.

#### PRODUCT STAGE STATEMENTS

Product stage statements are used on Texas Instruments data sheets to indicate the development stage(s) of the product(s) specified in the data sheets.

If all products specified in a data sheet are at the same development stage, the appropriate statement from the following list is placed in the lower left corner of the first page of the data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

If not all products specified in a data sheet are at the PRODUCTION DATA stage, then the first statement below is placed in the lower left corner of the first page of the data sheet. Subsequent pages of the data sheet containing PRODUCT PREVIEW information or ADVANCE INFORMATION are then marked in the lower left-hand corner with the appropriate statement given below:

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

| General Information                    | 1  |

|----------------------------------------|----|

| ALB Widebus™                           | 2  |

| ALVC Widebus™                          | 3  |

| LVT Octals                             | 4  |

| LVTZ Octals: Power Up and 3 State      | 5  |

| LVT Widebus™                           | 6  |

| LVT JTAG/IEEE 1149.1                   | 7  |

| LVC MSI and Octals                     | 8  |

| LVC Widebus™                           | 9  |

| LV MSI and Octals                      | 10 |

| GTL Transceivers and Backplane Drivers | 11 |

| Application Reports                    | 12 |

| Characteristics Information            | 13 |

| Mechanical Data                        | 14 |

### Contents

|                                          | Page |

|------------------------------------------|------|

| Alphanumeric Index                       | 1–3  |

| Glossary                                 | 1–5  |

| Explanation of Function Tables           | 1–9  |

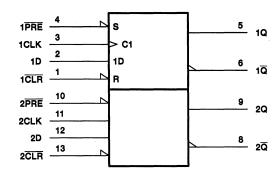

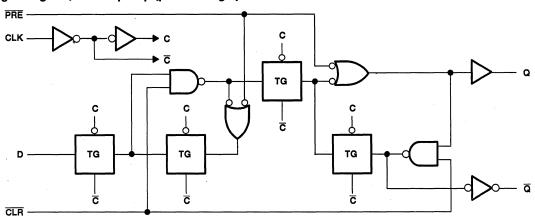

| D Flip-Flop and Latch Signal Conventions | 1–11 |

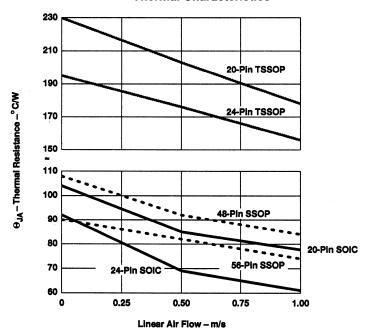

| Thermal Information                      |      |

| Functional Index                         | 1–15 |

#### **ALPHANUMERIC INDEX**

| DEVICE                                 | PAGE I | DEVICE                        | PAGE   |

|----------------------------------------|--------|-------------------------------|--------|

| ALB Widebus™                           |        | LV MSI and Octals (continued) |        |

| SN74ALB16244                           |        | SN74LV32                      | 10. 27 |

|                                        | 2-5    | SN74LV74                      |        |

| ALVC Widebus™                          |        | SN74LV125                     |        |

| SN74ALVC164245                         | j      | SN74LV138                     |        |

| SN74ALVCH16240                         |        | SN74LV164                     |        |

| SN74ALVCH16244                         |        | SN74LV165                     |        |

| SN74ALVCH16245                         |        | SN74LV174                     |        |

| SN74ALVCH16260                         | l l    | SN74LV240                     |        |

| SN74ALVCH16269                         |        | SN74LV244                     |        |

| SN74ALVCH16270                         |        | SN74LV245                     |        |

| SN74ALVCH16271                         |        | SN74LV273                     |        |

| SN74ALVCH16272                         |        | SN74LV373                     |        |

| SN74ALVCH16344                         |        | SN74LV374                     |        |

| SN74ALVCH16373                         |        | SN74LV573                     | 10-87  |

| SN74ALVOH46400                         |        | SN74LV574                     | 10-91  |

| SN74ALVOL46500                         | 3      | SN74LVU04                     | 10-15  |

| SN74ALVCH16500                         |        | LVO NOL d O-d-l-              |        |

| SN74ALVCH16501                         |        | LVC MSI and Octals            | 0.5    |

| SN74ALVCH16525                         |        | SN74LVC00                     |        |

| SN74ALVCH16543                         |        | SN74LVC02<br>SN74LVC04        |        |

|                                        |        |                               |        |

| SN74ALVOU46646                         |        | SN74LVC08                     |        |

| SN74ALVCH16646                         |        | SN74LVC10                     |        |

| SN74ALVCH16052                         |        | SN74LVC32                     |        |

|                                        |        |                               |        |

| SN74ALVCH16820                         |        | SN74LVC74<br>SN74LVC86        |        |

| SN74ALVCH16821                         |        | SN74LVC86                     |        |

| SN74ALVOH16825                         |        | SN74LVC112                    |        |

| SN74ALVCH16827                         | 1      | SN74LVC126                    |        |

| SN74ALVCH16827                         |        | SN74LVC126                    |        |

| SN74ALVCH16841                         | 1      | SN74LVC138                    |        |

| SN74ALVCH16843                         |        | SN74LVC138                    |        |

| SN74ALVCH16901                         |        | SN74LVC157                    |        |

| SN74ALVCH16952                         |        | SN74LVC158                    |        |

| SN74ALVCH162268                        |        | SN74LVC240                    |        |

| SN74ALVCH162525                        |        | SN74LVC241                    |        |

| SN74ALVCH162601                        |        | SN74LVC244A                   |        |

| SN74ALVCH162820                        |        | SN74LVC245A                   |        |

| SN74ALVCH162827                        | 1      | SN74LVC257                    |        |

| SN74ALVCHR162269                       | 1      | SN74LVC258                    |        |

| SN74ALVCHR162409                       | 1      | SN74LVC373A                   |        |

|                                        | 0 100  | SN74LVC374A                   |        |

| GTL Transceivers and Backplane Drivers |        | SN74LVC540                    |        |

| SN54GTL16612 SN74GTL16612              | i      | SN74LVC541                    |        |

| SN54GTL16616 SN74GTL16616              | ,      | SN74LVC543                    |        |

| SN54GTL16622 SN74GTL16622              | 1      | SN74LVC544                    |        |

| SN54GTL16921 SN74GTL16921              | 11–25  | SN74LVC573A                   |        |

| LV MSI and Octals                      | ļ      | SN74LVC574A                   |        |

| SN74LV00                               | . 10–3 | SN74LVC646                    |        |

| SN74LV02                               |        | SN74LVC652                    |        |

| SN74LV04                               | 10–11  | SN74LVC821                    |        |

| SN74LV08                               |        | SN74LVC823                    |        |

| SN74LV14                               | 10–23  | SN74LVC827                    |        |

#### **ALPHANUMERIC INDEX**

| DEVICE         PAGE           LVC MSI and Octals (continued)         8-195           SN74LVC828         8-199           SN74LVC841         8-199           SN74LVC843         8-203           SN74LVC861         8-207           SN74LVC863         8-211           SN74LVC2952         8-215           SN74LVC4245         8-109           SN74LVCH244         8-93           SN74LVCH245         8-103           SN74LVCH245         8-103           SN74LVCH6246         9-3           SN74LVC16240         9-3           SN74LVC16241         9-7           SN74LVC16244A         9-11           SN74LVC16245A         9-29           SN74LVC16373         9-47           SN74LVC16374         9-53           SN74LVC16540         9-59           SN74LVC16541         9-63           SN74LVC16540         9-59           SN74LVC16540         9-59           SN74LVC16540         9-59           SN74LVC16540         9-59           SN74LVC16540         9-63           SN74LVC16540         9-63           SN74LVC16540         9-75           SN74LVC16540 <t< th=""><th></th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                                         |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------|--------|

| SN74LVC828       8-195         SN74LVC841       8-199         SN74LVC843       8-203         SN74LVC861       8-207         SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVCH244       9-3         SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16244A       9-11         SN74LVC16245A       9-29         SN74LVC16373       9-47         SN74LVC16540       9-53         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16543       9-67         SN74LVC16654       9-75         SN74LVC16952       9-83         SN74LVC16952       9-83         SN74LVC16952       9-93         SN74LVC16245       9-21         LVT JAG/IEEE 1149.1       SN54LVT18245       7-3         SN54LVT18640       SN74LVT18652       7-3         SN54LVT18666                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DEVICE               | •                                       | PAGE   |

| SN74LVC841       8-199         SN74LVC843       8-203         SN74LVC861       8-207         SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16245A       9-11         SN74LVC16245A       9-29         SN74LVC16373       9-47         SN74LVC16540       9-53         SN74LVC16540       9-53         SN74LVC16540       9-53         SN74LVC16540       9-63         SN74LVC16540       9-67         SN74LVC16540       9-67         SN74LVC16540       9-75         SN74LVC16540       9-75         SN74LVC16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LVC MSI and Octals ( | continued)                              |        |

| SN74LVC843       8-203         SN74LVC861       8-207         SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16245A       9-11         SN74LVC1624AA       9-11         SN74LVC16373       9-47         SN74LVC16374       9-59         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16544       9-67         SN74LVC16654       9-75         SN74LVC16654       9-75         SN74LVC16654       9-75         SN74LVC16952       9-83         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVC162244       9-23         SN74LVT18245       N74LVT18502         SN54LVT18245       SN74LVT18504       7-3         SN54LVT18640       SN74LVT18504       7-3         SN54LVT18650                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SN74LVC828           |                                         | 8-195  |

| SN74LVC861       8-207         SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVCH245       8-17         LVC Widebus™       SN74LVC16240         SN74LVC16241       9-7         SN74LVC16245A       9-11         SN74LVC16245A       9-29         SN74LVC16373       9-47         SN74LVC16374       9-53         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-63         SN74LVC16654       9-75         SN74LVC16654       9-75         SN74LVC16654       9-75         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVC162244       9-23         SN74LVC162244       9-23         SN74LVC162245       9-35         SN74LVT18244       9-1         LVT JAG/IEEE 1149.1       SN54LVT18245       7-3         SN54LVT18640       S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SN74LVC841           |                                         | 8-199  |

| SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC1624A       9-11         SN74LVC16373       9-47         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-63         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC16652       9-93         SN74LVC16244A       9-17         SN74LVCH6245A       9-23         SN74LVCH6244A       9-17         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVT18245       SN74LVT18260         SN74LVT18264       7-3         SN74LVT18264       7-3         SN54LVT18264       SN74LVT18264         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182645                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SN74LVC843           |                                         | 8-203  |

| SN74LVC863       8-211         SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH245       8-103         SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC1624A       9-11         SN74LVC16373       9-47         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-63         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC16652       9-93         SN74LVC16244A       9-17         SN74LVCH6245A       9-23         SN74LVCH6244A       9-17         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVCH6245A       9-35         SN74LVT18245       SN74LVT18260         SN74LVT18264       7-3         SN74LVT18264       7-3         SN54LVT18264       SN74LVT18264         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182645                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SN74LVC861           |                                         | 8-207  |

| SN74LVC2952       8-215         SN74LVC4245       8-109         SN74LVCH244       8-93         SN74LVCH245       8-103         SN74LVCH246       8-17         LVC Widebus™       SN74LVC16240         SN74LVC16241       9-3         SN74LVC16245A       9-11         SN74LVC16373       9-47         SN74LVC16540       9-59         SN74LVC16541       9-59         SN74LVC16543       9-67         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC16652       9-93         SN74LVC16652       9-93         SN74LVC162244       9-23         SN74LVC162245       9-35         SN74LVCH16244A       9-17         SN74LVCH16245A       9-35         SN74LVCH16245A       9-35         SN74LVT18265       7-3         SN74LVT18640       7-3         SN74LVT18640       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT182661       SN74LVT182640       7-3         SN54LVT182662       SN74LVT182640       7-3         SN54LVT182663       SN74LVT182640                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |                                         |        |

| SN74LVC4245       8–109         SN74LVCH244       8–93         SN74LVCH245       8–103         SN74LVCU04       8–17         LVC Widebus™       SN74LVC16240         SN74LVC16241       9–3         SN74LVC16244A       9–11         SN74LVC16245A       9–29         SN74LVC16373       9–47         SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16646       9–75         SN74LVC16652       9–83         SN74LVC16652       9–83         SN74LVC16652       9–83         SN74LVC166244       9–23         SN74LVC162244       9–23         SN74LVCH16245A       9–35         SN74LVCH16245A       9–35         SN74LVC162244       9–23         SN74LVC162245       9–31         LVT JTAG/IEEE 1149.1       NYALVT18604       7–3         SN54LVT18245       NYALVT18604       7–3         SN54LVT18646       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18650       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                                         |        |

| SN74LVCH244 8-93 SN74LVCH245 8-103 SN74LVCU04 8-17  LVC Widebus™ SN74LVC16240 9-3 SN74LVC16241 9-7 SN74LVC16245A 9-11 SN74LVC16245A 9-11 SN74LVC16373 9-47 SN74LVC16540 9-59 SN74LVC16540 9-59 SN74LVC16540 9-63 SN74LVC16541 9-63 SN74LVC16543 9-67 SN74LVC166543 9-67 SN74LVC16652 9-83 SN74LVC16652 9-83 SN74LVC16652 9-93 SN74LVC165244 9-23 SN74LVC16244A 9-17 SN74LVC16244A 9-17 SN74LVCH16245A 9-35 SN74LVCH16245A 9-35 SN74LVCH16245A 9-35 SN74LVCH16245A 9-35 SN74LVCH16245A 9-35 SN74LVCH16245A 9-35 SN74LVT18245 SN74LVT18245 7-3 SN54LVT18245 SN74LVT18640 7-3 SN54LVT18646 SN74LVT18640 7-3 SN54LVT18652 SN74LVT18640 7-3 SN54LVT18652 SN74LVT18646 7-3 SN54LVT18245 SN74LVT18640 7-3 SN54LVT182640 SN74LVT18652 7-3 SN54LVT182640 SN74LVT182640 7-3 SN54LVT182652 SN74LVT182640 7-3 SN54LVT182652 SN74LVT182660 7-3 SN54LVT182652 SN74LVT182664 7-3 SN54LVT182653 SN74LVT182664 7-3 SN54LVT182654 SN74LVT182664 7-3 SN54LVT182655 SN74LVT182665 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182665 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182660 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182665 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182665 7-3 SN54LVT182650 SN74LVT182664 7-3 SN54LVT182650 SN74LVT182665 7-3 SN54LVT182660 SN74LVT182664 7-3 SN54LVT182660 SN74LVT182660 7-3 |                      |                                         |        |

| SN74LVCH245       8–103         SN74LVCU04       8–17         LVC Widebus™       SN74LVC16240       9–3         SN74LVC16241       9–7         SN74LVC16245A       9–11         SN74LVC16373       9–47         SN74LVC16574       9–53         SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16646       9–75         SN74LVC16652       9–83         SN74LVC16652       9–83         SN74LVC16652       9–83         SN74LVC162244       9–23         SN74LVCH162245       9–35         SN74LVCH162245       9–35         SN74LVCH162245       9–35         SN74LVCH162245       9–31         LVT JTAG/IEEE 1149.1       SN54LVT18245       7–3         SN54LVT18245       SN74LVT18245       7–3         SN74LVT18640       N74LVT182640       7–3         SN54LVT18662       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                                         |        |

| SN74LVCU04       8-17         LVC Widebus™       SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16245A       9-11         SN74LVC16373       9-47         SN74LVC16540       9-53         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC16652       9-93         SN74LVC1662244       9-23         SN74LVCH16245A       9-17         SN74LVCH16245A       9-35         SN74LVCH16245       9-35         SN74LVCH16245       9-35         SN74LVT18245       7-3         SN74LVT18640       SN74LVT18502       7-3         SN54LVT18646       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT18265       SN74LVT182502       7-3         SN54LVT182640       SN74LVT182504       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182640       SN7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                                         |        |

| LVC Widebus™       SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16244A       9-11         SN74LVC16245A       9-29         SN74LVC16373       9-47         SN74LVC16540       9-53         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC166543       9-67         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVCH16244A       9-17         SN74LVCH16245A       9-35         SN74LVCH16245A       9-35         SN74LVT18245       SN74LVT18502       7-3         SN54LVT18245       SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18646       7-3         SN54LVT182504       SN74LVT182645       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182652                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |                                         |        |

| SN74LVC16240       9-3         SN74LVC16241       9-7         SN74LVC16244A       9-11         SN74LVC16373       9-29         SN74LVC16374       9-53         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC162244       9-23         SN74LVCH16244A       9-17         SN74LVCH16245A       9-35         SN74LVCH16245       9-35         SN74LVT18245       SN74LVT18502       7-3         SN54LVT18640       SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18640       7-3         SN54LVT182245       SN74LVT182640       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT240       SN74LVT240       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3N/4LVC004           | • • • • • • • • • • • • • • • • • • • • | . 0-17 |

| SN74LVC16241       9-7         SN74LVC16244A       9-11         SN74LVC16245A       9-29         SN74LVC16373       9-47         SN74LVC16540       9-53         SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16654       9-75         SN74LVC16652       9-83         SN74LVC16652       9-83         SN74LVC162244       9-23         SN74LVCH1624AA       9-17         SN74LVCH16245A       9-35         SN74LVCH16245A       9-35         SN74LVT18245       SN74LVT18502       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT18245       SN74LVT18652       7-3         SN54LVT182646       SN74LVT182504       7-3         SN54LVT182645       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182646       7-3         SN54LVT182646       SN74LVT182646       7-3         SN54LVT182645       SN74LVT182646       7-3         SN54LVT182652                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LVC Widebus™         |                                         |        |

| SN74LVC16244A       9–11         SN74LVC16245A       9–29         SN74LVC16373       9–47         SN74LVC16540       9–53         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16646       9–75         SN74LVC16652       9–83         SN74LVC16652       9–83         SN74LVC16652       9–35         SN74LVC162244       9–23         SN74LVCH16245A       9–17         SN74LVCH16245A       9–35         SN74LVCH16245A       9–35         SN74LVT18245       SN74LVT18502       7–3         SN54LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18646       7–3         SN54LVT18652       SN74LVT18646       7–3         SN54LVT182245       SN74LVT182502       7–3         SN54LVT182640       SN74LVT182504       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182646       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182646       7–3         SN54LVT182640       SN74LVT182646       7–3         SN54LVT182652       SN74LVT182646       7–3         SN54LVT125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SN74LVC16240         |                                         | 9–3    |

| SN74LVC16245A       9–29         SN74LVC16373       9–47         SN74LVC16374       9–53         SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC166543       9–67         SN74LVC166546       9–75         SN74LVC16652       9–83         SN74LVC16952       9–93         SN74LVC16952       9–35         SN74LVCH16244A       9–17         SN74LVCH16245A       9–35         SN74LVCH16245       9–35         SN74LVT18245       7–3         SN74LVT18502       7–3         SN74LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18640       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182650       SN74LVT182504       7–3         SN54LVT182640       SN74LVT182504       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182646       SN74LVT182646       7–3         SN54LVT182646       SN74LVT182640       7–3         SN54LVT182662       SN74LVT182666       7–3         SN54LVT182644       SN74LVT182666       7–3         SN54LVT125       A-3      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SN74LVC16241         |                                         | 9–7    |

| SN74LVC16373       9-47         SN74LVC16374       9-53         SN74LVC16540       9-59         SN74LVC16541       9-63         SN74LVC16643       9-67         SN74LVC166543       9-67         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC16952       9-93         SN74LVCH16244A       9-17         SN74LVCH16245A       9-35         SN74LVCH16245       9-35         SN74LVT18245       7-3         SN74LVT18502       7-3         SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182645       SN74LVT182646       7-3         SN54LVT182640       SN74LVT182504       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182640       7-3         SN54LVT182662       SN74LVT182662       7-3         SN54LVT182662       SN74LVT182666       7-3         SN54LVT125       4-3         SN54LVT124       SN74LVT244       4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SN74LVC16244A.       |                                         | . 9–11 |

| SN74LVC16374       9–53         SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16654       9–75         SN74LVC16652       9–83         SN74LVC16952       9–93         SN74LVC162244       9–23         SN74LVCH16245A       9–35         SN74LVCH16245       9–35         SN74LVCH16245       9–31         LVT JTAG/IEEE 1149.1       SN74LVT18502       7–3         SN54LVT18245       SN74LVT18502       7–3         SN54LVT18640       SN74LVT18640       7–3         SN54LVT18652       SN74LVT18646       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182640       SN74LVT182652       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182662       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT125       A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SN74LVC16245A.       |                                         | . 9–29 |

| SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16646       9–75         SN74LVC16652       9–83         SN74LVC16952       9–93         SN74LVC162244       9–23         SN74LVCH16245A       9–35         SN74LVCH16245       9–35         SN74LVCH16245       9–41         LVT JTAG/IEEE 1149.1       SN74LVT18502       7–3         SN54LVT18245       SN74LVT18502       7–3         SN74LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18646       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182245       SN74LVT182245       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT125       A–3         SN54LVT240       SN74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SN74LVC16373         |                                         | . 9–47 |

| SN74LVC16540       9–59         SN74LVC16541       9–63         SN74LVC16543       9–67         SN74LVC16646       9–75         SN74LVC16652       9–83         SN74LVC16952       9–93         SN74LVC162244       9–23         SN74LVCH16245A       9–35         SN74LVCH16245       9–35         SN74LVCH16245       9–41         LVT JTAG/IEEE 1149.1       SN74LVT18502       7–3         SN54LVT18245       SN74LVT18502       7–3         SN74LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18646       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182245       SN74LVT182245       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182640       SN74LVT182640       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT182652       SN74LVT182660       7–3         SN54LVT125       A–3         SN54LVT240       SN74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SN74LVC16374         |                                         | . 9–53 |

| SN74LVC16541       9-63         SN74LVC16543       9-67         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVCH16245A       9-35         SN74LVCH16245A       9-35         SN74LVCR162245       9-41         LVT JTAG/IEEE 1149.1       SN74LVT18245       7-3         SN54LVT18245       SN74LVT18502       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18646       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182245       SN74LVT182245       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182640       7-3         SN54LVT182652       SN74LVT182662       7-3         LVT Octals       SN54LVT125       4-3         SN54LVT240       SN74LVT25       4-3         SN54LVT241       SN74LVT241       4-15         SN54LVT245       SN74LVT245A       4-21         SN54LVT245       SN74LVT245A       4-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                                         |        |

| SN74LVC16543       9-67         SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVCH16245A       9-35         SN74LVCH16245       9-35         SN74LVT18245       9-41         LVT JTAG/IEEE 1149.1       SN74LVT18502       7-3         SN54LVT18640       SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18646       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182245       SN74LVT182502       7-3         SN54LVT182640       SN74LVT182504       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT125       SN74LVT25       4-3         SN54LVT240       SN74LVT240       4-9         SN54LVT244       SN74LVT245A       4-21         SN54LVT245       SN74LVT245A       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                                         |        |

| SN74LVC16646       9-75         SN74LVC16652       9-83         SN74LVC16952       9-93         SN74LVC162244       9-23         SN74LVCH16244A       9-17         SN74LVCH16245       9-35         SN74LVCR162245       9-41         LVT JTAG/IEEE 1149.1       1         SN54LVT18245       SN74LVT18245       7-3         SN54LVT18640       SN74LVT18502       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18646       7-3         SN54LVT18652       SN74LVT18646       7-3         SN54LVT182245       SN74LVT182245       7-3         SN54LVT182504       SN74LVT182502       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182645       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT182640       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT125       SN74LVT182652       7-3         LVT Octals       SN74LVT125       4-3         SN54LVT240       SN74LVT240       4-9         SN54LVT244       SN74LVT245A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                                         |        |

| SN74LVC16652       9–83         SN74LVC16952       9–93         SN74LVC162244       9–23         SN74LVCH16244A       9–17         SN74LVCH16245A       9–35         SN74LVCR162245       9–41         LVT JTAG/IEEE 1149.1       1         SN54LVT18245       SN74LVT18245       7–3         SN74LVT18502       7–3         SN74LVT18504       7–3         SN54LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18652       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182245       SN74LVT182245       7–3         SN54LVT182504       SN74LVT182502       7–3         SN54LVT182664       SN74LVT182640       7–3         SN54LVT182664       SN74LVT182640       7–3         SN54LVT182664       SN74LVT182646       7–3         SN54LVT182662       SN74LVT182662       7–3         SN54LVT182662       SN74LVT182666       7–3         SN54LVT182662       SN74LVT182666       7–3         SN54LVT125       4–3         SN54LVT240       SN74LVT240       4–9         SN54LVT244       SN74LVT244       4–21         SN54LVT245 <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                                         |        |

| SN74LVC16952       9–93         SN74LVC162244       9–23         SN74LVCH16245A       9–17         SN74LVCH16245A       9–35         SN74LVCR162245       9–41         LVT JTAG/IEEE 1149.1       1         SN54LVT18245       SN74LVT18245       7–3         SN74LVT18502       7–3         SN74LVT18504       7–3         SN54LVT18640       SN74LVT18640       7–3         SN54LVT18652       SN74LVT18646       7–3         SN54LVT18652       SN74LVT18652       7–3         SN54LVT182245       SN74LVT182245       7–3         SN54LVT182504       SN74LVT182502       7–3         SN54LVT182504       SN74LVT182640       7–3         SN54LVT182646       SN74LVT182640       7–3         SN54LVT182646       SN74LVT182646       7–3         SN54LVT182646       SN74LVT182664       7–3         SN54LVT182652       SN74LVT182666       7–3         SN54LVT182652       SN74LVT182665       7–3         SN54LVT125       4–3         SN54LVT240       SN74LVT240       4–9         SN54LVT244       SN74LVT244       4–21         SN54LVT245       SN74LVT245A       4–27 <tr< td=""><td></td><td></td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                                         |        |

| SN74LVC162244       9–23         SN74LVCH16244A       9–17         SN74LVCH16245A       9–35         SN74LVCR162245       9–41         LVT JTAG/IEEE 1149.1       1         SN54LVT18245       SN74LVT18245       7–3         SN74LVT18502       7–3         SN74LVT18504       7–3         SN54LVT18640       SN74LVT18640       7–3         SN54LVT18646       SN74LVT18646       7–3         SN54LVT182245       SN74LVT18652       7–3         SN54LVT182245       SN74LVT182245       7–3         SN54LVT182604       SN74LVT182502       7–3         SN54LVT182604       SN74LVT182604       7–3         SN54LVT182646       SN74LVT182640       7–3         SN54LVT182665       SN74LVT182666       7–3         SN54LVT182652       SN74LVT182652       7–3         LVT Octals       SN74LVT125       4–3         SN54LVT240       SN74LVT240       4–9         SN54LVT244       SN74LVT241       4–15         SN54LVT245       SN74LVT245A       4–21         SN54LVT245       SN74LVT245A       4–27         SN54LVT243       SN74LVT245A       4–27         SN54LVT243       SN74LVT245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                                         |        |

| SN74LVCH16244A       9-17         SN74LVCH16245A       9-35         SN74LVCR162245       9-41         LVT JTAG/IEEE 1149.1       SN54LVT18245       7-3         SN54LVT18245       SN74LVT18502       7-3         SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18646       SN74LVT18646       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182245       SN74LVT182245       7-3         SN54LVT182504       SN74LVT182502       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182652       7-3         LVT Octals       SN74LVT182652       7-3         SN54LVT125       SN74LVT240       4-9         SN54LVT244       SN74LVT241       4-15         SN54LVT244       SN74LVT244A       4-21         SN54LVT273       SN74LVT245       4-3         SN54LVT543       SN74LVT543       4-39         SN54LVT573       SN74LVT543       4-39         SN54LVT574       SN74LVT574 <t< td=""><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                                         |        |

| SN74LVCH16245A       9-35         SN74LVCR162245       9-41         LVT JTAG/IEEE 1149.1       SN74LVT18245       7-3         SN54LVT18245       SN74LVT18502       7-3         SN74LVT18504       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182245       SN74LVT182502       7-3         SN54LVT182504       SN74LVT182504       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182646       7-3         SN54LVT182652       SN74LVT182665       7-3         SN54LVT182652       SN74LVT182666       7-3         SN54LVT182652       SN74LVT182652       7-3         LVT Octals       SN54LVT125       4-3         SN54LVT240       SN74LVT240       4-9         SN54LVT244       SN74LVT241       4-15         SN54LVT245       SN74LVT244A       4-21         SN54LVT273       SN74LVT243       4-27         SN54LVT273       SN74LVT253       4-33         SN54LVT543       SN74LVT543       4-39         SN54LVT573       SN74LVT573       4-47         SN54LVT574       SN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                                         |        |

| SN74LVCR162245       9-41         LVT JTAG/IEEE 1149.1         SN54LVT18245       7-3         SN74LVT18502       7-3         SN74LVT18604       7-3         SN54LVT18640       SN74LVT18640       7-3         SN54LVT18652       SN74LVT18652       7-3         SN54LVT182245       SN74LVT182502       7-3         SN54LVT182504       7-3         SN54LVT182640       SN74LVT182640       7-3         SN54LVT182646       SN74LVT182662       7-3         SN54LVT182662       SN74LVT182652       7-3         LVT Octals         SN54LVT125       4-3         SN54LVT125       4-3         SN54LVT240       SN74LVT125       4-3         SN54LVT241       SN74LVT241       4-15         SN54LVT244       SN74LVT244A       4-21         SN54LVT273       SN74LVT273       4-33         SN54LVT543       SN74LVT543       4-39         SN54LVT573       SN74LVT573       4-47         SN54LVT574       SN74LVT575       4-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                                         |        |

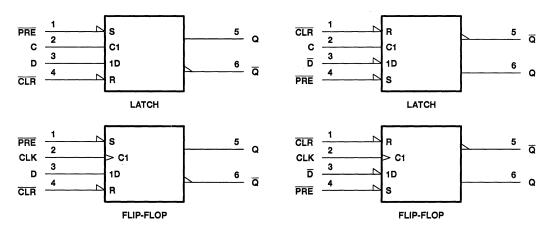

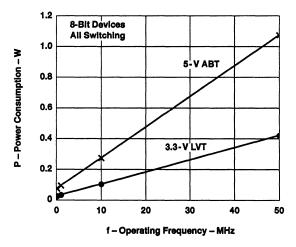

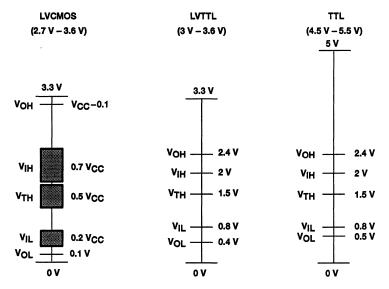

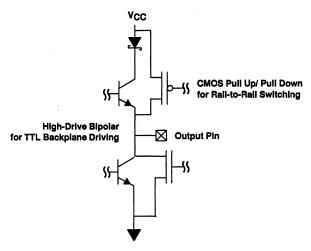

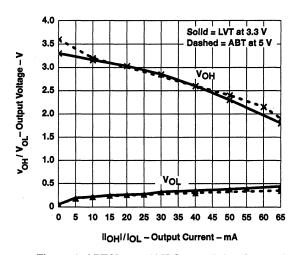

| LVT JTAG/IEEE 1149.1  SN54LVT18245 SN74LVT18245 7-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                                         |        |