X

## **TOSHIBA**

Static RAM/ Non-volatile Memory

1 9 9 6

DATA BOOK

# **TOSHIBA**

Static RAM Non-Volatile Memory 1996

#### Standard Static RAM

| Part Number  | Date   | Density | Organization | Package      | Features              | Lit. Number | Page Number |

|--------------|--------|---------|--------------|--------------|-----------------------|-------------|-------------|

| TC55257D-L   | . 7/95 | 256K    | 32K x 8      | P, F, FT     | Low Power             | SR25010795  | A-1         |

| TC55257DI-L  | . 9/95 | 256K    | 32K x 8      | P, F, FT     | Ind. Temp/Low Power   | SR25020995  | A-11        |

| TC55257DI-V  | 12/95  | 256K    | 32K x 8      | P, F, FT     | Ind. Temp/Low Voltage | SR25031295  | A-21        |

| TC55257D-V   | . 9/95 | 256K    | 32K x 8      | P, F, FT     | Low Voltage           | SR25040995  | A-33        |

| TC551001B    | . 7/95 | 1M      | 128K x 8     | P, F, FT, TR |                       | SR01010795  | A-45        |

| TC551001B-L  | . 7/95 | 1M      | 128K x 8     | P, F, FT.,TR | Low Power             | SR01020795  | A-57        |

| TC551001BI   | . 9/95 | 1M      | 128K x 8     | P, F, FT, TR | Industrial Temp       | SR01030994  | A-69        |

| TC551001BI-L | . 9/95 | 1M      | 128K x 8     | P, F, FT, TR | Ind. Temp/Low Power   | SR01040994  | A-81        |

| TC551001BI-V | . 2/95 | 1M      | 128K x 8     | P, F, FT, TR | Ind. Temp/Low Voltage | SR01050295  | A-93        |

| TC551001B-V  | . 7/95 | 1M      | 128K x 8     | P, F, FT, TR | Low Voltage           | SR01060795  | A-109       |

| TC554161     | . 7/95 | 4M      | 256K x 16    | FT           |                       | SR04010795  | A-123       |

| TC554161-L   | . 7/95 | 4M      | 256K x16     | FT           | Low Power             | SR04020795  | A-133       |

| TC554161I    | . 2/95 | 4M      | 256K x16     | FT           | Ind. Temp             | SR04030295  | A-143       |

| TC554161I-L  | . 2/95 | 4M      | 256K x16     | FT           | Ind. Temp/Low Power   | SR04040295  | A-153       |

| TC554161I-V  | 10/95  | 4M      | 256K x16     | FT           | Ind. Temp/Low Voltage | SR04051095  | A-163       |

| TC554161-V   | . 7/95 | 4M      | 256K x16     | FT           | Low Voltage           | SR04060795  | A-173       |

### **High Speed Static RAM**

| Part Number | Date    | Density | Organization | Package | Features       | Lit. Number | Page Number |

|-------------|---------|---------|--------------|---------|----------------|-------------|-------------|

| TC55V328A   | . 12/94 | 256K    | 32K x 8      | J       | 3.3V Operation | SR25011294  | B-1         |

| TC558128A   | 7/95    | 1M      | 128K x 8     | ل       |                | SR01010795  | B-9         |

| TC559128A   | 7/95    | 1.125M. | 128K x 9     | J       |                | SR01020795  | B-17        |

| TC551664A   | 8/95    | 1M      | 64K x 16     | J       |                | SR01030895  | B-25        |

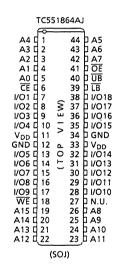

| TC551864A   | 7/95    | 1.125M. | 64K x 18     | J       |                | SR01040795  | B-33        |

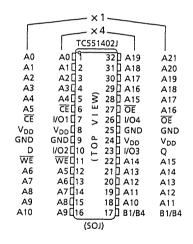

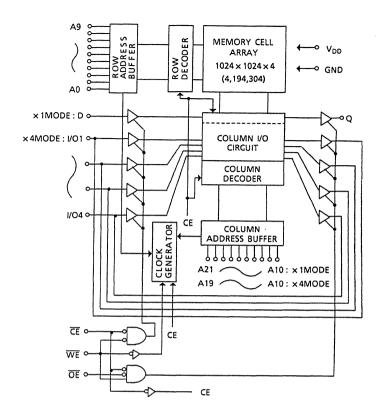

| TC551402    | 7/95    | 4M      | 1M x 4       | J       |                | SR04010995  | B-41        |

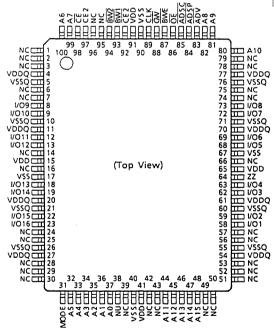

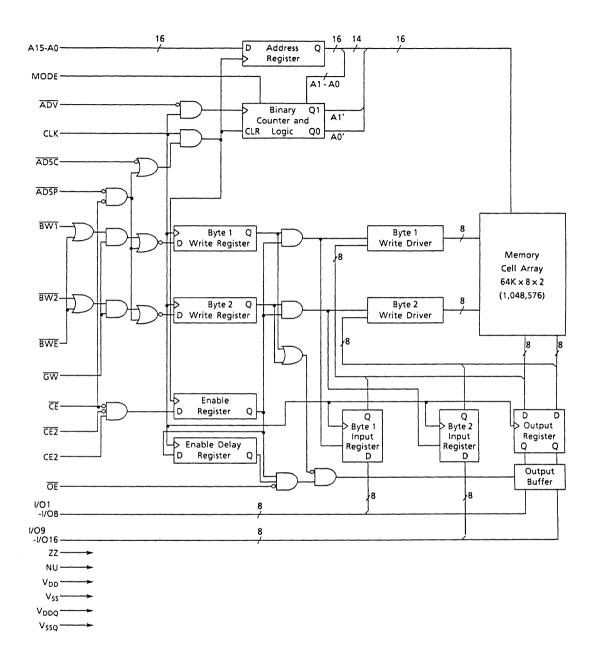

### **High Speed Synchronous RAM**

| Part Number | Date    | Density | Organization | Package | Features       | Lit. Number | Page Number |

|-------------|---------|---------|--------------|---------|----------------|-------------|-------------|

| TC55V1165   | . 12/95 | 1M      | 64K x 16     | FF      | 3.3V Operation | SR01011295  |             |

| TC55V1325   | . 12/95 | 1M      | 32K x 32     | FF      | 3.3V Operation | SR01021295  |             |

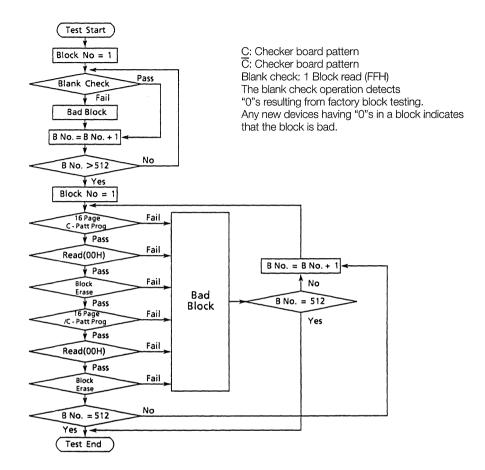

### Non-Volatile Memory

| Part Number | Date | Density | Organization  | Package | Features                         | Lit. Number  | Page Number |

|-------------|------|---------|---------------|---------|----------------------------------|--------------|-------------|

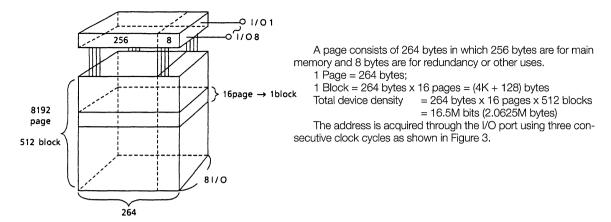

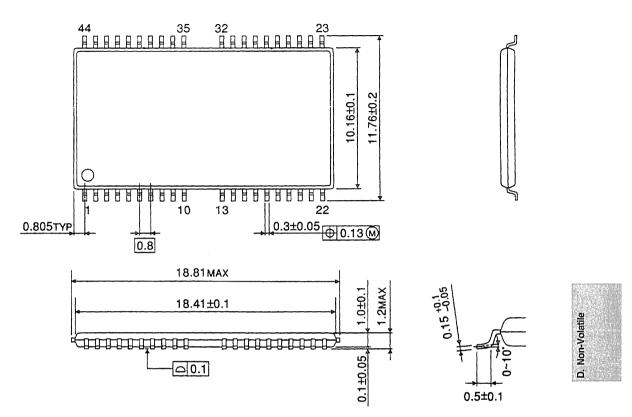

| TC58A040    | 1/96 | 4M      | 4M x 1        | SOP     | .Designed for audio applications | . NV04010196 | D-1         |

| TC5816AFT   | 1/96 | 16M     | 2M x 8        | TSOP II | Industrial temperature available | . NV16010196 | D-31        |

| TC5816ADC   | 3/96 | 16M     | 2M x 8        | SSFDC   | Solid state floppy disk          | . NV16030396 | D-69        |

| TC5832      | 1/96 | 32M     | $4M \times 8$ | TSOP II | 3.3V and 5V versions available   | NV32010196   | D-107       |

Package: P = Plastic DIP, F = Flat package (SOP), SP = Slim Plastic DIP, FW = Flat Wide package

FT = Forward bend TSOP, TR = Reverse bend TSOP, J = SOJ

Notes

## **Standard SRAM**

### TC55257DPL/DFL/DFTL-55L/70L/85L

PRELIMINARY

#### SILICON GATE CMOS

#### 32.768 WORD x 8 BIT STATIC RAM

#### Description

The TC55257DPL is a 262,144 bit static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mA/MHz (typ.) and a minimum cycle time of 55ns.

When  $\overline{CE}$  is a logical high, the device is placed in a low power standby mode in which the standby current is 0.3uA typically. The TC55257DPL has two control inputs. Chip Enable (CE) allows for device selection and data retention control, while an Output Enable input (OE) provides fast memory access. Thus the TC55257DPL is suitable for use in microprocessor application systems where high speed, low power, and battery backup are required.

The TC55257DPL is offered in a standard dual-in-line 28-pin plastic package (0.6 inch width), a small outline plastic package, and a thin small outline plastic package (forward type).

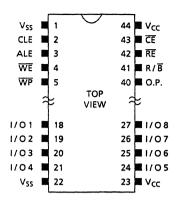

#### Pin Connection (Top View)

#### **Features**

• Low power dissipation: 27.5mW/MHz (typ.)

• Standby current:  $2\mu A$  (max.) at  $Ta = 25^{\circ}C$

• 5V single power supply

• Access time (max.)

|                | TC55 | TC55257DPL/DFL/DFTL |      |  |  |  |  |  |  |

|----------------|------|---------------------|------|--|--|--|--|--|--|

|                | -55L | -70L                | -85L |  |  |  |  |  |  |

| Access Time    | 55ns | 70ns                | 85ns |  |  |  |  |  |  |

| CE Access Time | 55ns | 70ns                | 85ns |  |  |  |  |  |  |

| OE Access Time | 30ns | 35ns                | 45ns |  |  |  |  |  |  |

• Power down feature:

• Data retention supply voltage:

$2.0 \sim 5.5V$

• Inputs and outputs directly TTL compatible

TC55257DPL Package

: DIP28-P-600

TC55257DFL

: SOP28-P-450

TC55257DFTL: TSOP28-P

### **Pin Names**

| Address Inputs           |

|--------------------------|

| Read/Write Control Input |

| Output Enable Input      |

| Chip Enable Input        |

| Data Input/Output        |

| Power (+5V)              |

| Ground                   |

|                          |

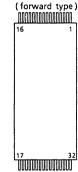

#### **TSOP Pinout**

| PIN NO.  | 1              | 2               | 3              | 4              | 5               | 6    | 7        | 8               | 9               | 10             | 11             | 12             | 13             | 14              |

|----------|----------------|-----------------|----------------|----------------|-----------------|------|----------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|

| PIN NAME | ŌĒ             | A <sub>11</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>13</sub> | R/W  | $V_{DD}$ | A <sub>14</sub> | A <sub>12</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>  |

| PIN NO.  | 15             | 16              | 17             | 18             | 19              | 20   | 21       | 22              | 23              | 24             | 25             | 26             | 27             | 28              |

| PIN NAME | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | I/O1           | 1/02            | I/O3 | GND      | 1/04            | 1/05            | 1/06           | I/O7           | I/O8           | CE             | A <sub>10</sub> |

| 0 | 28        | PIN                                | DIP 8          | SOP                          |

|---|-----------|------------------------------------|----------------|------------------------------|

|   |           | [] <sub>2</sub><br>[] <sub>3</sub> | 28<br>27<br>26 | V <sub>DD</sub><br>RW<br>A13 |

|   | <b>A6</b> |                                    | 25             | H A8                         |

|   |           | <u></u>                            | 24             | A9                           |

|   |           | 96                                 | 23             | <u> </u>                     |

|   | Α3        |                                    | 22             | OE                           |

|   | A2        |                                    | 21             | A10                          |

|   | A1        |                                    | 20             | CE                           |

|   |           | 9 10                               | 19             | 1/08                         |

|   | /01       |                                    | 18             | 1/07                         |

|   | /02       |                                    | 17             | 1/06                         |

|   | /03       |                                    | 16             | 1/05                         |

|   | GND       | 14                                 | 15             | 1/04                         |

o 28 PIN TSOP

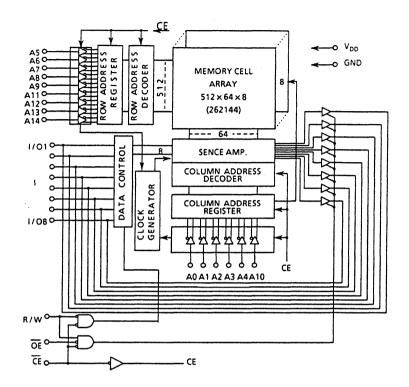

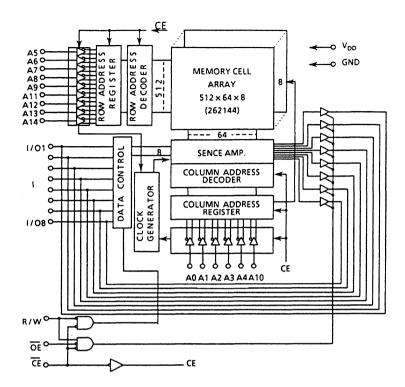

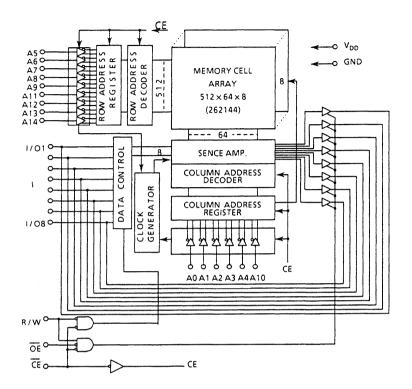

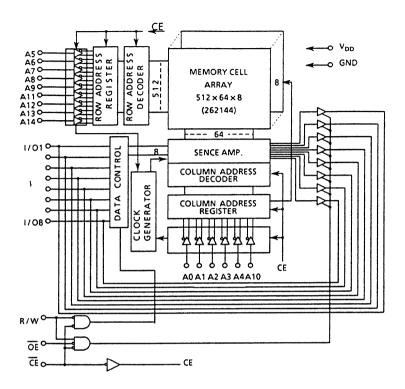

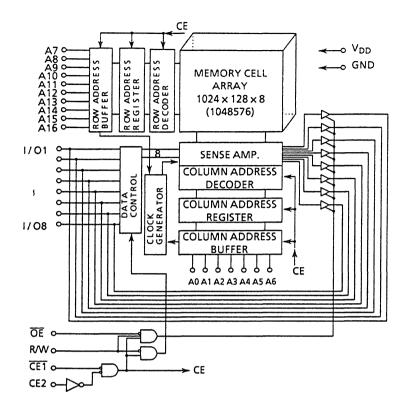

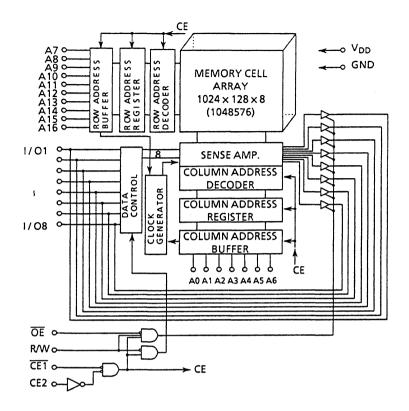

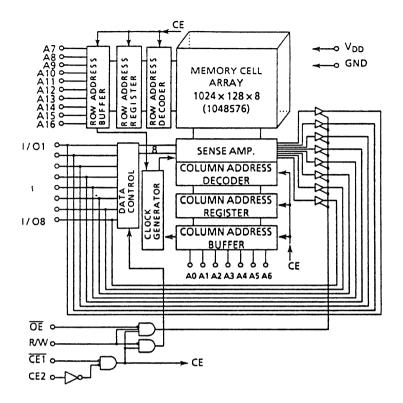

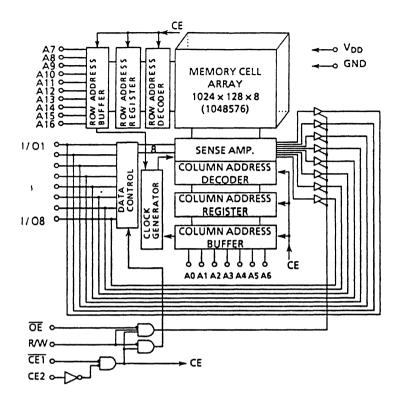

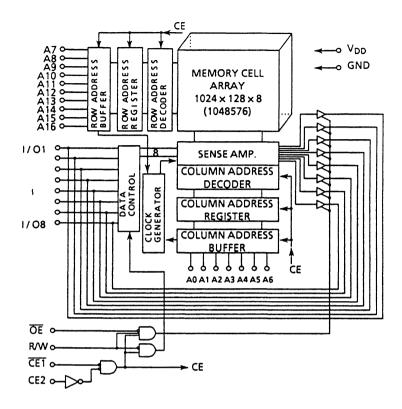

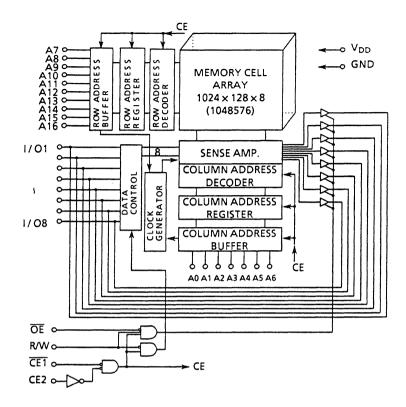

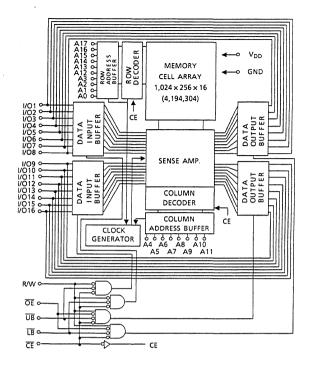

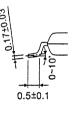

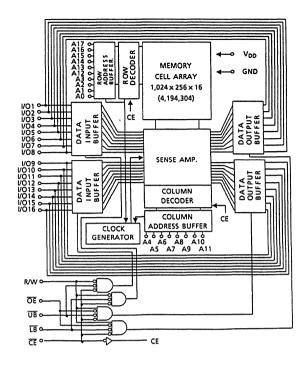

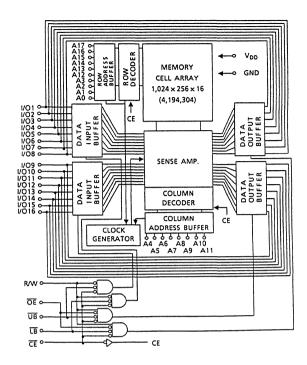

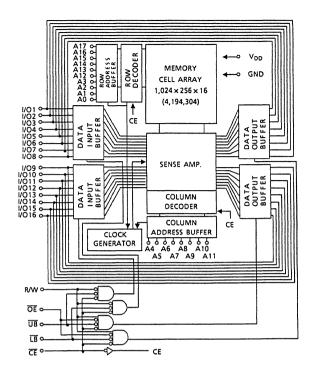

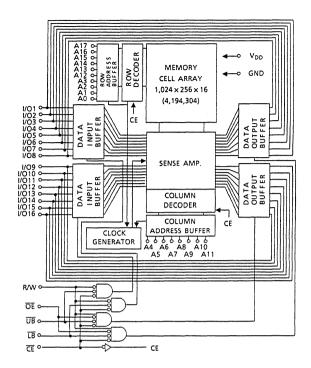

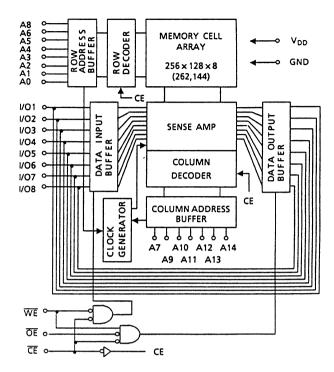

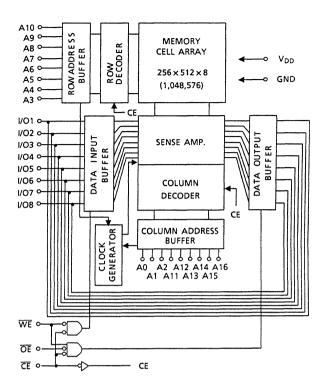

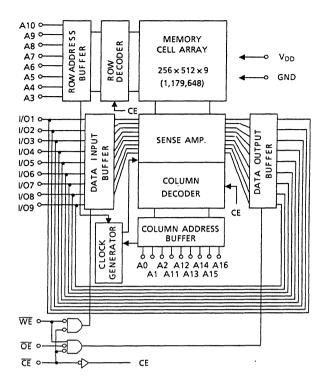

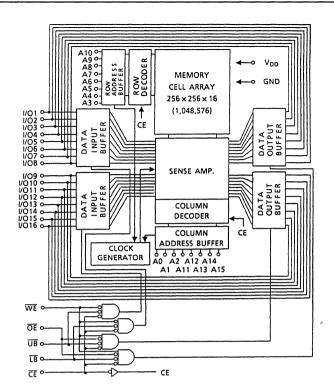

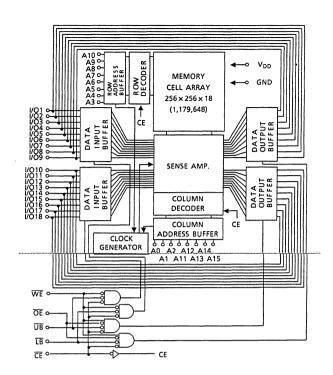

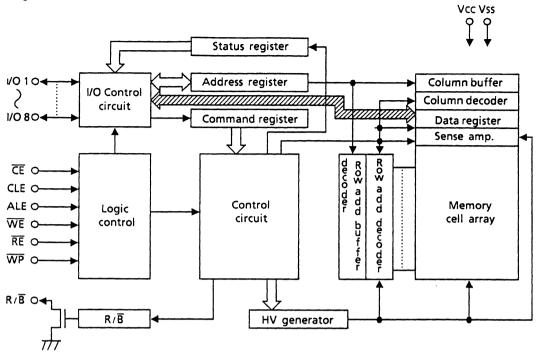

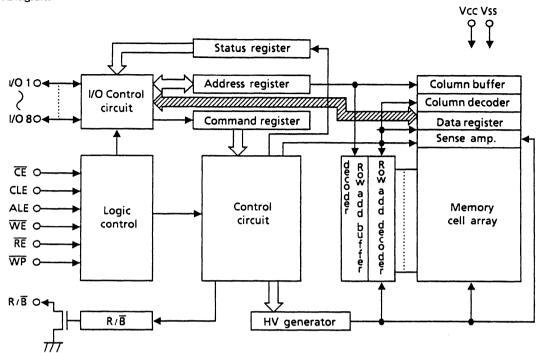

#### **Block Diagram**

### **Operating Mode**

| OPERATION MODE  | CE | ŌĒ | R/W | I/01 ~ I/08      | POWER            |

|-----------------|----|----|-----|------------------|------------------|

| Read            | L  | L  | Н   | D <sub>OUT</sub> | I <sub>DDO</sub> |

| Write           | L  | *  | L   | D <sub>IN</sub>  | I <sub>DDO</sub> |

| Output Deselect | L  | Н  | Н   | High-Z           | I <sub>DDO</sub> |

| Standby         | Н  | *  | *   | High-Z           | I <sub>DDS</sub> |

<sup>\*</sup> H or L

### **Maximum Ratings**

| SYMBOL              | ITEM                         | RATING                        | UNIT |

|---------------------|------------------------------|-------------------------------|------|

| V <sub>DD</sub>     | Power Supply Voltage         | -0.3 ~ 7.0                    | V    |

| V <sub>IN</sub>     | Input Voltage                | -0.3* ~ 7.0                   | ٧    |

| V <sub>I/O</sub>    | Input and Output Voltage     | -0.5* ~ V <sub>DD</sub> + 0.5 | V    |

| P <sub>D</sub>      | Power Dissipation            | 1.0/0.6**                     | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                           | °C   |

| T <sub>STRG</sub>   | Storage Temperature          | -55 ~ 150                     | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | 0 ~ 70                        | °C   |

<sup>\* -3.0</sup>V at pulse width 50ns

<sup>\*\*</sup> SOP

### **DC Recommended Operating Conditions**

| SYMBOL          | PARAMETER                     | MIN.  | TYP. | MAX.                  | UNIT |

|-----------------|-------------------------------|-------|------|-----------------------|------|

| V <sub>DD</sub> | Power Supply Voltage          | 4.5   | 5.0  | 5.5                   |      |

| V <sub>IH</sub> | Input High Voltage            | 2.2   | _    | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub> | Input Low Voltage             | -0.3* | _    | 0.8                   | V    |

| V <sub>DH</sub> | Data Retention Supply Voltage | 2.0   | -    | 5.5                   |      |

<sup>\* -3.0</sup>V at pulse width 50ns

| DC and 0          | OC and Operating Characteristics (Ta = 0 ~ 70°C, V <sub>DD</sub> = 5V±10%) |                                                                                                   |                                 |      |      |      |      |  |  |  |

|-------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|------|--|--|--|

| SYMBOL            | PARAMETER                                                                  | TEST CONDITION                                                                                    |                                 |      | TYP. | MAX. | UNIT |  |  |  |

| ILI               | Input Leakage Current                                                      | $V_{IN} = 0 \sim V_{DD}$                                                                          |                                 | -    | -    | ±1.0 | μА   |  |  |  |

| I <sub>LO</sub>   | Output Leakage Current                                                     | $\overline{CE} = V_{IH} \text{ or } R/W = V_{IL}$<br>$V_{OUT} = 0 \sim V_{DD}$                    | or $\overline{OE} = V_IH$       | _    | _    | ±1.0 | μА   |  |  |  |

| I <sub>OH</sub>   | Output High Current                                                        | V <sub>OH</sub> = 2.4V                                                                            |                                 | -1.0 | -    | -    | mA   |  |  |  |

| l <sub>OL</sub>   | Output Low Current                                                         | V <sub>OL</sub> = 0.4V                                                                            |                                 |      | _    | _    | mA   |  |  |  |

|                   |                                                                            | CE = V <sub>IL</sub>                                                                              | t <sub>cycle</sub> = 1μs        | 1    | 10   | _    |      |  |  |  |

| I <sub>DDO1</sub> |                                                                            | R/W = V <sub>IH</sub><br>Other Input = V <sub>IH</sub> /V <sub>IL</sub><br>I <sub>OUT</sub> = 0mA | t <sub>cycle</sub> = Min. cycle | 1    | -    | 70   |      |  |  |  |

|                   | Operating Current                                                          | <u>CE</u> = 0.2V                                                                                  | t <sub>cycle</sub> = 1μs        | 1    | 5    | _    | mA   |  |  |  |

| I <sub>DDO2</sub> |                                                                            | $R/W = V_{DD} - 0.2V$ Other Input $= V_{DD} - 0.2V/0.2V$ $I_{OUT} = 0mA$                          | t <sub>cycle</sub> = Min. cycle | 1    | _    | 60   |      |  |  |  |

| I <sub>DDS1</sub> |                                                                            | CE = V <sub>IH</sub>                                                                              |                                 | -    | _    | 3    | mA   |  |  |  |

| longe             | Standby Current                                                            | $\overline{CE} = V_{DD} - 0.2V$                                                                   | Ta = 0 ~ 70°C                   | -    | _    | 20   | μА   |  |  |  |

| I <sub>DDS2</sub> |                                                                            | V <sub>DD</sub> = 2.0V ~ 5.5V                                                                     | Ta = 25°C                       |      | 0.3  | 2    | μΑ   |  |  |  |

### Capacitance\* (Ta = 25°C, f = 1MHz)

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX. | UNIT |

|------------------|--------------------|------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = GND  | 10   | nE.  |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10   | рF   |

Note: This parameter is periodically sampled and is not 100% tested.

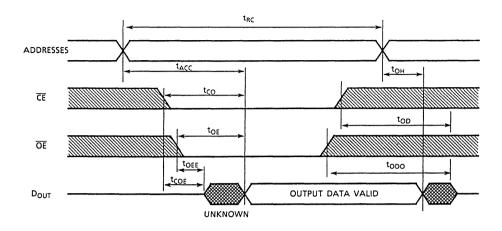

### AC Characteristics (Ta = 0 ~ $70^{\circ}$ C, $V_{DD}$ = $5V\pm10\%$ )

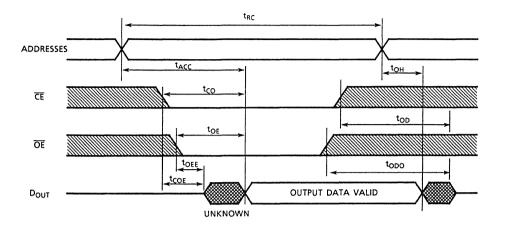

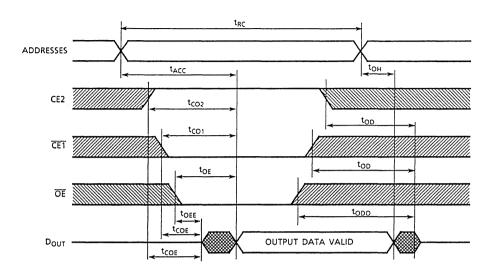

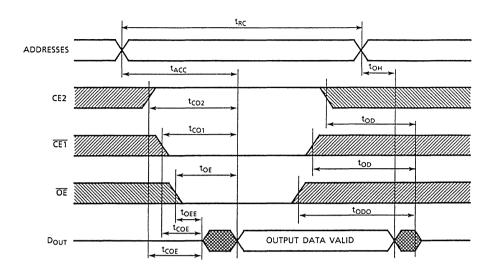

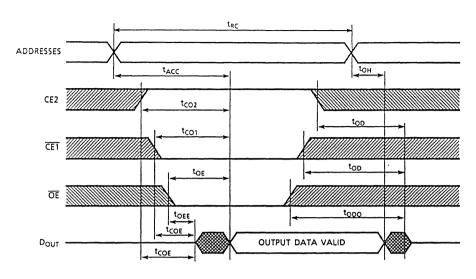

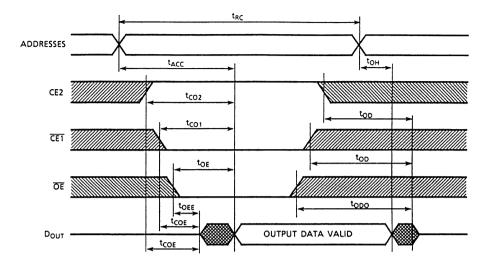

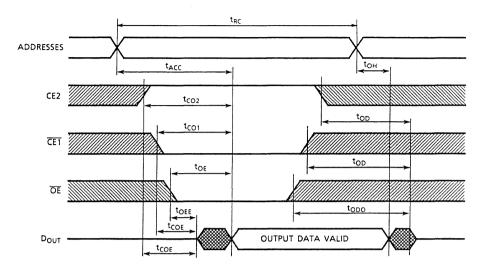

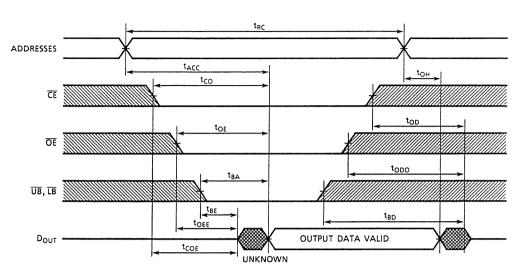

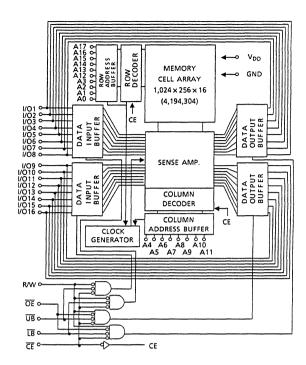

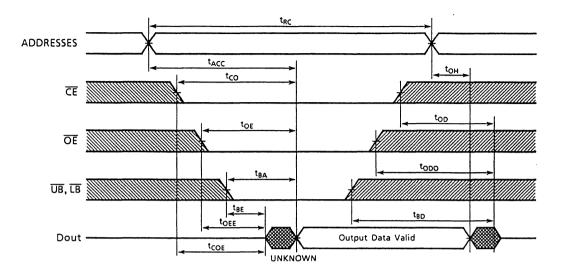

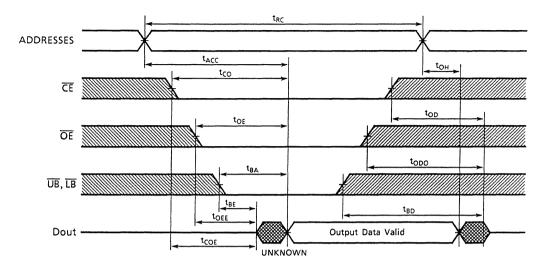

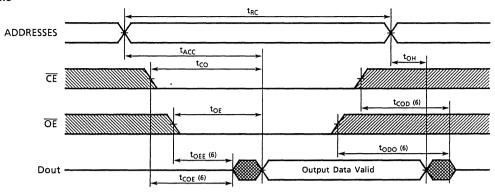

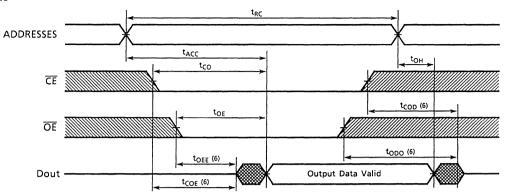

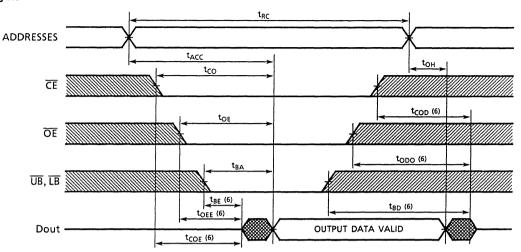

### **Read Cycle**

|                  |                                      | TC55257DPL/DFL/DFTL |      |      |      |      |      |      |  |

|------------------|--------------------------------------|---------------------|------|------|------|------|------|------|--|

| SYMBOL           | PARAMETER                            | -55L                |      | -70L |      | -85L |      | UNIT |  |

|                  |                                      | MIN.                | MAX. | MIN. | MAX. | MIN. | MAX. |      |  |

| t <sub>RC</sub>  | Read Cycle Time                      | 55                  | _    | 70   | -    | 85   | _    |      |  |

| t <sub>ACC</sub> | Address Access Time                  | _                   | 55   | _    | 70   | _    | 85   |      |  |

| t <sub>CO</sub>  | CE Access Time                       | -                   | 55   | _    | 70   | _    | 85   |      |  |

| t <sub>OE</sub>  | Output Enable to Output in Valid     | _                   | 30   | _    | 35   | _    | 45   |      |  |

| t <sub>COE</sub> | Chip Enable (CE) to Output in Low-Z  | 10                  | -    | 10   | _    | 10   | _    | ns   |  |

| t <sub>OEE</sub> | Output Enable to Output in Low-Z     | 5                   | -    | 5    | -    | 5    | _    |      |  |

| t <sub>OD</sub>  | Chip Enable (CE) to Output in High-Z | _                   | 20   | -    | 25   | _    | 30   |      |  |

| t <sub>ODO</sub> | Output Enable to Output in High-Z    | _                   | 20   | _    | 25   | _    | 30   |      |  |

| t <sub>OH</sub>  | Output Data Hold Time                | 10                  | -    | 10   | -    | 10   | _    |      |  |

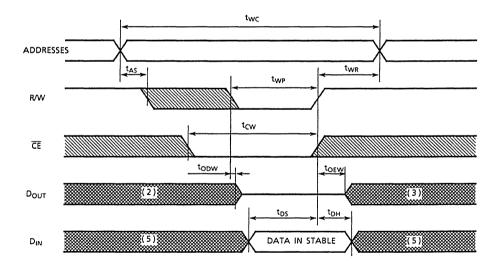

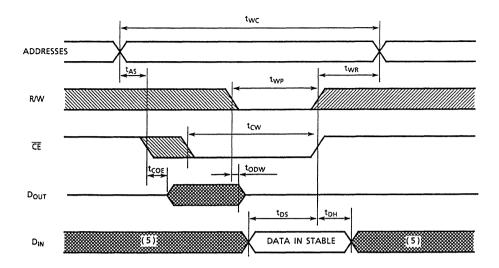

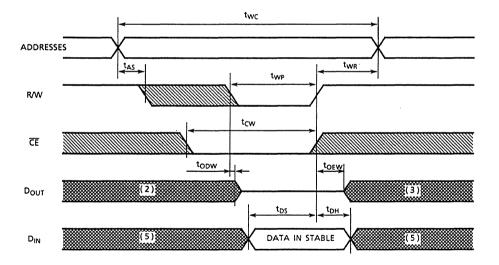

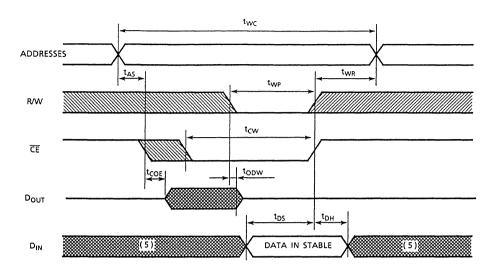

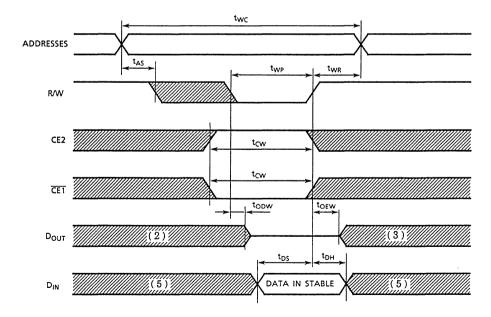

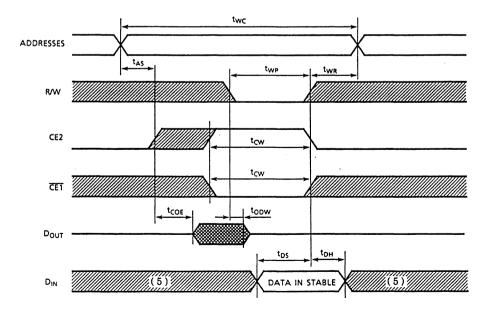

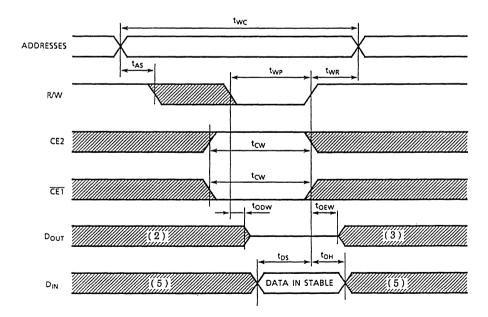

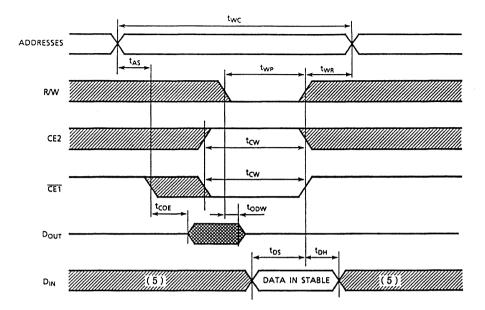

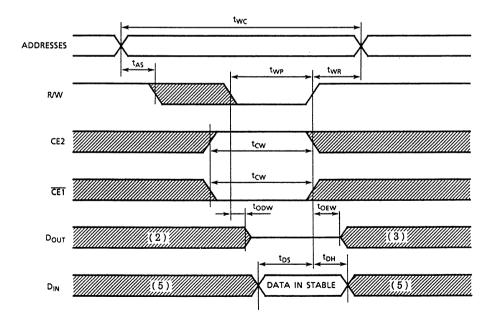

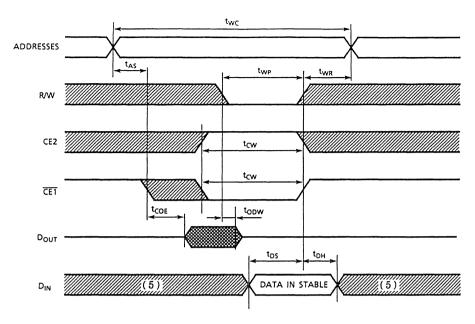

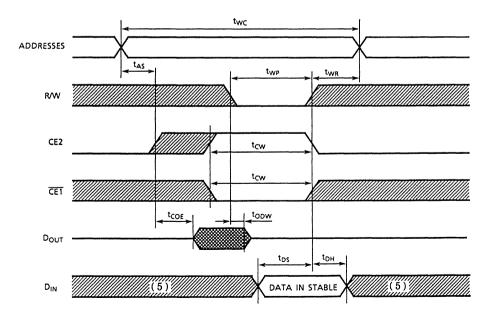

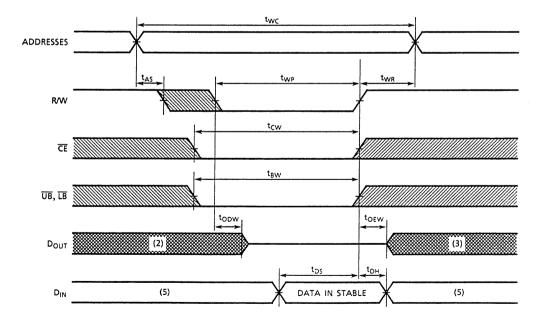

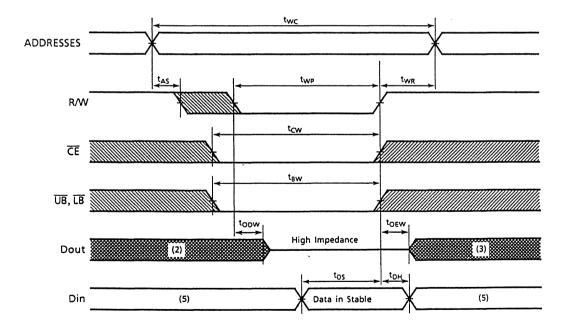

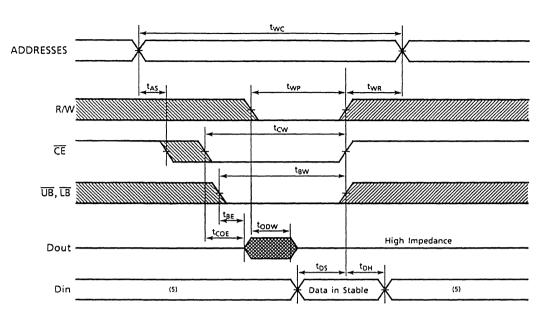

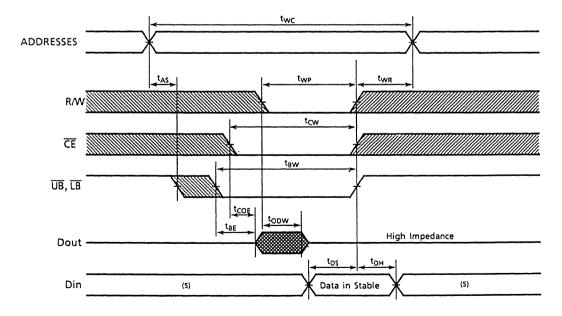

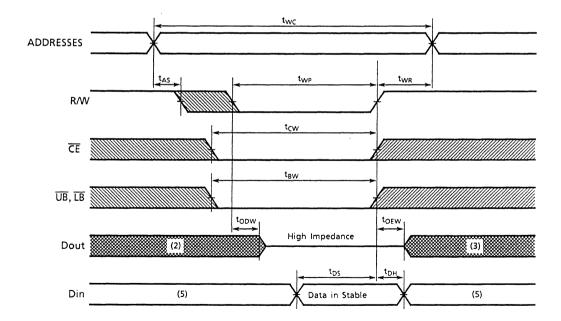

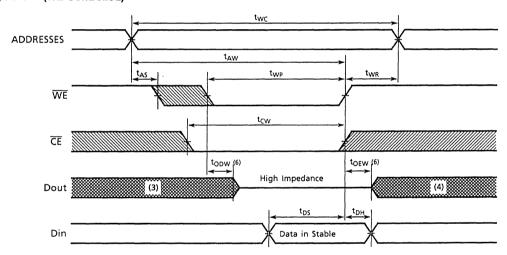

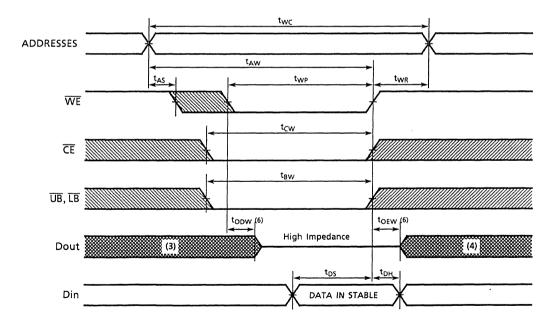

### **Write Cycle**

|                  |                                | TC55257DPL/DFLL |      |      |      |      |      |      |  |

|------------------|--------------------------------|-----------------|------|------|------|------|------|------|--|

| SYMBOL           | PARAMETER                      | -5              | 5L   | -7   | OL   | -85L |      | UNIT |  |

|                  |                                | MIN.            | MAX. | MIN. | MAX. | MIN. | MAX. |      |  |

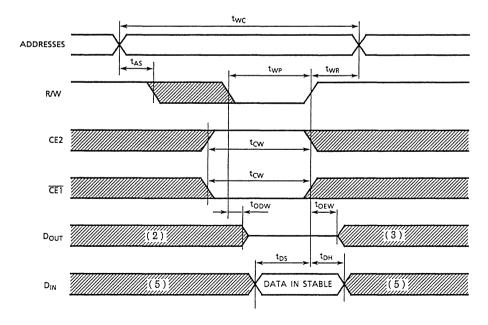

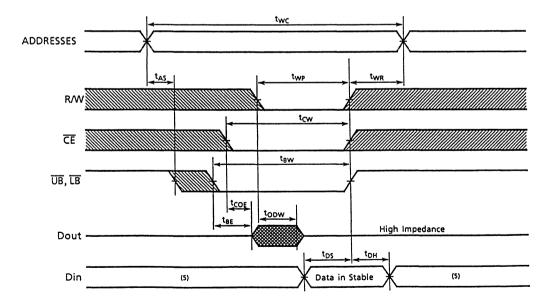

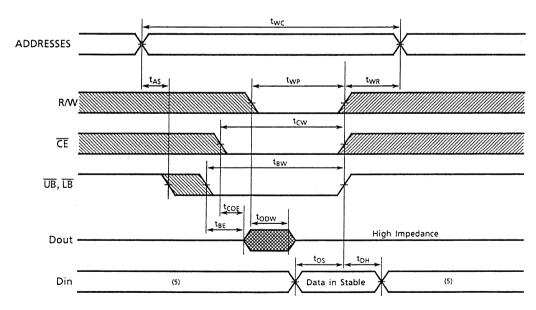

| t <sub>WC</sub>  | Write Cycle Time               | 55              | -    | 70   | -    | 85   | _    |      |  |

| t <sub>WP</sub>  | Write Pulse Width              | 45              | -    | 50   | -    | 60   | _    | 1    |  |

| t <sub>CW</sub>  | Chip Selection to End of Write | 50              | -    | 60   | -    | 65   | _    | 1    |  |

| t <sub>AS</sub>  | Address Setup Time             | 0               | _    | 0    | _    | 0    | _    | ]    |  |

| t <sub>WR</sub>  | Write Recovery Time            | 0               | _    | 0    | _    | 0    | _    | ns   |  |

| t <sub>ODW</sub> | R/W to Output in High-Z        | _               | 20   | -    | 25   | _    | 30   |      |  |

| t <sub>OEW</sub> | R/W to Output in Low-Z         | 5               | -    | 5    | -    | 5    | _    |      |  |

| t <sub>DS</sub>  | Data Setup Time                | 25              | _    | 30   | _    | 40   | _    |      |  |

| t <sub>DH</sub>  | Data Hold Time                 | 0               | _    | 0    | -    | 0    | _    | 1    |  |

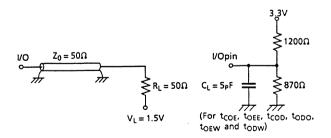

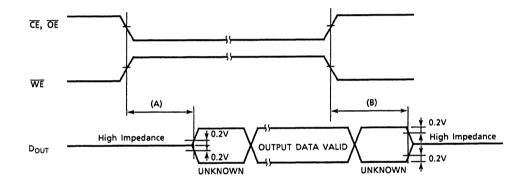

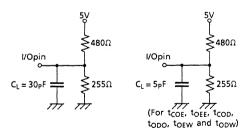

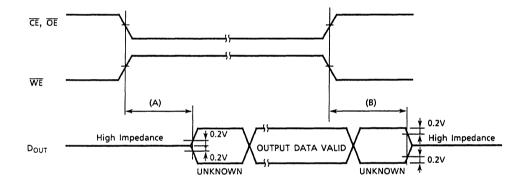

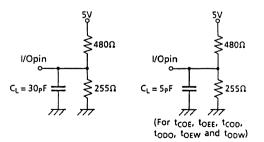

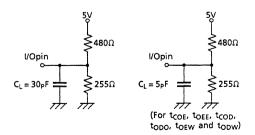

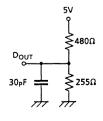

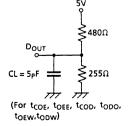

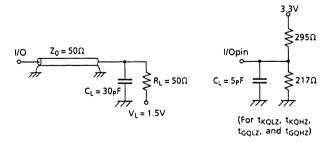

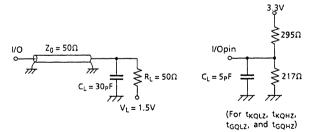

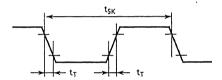

#### **AC Test Conditions**

| Input Pulse Levels                        | 2.4V/0.6V                                                                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|

| Input Pulse Rise and Fall Time            | 5ns                                                                                               |

| Input Timing Measurement Reference Level  | 1.5V                                                                                              |

| Output Timing Measurement Reference Level | 1.5V                                                                                              |

| Output Load                               | 1 TTL Gate and C <sub>L</sub> = 30pF (-55L)<br>1 TTL Gate and C <sub>L</sub> = 100pF (-70L, -85L) |

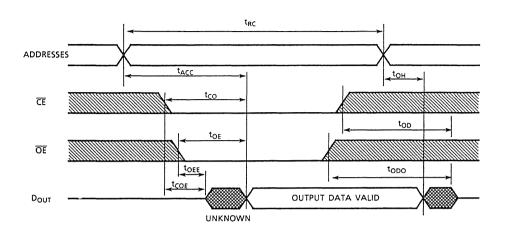

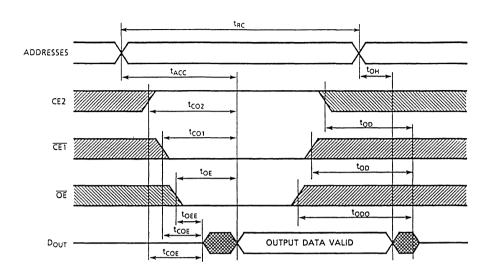

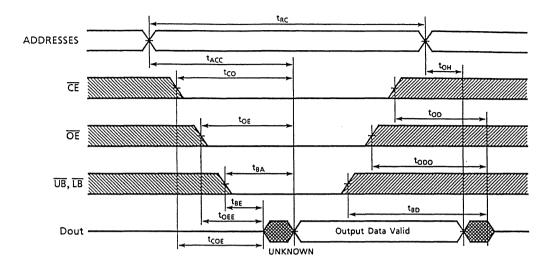

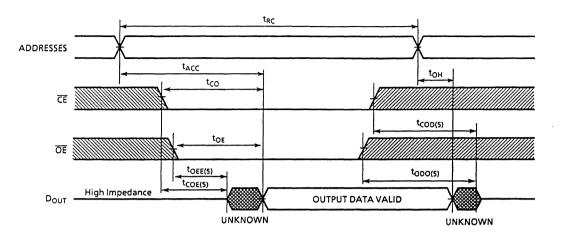

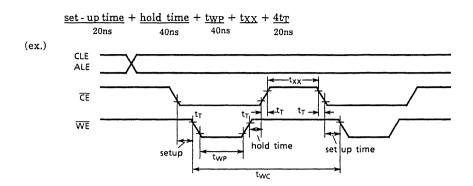

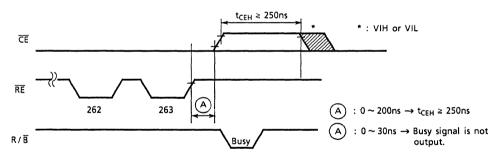

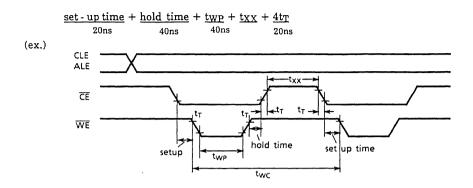

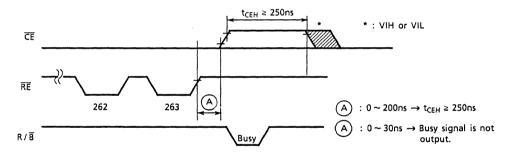

### **Timing Waveforms**

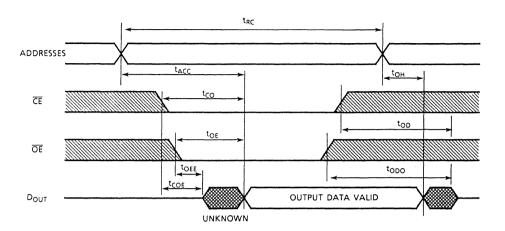

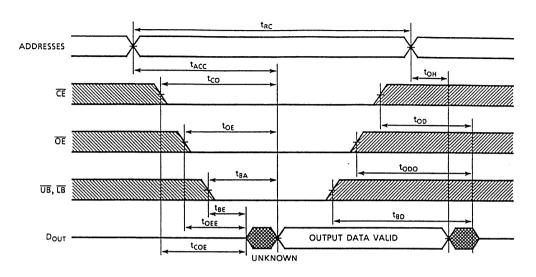

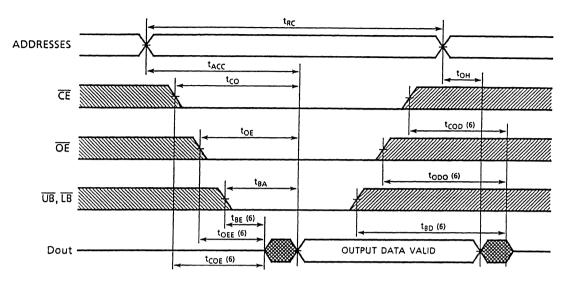

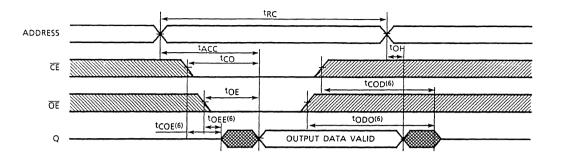

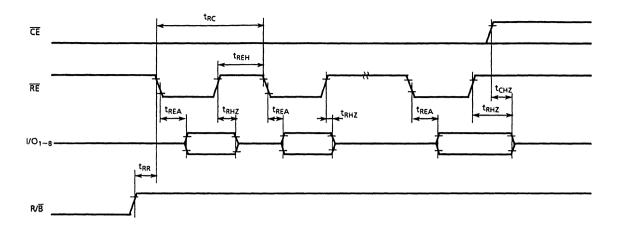

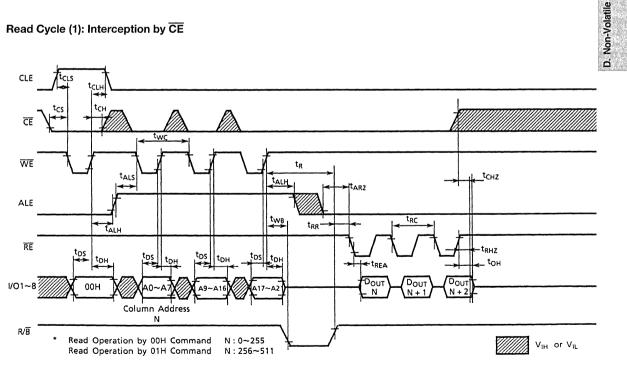

### Read Cycle (1)

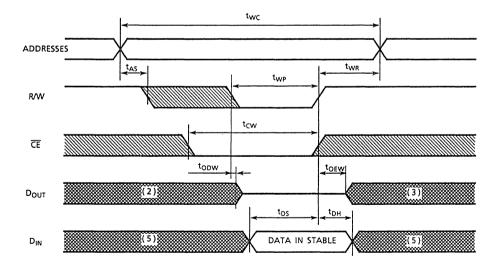

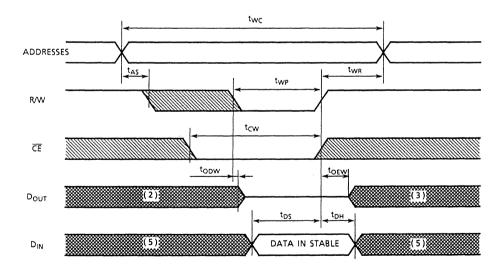

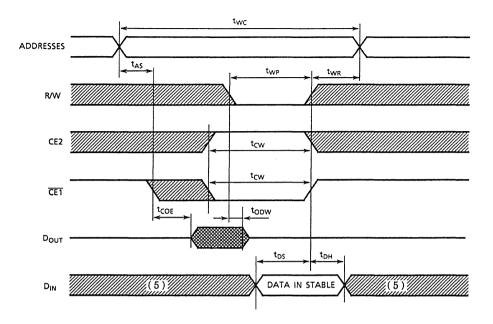

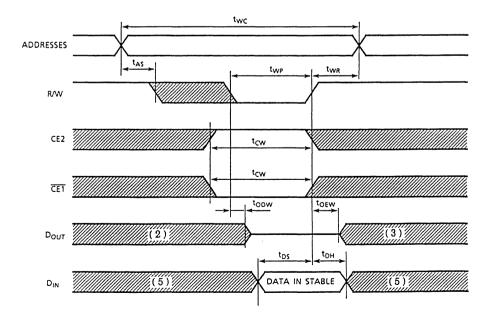

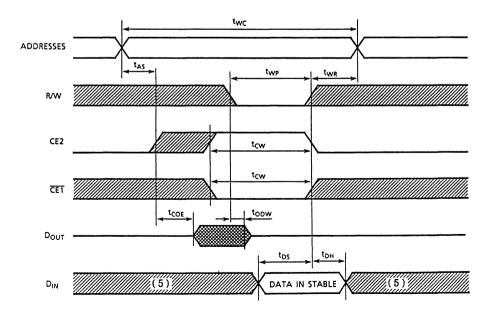

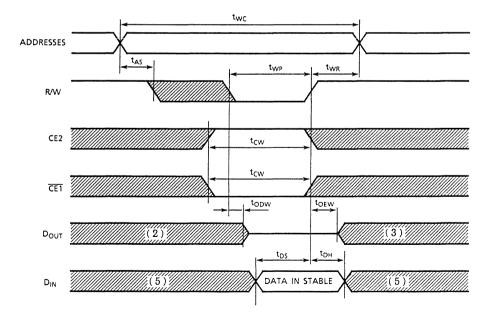

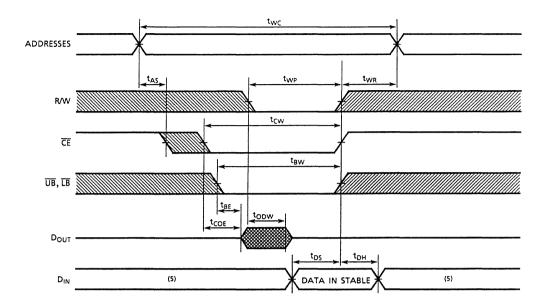

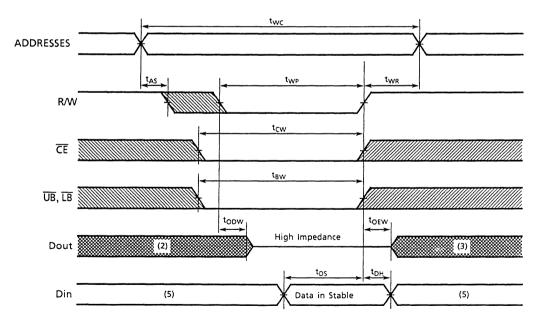

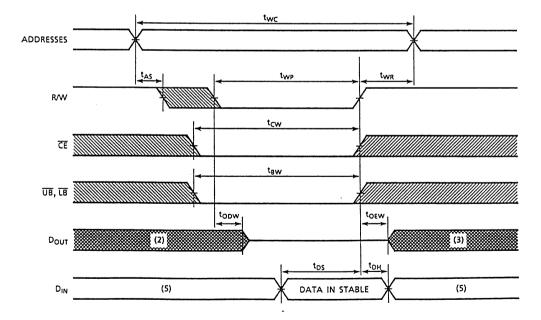

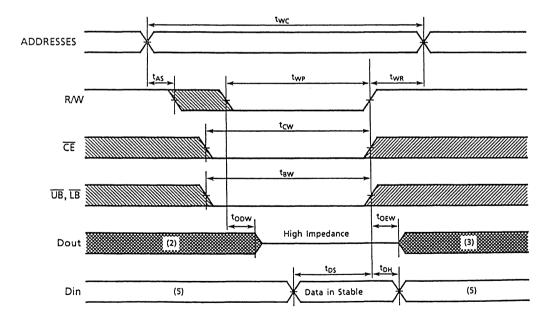

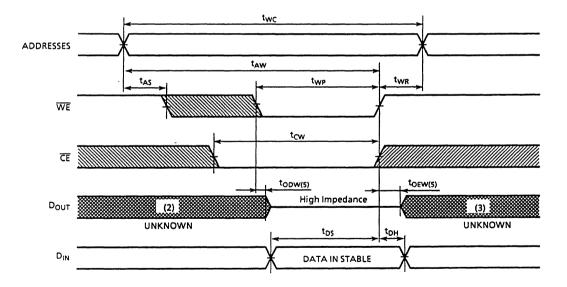

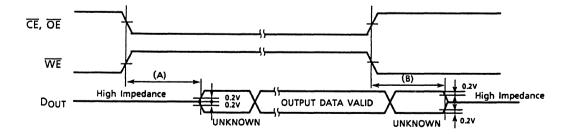

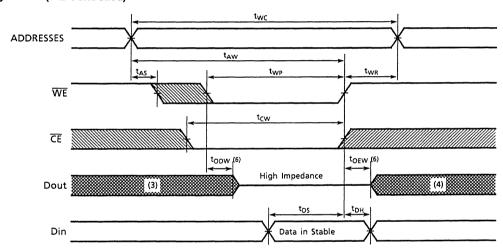

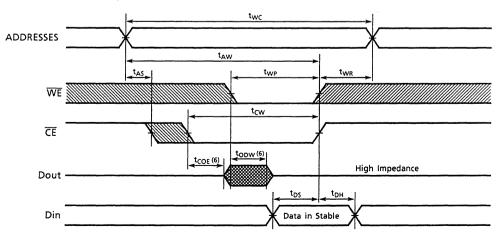

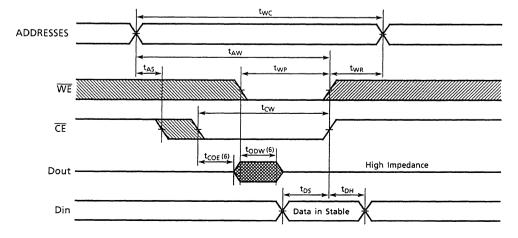

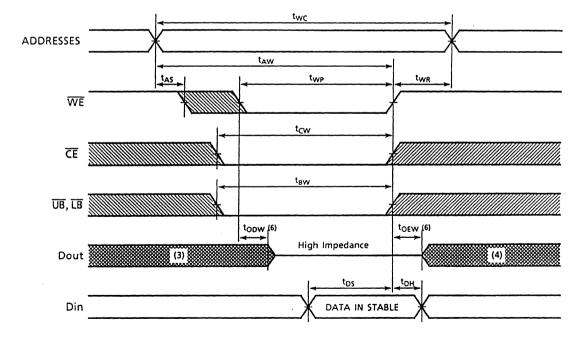

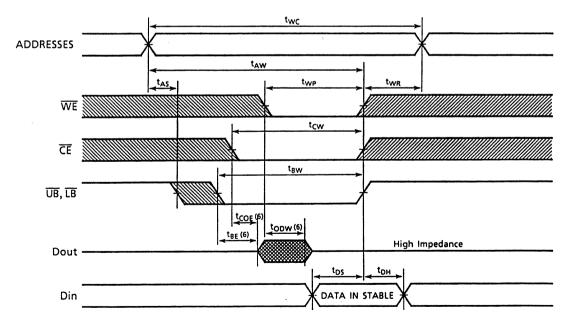

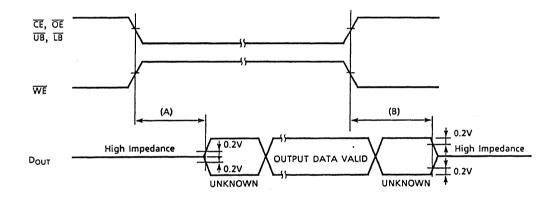

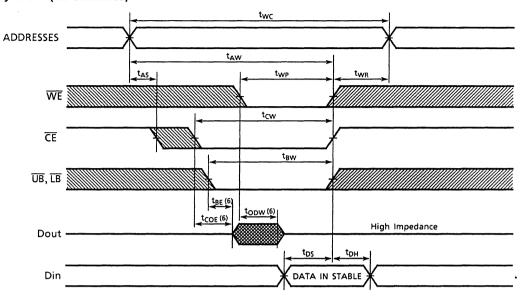

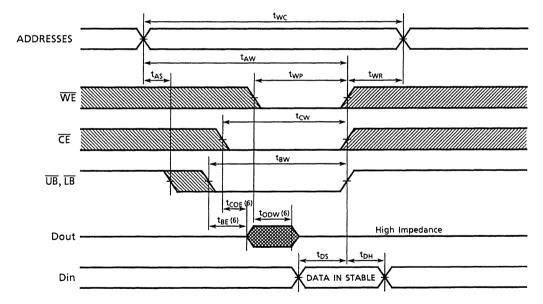

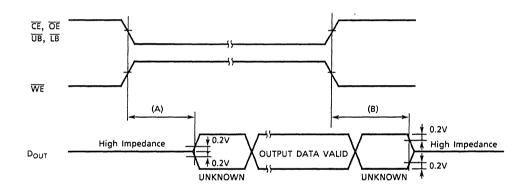

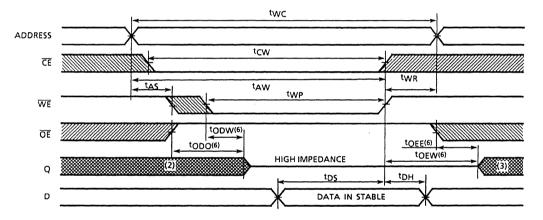

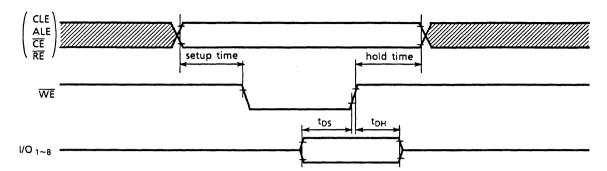

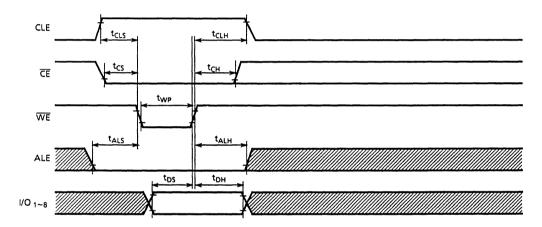

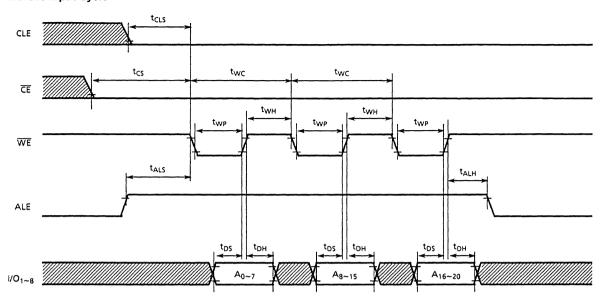

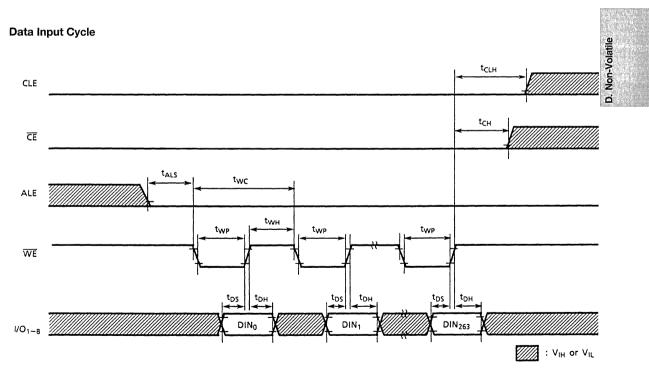

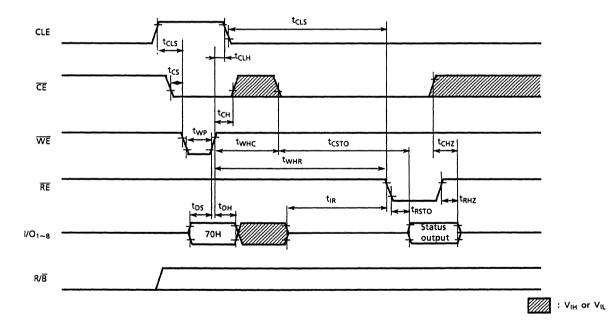

### Write Cycle 1 (4) (R/W Controlled Write)

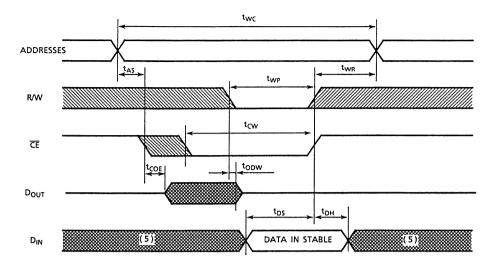

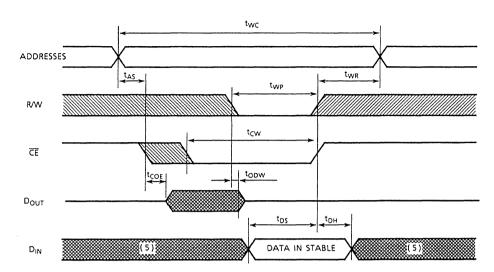

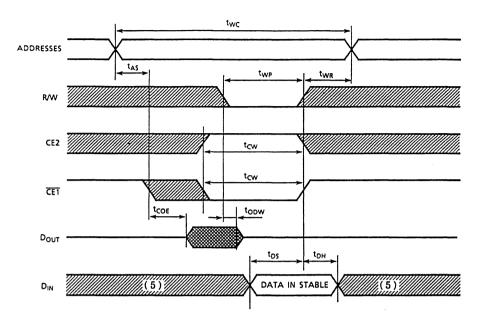

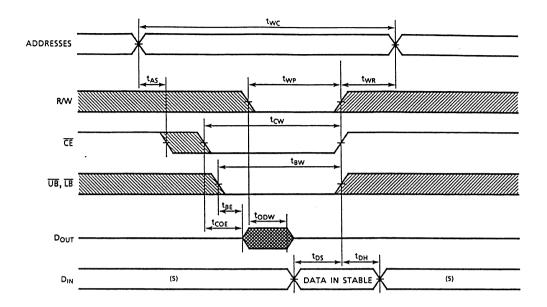

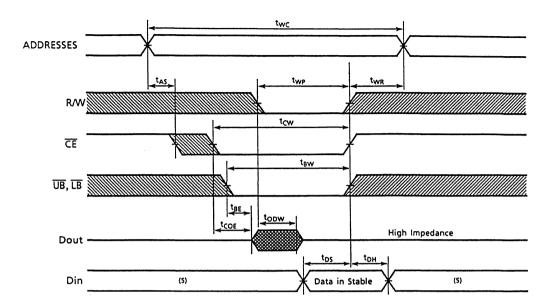

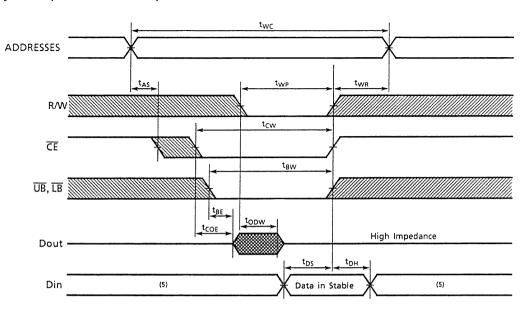

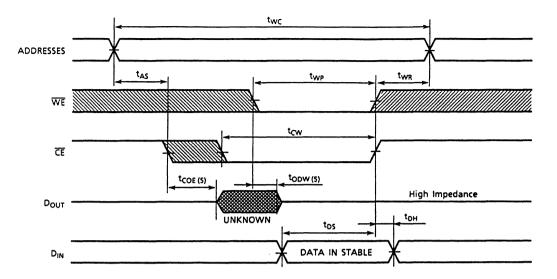

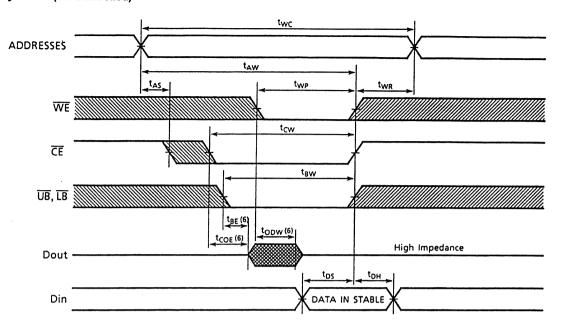

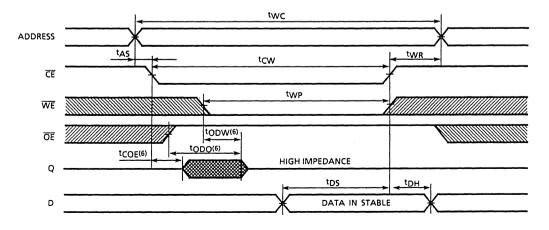

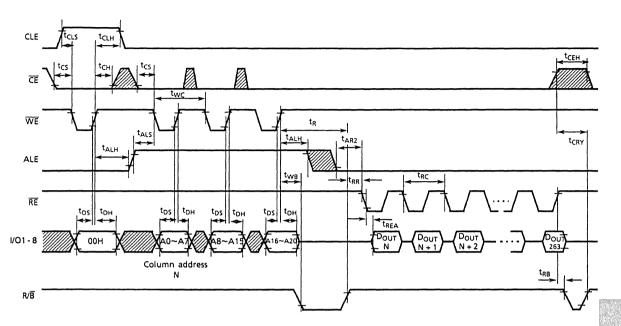

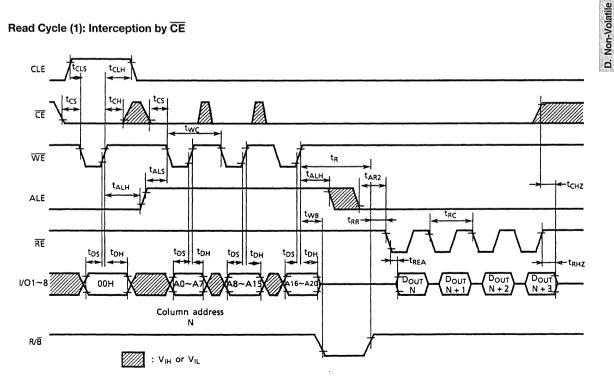

### Write Cycle 2 (4) (CE Controlled Write)

#### Notes:

- 1. R/W is High for read cycle.

- 2. Assuming that  $\overline{\text{CE}}$  Low transition occurs coincident with or after the R/W Low transition, Outputs remain in a high impedance state.

- 3. Assuming that  $\overline{\text{CE}}$  High transition occurs coincident with or prior to the R/W High transition, Outputs remain in a high impedance state.

- 4. Assuming that  $\overline{OE}$  is High for a write cycle, the Outputs are in a high impedance state during this period.

- 5. The I/O may be in the output state during this time; input signals of opposite phase must not be applied.

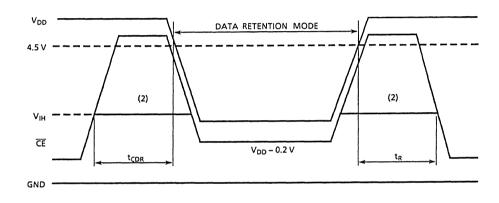

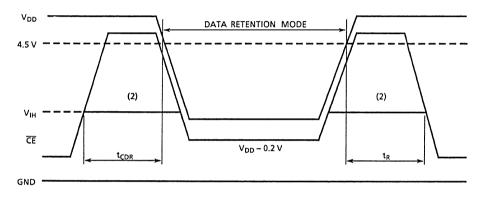

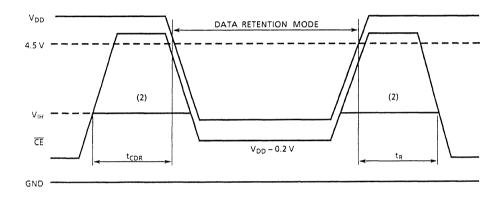

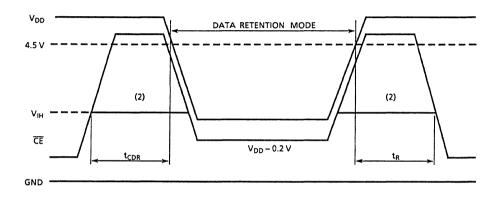

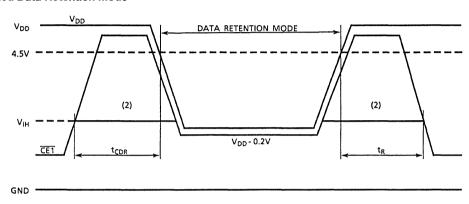

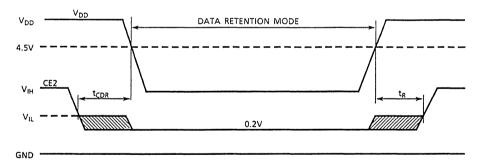

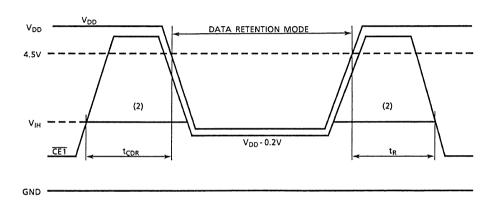

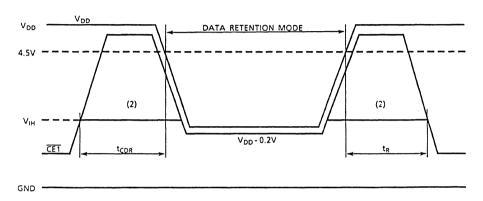

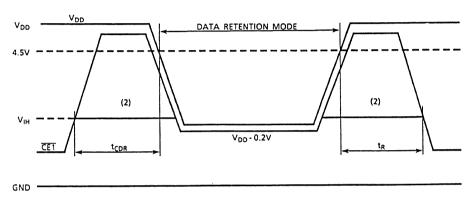

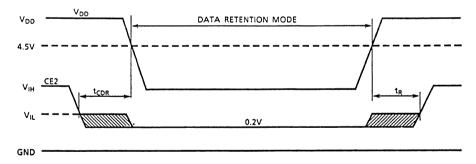

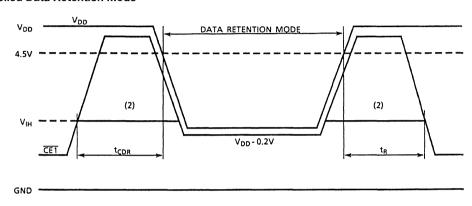

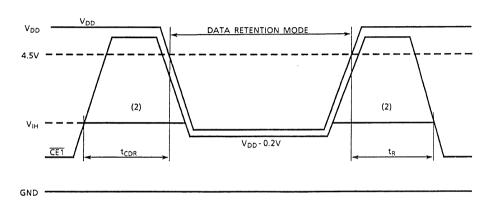

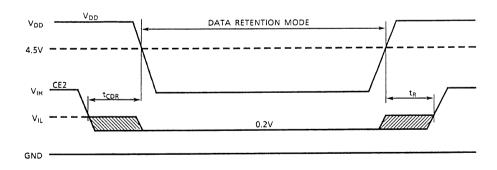

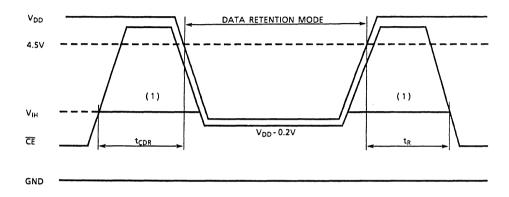

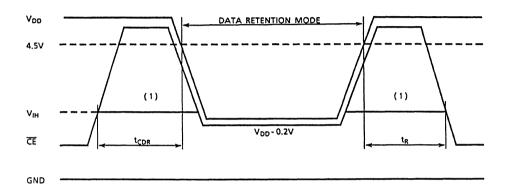

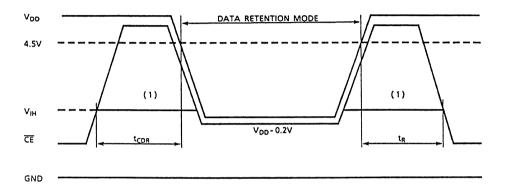

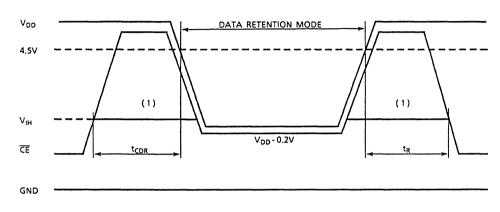

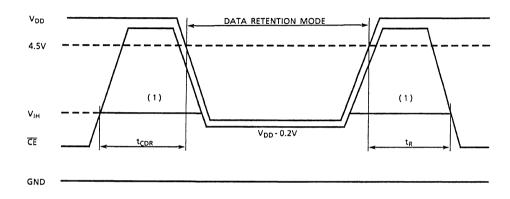

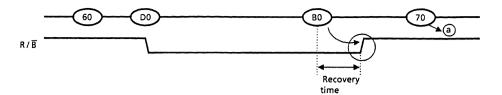

Data Retention Characteristics (Ta =  $0 \sim 70^{\circ}$ C)

| SYMBOL           | PARAMETER                            | MIN.            | TYP. | MAX. | UNIT |    |

|------------------|--------------------------------------|-----------------|------|------|------|----|

| V <sub>DH</sub>  | Data Retention Supply Voltage        | 2.0             | _    | 5.5  | V    |    |

|                  | Standby Current                      | $V_{DH} = 3.0V$ | -    | _    | 10*  |    |

| DDS2             | Standby Current                      | _               | -    | 20   | μΑ   |    |

| t <sub>CDR</sub> | Chip Deselect to Data Retention Mode | 0               | -    | _    | no   |    |

| t <sub>R</sub>   | Recovery Time                        |                 |      |      | _    | ns |

<sup>\*:</sup>  $2\mu$ A (Max.) Ta =  $0 \sim 40^{\circ}$ C

Note (1): Read Cycle Time

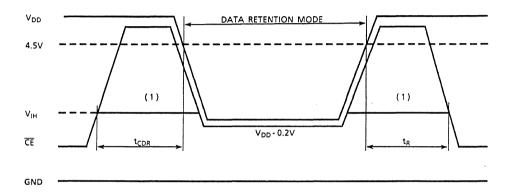

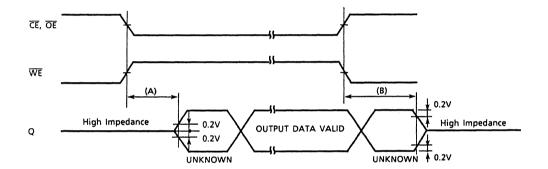

### **CE** Controlled Data Retention Mode

Note (2): If the  $V_{IH}$  of  $\overline{CE}$  is 2.2V in operation,  $I_{DDS1}$  current flows during the period that the  $V_{DD}$  voltage is going down from 4.5V to 2.4V.

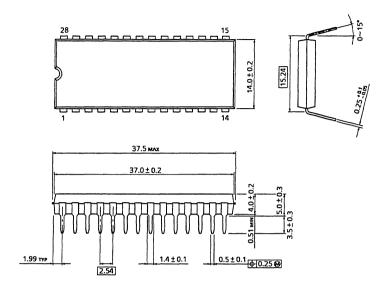

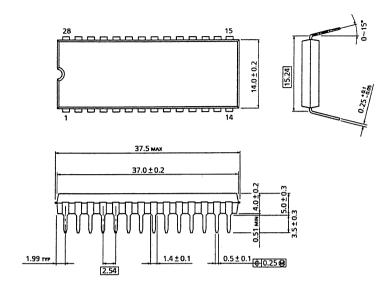

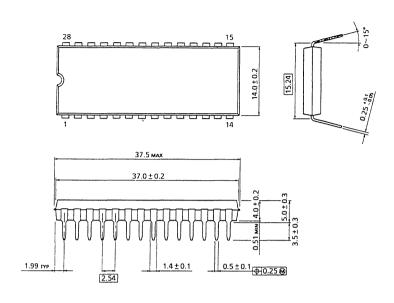

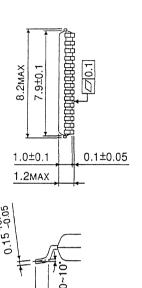

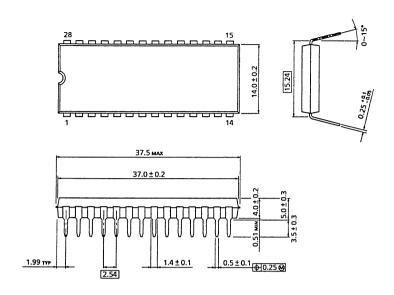

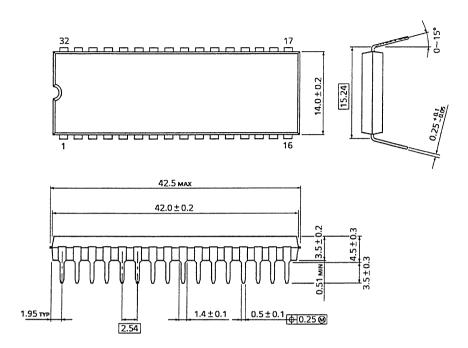

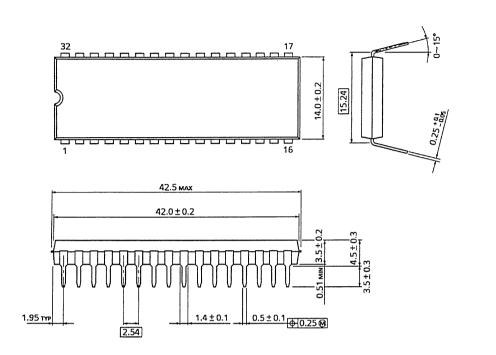

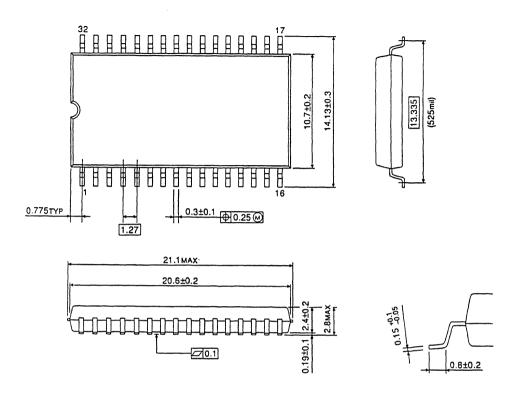

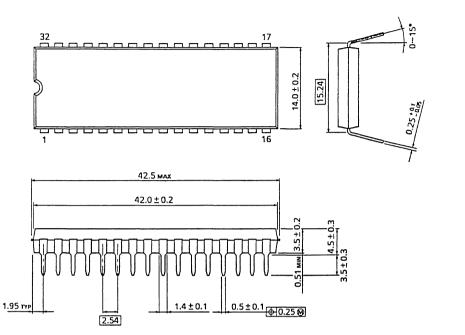

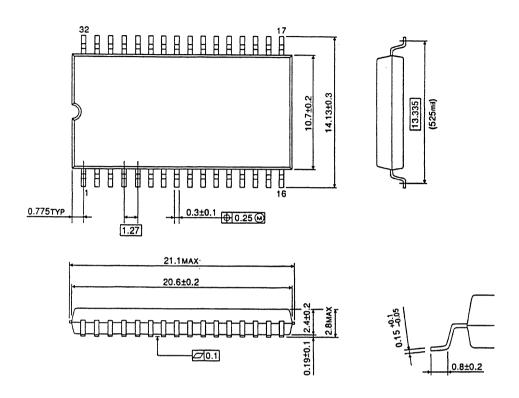

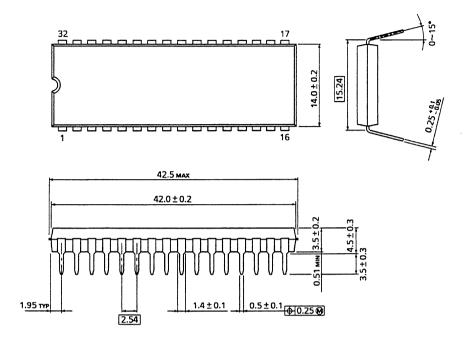

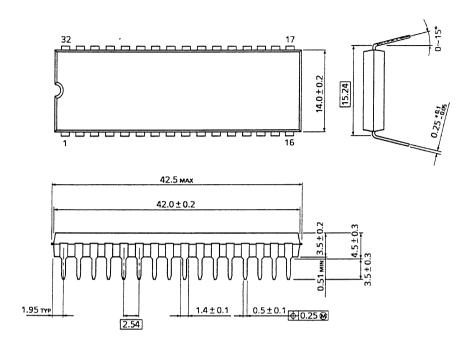

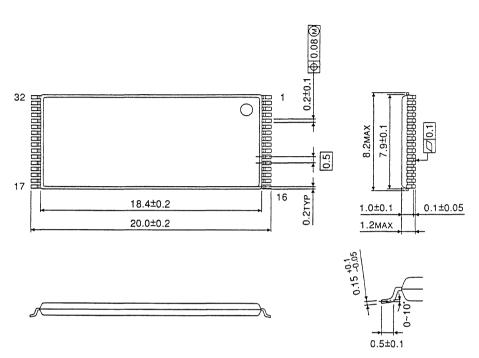

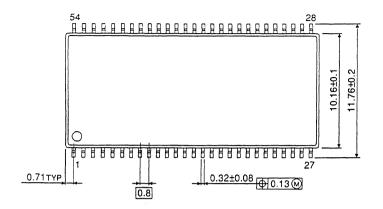

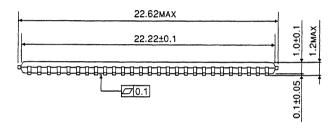

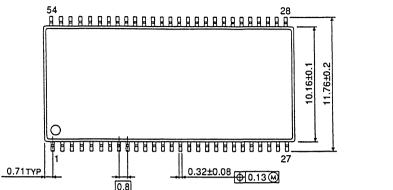

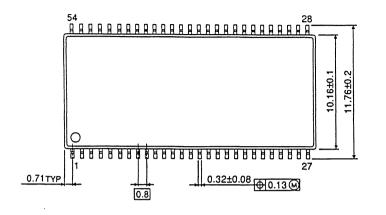

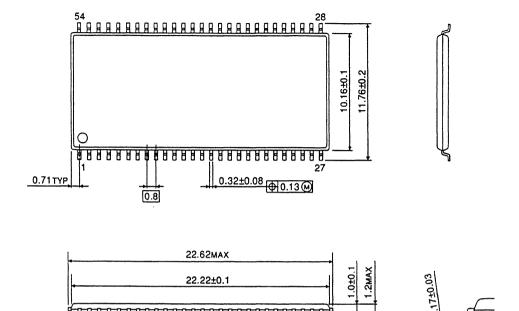

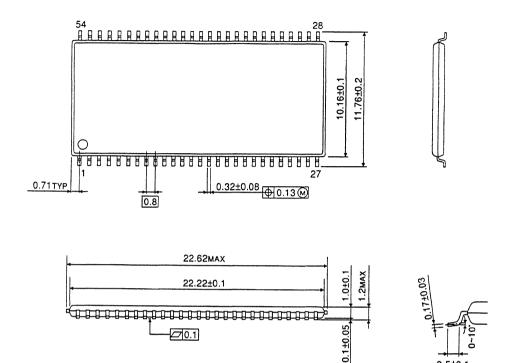

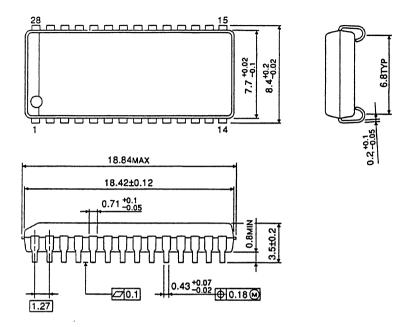

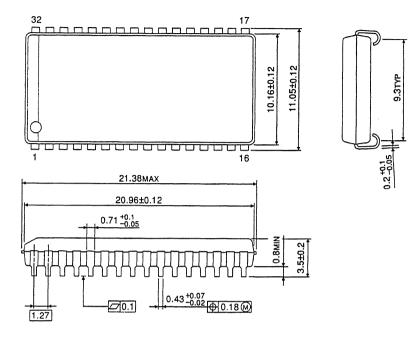

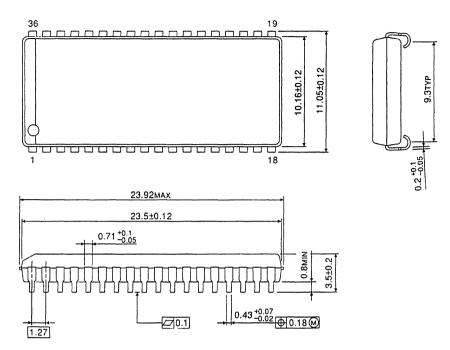

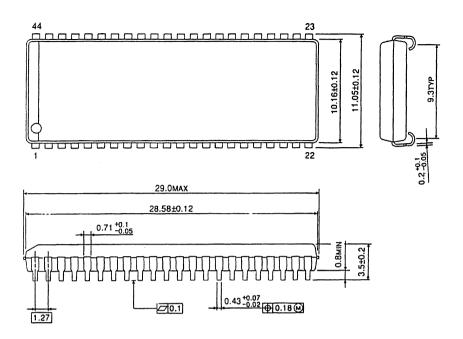

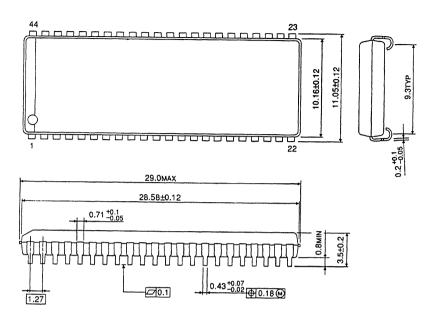

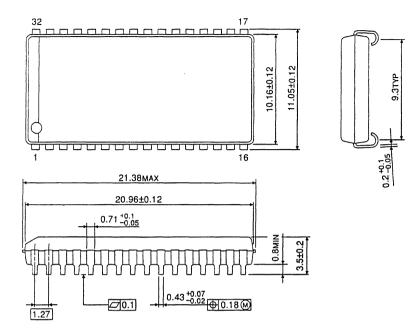

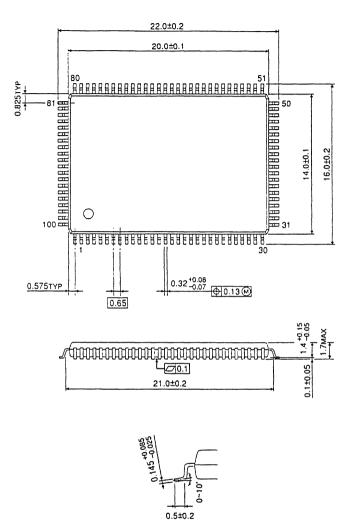

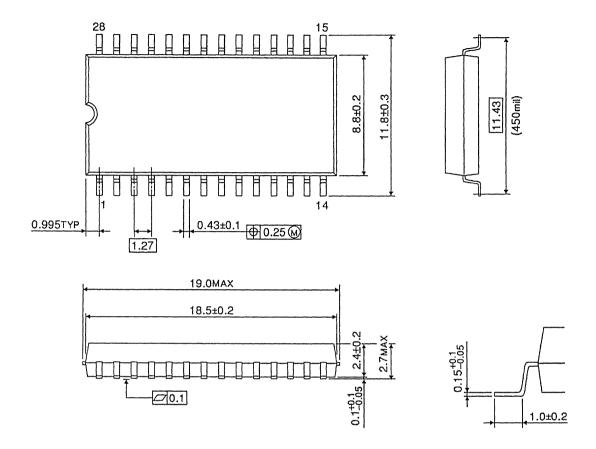

**Outline Drawing**

DIP28-P-600

Unit in mm

Weight: 4.42g (Typ.)

Unit in mm

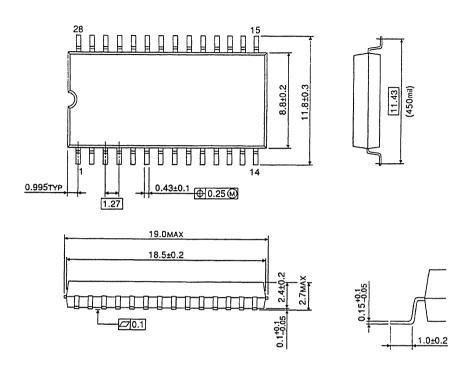

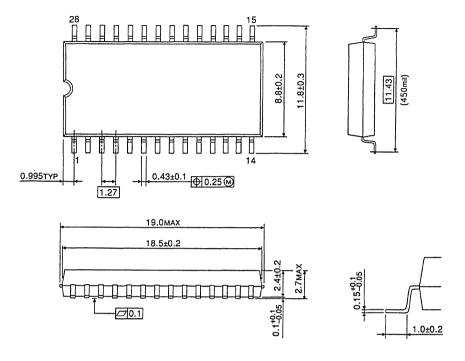

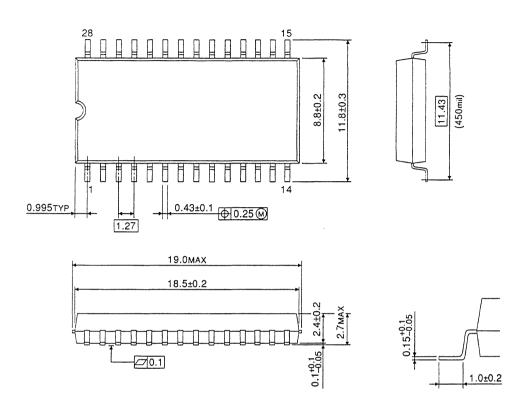

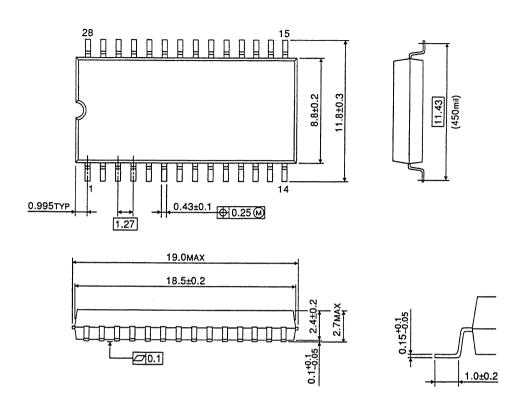

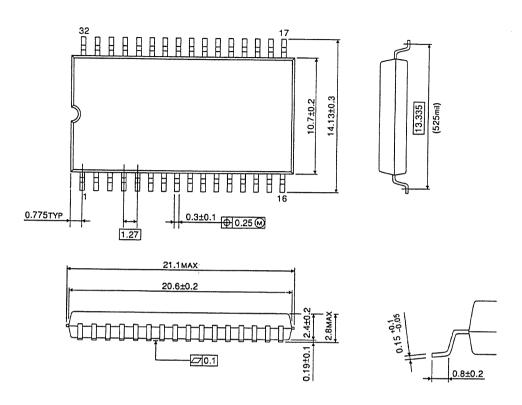

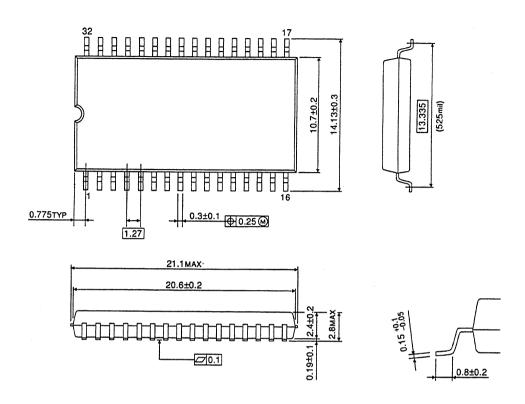

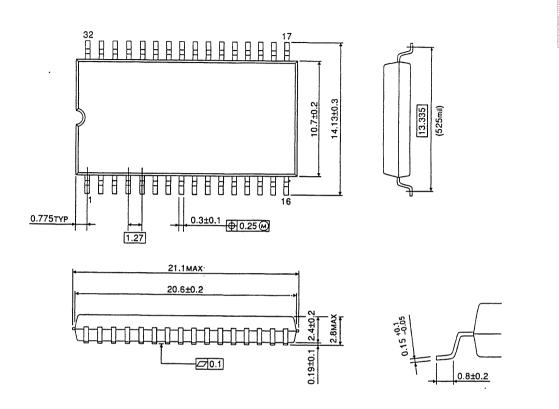

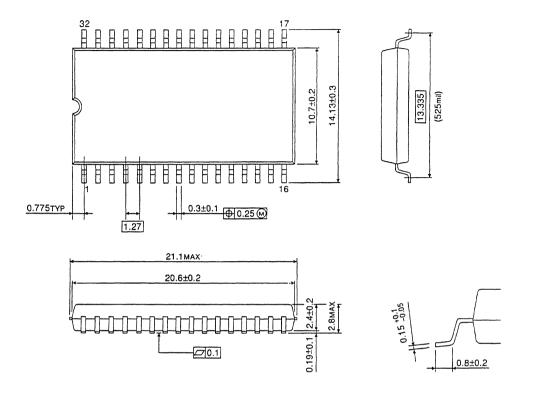

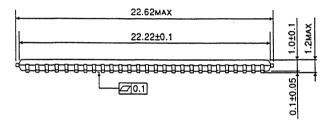

### **Outline Drawing**

SOP28-P-450

Weight: 0.79g (Typ.)

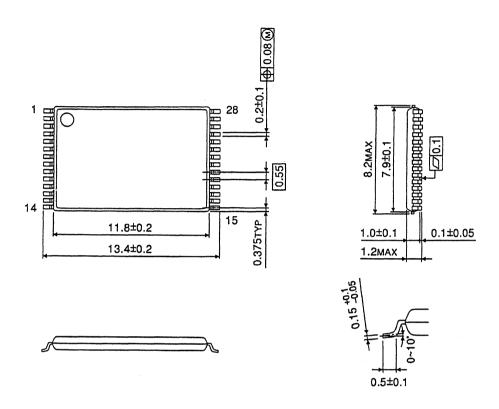

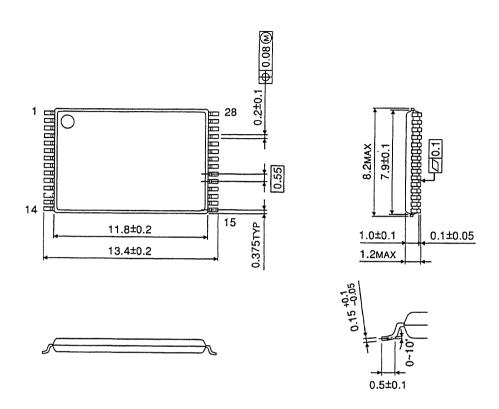

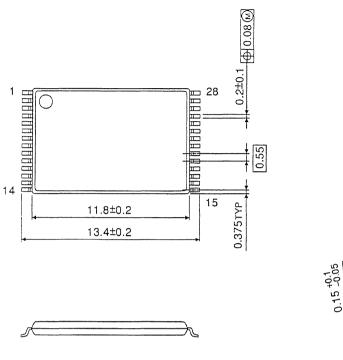

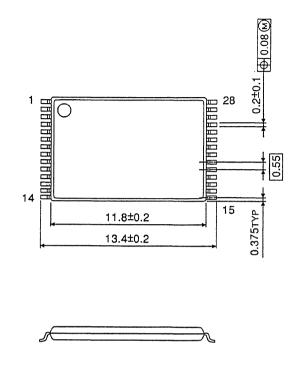

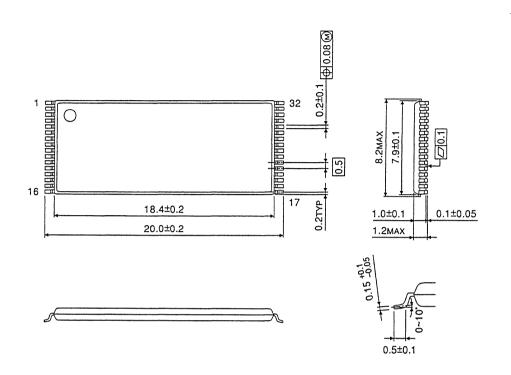

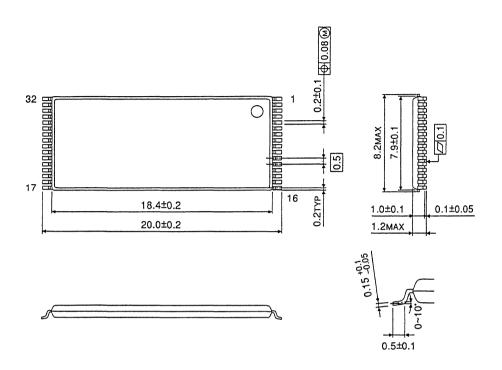

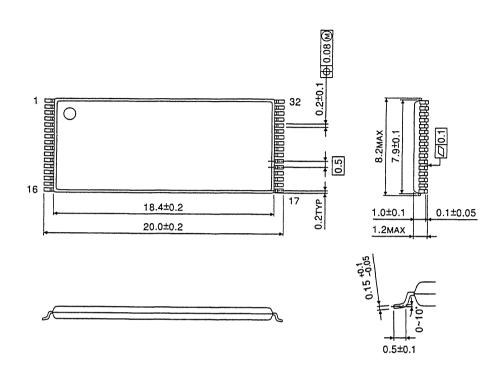

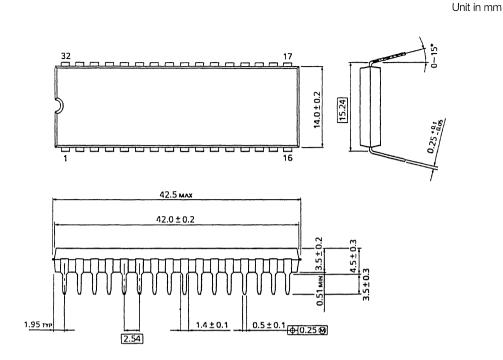

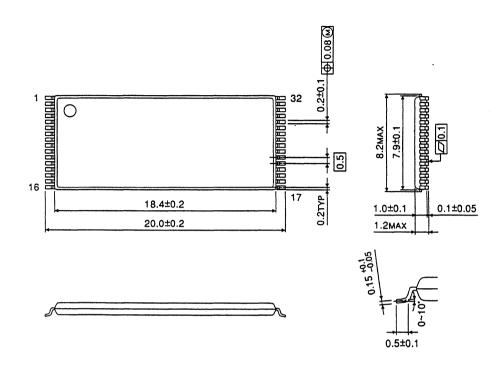

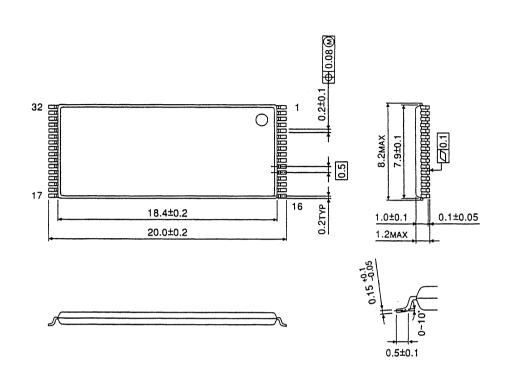

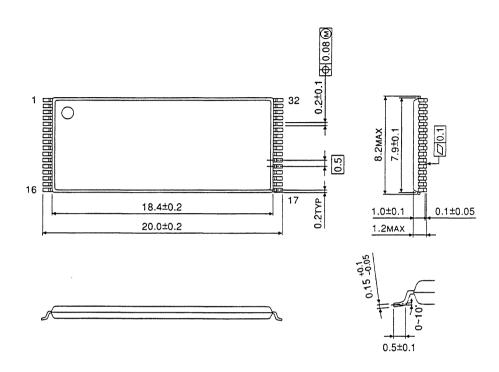

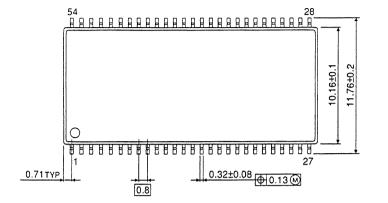

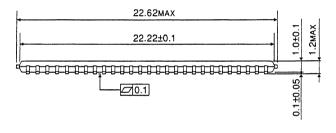

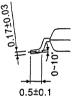

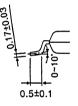

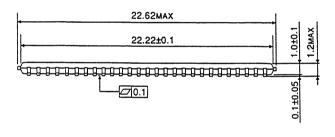

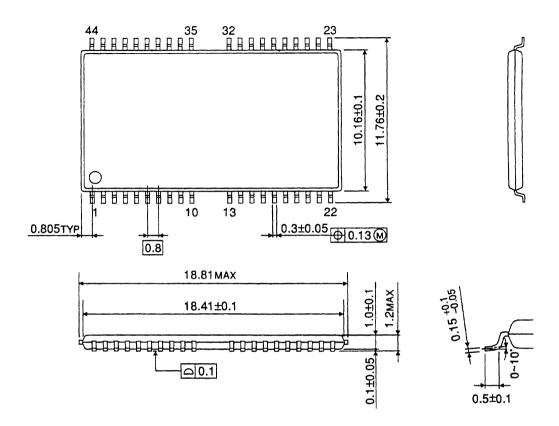

#### **Outline Drawing**

TSOP29-P

Unit in mm

Weight: 0.22g (Typ.)

This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

<sup>2.</sup> LIFE SUPPORT POLICY

Toshiba products described in this document are not authorized for use as critical components in life support systems without the written consent of the appropriate officer of Toshiba America, Inc. Life support systems are either systems intended for surgical implant in the body or systems which sustain life.

A critical component in any component of a life support system whose failure to perform may cause a malfunction of the life support system, or may affect its safety or effectiveness.

<sup>3.</sup> The information in this document has been carefully checked and is believed to be reliable; however no responsibility can be assumed for inaccuracies that may not have been caught. All information in this data book is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

### TC55257DPI/DFI/DFTI-70L/-85L

**PRELIMINARY**

#### SILICON GATE CMOS

#### 32,768 WORD x 8 BIT STATIC RAM

#### Description

The TC55257DPI is a 262,144 bit static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mA/MHz (typ.) and a minimum cycle time of 70ns.

When  $\overline{\text{CE}}$  is a logical high, the device is placed in a low power standby mode in which the standby current is  $0.3\mu\text{A}$  typically. The TC55257DPI has two control inputs. Chip Enable ( $\overline{\text{CE}}$ ) allows for device selection and data retention control, and an Output Enable input ( $\overline{\text{OE}}$ ) provides fast memory access. The TC55257DPI is suitable for use in microprocessor application systems where high speed, low power, and battery backup are required. The TC55257DPI is guaranteed over an operating temperature range of -40 ~ 85°C so the TC55257DPI is suitable for use in wide operating temperature systems.

The TC55257DPI is offered in a standard dual-in-line 28-pin plastic package (0.6 inch width), a small outline plastic package, and a thin small outline plastic package (forward type).

#### **Features**

#### • Low power dissipation:

27.5mW/MHz (typ.)

Standby current:

$2\mu A$  (max.) at Ta = 25°C ° 28 PIN DIP & SOP

• 5V single power supply

· Access time (max.)

|                | TC55257DPI/DFI/DFTI |      |  |  |  |

|----------------|---------------------|------|--|--|--|

|                | -70L                | -85L |  |  |  |

| Access Time    | 70ns                | 85ns |  |  |  |

| CE Access Time | 70ns                | 85ns |  |  |  |

| OE Access Time | 35ns                | 45ns |  |  |  |

Power down feature:

• Data retention supply voltage:

eature:  $\overline{\text{CE}}$ supply voltage: 2.0 ~ 5.5V

• Inputs and outputs directly TTL compatible

• Wide operating temperature: -40 ~ 85°C

Package

TC55257DPI

: DIP28-P-600

TC55257DFI

: SOP28-P-450 : TSOP28-P

TC55257DFTI : TS0

#### Pin Names

| A0 ~ A14        | Address Inputs           |

|-----------------|--------------------------|

| R/W             | Read/Write Control Input |

| ŌĒ              | Output Enable Input      |

| CE              | Chip Enable Input        |

| I/O1 ~ I/O8     | Data Input/Output        |

| V <sub>DD</sub> | Power (+5V)              |

| GND             | Ground                   |

| PIN NO.  | 1              | 2               | 3              | 4              | 5               | 6    | 7               | 8               | 9               | 10             | 11             | 12             | 13             | 14              |

|----------|----------------|-----------------|----------------|----------------|-----------------|------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|

| PIN NAME | ŌĒ             | A <sub>11</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>13</sub> | R/W  | V <sub>DD</sub> | A <sub>14</sub> | A <sub>12</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>  |

| PIN NO.  | 15             | 16              | 17             | 18             | 19              | 20   | 21              | 22              | 23              | 24             | 25             | 26             | 27             | 28              |

| PIN NAME | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | 1/01           | 1/02            | I/O3 | GND             | 1/04            | I/O5            | I/O6           | 1/07           | I/O8           | CE             | A <sub>10</sub> |

### Pin Connection (Top View)

|        | $\overline{}$ |                      |

|--------|---------------|----------------------|

| A14 L  |               | 28   V <sub>DD</sub> |

| A12 [  |               | 27 🏻 R/W             |

| A7 [   |               | 26 D A13             |

| A6 [   |               | 25 🛭 A8              |

| A5 [   |               | 24 🛭 A9              |

| A4 [   |               | 23 DA11              |

| A3 [   |               | 22 OE                |

| A2 [   |               | 21 A10               |

| A1 [   | 9             | 20 TE                |

| A0 [   |               | 19 🖟 1/08            |

| 1/01 [ |               | 18 🖟 1/07            |

| 1/02 [ | 12            | 17 🖟 1/06            |

| 1/03 [ |               | 16 1/05              |

| GND [  | 14            | 15 1/04              |

#### **Block Diagram**

### **Operating Mode**

| OPERATION MODE  | CE | ŌĒ | R/W | I/01 ~ I/08      | POWER            |

|-----------------|----|----|-----|------------------|------------------|

| Read            | L  | L  | Н   | D <sub>OUT</sub> | I <sub>DDO</sub> |

| Write           | L  | *  | L   | D <sub>IN</sub>  | I <sub>DDO</sub> |

| Output Deselect | L  | Н  | Н   | High-Z           | I <sub>DDO</sub> |

| Standby         | Н  | *  | *   | High-Z           | I <sub>DDS</sub> |

<sup>\*</sup> H or L

#### **Maximum Ratings**

| SYMBOL              | ITEM                         | RATING                        | UNIT |

|---------------------|------------------------------|-------------------------------|------|

| V <sub>DD</sub>     | Power Supply Voltage         | -0.3 ~ 7.0                    | V    |

| V <sub>IN</sub>     | Input Voltage                | -0.3* ~ 7.0                   | ٧    |

| V <sub>I/O</sub>    | Input and Output Voltage     | -0.5* ~ V <sub>DD</sub> + 0.5 | V    |

| P <sub>D</sub>      | Power Dissipation            | 1.0/0.6**                     | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                           | °C   |

| T <sub>STRG</sub>   | Storage Temperature          | -55 ~ 150                     | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | -40 ~ 85                      | °C   |

<sup>\* -3.0</sup>V at pulse width 50ns

<sup>\*\*</sup> SOP

### **DC** Recommended Operating Conditions

| SYMBOL          | PARAMETER                     | MIN.  | TYP. | MAX.                  | UNIT |

|-----------------|-------------------------------|-------|------|-----------------------|------|

| $V_{DD}$        | Power Supply Voltage          | 4.5   | 5.0  | 5.5                   |      |

| V <sub>IH</sub> | Input High Voltage            | 2.4   | -    | V <sub>DD</sub> + 0.3 | \/   |

| V <sub>IL</sub> | Input Low Voltage             | -0.3* | -    | 0.6                   | V    |

| V <sub>DH</sub> | Data Retention Supply Voltage | 2.0   | _    | 5.5                   |      |

<sup>\* -3.0</sup>V at pulse width 50ns

### DC and Operating Characteristics (Ta = -40 ~ 85°C, $V_{DD}$ = 5V $\pm$ 10%)

| SYMBOL            | PARAMETER              | TEST CONDITION                                                                                                   |                                 |      | TYP. | MAX. | UNIT |

|-------------------|------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|------|

| lլյ               | Input Leakage Current  | V <sub>IN</sub> = 0 ~ V <sub>DD</sub>                                                                            |                                 | _    | -    | ±1.0 | μА   |

| I <sub>LO</sub>   | Output Leakage Current | $\overline{CE} = V_{IH} \text{ or } R/W = V_{IL}$<br>$V_{OUT} = 0 \sim V_{DD}$                                   | or $\overline{OE} = V_IH$       | _    | _    | ±1.0 | μА   |

| lон               | Output High Current    | V <sub>OH</sub> = 2.4V                                                                                           |                                 | -1.0 | _    | _    | mA   |

| l <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.4V                                                                                           |                                 | 4.0  | _    | -    | mA   |

|                   |                        | CE = V <sub>IL</sub>                                                                                             | t <sub>cycle</sub> = 1μs        | _    | 10   | -    |      |

| I <sub>DDO1</sub> |                        | $R/W = V_{IH}$                                                                                                   | t <sub>cycle</sub> = Min. cycle | _    | _    | 70   |      |

|                   | Operating Current      | CE = 0.2V                                                                                                        | t <sub>cycle</sub> = 1μs        | -    | 5    | _    | mA   |

| I <sub>DDO2</sub> |                        | $ \begin{aligned} R/W &= V_{DD} - 0.2V \\ Other Input \\ &= V_{DD} - 0.2V/0.2V \\ I_{OUT} &= 0mA \end{aligned} $ | t <sub>cycle</sub> = Min. cycle | _    | _    | 60   | :    |

| I <sub>DDS1</sub> |                        | CE = V <sub>IH</sub>                                                                                             |                                 | -    | _    | 3    | mA   |

|                   | Standby Current        | CE = V <sub>DD</sub> - 0.2V                                                                                      | Ta = -40 ~ 85°C                 | -    | _    | 30   |      |

| I <sub>DDS2</sub> |                        | $V_{DD} = 2.0V \sim 5.5V$                                                                                        | Ta = 25°C                       | _    | 0.3  | 2    | μΑ   |

### Capacitance\* (Ta = 25°C, f = 1MHz)

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX. | UNIT |

|------------------|--------------------|------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = GND  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10   | ρF   |

<sup>\*</sup>This parameter is periodically sampled and is not 100% tested.

### AC Characteristics (Ta = -40 $\sim$ 85 $^{\circ}$ C, V<sub>DD</sub> = 5V $\pm$ 10%)

### **Read Cycle**

| SYMBOL           | PARAMETER                            | -7   | OL   | -8   | UNIT |    |

|------------------|--------------------------------------|------|------|------|------|----|

|                  |                                      | MIN. | MAX. | MIN. | MAX. |    |

| t <sub>RC</sub>  | Read Cycle Time                      | 70   | _    | 85   | -    |    |

| t <sub>ACC</sub> | Address Access Time                  | _    | 70   | _    | 85   |    |

| t <sub>CO</sub>  | CE Access Time                       | _    | 70   | _    | 85   |    |

| t <sub>OE</sub>  | Output Enable to Output in Valid     | _    | 35   | _    | 45   |    |

| t <sub>COE</sub> | Chip Enable (CE) to Output in Low-Z  | 5    | _    | 5    | _    | ns |

| t <sub>OEE</sub> | Output Enable to Output in Low-Z     | 0    | -    | 0    | _    | ]  |

| t <sub>OD</sub>  | Chip Enable (CE) to Output in High-Z | _    | 25   | _    | 30   |    |

| t <sub>ODO</sub> | Output Enable to Output in High-Z    | _    | 25   | _    | 30   |    |

| t <sub>OH</sub>  | Output Data Hold Time                | 10   | -    | 10   | _    | 1  |

### Write Cycle

|                  |                                |      | TC55257DI | PI/DFI/DFT |      |    |

|------------------|--------------------------------|------|-----------|------------|------|----|

| SYMBOL           | PARAMETER                      | -7   | OL        | -8         | UNIT |    |

|                  |                                | MIN. | MAX.      | MIN.       | MAX. |    |

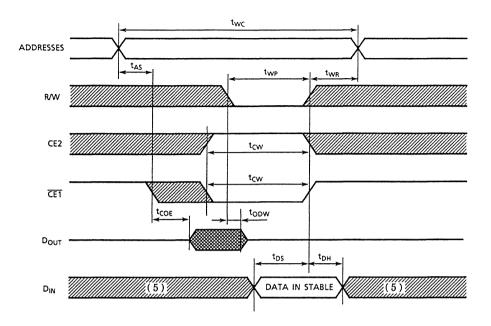

| t <sub>WC</sub>  | Write Cycle Time               | 70   | -         | 85         | _    |    |

| t <sub>WP</sub>  | Write Pulse Width              | 50   | _         | 60         | _    |    |

| t <sub>CW</sub>  | Chip Selection to End of Write | 60   | _         | 65         | _    |    |

| t <sub>AS</sub>  | Address Setup Time             | 0    | -         | 0          | _    |    |

| t <sub>WR</sub>  | Write Recovery Time            | 0    | _         | 0          | _    | ns |

| t <sub>ODW</sub> | R/W to Output in High-Z        | _    | 25        | _          | 30   |    |

| t <sub>OEW</sub> | R/W to Output in Low-Z         | 0    | _         | 0          | _    |    |

| t <sub>DS</sub>  | Data Setup Time                | 30   | _         | 40         | _    |    |

| t <sub>DH</sub>  | Data Hold Time                 | 0    | _         | 0          | _    |    |

### **AC Test Conditions**

| Input Pulse Levels                        | 2.6V/0.4V                             |

|-------------------------------------------|---------------------------------------|

| Input Pulse Rise and Fall Time            | 5ns                                   |

| Input Timing Measurement Reference Level  | 1.5V                                  |

| Output Timing Measurement Reference Level | 1.5V                                  |

| Output Load                               | 1 TTL Gate and C <sub>L</sub> = 100pF |

### **Timing Waveforms**

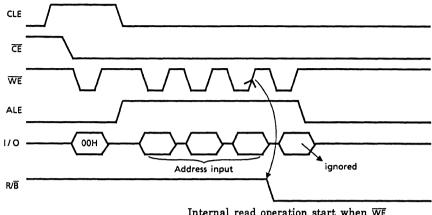

Read Cycle (1)

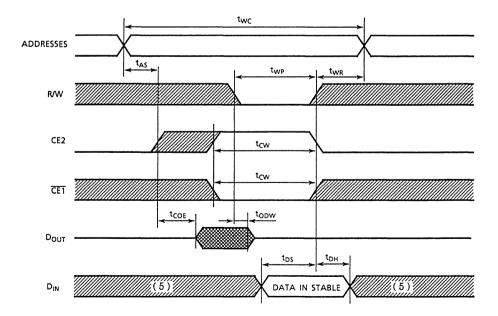

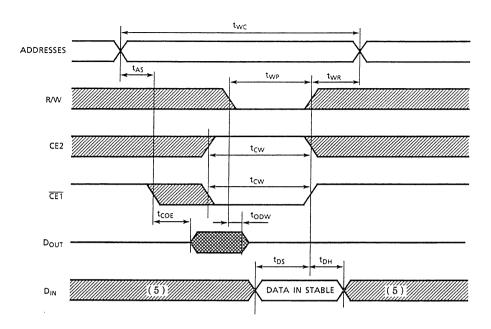

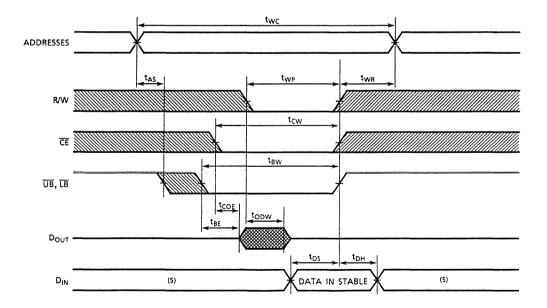

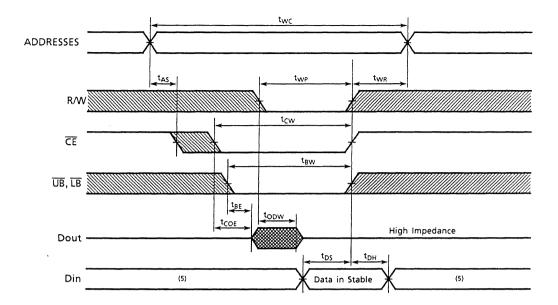

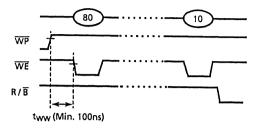

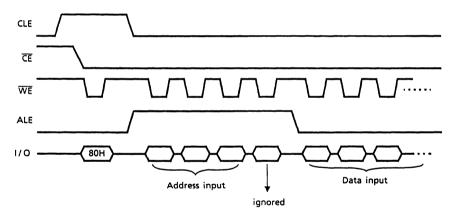

### Write Cycle 1 (4) (R/W Controlled Write)

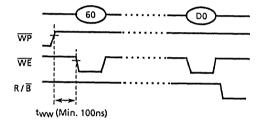

### Write Cycle 2 (4) (CE Controlled Write)

#### Notes:

- 1. R/W is High for read cycle.

- 2. Assuming that  $\overline{\text{CE}}$  Low transition occurs coincident with or after the R/W low transition, Outputs remain in a high impedance state.

- 3. Assuming that  $\overline{\text{CE}}$  High transition occurs coincident with or prior to the R/W high transition, Outputs remain in a high impedance state.

- 4. Assuming that  $\overline{OE}$  is High for a write cycle, the Outputs are in a high impedance state during this period.

- 5. The I/O may be in the output state during this time; input signals of opposite phase must not be applied.

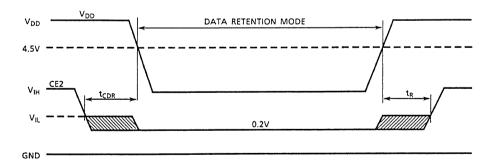

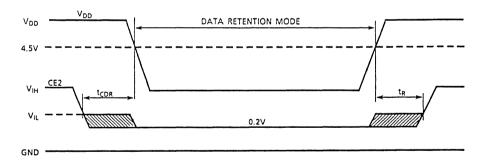

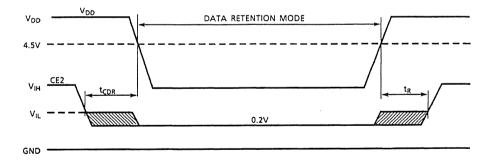

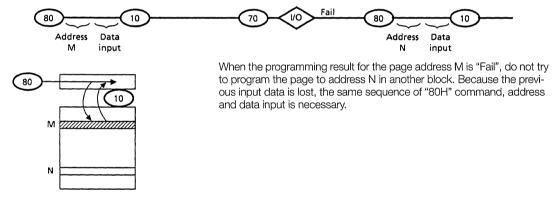

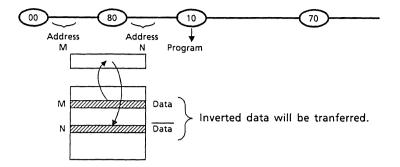

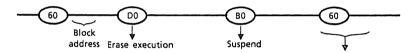

### Data Retention Characteristics (Ta = -40 ~ 85°C)

| SYMBOL            | PARAMETER                            | PARAMETER               |   |    | MAX.  | UNIT |

|-------------------|--------------------------------------|-------------------------|---|----|-------|------|

| V <sub>DH</sub>   | Data Retention Supply Voltage        | etention Supply Voltage |   |    | 5.5   | ٧    |

|                   | Standby Current                      | V <sub>DH</sub> = 3.0V  | - | -  | 15*   | μΑ   |

| I <sub>DDS2</sub> | Standby Current                      | _                       | _ | 30 | μΑ    |      |

| t <sub>CDR</sub>  | Chip Deselect to Data Retention Mode |                         | 0 | _  | _     | ns   |

| t <sub>R</sub>    | Recovery Time                        | t <sub>RC(1)</sub>      | - | _  | 1 115 |      |

Note (1): Read Cycle Time

### **CE** Controlled Data Retention Mode

Note (2): If the  $V_{IH}$  of  $\overline{CE}$  is 2.4V in operation,  $I_{DDS1}$  current flows during the period that the  $V_{DD}$  voltage is going down from 4.5V to 2.6V.

<sup>\*2</sup> $\mu$ A (max.) Ta = 0 ~ 40°C

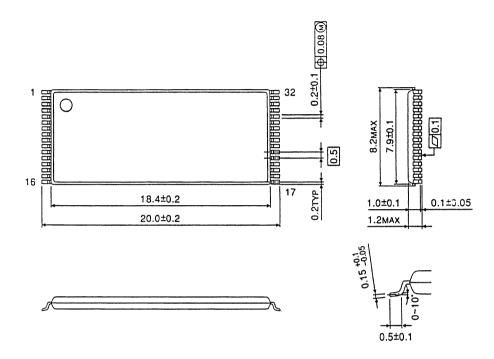

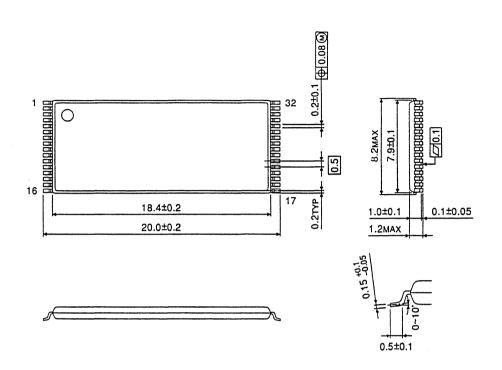

**Outline Drawing**

DIP28-P-600 Unit in mm

Weight: 4.42g (Typ.)

Unit in mm

### **Outline Drawing**

SOP28-P-450

Weight: 0.79g (Typ.)

#### **Outline Drawing**

TSOP28-P

Unit in mm

Weight: 0.22g (Typ.)

<sup>1.</sup> This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

<sup>2.</sup> LIFE SUPPORT POLICY

Toshiba products described in this document are not authorized for use as critical components in life support systems without the written consent of the appropriate officer of Toshiba America, Inc. Life support systems are either systems intended for surgical implant in the body or systems which sustain life.

A critical component in any component of a life support system whose failure to perform may cause a malfunction of the life support system, or may affect its safety or effectiveness.

<sup>3.</sup> The information in this document has been carefully checked and is believed to be reliable; however no responsibility can be assumed for inaccuracies that may not have been caught. All information in this data book is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

## TOSHIBA

### TC55257DPI/DFI/DFTI-70V/85V

#### **PRELIMINARY**

#### SILICON GATE CMOS

#### 32.768 WORD x 8 BIT STATIC RAM

#### Description

The TC55257DPI is a 262,144 bit static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 2.7 ~ 5.5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mA/MHz (typ.) and a minimum cycle time of 70ns.

When  $\overline{CE}$  is a logical high, the device is placed in a low power standby mode in which the standby current is 0.3µA typically. The TC55257DPI has two control inputs, Chip Enable (CE) allows for device selection and data retention control, while an Output Enable input (OE) provides fast memory access. The TC55257DPI is suitable for use in microprocessor application systems where high speed, low power, and battery backup are required. The TC55257DPI is guaranteed over an operating temperature range of -40 ~ 85°C so the TC55257DPI is suitable for use in wide operating temperature systems.

The TC55257DPI is offered in a standard dual-in-line 28-pin plastic package (0.6 inch width), a small outline plastic package, and a thin small outline plastic package (forward type).

#### **Features**

Low power dissipation:

27.5mW/MHz (tvp.)

Standby current:

$2\mu A$  (max.) at  $Ta = 25^{\circ}C$

• Single 2.7 ~ 5.5V power supply

Access time (max.)

|                | 5V±       | 10%  | 2.7 ~ | 5.5V  |  |

|----------------|-----------|------|-------|-------|--|

|                | -70V -85V |      | -70V  | -85V  |  |

| Access Time    | 70ns      | 85ns | 120ns | 150ns |  |

| CE Access Time | 70ns      | 85ns | 120ns | 150ns |  |

| OE Access Time | 35ns      | 45ns | 70ns  | 75ns  |  |

Power down feature:

CE

• Data retention supply voltage:

$2.0 \sim 5.5 \text{V}$

Inputs and outputs directly TTL compatible

• Wide operating temperature: -40 ~ 85°C

Package

TC55257DPI

: DIP28-P-600

TC55257DFI

: SOP28-P-450

TC55257DFTI

: TSOP28-P

#### Pin Names

| A0 ~ A14        | Address Inputs           |

|-----------------|--------------------------|

| R/W             | Read/Write Control Input |

| ŌĒ              | Output Enable Input      |

| CE              | Chip Enable Input        |

| I/O1 ~ I/O8     | Data Input/Output        |

| V <sub>DD</sub> | Power (+5V)              |

| GND             | Ground                   |

#### A6 []4 A5 [ 5 A4 [] 6 A3 🛛 7

A14 0 1

A12 42

A7 [ 3

23 A11 22 OE 21 A10 A2 48 20 CE A0 0 10 19 1/08 1/01 11 1/02 12 17 1/06 16 1/05 1/03 413 GND 4

o 28 PIN DIP & SOP

28 VOD

27 R/W

26 A13

24 D A9

#### o 28 PIN TSOP

(forward type)

### **TSOP Pinout**

|   | PIN NO.  | 1              | 2               | 3              | 4                | 5               | 6    | 7        | 8               | 9               | 10             | 11             | 12             | 13             | 14              |

|---|----------|----------------|-----------------|----------------|------------------|-----------------|------|----------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|

| - | PIN NAME | ŌĒ             | A <sub>11</sub> | A <sub>9</sub> | . A <sub>8</sub> | A <sub>13</sub> | R/W  | $V_{DD}$ | A <sub>14</sub> | A <sub>12</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>  |

|   | PIN NO.  | 15             | 16              | 17             | 18               | 19              | 20   | 21       | 22              | 23              | 24             | 25             | 26             | 27             | 28              |

|   | PIN NAME | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | 1/01             | 1/02            | 1/03 | GND      | 1/04            | 1/05            | 1/06           | 1/07           | I/O8           | CE             | A <sub>10</sub> |

#### **Block Diagram**

#### **Operating Mode**

| OPERATION MODE  | CE | ŌĒ | R/W | I/01 ~ I/08      | POWER            |

|-----------------|----|----|-----|------------------|------------------|

| Read            | L  | L  | Н   | D <sub>OUT</sub> | I <sub>DDO</sub> |

| Write           | L  | *  | L   | D <sub>IN</sub>  | I <sub>DDO</sub> |

| Output Deselect | L  | Н  | Н   | High-Z           | I <sub>DDO</sub> |

| Standby         | Н  | *  | *   | High-Z           | I <sub>DDS</sub> |

$<sup>^{*}</sup>$  H or L

### **Maximum Ratings**

| SYMBOL              | ITEM                         | RATING                        | UNIT |

|---------------------|------------------------------|-------------------------------|------|

| V <sub>DD</sub>     | Power Supply Voltage         | -0.3 ~ 7.0                    | V    |

| V <sub>IN</sub>     | Input Voltage                | -0.3* ~ 7.0                   | ٧    |

| V <sub>I/O</sub>    | Input and Output Voltage     | -0.5* ~ V <sub>DD</sub> + 0.5 | ٧    |

| P <sub>D</sub>      | Power Dissipation            | 1.0/0.6**                     | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                           | °C   |

| T <sub>STRG</sub>   | Storage Temperature          | -55 ~ 150                     | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | -40 ~ 85                      | °C   |

<sup>\* -3.0</sup>V at pulse width 50ns

<sup>\*\*</sup> SOP

### DC Recommended Operating Conditions (Ta = -40 ~ 85°C)

| SYMBOL          | PARAMETER                     | 5V ± 10% |      |                       | :                     | UNIT |                       |       |

|-----------------|-------------------------------|----------|------|-----------------------|-----------------------|------|-----------------------|-------|

|                 | TAIRMETEN                     | MIN.     | TYP. | MAX.                  | MIN.                  | MIN. | MAX.                  | 01111 |

| V <sub>DD</sub> | Power Supply Voltage          | 4.5      | _    | 5.5                   | 2.7                   | _    | 5.5                   |       |

| V <sub>IH</sub> | Input High Voltage            | 2.4      | -    | V <sub>DD</sub> + 0.3 | V <sub>DD</sub> - 0.2 | -    | V <sub>DD</sub> + 0.3 | \/    |

| V <sub>IL</sub> | Input Low Voltage             | -0.3*    | _    | 0.6                   | -0.3*                 | -    | 0.2                   | V     |

| $V_{DH}$        | Data Retention Supply Voltage | 2.0      | _    | 5.5                   | 2.0                   | _    | 5.5                   |       |

<sup>\* -3.0</sup>V at pulse width at 50ns Max.

### DC and Operating Characteristics (Ta = -40 ~ 85°C, $V_{DD}$ = 5V±10%)

| SYMBOL            | PARAMETER              | TEST CONDITION                                                                                      |                                 |     | TYP. | MAX. | UNIT |

|-------------------|------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|-----|------|------|------|

| lLi               | Input Leakage Current  | $V_{IN} = 0 \sim V_{DD}$                                                                            |                                 | -   | -    | ±1.0 | μА   |

| I <sub>LO</sub>   | Output Leakage Current | $\overline{CE} = V_{IH}$ or R/W = $V_{IL}$ or $\overline{OE} = V_{IH}$<br>$V_{OUT} = 0 \sim V_{DD}$ |                                 |     | -    | ±1.0 | μΑ   |

| I <sub>OH</sub>   | Output High Current    | V <sub>OH</sub> = 2.4V                                                                              |                                 |     | _    | _    | mA   |

| l <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.4V                                                                              |                                 | 4.0 | _    | -    | mA   |

|                   | Operating Current      | CE = V <sub>IL,</sub> R/W = V <sub>IH</sub>                                                         | t <sub>cycle</sub> = 1μs        | _   | 10   | _    |      |

| I <sub>DDO1</sub> |                        | Other Input = V <sub>IH</sub> /V <sub>IL</sub><br>I <sub>OUT</sub> = 0mA                            | t <sub>cycle</sub> = Min. cycle | -   | _    | 70   | mA   |

|                   |                        | $\overline{CE} = 0.2V$ , R/W = $V_{DD} - 0.2V$                                                      | t <sub>cycle</sub> = 1μs        | 1   | 5    | _    | 111/ |

| I <sub>DDO2</sub> |                        | Other Input = $V_{DD}$ - 0.2V/0.2V<br>$I_{OUT}$ = 0mA                                               | t <sub>cycle</sub> = Min. cycle | _   | _    | 60   |      |

| I <sub>DDS1</sub> |                        | CE = V <sub>IH</sub>                                                                                |                                 | _   | _    | 3    | mA   |

| I <sub>DDS2</sub> | Standby Current        | <del>CE</del> = V <sub>DD</sub> - 0.2V                                                              | Ta = -40 ~ 85°C                 | _   | _    | 30   |      |

|                   |                        | $V_{DD} = 2.0V \sim 5.5V$                                                                           | Ta = 25°C                       | _   | 0.3  | 2    | μΑ   |

### DC and Operating Characteristics (Ta = -40 ~ 85°C, $V_{DD}$ = 3V $\pm$ 10%)

| SYMBOL            | PARAMETER              | 1                                                                                                     | EST CONDITIO      | N                               |        | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------------|-------------------------------------------------------------------------------------------------------|-------------------|---------------------------------|--------|------|------|------|------|

| ILI               | Input Leakage Current  | $V_{IN} = 0 \sim V_{DD}$                                                                              |                   |                                 |        | -    | _    | ±1.0 | μΑ   |

| I <sub>LO</sub>   | Output Leakage Current | $\overline{CE} = V_{IH}$ or R/W = $V_{IL}$ or $\overline{OE} = V_{IH}$ ,<br>$V_{OUT} = 0 \sim V_{DD}$ |                   |                                 | -      | -    | ±1.0 | μА   |      |

| I <sub>OH</sub>   | Output High Current    | $V_{OH} = V_{DD} - 2.0V$                                                                              |                   |                                 | -0.1   | _    | _    | mA   |      |

| I <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.2V                                                                                |                   |                                 | 0.1    | _    | -    | mA   |      |

|                   |                        | Other Input = $V_{DD}$ - 0.2V/0.2V $t_{cycle}$                                                        |                   | Min.                            | -      | _    | 20   |      |      |

| I <sub>DDO2</sub> | Operating Current      |                                                                                                       |                   | t <sub>cycle</sub>              | 1µs    | -    | _    | 5    | mA   |

|                   |                        |                                                                                                       | $V_{DD} = 3V \pm$ | Ta = -40 ~                      | - 85°C | _    | -    | 20   |      |

|                   |                        |                                                                                                       | 10%               | Ta = 25°C                       | ;      | -    | 1    | 1.5  |      |

| I <sub>DDS2</sub> | Standby Current        | $\overline{CE} = V_{DD} - 0.2V$                                                                       |                   | Ta = -40 ~  DD = 3.0V Ta = 25°C |        | _    | _    | 2    | μА   |

|                   |                        |                                                                                                       | $V_{DD} = 3.0V$   |                                 |        | _    | _    | 1    |      |

|                   |                        |                                                                                                       |                   | Ta = -40 ~                      | - 85°C | _    | _    | 15   |      |

### Capacitance (Ta = 25°C, f = 1MHz)

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX. | UNIT |

|------------------|--------------------|------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = GND  | 10   | "F   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10   | pF   |

Note: This parameter is periodically sampled and is not 100% tested.

### AC Characteristics (Ta = -40 ~ 85°C, $V_{DD}$ = 5V $\pm$ 10%)

### Read Cycle

| SYMBOL           | PARAMETER                         | -70V |      | -85V |      | UNIT |

|------------------|-----------------------------------|------|------|------|------|------|

|                  |                                   | MIN. | MAX. | MIN. | MAX. |      |

| t <sub>RC</sub>  | Read Cycle Time                   | 70   | -    | 85   | -    |      |

| t <sub>ACC</sub> | Address Access Time               | _    | 70   | _    | 85   |      |

| t <sub>CO</sub>  | CE Access Time                    | _    | 70   |      | 85   |      |

| t <sub>OE</sub>  | Output Enable to Output in Valid  | _    | 35   | _    | 45   |      |

| t <sub>COE</sub> | Chip Enable to Output in Low-Z    | 5    | _    | 5    | _    | ns   |

| t <sub>OEE</sub> | Output Enable to Output in Low-Z  | 0    | -    | 0    | _    |      |

| t <sub>OD</sub>  | Chip Enable to Output in High-Z   | _    | 25   | _    | 30   |      |

| t <sub>ODO</sub> | Output Enable to Output in High-Z | _    | 25   | _    | 30   |      |

| t <sub>OH</sub>  | Output Data Hold Time             | 10   | _    | 10   | _    |      |

### Write Cycle

| SYMBOL           | PARAMETER                      | -70V |      | -85V |      | UNIT |

|------------------|--------------------------------|------|------|------|------|------|

|                  |                                | MIN. | MAX. | MIN. | MAX. |      |

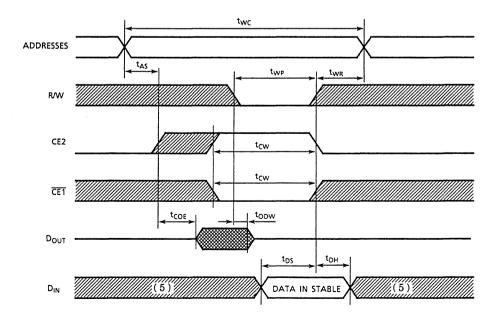

| t <sub>WC</sub>  | Write Cycle Time               | 70   | -    | 85   | -    |      |

| t <sub>WP</sub>  | Write Pulse Width              | 50   | _    | 60   | _    |      |

| t <sub>CW</sub>  | Chip Selection to End of Write | 60   | -    | 65   | -    |      |

| t <sub>AS</sub>  | Address Setup Time             | 0    | _    | 0    | _    |      |

| t <sub>WR</sub>  | Write Recovery Time            | 0    | _    | 0    | -    | ns   |

| t <sub>ODW</sub> | R/W to Output in High-Z        | _    | 25   | _    | 30   |      |

| t <sub>OEW</sub> | R/W to Output in Low-Z         | 0    | _    | 0    | _    |      |

| t <sub>DS</sub>  | Data Setup Time                | 30   | _    | 40   | _    |      |

| t <sub>DH</sub>  | Data Hold Time                 | 0    | _    | 0    | _    |      |

### **AC Test Conditions**

| Input Pulse Levels                        | 2.6V/0.4V                                                                                         |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|

| Input Pulse Rise and Fall Time            | 5ns                                                                                               |

| Input Timing Measurement Reference Level  | 1.5V                                                                                              |

| Output Timing Measurement Reference Level | 1.5V                                                                                              |

| Output Load                               | 1 TTL Gate and C <sub>L</sub> = 30pF (-55V)<br>1 TTL Gate and C <sub>L</sub> = 100pF (-70V, -85V) |

### AC Characteristics (Ta = -40 $\sim 85^{\circ}$ C, $V_{DD}$ = 2.7 $\sim 5.5$ V)

### Read Cycle

| SYMBOL           | PARAMETER                         | -70V |      | -85V |      | UNIT |

|------------------|-----------------------------------|------|------|------|------|------|

|                  |                                   | MIN. | MAX. | MIN. | MAX. |      |

| t <sub>RC</sub>  | Read Cycle Time                   | 120  | -    | 150  | _    |      |

| t <sub>ACC</sub> | Address Access Time               | _    | 120  | _    | 150  |      |

| t <sub>CO</sub>  | CE Access Time                    | _    | 120  | _    | 150  |      |

| t <sub>OE</sub>  | Output Enable to Output in Valid  | _    | 70   | -    | 75   |      |

| t <sub>COE</sub> | Chip Enable to Output in Low-Z    | 5    | _    | 5    | _    | ns   |

| toee             | Output Enable to Output in Low-Z  | 0    | _    | 0    | _    |      |

| t <sub>OD</sub>  | Chip Enable to Output in High-Z   | _    | 50   | _    | 50   |      |

| t <sub>ODO</sub> | Output Enable to Output in High-Z | _    | 50   | -    | 50   |      |

| t <sub>OH</sub>  | Output Data Hold Time             | 10   | _    | 10   | _    |      |

### Write Cycle

| SYMBOL           | PARAMETER                      | -70V |      | -85V |      | UNIT |

|------------------|--------------------------------|------|------|------|------|------|

|                  |                                | MIN. | MAX. | MIN. | MAX. |      |

| t <sub>WC</sub>  | Write Cycle Time               | 120  | _    | 150  | -    |      |

| t <sub>WP</sub>  | Write Pulse Width              | 80   | _    | 100  | _    | 1    |

| t <sub>CW</sub>  | Chip Selection to End of Write | 100  | _    | 120  | -    |      |

| t <sub>AS</sub>  | Address Setup Time             | 0    | _    | 0    | _    | ]    |

| t <sub>WR</sub>  | Write Recovery Time            | 0    | -    | 0    | _    | ns   |

| t <sub>ODW</sub> | R/W to Output in High-Z        | _    | 50   | -    | 50   |      |

| toew             | R/W to Output in Low-Z         | 0    | _    | 0    | _    |      |

| t <sub>DS</sub>  | Data Setup Time                | 50   | -    | 60   | _    |      |

| t <sub>DH</sub>  | Data Hold Time                 | 0    | _    | 0    | _    |      |

### **AC Test Conditions**

| Input Pulse Levels                         | V <sub>DD</sub> - 0.2V/0.2V          |

|--------------------------------------------|--------------------------------------|

| Input Pulse Rise and Fall Time             | 5ns                                  |

| Input Timing Measurement Reference Level   | 1.5V                                 |

| Output Timing Measurement Reference Levels | 1.5V                                 |

| Output Load                                | C <sub>L</sub> = 100pF (Include Jig) |

### **Timing Waveforms**

### Read Cycle (1)

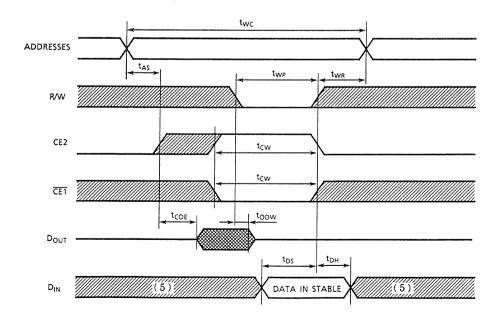

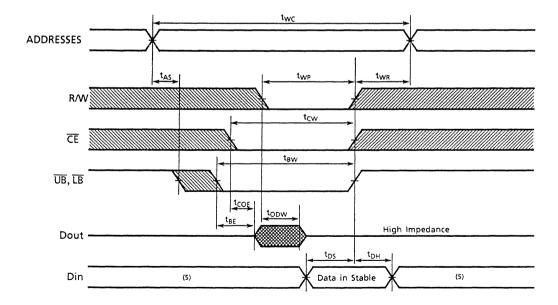

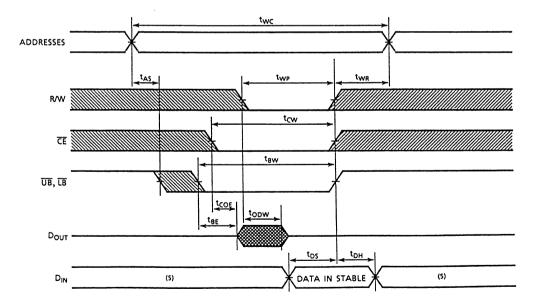

### Write Cycle 1 (4) (R/W Controlled Write)

### Write Cycle 2 (4) (CE Controlled Write)

#### Notes:

- 1. R/W is High for read cycle.

- 2. Assuming that the  $\overline{\text{CE}}$  Low transition occurs coincident with or after the R/W Low transition, Outputs remain in a high impedance state.

- 3. Assuming that  $\overline{\text{CE}}$  High transition occurs coincident with or prior to the R/W High transition, Outputs remain in a high impedance state.

- 4. Assuming that  $\overline{OE}$  is High for a Write Cycle, Outputs are in a high impedance state during this period.

- 5. The I/O may be in the output state during this time, input signals of opposite phase must not be applied.

### Data Retention Characteristics (Ta = -40 ~ 85°C)

| SYMBOL           | PARAMETER                            |                        | MIN.               | TYP. | MAX. | UNIT |

|------------------|--------------------------------------|------------------------|--------------------|------|------|------|

| V <sub>DH</sub>  | Data Retention Supply Voltage        |                        | 2.0                | -    | 5.5  | ٧    |

| 1                | Standby Cyrrent                      | V <sub>DH</sub> = 3.0V | _                  | _    | 15*  |      |

| DDS2             | Standby Current $V_{DH} = 5.5V$      |                        | _                  | -    | 30   | μΑ   |

| t <sub>CDR</sub> | Chip Deselect to Data Retention Mode |                        | 0                  | -    | _    |      |

| t <sub>R</sub>   | Recovery Time                        |                        | t <sub>RC(1)</sub> | -    | _    | ns   |

Note (1): Read Cycle Time

\*  $2\mu A$  (max.)  $Ta = -40 \sim 40^{\circ} C$

### **CE** Controlled Data Retention Mode

Note (2): If the  $V_{IH}$  of  $\overline{CE}$  is 2.4V in operation,  $I_{DDS1}$  current flows during the period that the  $V_{DD}$  voltage is going down from 4.5V to 2.6V.

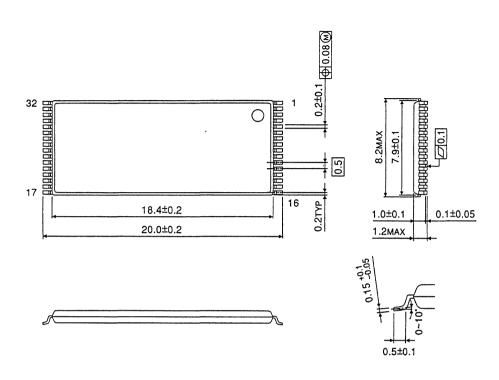

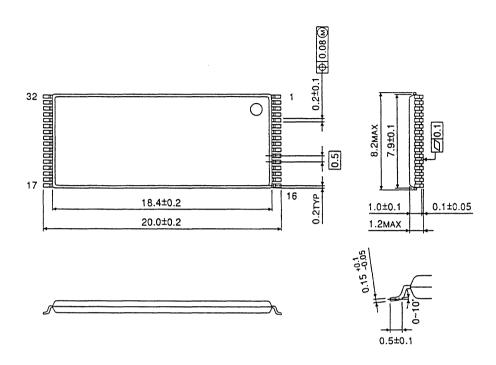

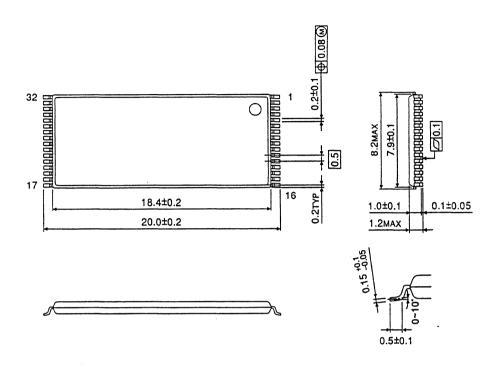

Unit in mm

### **Outline Drawing**

DIP28-P-600

Weight: 4.42g (Typ.)

SOP28-P-450

Unit in mm

Weight: 0.79g (Typ.)

TSOP29-P

Unit in mm

A. Standard Static RAM

0.5±0.1

Weight: 0.22g (Typ.)

**Notes**

<sup>1.</sup> This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

<sup>2.</sup> LIFE SUPPORT POLICY

Toshiba products described in this document are not authorized for use as critical components in life support systems without the written consent of the appropriate officer of Toshiba America, Inc. Life support systems are either systems intended for surgical implant in the body or systems which sustain life.

A critical component in any component of a life support system whose failure to perform may cause a malfunction of the life support system, or may affect its safety or effectiveness.

<sup>3.</sup> The information in this document has been carefully checked and is believed to be reliable; however no responsibility can be assumed for inaccuracies that may not have been caught. All information in this data book is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

# TC55257DPL/DFL/DFTL-55V/70V/85V

#### SILICON GATE CMOS

**PRELIMINARY**

#### 32.768 WORD x 8 BIT STATIC RAM

#### Description

The TC55257DPL is a 262,144 bit static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 2.7 ~ 5.5V power supply. Advanced circuit techniques provide both high speed and low power features with an operating current of 5mA/MHz (typ.) and a minimum cycle time of 55ns.

When  $\overline{CE}$  is a logical high, the device is placed in a low power standby mode in which the standby current is 0.3uA at room temperature. The TC55257DPL has two control inputs. Chip Enable (CE) allows for device selection and data retention control, while an Output Enable input (OE) provides fast memory access. The TC55257DPL is suitable for use in microprocessor application systems where high speed, low power, and battery backup are required.

The TC55257DPL is offered in a standard dual-in-line 28-pin plastic package (0.6 inch width), a small outline plastic package, and a thin small outline plastic package (forward type).

#### Features

#### Pin Connection (Top View)

• Low power dissipation:

27.5mW/MHz (tvp.)

• Standby current:

$2\mu A$  (max.) at  $Ta = 25^{\circ}C$

- Single 2.7 ~ 5.5V power supply

- Access time (max.)

|                   |      | 5V ± 10% | 2.7 ~ 5.5V |              |

|-------------------|------|----------|------------|--------------|

|                   | -55V | -70V     | -85V       | -55V/70V/85V |

| Access<br>Time    | 70ns | 85ns     | 100ns      | 150ns        |

| CE Access<br>Time | 70ns | 85ns     | 100ns      | 150ns        |

| OE Access<br>Time | 35ns | 45ns     | 50ns       | 75ns         |

o 28 PIN DIP & SOP

| 20   | PIIN | DIP & SUP          |

|------|------|--------------------|

|      |      | ~                  |

| A14  |      | 28 V <sub>DD</sub> |

| A12  |      | 27 🛭 R/W           |

| Α7   |      | 26 A13             |

| A6   |      | 25 A8              |

| A5   |      | 24 D A9            |

| A4   |      | 23 A11             |

| А3   |      | 22 DE              |

| A2   |      | 21 A10             |

| A1   |      | 20 CE              |

|      | 9 10 | 19 🖟 1/08          |

| 1/01 |      | 18 🖟 1/07          |

| 1/02 |      | 17 🖟 1/06          |

| 1/03 |      | 16 1/05            |

| GND  | 914  | 15 1/04            |

|      | _    |                    |

o 28 PIN TSOP (forward type)

- Power down feature: CE

- Data retention supply voltage: 2.0 ~ 5.5V

- Inputs and outputs TTL compatible

- Package TC55257DPL: DIP28-P-600

: SOP28-P-450 TC55257DFL TC55257DFTL : TSOP28-P

#### Pin Names

| A0 ~ A14        | Address Inputs           |

|-----------------|--------------------------|

| R/W             | Read/Write Control Input |

| ŌĒ              | Output Enable Input      |

| CE              | Chip Enable Input        |

| I/O1 ~ I/O8     | Data Input/Output        |

| V <sub>DD</sub> | Power                    |

| GND             | Ground                   |

#### **TSOP Pinout**

| PIN NO.  | 1              | 2               | 3              | 4              | 5               | 6    | 7        | 8               | 9               | 10             | 11             | 12             | 13             | 14              |

|----------|----------------|-----------------|----------------|----------------|-----------------|------|----------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|

| PIN NAME | ŌĒ             | A <sub>11</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>13</sub> | R/W  | $V_{DD}$ | A <sub>14</sub> | A <sub>12</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>  |

| PIN NO.  | 15             | 16              | 17             | 18             | 19              | 20   | 21       | 22              | 23              | 24             | 25             | 26             | 27             | 28              |

| PIN NAME | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | 1/01           | 1/02            | 1/03 | GND      | 1/04            | 1/05            | 1/06           | 1/07           | 1/08           | CE             | A <sub>10</sub> |

#### **Block Diagram**

#### **Operating Mode**

| OPERATION MODE  | CE | ŌĒ | R/W | I/01 ~ I/08      | POWER            |

|-----------------|----|----|-----|------------------|------------------|

| Read            | L  | L  | Н   | D <sub>OUT</sub> | I <sub>DDO</sub> |

| Write           | L  | *  | L   | D <sub>IN</sub>  | I <sub>DDO</sub> |

| Output Deselect | L  | Н  | Н   | High-Z           | I <sub>DDO</sub> |

| Standby         | Н  | *  | *   | High-Z           | I <sub>DDS</sub> |

<sup>\*</sup> H or L

#### **Maximum Ratings**

| SYMBOL                                | ITEM                         | RATING                        | UNIT |

|---------------------------------------|------------------------------|-------------------------------|------|

| V <sub>DD</sub>                       | Power Supply Voltage         | -0.3 ~ 7.0                    | ٧    |

| V <sub>IN</sub>                       | Input Voltage                | -0.3* ~ 7.0                   | V    |

| V <sub>I/O</sub>                      | Input and Output Voltage     | -0.5* ~ V <sub>DD</sub> + 0.5 | ٧    |

| P <sub>D</sub>                        | Power Dissipation            | 1.0/0.6**                     | W    |

| T <sub>SOLDER</sub>                   | Soldering Temperature (10 s) | 260                           | °C   |

| T <sub>STRG</sub> Storage Temperature |                              | -55 ~ 150                     | °C   |

| T <sub>OPR</sub>                      | Operating Temperature        | 0 ~ 70                        | °C   |

<sup>\* -3.0</sup>V at pulse width 50ns

<sup>\*\*</sup> SOP

#### DC Recommended Operating Conditions (Ta = $0 \sim 70^{\circ}$ C)

| SYMBOL          | PARAMETER                     |       | 5V ± 10 | )%                    |                       | UNIT |                       |       |  |

|-----------------|-------------------------------|-------|---------|-----------------------|-----------------------|------|-----------------------|-------|--|

| OTTINDOL        | TANAMETER                     | MIN.  | TYP.    | MAX.                  | MIN.                  | MIN. | MAX.                  | 01111 |  |

| $V_{DD}$        | Power Supply Voltage          | 4.5   | 5.0     | 5.5                   | 2.7                   | -    | 5.5                   |       |  |

| V <sub>IH</sub> | Input High Voltage            | 2.4   | -       | V <sub>DD</sub> + 0.3 | V <sub>DD</sub> - 0.2 | -    | V <sub>DD</sub> + 0.3 | v     |  |

| V <sub>IL</sub> | Input Low Voltage             | -0.3* | _       | 0.6                   | -0.3*                 | -    | 0.2                   | V     |  |

| V <sub>DH</sub> | Data Retention Supply Voltage | 2.0   | -       | 5.5                   | 2.0                   | -    | 5.5                   |       |  |

<sup>\* -3.0</sup>V at pulse width at 50ns Max.

# DC and Operating Characteristics (Ta = 0 ~ 70°C, $V_{DD}$ = 5V±10%)

| SYMBOL            | PARAMETER              | TEST COM                                                                      | IDITION                         | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------------|-------------------------------------------------------------------------------|---------------------------------|------|------|------|------|

| lLI               | Input Leakage Current  | V <sub>IN</sub> = 0 ~ V <sub>DD</sub>                                         |                                 | -    | _    | ±1.0 | μА   |

| I <sub>LO</sub>   | Output Leakage Current | $\overline{CE} = V_{IH} \text{ or R/W} = V_{IL}$<br>$V_{OUT} = 0 \sim V_{DD}$ | or $\overline{OE}$ = $V_IH$     | -    | -    | ±1.0 | μА   |

| loh               | Output High Current    | V <sub>OH</sub> = 2.4V                                                        | V <sub>OH</sub> = 2.4V          |      |      | _    | mA   |

| l <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.4V                                                        | V <sub>OL</sub> = 0.4V          |      |      |      | mA   |

| _                 |                        | CE = V <sub>IL</sub> , R/W = V <sub>IH</sub>                                  | t <sub>cycle</sub> = 1μs        | -    | 10   | -    |      |

| I <sub>DDO1</sub> |                        | Other Input = V <sub>IH</sub> /V <sub>IL</sub><br>I <sub>OUT</sub> = 0mA      | t <sub>cycle</sub> = Min. cycle | _    | -    | 70   |      |

|                   | Operating Current      | CE = 0.2V                                                                     | t <sub>cycle</sub> = 1μs        | _    | 5    | -    | mA   |

| I <sub>DDO2</sub> | Operating ourient      | $R/W = V_{DD} - 0.2V$ Other Input $= V_{DD} - 0.2V/0.2V$ $I_{OUT} = 0mA$      | t <sub>cycle</sub> = Min. cycle | _    | _    | 60   |      |

| I <sub>DDS1</sub> |                        | CE = V <sub>IH</sub>                                                          |                                 | -    | -    | 3    | mA   |

|                   | Standby Current        | $\overline{CE} = V_{DD} - 0.2V$                                               | Ta = -40 ~ 85°C                 | -    | -    | 20   |      |

|                   |                        | $V_{DD} = 2.0V \sim 5.5V$                                                     | Ta = 25°C                       | _    | 0.3  | 2    | μA   |

DC and Operating Characteristics (Ta = -0 ~ 70°C,  $V_{DD}$  = 3V±10%)

| SYMBOL            | PARAMETER              | 1                                                                                                     |                          | MIN.           | TYP.  | MAX. | UNIT |      |    |

|-------------------|------------------------|-------------------------------------------------------------------------------------------------------|--------------------------|----------------|-------|------|------|------|----|

| ILI               | Input Leakage Current  | $V_{IN} = 0 \sim V_{DD}$                                                                              |                          |                |       |      |      | ±1.0 | μΑ |

| I <sub>LO</sub>   | Output Leakage Current | $\overline{CE} = V_{IH}$ or R/W = $V_{IL}$ or $\overline{OE} = V_{IH}$ ,<br>$V_{OUT} = 0 \sim V_{DD}$ |                          |                |       | -    | _    | ±1.0 | μА |

| I <sub>OH</sub>   | Output High Current    | V <sub>OH</sub> = V <sub>DD</sub> - 2.0V                                                              |                          |                |       |      | -    | -    | mA |

| l <sub>OL</sub>   | Output Low Current     | V <sub>OL</sub> = 0.2V                                                                                |                          |                |       | 0.1  | -    | _    | mA |

| I <sub>DDO2</sub> | Operating Current      | CE = 0.2V<br>R/W = V <sub>DD</sub> = 2.0                                                              | t <sub>cycle</sub>       | Min.           | -   - | 20   | mA   |      |    |

|                   | oporating duriont      | Other Input = V <sub>D</sub><br>I <sub>OUT</sub> = 0mA                                                | <sub>D</sub> - 0.2V/0.2V | Cycle          | 1μs   | -    |      | 5    |    |

|                   |                        |                                                                                                       | $V_{DD} = 3V$            | Ta = -0 ~ 70°C |       | -    | _    | 15   |    |

|                   |                        |                                                                                                       | ± 10%                    | Ta = 25°C      |       | -    | 1    | 1.5  | μА |

| I <sub>DDS2</sub> | Standby Current        | $\overline{CE} = V_{DD} - 0.2V$<br>or $CE2 = 0.2V$                                                    |                          | Ta = 0 ~ 70°C  |       | -    | -    | 10   |    |

|                   |                        | 0. SEE = 0.2V                                                                                         | $V_{DD} = 3.0V$          | Ta = 0 ~ 40°C  |       | -    | -    | 2    |    |

|                   |                        |                                                                                                       |                          | Ta = 25°C      |       | -    | -    | 1    |    |

### Capacitance (Ta = 25°C, f = 1MHz)

**PRELIMINARY**

| SYMBOL           | PARAMETER          | TEST CONDITION         | MAX. | UNIT |

|------------------|--------------------|------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = GND  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = GND | 10   | PΓ   |

Note: This parameter is periodically sampled and is not 100% tested.

# AC Characteristics (Ta = 0 ~ 70°C, $V_{DD}$ = 5V $\pm$ 10%)

## **Read Cycle**

|                  |                                   | TC55257DPL/DFTL |      |      |      |      |      |      |  |