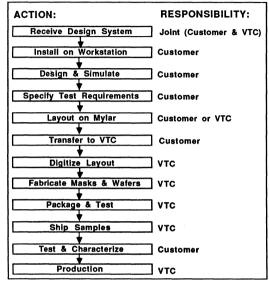

## HIGH-PERFORMANCE INTEGRATED CIRCUITS

# DATA BOOK AND APPLICATIONS MANUAL

- CMOS A·C·T Interface Logic Family

- Linear Signal Processing Circuits

- Analog Master Chips

- Linear/Digital Bipolar Cell Library

- High-Performance Digital Bipolar Cell Library

On the Silicon Frontier...™

# HIGH-PERFORMANCE INTEGRATED CIRCUITS

# DATA BOOK AND APPLICATIONS MANUAL

- CMOS A·C·T Interface Logic Family

- Linear Signal Processing Circuits

- Analog Master Chips

- Linear/Digital Bipolar Cell Library

- High-Performance Digital Bipolar Cell Library

All VTC products have input and output circuits that protect against damage due to high static voltages or electrostatic fields. However, VTC still recommends following normal ESD precautions for handling semiconductor devices.

VTC Incorporated reserves the right to make changes to its products without notice in order to improve design or performance, and assumes no responsibility for use of any circuits described or represented other than the circuitry embodied in VTC's products.

Copyright © 1985, VTC Incorporated. All Rights Reserved. Printed in USA.

İ١

•

~

### INTRODUCTION

#### VTC INCORPORATED

VTC is a specialist manufacturer of highperformance integrated circuits. The company consists of two operating divisions - Microcircuits, founded in 1967, uses advanced bipolar technology; the VHSIC Technology division, established in 1984, produces state-of-the-art CMOS products. Both operations are dedicated to the quality production of well-defined and specified high-performance circuits, focusing on highspeed and offering both standard products and semicustom services.

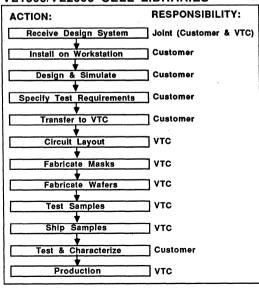

Microcircuits utilizes 2 and 3 micron bipolar technologies to produce analog, digital, and combined analog/digital functions. These include the VL1000 linear standard cell library and the VL2000 high-speed digital standard cell library. Both systems are work station based, and the 2000 offers the 300 picosecond internal gate delays of CML technology, 1500 to 5000 gate complexity, and inputs and outputs compatible with ALS, HCT, and 10KH ECL.

The VHSIC Technology division uses an advanced 1.6 micron, double level metal, N well process to produce the ACT family of interface functions and the VLSI 6000 gate array. The 6000 provides 800 picosecond internal gate delays with an on-chip maintenance system and the comprehensive Midas™ software simulation tools. It is provided in a choice of 172 pin packages - leadless chip carrier, pin grid array, or hermetic PTAB™. The division has developed a 1.2 micron double level metal P well process in both commercial and radiation-hardened flows, exhibiting hardness to a level beyond a megarad.

Both divisions are located in suburban Minneapolis, far from the costs and problems that plague semiconductor companies based in California's Silicon Valley. The company is well financed and has a complete capability to manufacture highly reliable integrated circuits.

Our designers are experienced and have the latest and best software and hardware tools to ensure a highly productive team that produces the most competitive circuits. We make our own masks in a shop equipped with E-beam technology.

VTC's manufacturing processes are the result of years of development and refinement with proven quality and reliability. Our R and D engineers and scientists will provide near-micron bipolar and submicron CMOS capability to maintain VTC's position at the leading edge of manufacturable semiconductor technology.

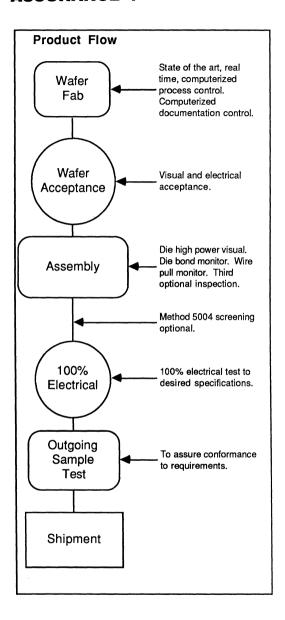

Our factories are designed for efficient, highvolume production with the most advanced manufacturing and test equipment. Our wafer fabrication areas use direct step-on-wafer fine-line photolithography; isotropic reactive ion etching to control small features; dry plasma etching; ion implantation to maintain rigid control over junction depths, profiles and transistor threshold voltages; and bias sputtered quartz to provide planar surfaces between metal layers. Rigorous process controls and cleanliness standards in class 10 clean rooms with class 1 work spaces are critical to achieving VTC's high yields in the production of complex VLSI circuits.

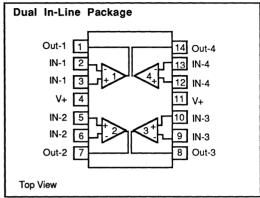

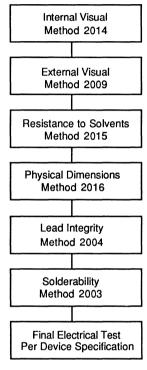

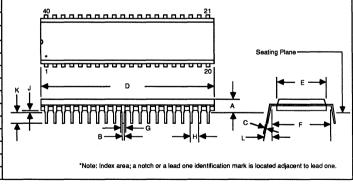

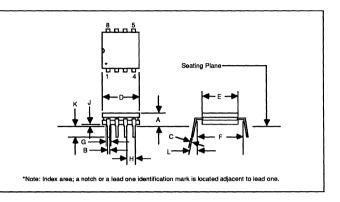

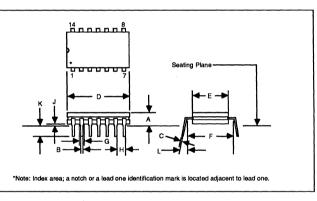

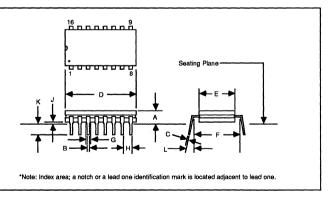

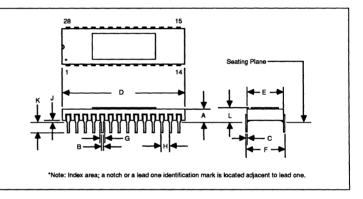

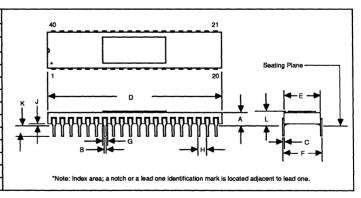

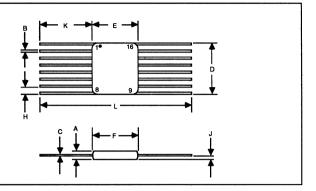

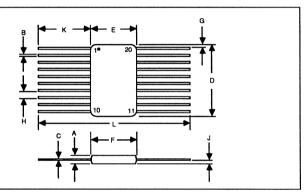

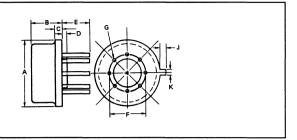

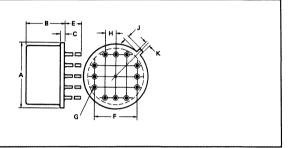

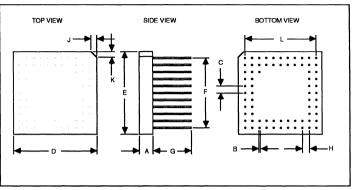

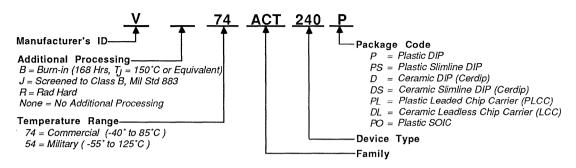

VTC's in-house packaging capability is well advanced and includes plastic and hermetic packages, dual in-line and surface mounted, from 6 to 172 pins. VTC's Tape Automated Bonding technique, PTAB™, offers a unique alternative to conventional wire bonding. Various testers are used with capabilities up to 120 pins. These include Sentry Series 80 and LTX systems, the latter having laser trim capability.

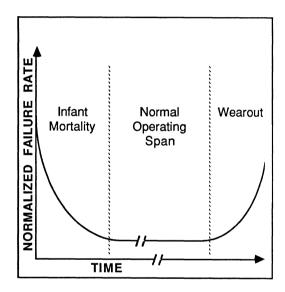

VTC's quality department has many millions of hours of operating life test data, and has the latest equipment to control vendor quality, provide process control, qualify new products, and provide critical feedback to R and D as new technology is developed.

vi

## A·C·T FAMILY APPLICATION NOTES

A·C·T FAMILY DATA SHEETS

LINEAR SIGNAL PROCESSING

BIPOLAR SEMICUSTOM

QUALITY

ORDERING AND PACKAGING

## TABLE OF CONTENTS SECTION I

| A.C. I. FAIVILY AP    | PLICATION NOTE                          | .5              |                                       |            |

|-----------------------|-----------------------------------------|-----------------|---------------------------------------|------------|

| INTRODUCTION          |                                         |                 |                                       |            |

| VTC'S ACT INTER       | FACE FAMILY                             |                 |                                       | l-vii      |

| SYSTEM DESIGN         | CONSIDERATION                           | ONS             |                                       |            |

|                       |                                         |                 |                                       | 1-1        |

| PRINTED CIRCUIT       | T BOARD CONNECTION                      | NS              |                                       |            |

| GROUND INTERC         | CONNECTION CRITERIA                     | A               |                                       | 1-1        |

| POWER DISTRIBL        | JTION ELEMENTS                          |                 |                                       | 1-3        |

| NON-PDE SUPPLY        | Y INTERCONNECTION                       | CRITERIA        |                                       | 1-6        |

| CALCULATION OF        | BYPASS CAPACITOR \                      | VALUES          |                                       | 1-7        |

| SIGNAL PROPAGA        | ATION IN TRANSMISSION                   | ON LINES        |                                       | 1-7        |

| REFLECTIONS AN        | ND LOADING                              |                 |                                       | 1-8        |

|                       |                                         |                 | S                                     |            |

| REFLECTION DIA        | GRAMS                                   |                 |                                       | 1-10       |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| REFERENCES            | • • • • • • • • • • • • • • • • • • • • |                 |                                       | 1-13       |

| DECION OACE. V        | ME DAOMOLANI                            |                 | LUTDV                                 |            |

| DESIGN CASE: V        |                                         |                 | UIIKY                                 | 0.4        |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 | · · · · · · · · · · · · · · · · · · · |            |

|                       |                                         |                 | SS LINES                              |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 | CONNECT MEDIA                         |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| 3)MICROSTE            | RIP I INFS                              |                 |                                       | 2-2        |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| CONCLUSION            |                                         |                 |                                       | 2-6        |

| REFERENCES            |                                         |                 |                                       | 2-7        |

|                       |                                         |                 |                                       |            |

| <b>POWER DISSIPAT</b> |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| 2)INTERNAL            | LOAD CADACITANCE T                      | ENI DISSIPATION |                                       | 3-3        |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| SUMMANT               |                                         |                 |                                       |            |

| AC CHARACTERI         | ISTICS OF THE V                         | ASA/7AACT INIT  | EDEACE EAMILY                         | ,          |

|                       | STICS OF THE                            | V34//4AC   114  | ENFACE FAIVIILI                       | 4.1        |

| WHAT THE SPECI        | FICATIONS IMPLY                         |                 |                                       | 4-1<br>4-1 |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| CAPACITIVE I OAD      | ), ITS EFFECT ON AC P                   | PERFORMANCE     | · · · · · · · · · · · · · · · · · · · |            |

| COMPOSITE CALC        | CULATION                                |                 | · · · · · · · · · · · · · · · · · · · | 4-5        |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

|                       |                                         |                 |                                       |            |

| CONCLUSION            |                                         |                 |                                       | 4.0        |

| DC CHARACTERISTICS OF THE V54/74ACT INTERFACE FAMILY       |             |

|------------------------------------------------------------|-------------|

| INTRODUCTION                                               | 5-1         |

| DATA SHEET SPECIFICATIONS                                  |             |

| INPUT CHARACTERISTICS                                      |             |

| INPUT PROTECTION                                           |             |

| OUTPUT CHARACTERISTICS                                     | 5-5         |

| POWER SUPPLY VOLTAGES, QUIESCENT CURRENTS, AND TEMPERATURE | 5-7         |

| ABSOLUTE MAXIMUM RATINGS                                   | 5-8         |

| CONCLUSION                                                 | 5-8         |

| CHARACTERIZATION AND SPECIFICATION OF THE                  |             |

| V54/74ACT INTERFACE FAMILY                                 |             |

| INTRODUCTION                                               | 0.4         |

| DC ELECTRICAL CHARACTERIZATION                             |             |

| AC ELECTRICAL CHARACTERIZATION                             |             |

| AC TEST JIGS AND SETUPS                                    | 6.7         |

| GROUNDING.                                                 | 6-7         |

| DECOUPLING CAPACITORS                                      | 6-R         |

| WIRING                                                     | 6-R         |

| JIG DELAY                                                  |             |

| UNIVERSAL JIG CONSTRUCTION                                 | 6-8         |

| AC TEST LOADS                                              |             |

| CORRELATION                                                |             |

|                                                            |             |

| ESD AND LATCH-UP                                           |             |

| INTRODUCTION                                               | 7-1         |

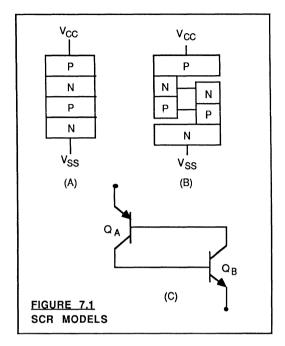

| LATCH-UP PHENOMENON                                        |             |

| DISCRETE SCR FUNCTIONING                                   |             |

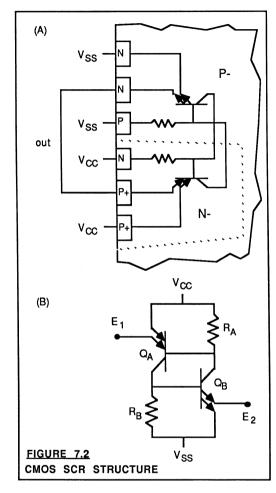

| CMOS SCR STRUCTURE                                         |             |

| LATCH-UP PREVENTION                                        |             |

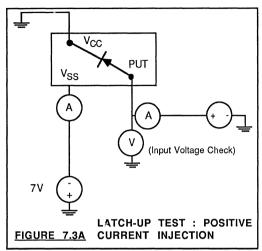

| TESTING FOR LATCH-UP.                                      | <u>7</u> -3 |

| TESTING ANALYSIS                                           | <u>7-4</u>  |

| ELECTROSTATIC DISCHARGE PROTECTION                         | 7-5         |

| COMPARISON OF THE V54/74ACT FAMILY TO 54/74LS, 54/74S,     |             |

| AND 54/74ALS INTERFACE FAMILIES                            |             |

| INTRODUCTION                                               |             |

| DC PERFORMANCE                                             |             |

| AC PERFORMANCE                                             |             |

| PERFORMANCE                                                |             |

| POWER DISSIPATION                                          |             |

| INPUT VOLTAGE CHARACTERISTICS                              |             |

| OPERATING TEMPERATURE RANGE                                | 2-0         |

| CONCLUSION                                                 | 9-Q         |

| 00110101011                                                |             |

### **FIGURES**

| 1.1A  | Ground Noise Example1-1                                           |

|-------|-------------------------------------------------------------------|

| 1.1B  | Equivalent Circuit                                                |

|       |                                                                   |

| 1.1C  | Gate Output Waveforms                                             |

| 1.2   | Ground and Supply System (2 Sided Board)                          |

| 1.3   | Top Side Links                                                    |

| 1.4   | Power Distribution Element (PDE)1-3                               |

| 1.5   | Parallel Flat conductors                                          |

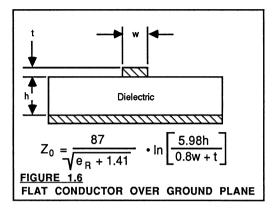

| 1.6   | Flat Conductor Over Ground Plane1-4                               |

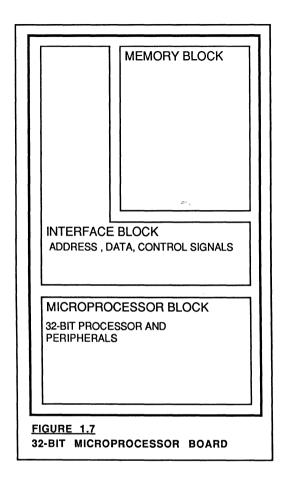

| 1.7   | 32-Bit Microprocessor Board                                       |

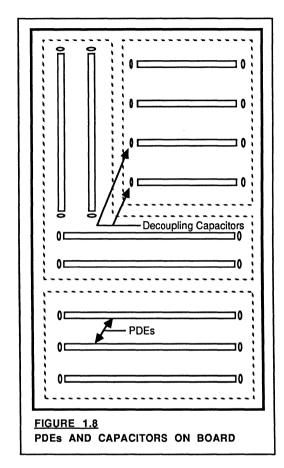

| 1.8   | PDEs and Capacitors on Board1-5                                   |

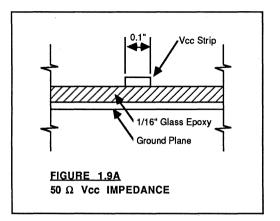

| 1.9A  | $50\Omega$ Vcc Impedance                                          |

| 1.9B  | 100Ω Vcc Impedance 1-6                                            |

| 1.9C  | $68\Omega$ Vcc Impedance                                          |

| 1.9D  | $90\Omega$ Vcc Impedance                                          |

|       | Example: Buffer Driving Line                                      |

| 1.100 | Buffer Output Waveforms                                           |

|       |                                                                   |

| 1.11  | Transmission Line                                                 |

| 1.12  | Transmission Line Geometries                                      |

| 1.13  | Gate Driving Transmission Line                                    |

| 1.14  | Reflections and Loading for Various Terminations                  |

| 1.15  | Gate Driving 120 $\Omega$ Line Reflection Diagram Low-to-High     |

| 1.16  | Gate Driving 120Ω Line Reflection Diagram High-to-Low1-11         |

| 1.17A | Crosstalk Coupling in Parallel Lines - Electrical Model           |

| 1.17B | Crosstalk Coupling in Parallel Lines - Noise Pulses at Point B    |

| 2.1   | VMEbus™ Signal Levels2-1                                          |

| 2.2   | Coaxial Cable, Twisted Pair2-2                                    |

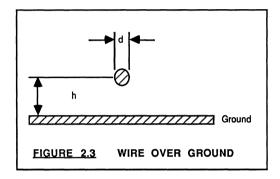

| 2.3   | Wire Over Ground2-2                                               |

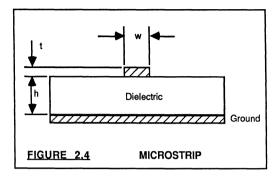

| 2.4   | Microstrip                                                        |

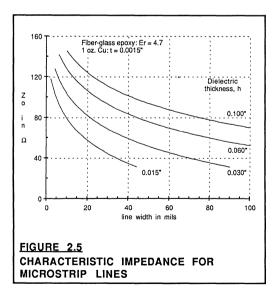

| 2.5   | Characteristic Impedance for Microstrip Lines                     |

|       | Characteristic impedance for Microstrip Lines                     |

| 2.6   | Capacitance per Unit Length for Microstrip Lines2-3               |

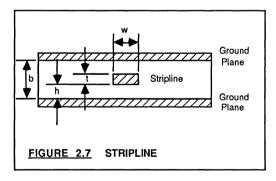

| 2.7   | Stripline         2-3                                             |

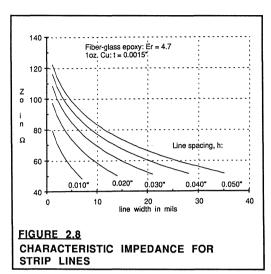

| 2.8   | Characteristic Impedance for Strip Lines                          |

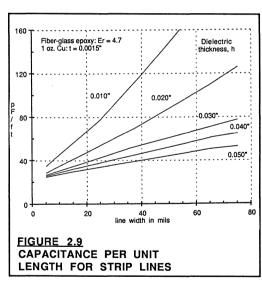

| 2.9   | Capacitance per Unit Length For Strip Lines2-4                    |

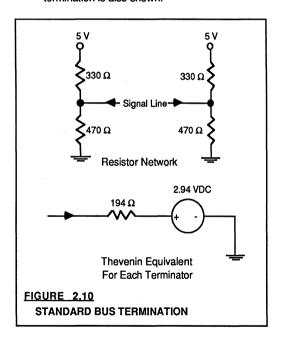

| 2.10  | Standard Bus Termination2-4                                       |

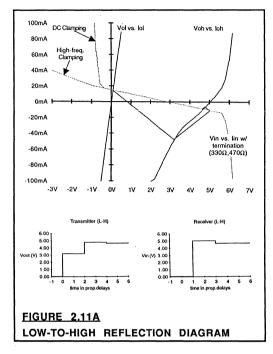

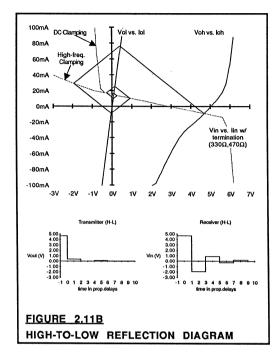

| 2.11A | Low-to-High Reflection Diagram2-5                                 |

| 2.11B | High-to-Low Reflection Diagram2-6                                 |

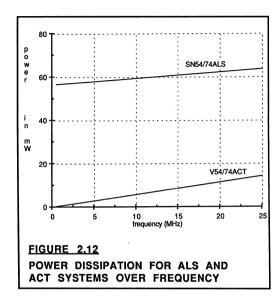

| 2.12  | Power Dissipation for ALS and ACT Systems Over Frequency          |

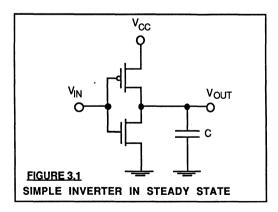

| 3.1   | Simple Inverter in Steady State                                   |

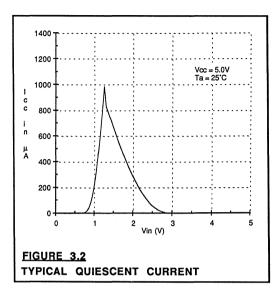

| 3.2   | Typical Quiescent Current                                         |

| 3.3   | Model of an Inverter in Transition                                |

| 3.4   | Cpd (Normalized) versus Rise Time                                 |

| 3.5   | Parasitic Internal Capacitances                                   |

|       |                                                                   |

| 3.6   | Transceiver Driving a Bus                                         |

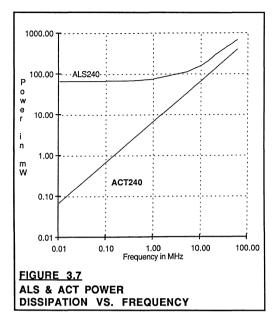

| 3.7   | ALS & ACT Power Dissipation versus Frequency                      |

| 4.1A  | 3-State Test Parameters                                           |

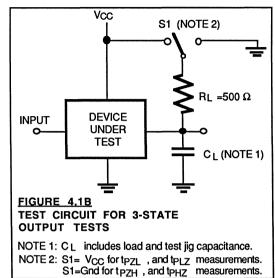

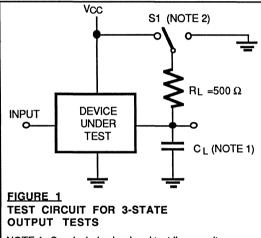

| 4.1B  | Test Circuit for 3-State Output Tests                             |

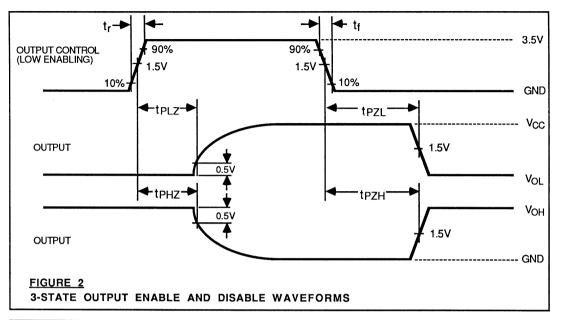

| 4.1C  | 3-State Output Enable and Disable Waveforms                       |

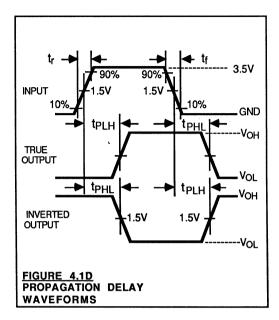

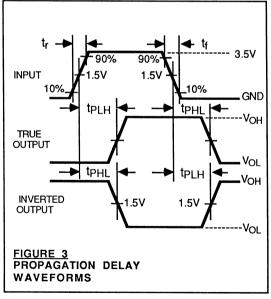

| 4.1D  | Propagation Delay Waveforms4-3                                    |

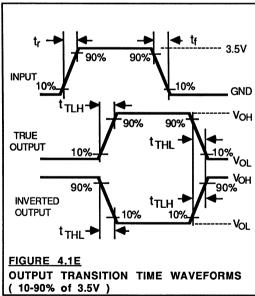

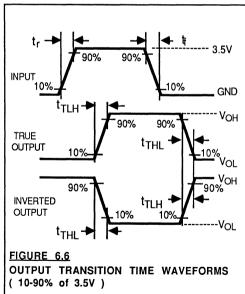

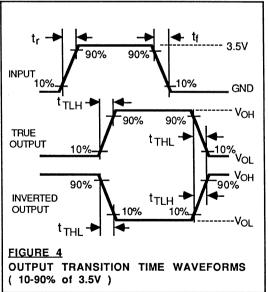

| 4.1E  | Output Transition Time Waveforms (10-90% of 3.5V)                 |

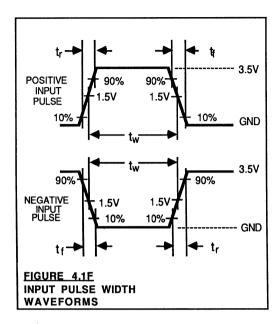

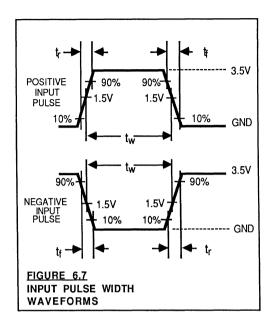

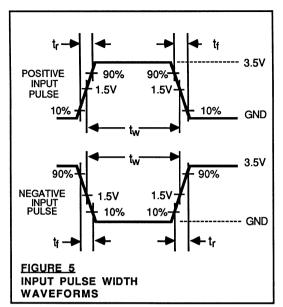

| 4.1F  | Input Pulse Width Waveforms                                       |

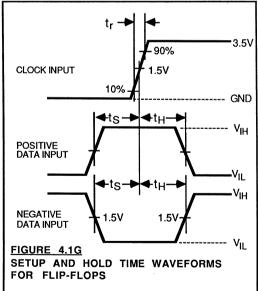

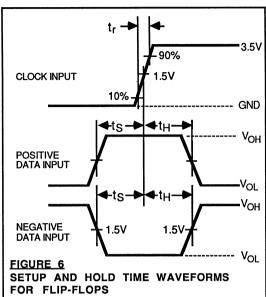

| 4.1G  | Setup and Hold Time Waveforms for Flip-Flops                      |

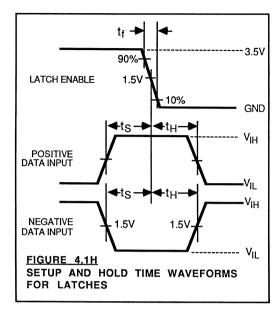

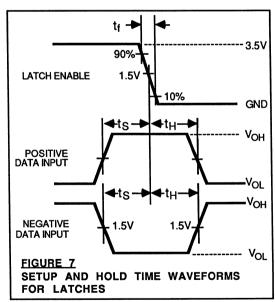

| 4.1H  | Setup and Hold Time Waveforms for Latches                         |

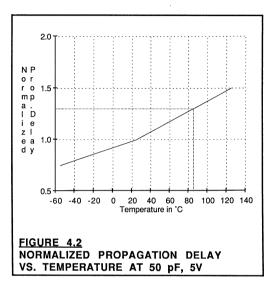

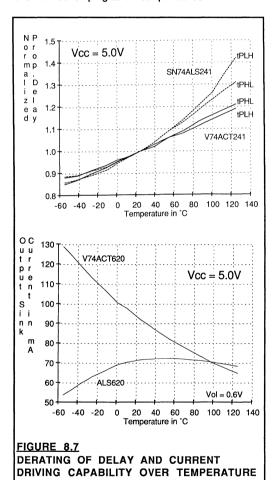

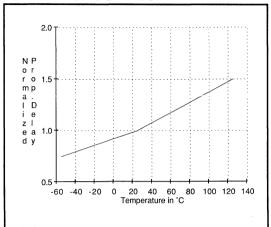

| 4.2   | Normalized Propagation Delay versus Temperature at 50 pF, 5V      |

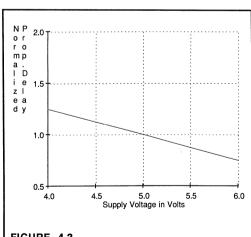

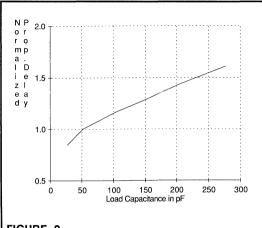

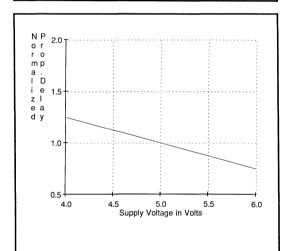

| 4.3   | Normalized Propagation Delay versus Supply Voltage at 50 pF, 25°C |

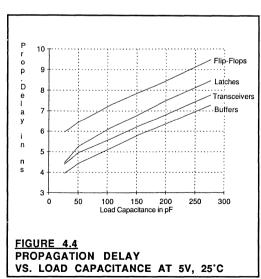

| 4.4   | Propagation Delay versus Load Capacitance at 5V, 25°C             |

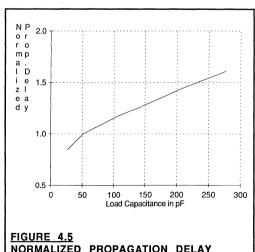

| 4.5   | Normalized Propagation Delay versus Load Capacitance at 5V, 25°C  |

| 4.6   |                                                                   |

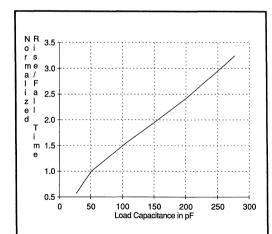

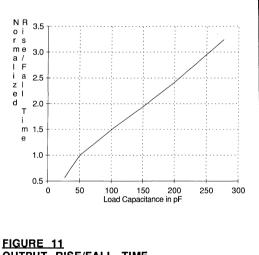

|       | Output Rise/Fall Time versus Output Load Capacitance              |

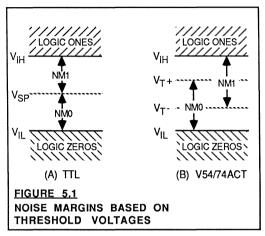

| 5.1   | Noise Margins Based on Threshold Voltages                         |

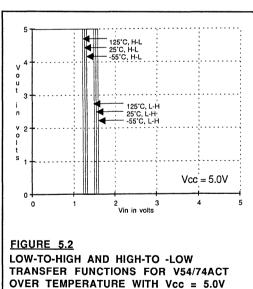

| 5.2   | Low-to-High & High-to-Low transfer Functions for V54/74ACT5-3     |

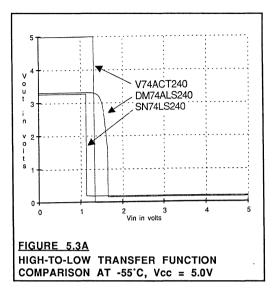

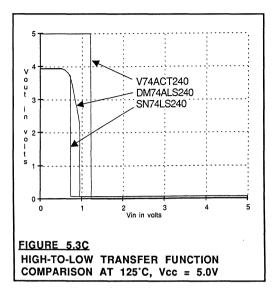

| 5.3A  | Transfer Function Comparison at -55°C, Vcc=5.0V                   |

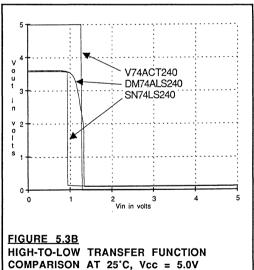

| 5.3B  | Transfer Function Comparison at 25°C, Vcc=5.0V5-3                 |

|       |                                                                   |

| 5.3C Transer Function Comparison at 125°C, Vcc = 5.0V                  | E 4 |

|------------------------------------------------------------------------|-----|

|                                                                        |     |

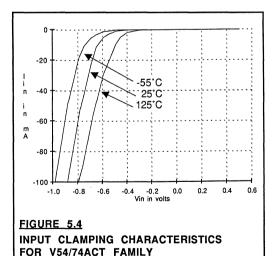

| 5.4 Input Clamping Characteristics for V54/74ACT Family                |     |

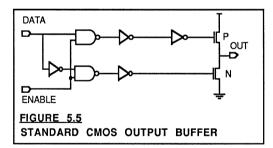

| 5.5 Standard CMOS Output Buffer                                        |     |

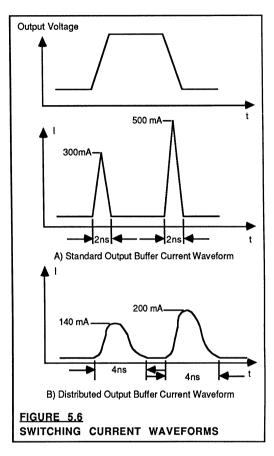

| 5.6 Switching Current Waveforms                                        | 5-5 |

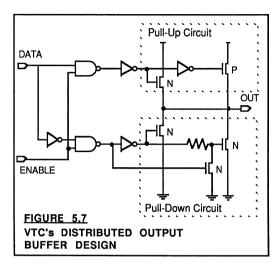

| 5.7 VTC's Distributed Output Buffer Design                             |     |

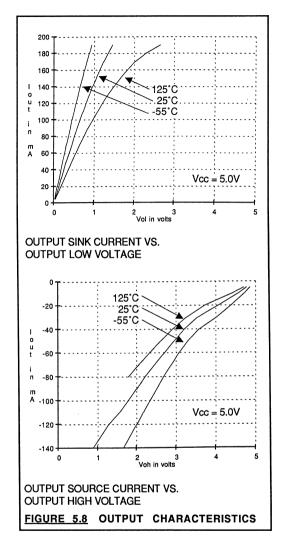

| 5.8 Output Characteristics                                             | 5-6 |

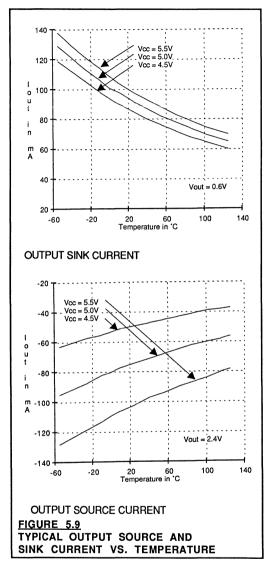

| Typical Output Source and Sink Current versus Temperature              |     |

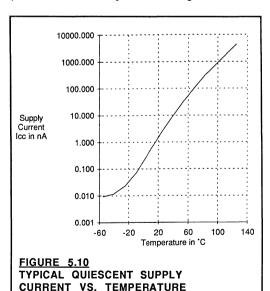

| 5.10 Typical Quiescent Supply Current versus Temperature               |     |

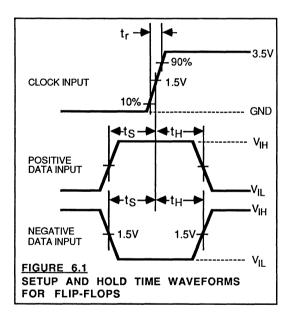

| Setup and Hold Time Waveforms for Flip-Flops                           | 6-5 |

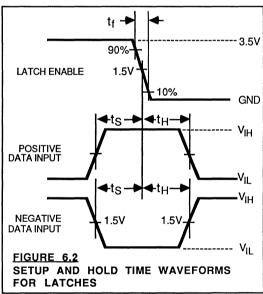

| Setup and Hold Time Waveforms for Latches                              |     |

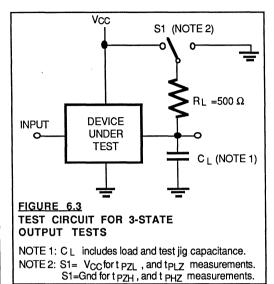

| 3.3 Test Circuit for 3-State Output Tests                              |     |

| 3.4 3-State Output Enable and Disable Waveforms                        |     |

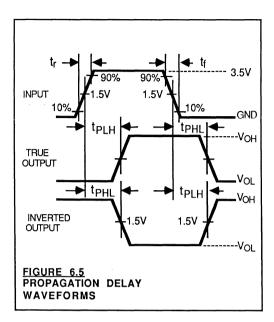

| S.5 Propagation Delay Waveforms                                        | 6-7 |

| 6.6 Output Transition Time Waveforms (10-90% of 3.5V)                  |     |

| 6.7 Input Pulse Width Waveforms                                        |     |

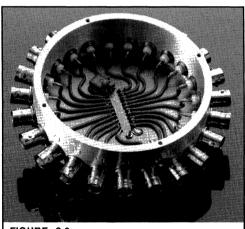

| 3.8 VTC Test Fixture                                                   |     |

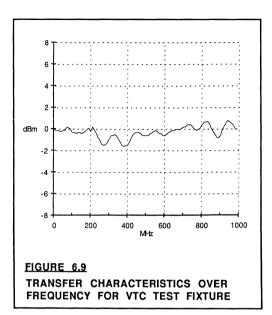

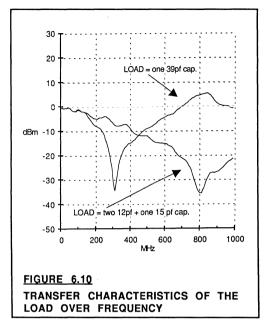

| 3.9 Transfer Characteristics over Frequency for VTC Test Fixture       | 6-9 |

| 3.10 Transfer Characteristics of the Load over Frequency               | 6-9 |

| 7.1 SCR Models                                                         | 7-1 |

| 7.2 CMOS SCR Structure                                                 |     |

| 7.3A Latch-up Test: Positive Current Injection                         | 7-4 |

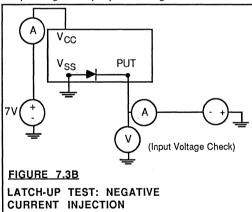

| 7.3B Latch-up Test: Negative Current Injection                         | 7-4 |

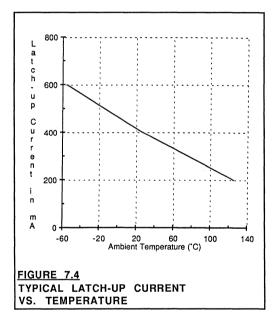

| 7.4 Required Latch-up Current vs Temperature                           | 7-4 |

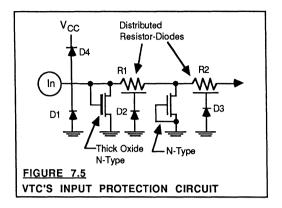

| 7.5 VTC's Input Protection Circuit                                     |     |

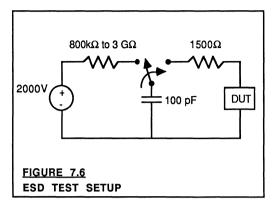

| 7.6 ESD Test Setup                                                     |     |

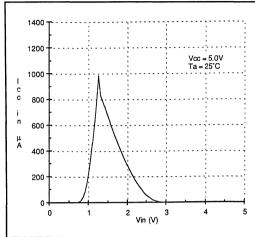

| 3.1 Quiescent Supply Current vs Input Voltage for V54/74ACT Family     |     |

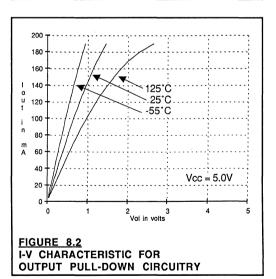

| 3.2 I-V Characteristic for Output Pull-down Circuitry                  |     |

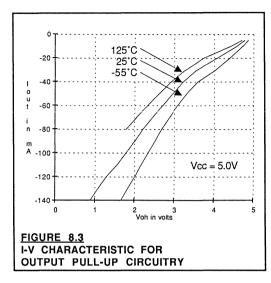

| 3.3 I-V Characteristic for Output Pull-up Circuitry                    |     |

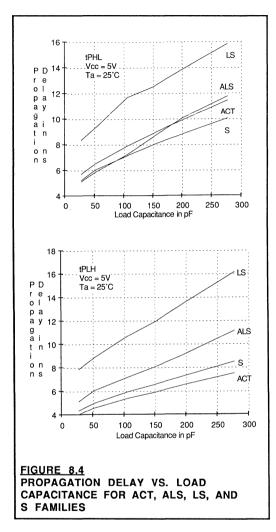

| Propagation Delay vs Load Capacitance for ACT, ALS, LS, and S Families |     |

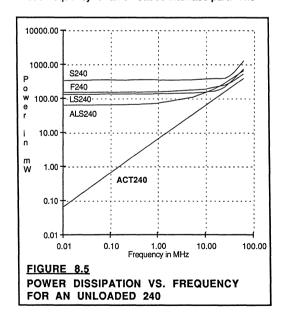

| 3.5 Power Dissipation vs Frequency for an Unloaded 240                 | 8-6 |

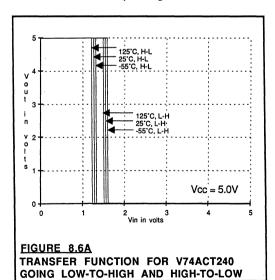

| 3.6A Transfer Function for V74ACT240 going Low-to-High and High-to-Low | 8-6 |

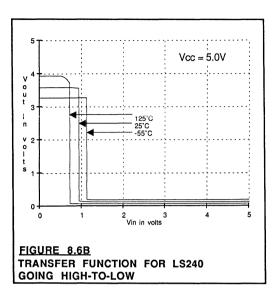

| 3.6B Transfer Function for LS240 going High-to-Low                     | 8-7 |

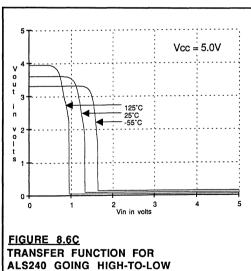

| B.6C Transfer Function for ALS240 going High-to-Low                    | 8-7 |

| B.7 Derating of Delay and Current Driving Capability over Temperature  | 8-7 |

## INTRODUCTION: A.C.T. INTERFACE LOGIC FAMILY

#### VTC'S ACT INTERFACE FAMILY

VTC's VHSIC Technology Division has produced a new family of interface circuits using an advanced 1.6 micron, double level metal CMOS process. This third generation CMOS logic family moves beyond the HCT products to match the high speed and drive capability of the bipolar ALS family with traditional CMOS power requirements.

The new family, designated ACT, uses familiar 74 series functions and pinouts to offer a new standard for interfacing requirements for systems engineers in several areas.

- direct replacement of the ALS family, with the benefit of three to five orders of magnitude of power reduction in the quiescent state:

- performance upgrade for existing systems using HCT products:

- state of the art interfaces for the latest generation of microprocessors, memories, and gate arrays.

All the possible requirements to set a new standard in a logic family have been incorporated into VTC's new ACT family:

- Low Power: input current several orders of magnitude less than equivalent ALS functions

- High Speed: propagation delays that meet and exceed those of ALS, 5 ns typical

- TTL Level Drive: 48 mA driving a 50Ω line for commercial temperature range (32 mA military)

- · Pin-Outs: same as ALS

- Latch-Up: typical current required exceeds 200 mA

- ESD Protection: greater than 2000 volts as defined by MIL-STD-883C Method 301

- Fully Characterized and Guaranteed: minimums and maximums, over temperature and voltage, 50 pF and 300 pF loads, commercial and military temperature ranges, test jig definition.

The application sections of the VTC data book are written to help designers gain maximum competitive advantage in their systems. The various sections include characterization of the family, test and correlation procedures, good system design and layout practices, comparison of ACT to other TTL and CMOS families, quality and reliability, and packaging.

## SYSTEM DESIGN CONSIDERATIONS

#### INTRODUCTION

As the digital integrated-circuit market has expanded, the need has increased for a very-high-speed logic family with low power dissipation. Present system design demands a logic family with high clock rate capability, short propagation delays, and a minimum of layout constraints. The V54/74ACT family of TTL-compatible CMOS logic has evolved from these factors.

The 1.0 ns gate propagation delay of CMOS gives the family a speed range between the ALS and AS families. Additional characteristics, such as low power dissipation, low input load currents, low input capacitance, and slower rise and fall times have eased the difficulties encountered in trying to balance system speed versus ease of design.

The V54/74ACT components have the capability of performing in a system that uses clock rates up to 75 MHz. To permit such high-speed operation, gate propagation delays must be short. To simplify wiring techniques and to minimize the use of transmission lines, rise and fall times have been kept to slower values. The typical rise time is 3 ns for 50 pF type loads, with propagation delays through the buffers and transceivers of less than 10 ns.

The V54/74ACT family can be used to obtain maximum versatility with low power and ease of layout design. The V54/74ACT family has the capability to drive long lines and is specified to be functionally compatible with their equivalent ALS part. In order to take full advantage of this family's capabilities, some restraints and cautions must be observed in laying out the board, power bussing to components, driving long lines, and using large fan-outs at maximum frequency.

The following material will give the system designer insight into these areas of concern:

- -the use of non-transmission line interconnections -power supply needs and constraints

- -the characteristics of transmission lines that affect the V54/74ACT interconnections.

#### PRINTED CIRCUIT BOARD CONNECTIONS

Layout rules for designing with the V54/74ACT family depend on the criteria of the system used. This circuit family may be used in layouts ranging from a single-layer printed circuit board (PCB) with wired interconnects, to the most elaborate multilayer board with a complete transmission line environment. The optimization of system layout will include considerations of system size, performance, and cost.

#### GROUND INTERCONNECTION CRITERIA

When possible, the use of power distribution elements (PDEs) or a ground plane is suggested. A ground plane is beneficial for maintaining a low noise voltage plane for the V<sub>CC</sub> supply and maintaining

constant characteristic impedance when transmission wires are necessary. A ground plane may be established by using a single-sided board with wired interconnects, or by using a double or multilayer PC board. Power distribution elements are also beneficial for providing low noise environments, and are strongly recommended by VTC. PDEs will be discussed later in this section.

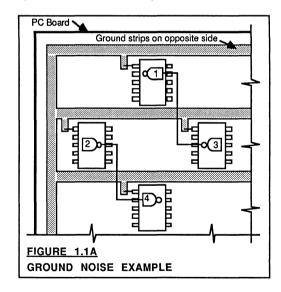

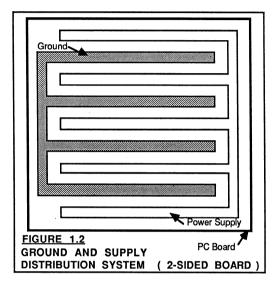

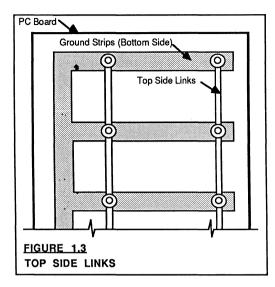

To illustrate how ground noise can couple through a common ground path and cause noise problems in the system, consider the situation outlined in Figure 1.1A. This figure shows a double-sided board with power and ground distribution on one side and signal traces on the other side. A typical ground and supply distribution system can be created by use of interwoven fingers of supply and ground paths, as illustrated in Figure 1.2.

The following text illustrates a possible scenario using this type of layout. Figure 1.1A shows four IC packages, where gate G3 drives gate G1 and gate G2 drives gate G4. Gates G2 and G3 share a common ground path. Figure 1.1B shows an electrical equivalent circuit for this set-up.

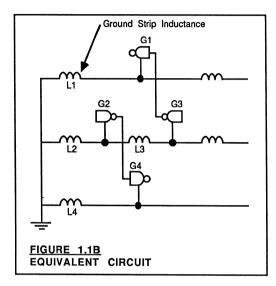

The inductors L1, L2, L3, and L4 represent the distributed inductance of the ground strips. As gate G3 switches from high to low, the transient ground current from G3 flows in the ground pin of G2. But there is a ground strip common for G2 and G3 with an equivalent inductance L2. The transient ground current from G3, acting on L2, appears as a positive spike on the ground

strip and could couple through to the output of gate G2, if G2 was on and in the low state. This happens because the  $V_{OL}$  level of G2 is always referenced to its ground pin. Thus, if the ground voltage changes, so does the  $V_{OL}$  signal.

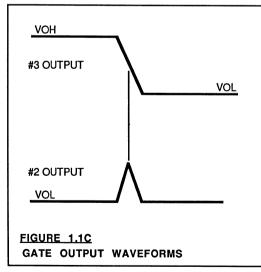

The positive spike on G2 appears at the input of G4. Figure 1.1C illustrates these waveforms. If the sum of the quiescent  $V_{OL}$  of G2 plus the positive spike due to ground bounce is big enough, the input of G4 could be driven into the threshold region, which could cause G4's output to amplify the spike and propagate it through the rest of the system.

Figure 1.3 suggests an approach to minimize these ground spikes for two-sided boards if PDEs or a ground plane are not provided. The ground distribution strips are periodically connected by narrow traces on the top of the board. This reduces the common ground inductance component of any two packages and minimizes the ground spike. These links need not be straight, as shown in the sketch. Typically, a spacing of a few inches will suffice.

Bus drivers need closer attention. The simultaneous switching of a group of bus drivers on a common ground strip only an inch or two long can cause large spikes. It is recommended that buffers driving a backplane be grouped at the edge of the board and have their ground isolated and brought in on a separate pin from the backplane supply structure. This is also recommended for any drivers or buffers on a board that will be driving long, heavily loaded buses on the PC board. Breadboarding will also work with fewer problems if the guidelines above are followed. Thus, the use of jumper wires to provide the ground connection is not recommended. The preferred

approach is to solder ground and supply pins. This would lead to realistic evaluations when using breadboards. For non-standard power pin-out, use copper braids or strips.

#### POWER DISTRIBUTION ELEMENTS

Transient noise voltages on the power distribution system of a circuit are caused by sudden changes in the current demand of the load. In high-speed digital circuits, the current and voltage changes can be assumed to be instantaneous for the purpose of calculating the demands on the power distribution system. Thus, assuming the current change is instantaneous, the resulting voltage change is a function of the characteristic impedance  $(Z_0)$  of the power distribution system:

$$Z_0 = \sqrt{(L_T/C_T)}$$

The instantaneous voltage change  $\Delta V$  will then be:

$$\Delta V = \Delta I \cdot Z_{\Omega}$$

From this equation it is obvious that the characteristic impedance of the power distribution system should be as low as possible to keep transient noise voltage to a minimum.

For comparison, consider the characteristic impedance of a copper power bus over a ground plane

separated by a glass epoxy board. This is a typical power distribution system for two-sided PCB's. Figure 1.6 illustrates this setup. If 1 oz. copper ( t=0.0015") is used over a glass epoxy board ( h=0.0625",  $e_R=4.7$ ) and the power strip is 0.1" wide, then the characteristic impedance is:

$$Z_0 = [87 / \sqrt{(4.7 + 1.41)}] \cdot \ln([5.98 \cdot 0.0625]/[0.8 \cdot 0.1 + 0.0015]) \approx 54\Omega$$

An excellent method of providing a good power distribution system using only a two-sided copper PCB is to incorporate power distribution elements (PDEs) into the circuitry. The use of PDEs is strongly recommended by VTC, and results in electronic assemblies that have low noise levels on their power and ground lines because of the inherent noise suppression of the PDEs.

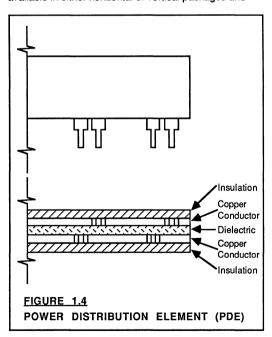

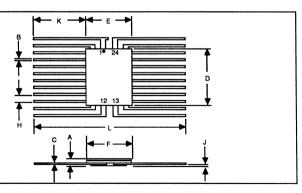

A PDE is composed of two flat conductors placed on top of each other and separated by a thin dielectric. This "sandwich" arrangement is then encapsulated with an insulative material. Contact pins are placed at specified intervals for easy access to the two conductors. Figure 1.4 shows a PDE. PDEs are available in either horizontal or vertical packages and

standard or custom lengths and pinout configurations from several manufacturers, such as Rogers Corporation in Tempe, Arizona.

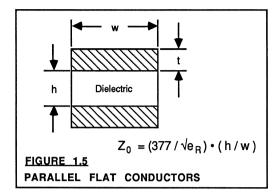

The characteristic impedance of a PDE can be calculated using the impedance equation for parallel flat conductors. An illustration of parallel flat conductors and their impedance equation is shown in Figure 1.5.

If the conductors in a PDE were 0.20" wide and separated by a 0.005" sheet of mylar (e $_{\rm R}$  = 5.0), then the characteristic impedance would be:

$$Z_0 = (377/\sqrt{5.0}) \cdot (0.005/0.20) = 4.2\Omega$$

The characteristic impedance of the PDE is more than ten times smaller than the characteristic impedance of the two-sided printed circuit board power distribution system mentioned in the preceding text. This illustrates the low impedance of a PDE, which makes it an excellent choice for power distribution.

To further reduce noise in a power distribution system using PDEs, use decoupling capacitors at each end of the PDEs. High-frequency ceramic disk capacitors with values of at least 0.01  $\mu$ F are recommended. It is also a good idea to decouple each power supply voltage brought on to the board edge contacts.

The recommended decoupling elements are a  $0.1\mu F$  hf ceramic-disk capacitor paralleling a 20 to 30  $\mu F$  tantalum capacitor.

When using PDEs in a circuit, it is best to arrange the PDEs so that each PDE handles only one type of circuit function. Interface components must always have a separate PDE because of their high source/sink capability. It is also a good practice to keep interface components at the edge of the board. This prevents switching noise from affecting more than one section of logic.

For example, consider the 32-bit microprocessor board outlined in Figure 1.7. Separate PDEs should supply the memory, interface, and microprocessor sections, as shown in Figure 1.8.

To avoid couplings between PDEs, which would increase the noise level, each bus bar should have a separate ground and power connection, with both connected at the same end and as close to the edge contacts as possible. Each chip should receive its power and ground from one PDE. If power and ground come from separate PDEs, the chip will couple noise from one PDE to another. Layout of a board using these guidelines helps isolate and lower the switching noise found in high-speed digital circuits.

## NON-PDE SUPPLY INTERCONNECTION CRITERIA

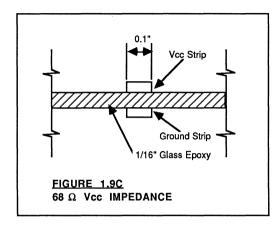

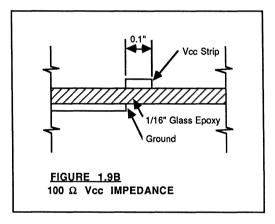

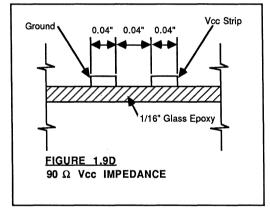

It is now apparent that logic gates and bus drivers need extra current when they switch. This in turn will cause transients on the power supply buses. In many cases V<sub>CC</sub> is distributed by V<sub>CC</sub> strips, which exhibit a fairly high impedance to transient loads. Figures 1.9A-D show examples of some typical V<sub>CC</sub> runs that might exist on the PC board and their corresponding impedance values.

In Figure 1.9A, the dynamic impedance of  $V_{CC}$  with respect to ground is 50  $\Omega$ , even though the  $V_{CC}$  trace width is generous and there is a complete ground plane. In B, the dynamic impedance doubles to 100  $\Omega$ . In C, the ground bus is also 0.1" wide and runs along

under the  $V_{CC}$  bus. This exhibits a dynamic impedance of 68  $\Omega$ . In D, the trace widths and spacing are such that the traces can run under a DIP package, between two rows of pins. In this configuration, the dynamic impedance is  $90\Omega$ .

These typical dynamic impedances for copper-foil power distribution point out that unless a bypass capacitor is located near the IC, a sudden current demand due to an IC output switching will cause a momentary reduction in  $V_{\rm CC}$ .

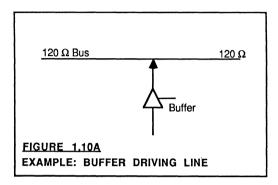

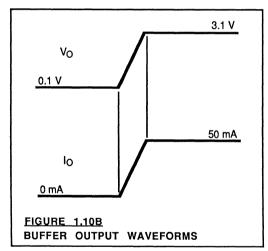

Consider the example illustrated in Figure 1.10A. It shows a buffer driving a line of 120  $\Omega$ . The buffer actually sees two 120  $\Omega$  lines in parallel, or a net dynamic load of 60  $\Omega$ . For this load impedance, the buffer output forces an initial low to high transition in about 3 ns. A 60  $\Omega$  load line on the  $I_{OH}$ - $V_{OH}$

characteristics shows a low to high step of approximately 3.0 V. Thus, a net change of 3.0 V into a 60  $\Omega$  load gives rise to a 50 mA current. If 10 outputs of the buffer IC switch simultaneously, the total current demand will be 0.5 A. This is a substantial current, requiring a bypass capacitor to supply it.

## CALCULATION OF BYPASS CAPACITOR VALUES

To evaluate the size of the bypass capacitor, we need to specify the tolerable  $V_{CC}$  drop. From circuit theory:  $Q = C \cdot V$

$I = C \cdot dV/dt = C \cdot \Delta V/\Delta t$

I is current demand.

C is required capacitor value.  $\Delta V$  is tolerable  $V_{CC}$  drop.  $\Delta t$  is the transition time of the signal.

In the above illustration, where 10 outputs switched simultaneously:

$\Delta t = 3 \text{ ns}$   $\Delta V = 0.1 \text{ V}$ I = 0.5 A

Hence:  $C = (0.5 \text{ A-}3x10^{-9})/0.1 \text{ V}$ = 15x10<sup>-9</sup> = 0.015  $\mu\text{F}$

≈ 0.02 µF

These equations illustrate an approximate method of estimating the size of a bypass capacitor based on current demand,  $V_{CC}$  drop, and the length of time that a capacitor must supply the charge. The following guidelines should be adhered to for bypassing purposes:

- Use bypass capacitors, one for each buffer and transceiver IC. If PDEs are used, place bypass capacitors at each end of the PDEs instead of at each buffer or transceiver.

- Bypass capacitors should have low inductance, highfrequency qualities.

- RF quality capacitors are preferred.

- Use decoupling capacitors where  $V_{CC}$  comes onto the board. The recommended decoupling elements are a 0.1  $\mu$ F ceramic disk capacitor in parallel with a 20 to 30  $\mu$ F tantalum capacitor.

- Distribute capacitors evenly throughout the board.

## SIGNAL PROPAGATION IN TRANSMISSION LINES

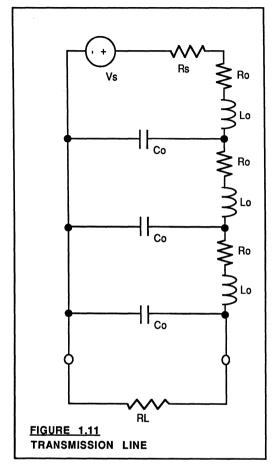

A transmission line is a signal path that exhibits a characteristic impedance. Transmission lines can be approximated by the lumped constant representation shown in Figure 1.11. For lossless lines  $R_{O}$  = 0. We will assume that the effect of  $R_{O}$  on  $Z_{O}$  is negligible.

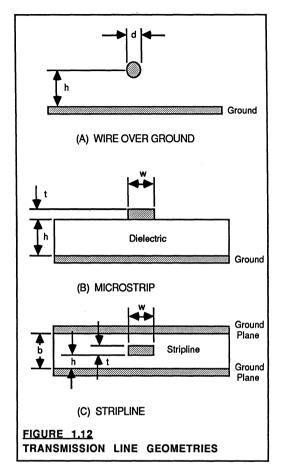

With a ground plane present, three types of transmission line geometries are feasible: a) wire over ground, b) microstrip, and c) strip line. These geometries are shown in Figure 1.12. The characteristic impedance of each can be evaluated by the following formulas: (References 1-14) a) Wire Over Ground

$Z_O = [60/\sqrt{(E_r+1.41)}] \cdot \ln(4h/d)$

b) Microstrip Line

$Z_0 = [87/\sqrt{(E_r+1.41)}] \cdot \ln[5.98h/(0.8w+t)]$

c) Strip Line  $Z_O = (60/\sqrt{E_f}) \cdot \ln[4b/(0.67\pi w \cdot (0.8 + (t/w)))]$

(Er is the dielectric constant)

#### REFLECTIONS AND LOADING

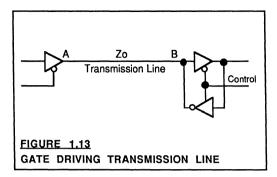

Consider a driving gate as shown in Figure 1.13, driving onto a transmission line of characteristic impedance  $Z_O$ . When the output of the driving gate changes state, the voltage at point A is a function of the voltage swing, output impedance, and line impedance.

$$V_A(t) = V_{IN} \cdot [Z_O/(R_O + Z_O)]$$

RO is the internal resistance of the driver.

Some time later, this voltage step reaches point B, where it may be reflected. The reflection coefficient  $f_{\rm L}$  depends on the load at the other end of the line.

$$f_L = (R_L - Z_O)/(R_L + Z_O)$$

A reflection will always occur, except when  $R_L = Z_O$ . The reflection will continue to bounce back and forth on the line, getting successively smaller in amplitude. The result is ringing on the signal line.

Rise time effects can be understood by considering the delay time of the line. If the line length 'l' is sufficiently short, the first reflections are seen at the sending end of the line while the driver is still changing state. The reflections are hidden by the rising edge of the pulse, and ringing is reduced. To limit undershoot to about 12% of the logic swing, the maximum open line length permitted would be:

$$L_{MAX} = t_r/2t_{pd}$$

tr is the rise time of the driving gate.

t<sub>pd</sub> is the propagation delay per unit line length

For the microstrip line, the propagation delay of the line may be calculated by:

$$t_{pd} = 1.017\sqrt{(0.475E_{r}+0.67)}$$

ns/ft.

$E_r$  is the dielectric constant of the board. For fiberglass epoxy boards  $E_r \approx 5.0$ , hence  $t_{pd}$  is approximately 1.75 ns/ft.

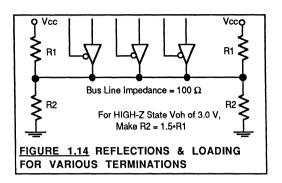

## REFLECTIONS AND LOADING FOR VARIOUS TERMINATIONS

The previous discussion assumed a line without any termination. If a termination resistor is used, the reflection value will be reduced, as given by the reflection coefficient:

$$f_{1} = (R_{1} - Z_{0})/(R_{1} + Z_{0})$$

Figure 1.14 shows a scheme for terminating each end of a data bus to limit reflections and establish a high level when all buffer outputs are in the high-Z state. Table 1.1 shows the percent reflection and the quiescent I<sub>OL</sub> load on a buffer for various values of R<sub>1</sub>.

$R_2$  is set at 1.5 times  $R_1$ , and  $I_{OL}$  is the load current due to the termination resistors.

| <u>TABLE 1.1</u> |              |                        |  |  |

|------------------|--------------|------------------------|--|--|

| $B_1\Omega$      | % Reflection | IOL Load mA (Each End) |  |  |

| 00               | 100          | 0                      |  |  |

| 510              | 51           | 8                      |  |  |

| 330              | 33           | 13                     |  |  |

| 240              | 18           | 17                     |  |  |

| 180              | 4            | 23                     |  |  |

| 160              | -2           | 26                     |  |  |

Until now, the effect of loading on the terminated line has been ignored. Fan-out along a signal line lowers the effective characteristic impedance. The effect of this is given by the equation:

$$Z_{O'} = Z_{O}/\sqrt{[1+(C_{D}/C_{O} \cdot I)]}$$

Zo'is the loaded line impedance.

ZO is the unloaded line impedance.

C<sub>D</sub> is the total distributed capacitance due to loads

$C_{\mbox{\scriptsize O}}$  is the intrinsic capacitance per unit length. I is the length of the line.

This shows that, in a bus or backplane environment, it is very difficult to prevent reflections by various line terminations if the number of loads are likely to change over the life of the system.

Loading also increases delay in the transmission line. Propagation delay of a loaded line may be calculated from the following equation:

$$t_{pd}' = t_{pd}\sqrt{[1+(C_D/C_O \cdot I)]}$$

$t_{pd}$  is the propagation delay of the loaded line.  $t_{pd}$  is the propagation delay of the unloaded line.

C<sub>D</sub> is the total distributed capacitance due to loads.

C<sub>O</sub> is the intrinsic capacitance per unit length. I is the length of the line.

Increased capacitive loading also slows the rise time of the signal because the driver must drive a larger load. All these factors should be considered when evaluating the signal propagation along a transmission line.

#### REFLECTION DIAGRAMS

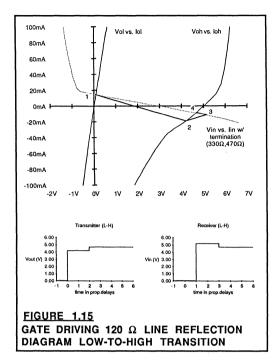

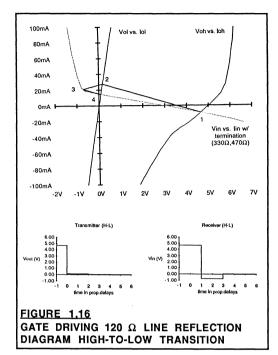

A reflection diagram is a graphic technique used to evaluate the effect of signal propagation and reflection over a transmission line. The graph has both the output-low and output-high (I-V) characteristics of the driver. The dashed line passing through the 3V point on the voltage axis is the I-V characteristic of the termination in parallel with the driver gate. Figure 1.15 and 1.16 show the reflection diagrams for the V54/74ACT family of drivers.

To make a low-to-high transition reflection diagram, as shown in Figure 1.15, start by drawing a -120  $\Omega$  (or the impedance of the driven line) line from point 1, the quiescent low condition. The intercept with the  $I_{OH}:V_{OH}$  characteristic, point 2, is the first step at the driver output. From point 2, draw a +120  $\Omega$  line to the termination line, intersecting at point 3. From point 3, draw a -120  $\Omega$  line, intersecting the  $I_{OH}:V_{OH}$  characteristic at point 4. Successive intercepts converge in the quiescent high condition. The voltage vs. time graphs illustrate the voltage changes at either end of the line. The changes at the receiver and driver are separated by a time T equal to the line delay of the line.

Figure 1.16 shows the high-to-low transition diagram. These transitions can be evaluated graphically while maintaining an acceptable level of accuracy. The mathematical calculations tend to be tedious and fail to reveal the physical mechanisms taking place.

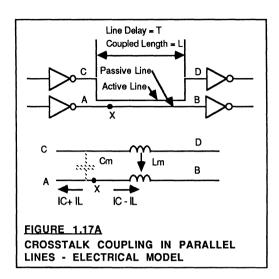

#### CROSSTALK

Crosstalk is caused by capacitive and inductive coupling of signals along parallel lines. Figure 1.17A shows an electrical equivalent circuit of two parallel lines. A pulse propagating down line CD is capacitively coupled into line AB. The effect of the coupled pulse is lumped at point X. The coupled voltage on line AB causes current I<sub>C</sub> to flow from the point of coupling to both ends.

Current in the direction of A is called "backward crosstalk" and current in the direction of B is called "forward crosstalk." Similar coupling is caused by the mutual inductance of the lines, this current couples in the direction of "backward crosstalk."

Because the line is not terminated, these signals also go through reflections at A, and after 2td's reach B. The crosstalk amplitude can be calculated by the following equation: (Reference 11)

$$\begin{split} V(x_1,t) &= k_1 \cdot x \cdot d/dt \{ V_{IN}[t-T_D(x/l)] + k_D[V_{IN}(t-T_D(x/l)) - V_{IN}(t-T_D(x/l))] \} \end{split}$$

$k_f$  = forward crosstalk coefficient =  $-1/2[(L_M/Z_O)-C_M^*Z_O]$

$k_b$  = backward crosstalk coefficient =  $(V4T_D)[(L_M/Z_O)+C_M^*Z_O]$

$L_{\mbox{\scriptsize M}}$  = mutual line inductance per unit length.

C<sub>M</sub> = mutual line capacitance per unit length.

$Z_{O}$  = characteristic line impedance.

I = line length.

x = an arbitrary point along line.

$T_D$  = delay through the line.

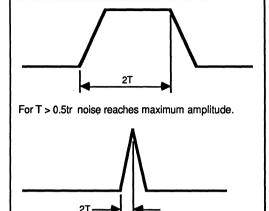

The amplitude of crosstalk is a function of line length for short lines. Short lines are defined as lines that have a propagation delay less than one-half the input rise time. The width of the crosstalk pulse will always be a function of the length of the line. The rise and fall times of the crosstalk pulse on line AB are the same as the rise time of the signal propagating down line CD. Figure 1.17B illustrates a crosstalk (noise) pulse that would be seen at point B for various line delays.

Termination reduces the amplitude of crosstalk signals. Even partial termination will reduce the amplitude of a signal appearing at the end of the line. Table 1.2 illustrates this point. A terminating resistor twice the value of the line impedance reduces the noise amplitude by one-third. A matched termination cuts the noise amplitude in half, relative to the nonterminated

line.

| TABLE 1.2       |                              |

|-----------------|------------------------------|

| Noise Amplitude | Termination R, in terms of Z |

| 100%            | R = 0                        |

| 67%             | R = 2•Z                      |

| 60%             | R = 1.5•Z                    |

| 50%             | R = 1•Z                      |

General recommendations for crosstalk reduction are:

- a) Maximize the spacing between signal lines, which reduces coupling inductance and capacitance.

- b) Minimize spacing between signal line and around.

- Wrap a wire around the talker to confine its field. or around the listener to shield it.

- d) Use split-resistor termination.

- e) Locate a ground trace next to the active wires.

- f) Make every other conductor in a flat cable a ground.

For multilayer crosstalk reduction, position signal lines perpendicular to each other in adjacent planes and use power planes as shields between pairs of signal planes.

#### SUMMARY AND CONCLUSION

The preceding text has been an overview of the problems and issues common to most system design environments. General design guidelines with numerical illustrations and formulas were provided.

These guidelines are useful tools for analysis of specific

For T = 0.5tr noise just reaches maximum amplitude.

For T < 0.5tr noise never reaches maximum amplitude.

## FIGURE 1.17B CROSSTALK COUPLING IN PARALLEL LINES - NOISE PULSES AT POINT B

design issues the system designer will encounter. References are provided for further information.

The VTC interface buffer, driver, latch, and transceiver families offer short delay and setup times, high drive capability (fan-out), low power dissipation, low input capacitance, and a low input current requirement for modern high-performance TTL systems environments.

Improved performance, fast edge rates, and high drive capability means that care must be exercised in the design of the layout environment of both signal paths and the grounding system. Every line behaves like a transmission line, so careful consideration should be given to the relationships between loading, termination, noise margins, and ringing.

The power distribution network could require PDEs, heavier bussing, a grid approach, or a separate ground plane, depending on the driver layout and overall current densities. The device capability to sink

48 mA per bit and the charging/discharging of bus lines can cause large ground currents. Supply decoupling should be located close to the actual drivers to provide the current required for the charging of bus lines.

The following are general suggestions to minimize grounding and noise problems:

#### Minimize Crosstalk:

- Use power distribution elements.

- Use topside links for the ground grid.

- Use a dedicated ground plane in multilayer boards.

- Make every other wire in a flat cable a ground wire.

- Minimize spacing between a signal line and ground line.

- Maximize spacing between signal lines.

- If possible, use a four layer board with a dedicated ground and supply plane.

#### Increase Decoupling:

- Use high-frequency capacitors of the tantalum and ceramic types.

- Provide a bypass capacitor close to the buffer package.

- Use a dedicated supply plane if the system warrants it.

If the system has mostly CMOS or NMOS components, the current requirements of the system may not be very high. In this case, dedicated supply planes may not be necessary; decoupling capacitors with a good ground grid might do the job. Analyze your component's requirement and follow the relevant guidelines from above in the general layout of your system.

#### REFERENCES

- Kaupp, H. R., "Characteristics of Microstrip Transmission Lines," IEEE Transactions on Electronic Computers, Vol. EC-16, No. 2, April 1967, pp. 185-193.

- Cohn, S. B., "Characteristic Impedance of the Shielded Strip Transmission Line," Transactions IRE, Vol. MTT-2, July 1954, pp. 52-57.

- Springfield, W. K., "Designing Transmission Lines into Multilayer Circuit Boards," Electronics, November 1, 1965, pp. 90-96.

- 4) Skilling, H. H., "Electric Transmission Lines," New York, McGraw-Hill, 1951.

- Defalco, J. A., "Reflections and Crosstalk in Logic Circuit Interconnections," IEEE Spectrum, July 1970, pp. 44-50.

- Millman, J., and Taub, H., "Pulse, Digital and Switching Waveform," New York, McGraw-Hill, 1965, pp. 83-106.

- 7) "Time Domain Reflectometry," Hewlett-Packard Application Note 62, 1964.

- Botos, Bob, "Nanosecond Pulse Handling Techniques in I/C Interconnections," Motorola Application Note AN-270.

- Schwarzmann, A., "Microstrip Plus Equations Adds Up to Fast Designs," Electronics, October 2, 1967, pp. 109-112.

- Catt, I., "Crosstalk (Noise) in Digital Systems," IEEE Transactions on Electronic Computers, Vol. EC-16, No. 6, December 1967, pp. 743-763.

- Feller, A., H. R. Kaupp, J. J. Digiacoma, "Crosstalk and Reflections in High-speed Digital Systems," Proceedings, Fall Joint Computer Conference, 1965, pp. 511-525.

- Cohn, S. B., "Shielded Coupled-Strip Transmission Line," IRE Transactions-Microwave Theory and Techniques, October 1955, pp. 29-38.

- Gabbard, O. G., "High-Speed Digital Logic for Satellite Communications," Electro-Technology, April 1969, pp. 59-65.

- 14) Henschen, I. E. and E. M. Reyner II, "Adapting PC Connectors for Impedance Matching," Proceedings, NEPCON, 1970.

- MECL System Design Handbook, Motorola Incorporated.

- Q/PAC User's Guide, Rogers Corporation, Tempe, AZ.

### **DESIGN CASE**

#### INTRODUCTION

A bus line is designed to interconnect several points in a system with a common data path. Normally, drivers and receivers are located at each end of the line, so data can flow in either direction. Additional drivers and receivers often connect to the bus at various points along the line, requiring that the driver be capable of sending a signal in both directions.

Due to this criteria, a high-speed bus driver should be capable of operating into a load equal to one-half the characteristic line impedance. At any given time, only one driver on a bus can send data. In this section, single-ended buses will be considered with an illustrated example of the VMEbus™.

#### HIGH-SPEED REQUIREMENTS

A sample specification of the VMEbus™'s electrical requirements is discussed and analyzed.

Generally, high-speed single-ended buses can have a high fan-out density and use TTL/CMOS/ ECL type circuits as drivers and receivers. The signal type and voltage levels are determined by system requirements. The VMEbus™ specifies typical TTL voltage signals.

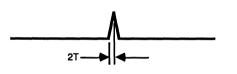

All VMEbus™ signals are limited to positive levels between 0 and 5 volts. The signal levels are:

a) 0.0 V ≤ Driver low output level (V<sub>OI</sub>) ≤ 0.6V.

- b) 0.0 V ≤ Receiver low input level (V<sub>II</sub> ) ≤ 0.8V.

- c) 2.4 V  $\leq$  Driver high output level (V<sub>OH</sub>)  $\leq$  5.0V.

- d) 2.0 V  $\leq$  Receiver high input level (V<sub>IH</sub>)  $\leq$  5.0V.

Figure 2.1 gives a simple representation of these levels. The V54/74ACT series bus interface circuit family meets the specifications in Figure 2.1.

#### VMEBUS™ SPECIFICATIONS

The VMEbus™ calls out the electrical specifications for standard 3-state signal lines. This class of signals consists of address lines A00-A31, data lines D00-D31, and transfer signals Am0-Am5. The following paragraph lists in detail the voltage and current specification for this class of lines.

#### DRIVER CHARACTERISTICS FOR STANDARD 3-STATE CLASS LINES

a) Low state output current: I<sub>OL</sub> ≥ 48 mA.

b) Low state output voltage:  $V_{OL} \le 0.6 \text{ V}$  at  $I_{OL} = 48 \text{ mA}$ .

- c) High state output current:  $I_{OH} \ge -3$  mA.

- d) High state output voltage:  $V_{OH} \ge 2.4 \text{ V}$  at  $I_{OH} = -3 \text{ mA}$ .

- e) High level output current: I<sub>OZH</sub> ≤ 100 μA at V<sub>O</sub> = 2.7 V 3-state off.

- f) Low level output current: I<sub>OZL</sub> ≤ -100 μA at V<sub>O</sub> = 0.6 V 3-state off.

- g) Short circuit current: I<sub>OS</sub> minimum -25 mA, maximum -225 mA, at 0 V.

- h) Output capacitance: Driver, C<sub>OUT</sub> ≤ 15 pF Transceiver, C<sub>BUS</sub> ≤ 18 pF.

The total capacitive load presented by a VME module to any of these lines shall not exceed 20 pF.

All bus receivers should have an input diode clamp that prevents negative voltage excursions from going below -1.5 V. The other requirements for the VMEbus™ signals are given in the following paragraph.

Receiver circuits for signals should provide the following electrical characteristics as a maximum:

- a) Low level input current:  $I_{|L|} \le -600 \mu A$  at  $V_{|L|} = 0.5 V$

- b) High level input current:  $I_{IH} \le 50 \mu A$  at  $V_{IH} = 2 AV$

- c) Positive or negative going threshold voltages:  $0.8 \text{ V} \le \text{V}_T \le 2.0 \text{ V}$ .

(Receivers on these lines are recommended, but not required, to have hysteresis inputs)

d) Input capacitance: Receiver, C<sub>IN</sub> ≤ 7 pF.

Transceiver, C<sub>BUS</sub> ≤ 18 pF.

The V74/54ACT interface family meets or exceeds these specifications. The input currents are in the 1µA range. The quiescent supply currents are small, in the 25 µA range. The V54/74ACT series has a high current sink/source capability for low and high states. Refer to the DC characteristics table for the detailed specification numbers.

## BACKPLANE SIGNAL LINE INTERCONNECTIONS

The VMEbus™ is an asynchronous, high-speed bus intended for high-performance systems. The backplane signals must be treated as transmission lines. These backplanes are characterized by the following features:

- Maximum signal line length is 19".

- Maximum number of slots (loads) is 20.

- Termination networks at each end of the bus.

Thus, the fan-out is limited to a maximum of 20 loads. The VMEbus™ can be modeled as a transmission line with distributed loads. The backplane line has an intrinsic characteristic impedance Z<sub>O</sub>. The fan-out along a signal line lowers the effective characteristic impedance to Z<sub>O</sub>', as given by the equation:

$$Z_{O'} = Z_{O'} \{ \sqrt{1 + (C_{D'}C_{O'}) \}}$$

(for strip lines)

Z<sub>O</sub> is the unloaded line impedance.

CD is the total distributed capacitance.

C<sub>O</sub> is the line intrinsic capacitance per unit length.

I is the line length.

## TRANSMISSION LINE CHARACTERISTICS OF SOME INTERCONNECT MEDIA

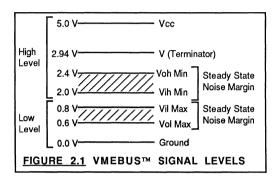

Figures 2.2 through 2.5 show various transmission line types that can be used for interconnecting high-speed logic systems. A brief description and general impedance estimation formulas are given in the following section. This is included to give a flavor of the information and data needed to do a typical design of bus driver circuits. The description is by no means complete and comprehensive, but is used to illustrate the procedure that should be followed for the actual design.

#### 1) COAXIAL CABLE, TWISTED PAIR

Figure 2.2 shows a coaxial cable and a twisted pair. Coaxial cable is available with characteristic impedances of 50, 75, 100, and 125 ohms. The twisted pair can be made from standard hookup wire. A twisted pair has a characteristic impedance of approximately 110  $\Omega$ . This wire type can be used for long line lengths located in the backplane.

#### 2) WIRE OVER GROUND

Figure 2.3 shows the cross-section of a wire over a ground. It can be used for backplane wiring and general breadboarding. The characteristic impedance of this wire is:

$$Z_O = (60/\sqrt{E_r}) \cdot \ln(4h/d)$$

E<sub>r</sub> is the dielectric constant of the medium. d is the diameter of the wire. h is the distance from the ground plane.

#### 3) MICROSTRIP LINES

Figure 2.4 shows the microstrip line. The characteristic impedance Z<sub>O</sub> of a microstrip line is:

$$Z_{O} = [87/\sqrt{(E_{r}+1.41)}] \cdot \ln[5.98h/(0.8w+t)]$$

E<sub>r</sub> is the dielectric constant of the board. h is the thickness of the dielectric. t is the thickness of the line. w is the line width.

The above equation is fairly accurate for ratios of width to thickness between 0.1 and 3.0, and dielectric constants between 1 and 12.

Figures 2.5 and 2.6 show curves for microstrip impedance and capacitance per foot as a function of

line width and spacing. The inductance per foot can be calculated using the following formula:

$$L_0 = Z_0^2 \cdot C_0$$

CO is capacitance per foot.

Z<sub>O</sub> is the characteristic impedance.

The propagation delay of the line can be calculated by using the following formula:

$$tpD = 1.017\sqrt{[0.475E_r+0.67]}$$

ns/ft.

For G-10 fiberglass epoxy boards ( $E_{\Gamma} = 5.0$ ) the propagation delay of the microstrip line is 1.77 ns/ft.

#### 4) STRIPLINE

A strip line consists of a copper strip centered in a dielectric medium between two conducting planes, as shown in Figure 2.7. The characteristic impedance of a stripline, as given by theory, is:

$$Z_{O} = [60/\sqrt{E_{f}}] \cdot \ln\{4b/[0.67\pi w(0.8+(t/w))]\}$$

Figures 2.8 and 2.9 show values of Z<sub>O</sub> and capacitance for various stripline widths and thicknesses. The inductance can be found using the formula:

$$L_O = Z_O^2 \cdot C_O$$

The propagation delay is given by the relation:

$t_{PD} = 1.017 \sqrt{E_r} \text{ ns/ft.}$

The previous text summarizes the various types of interconnect technologies. The actual numbers can be

found by measurements or from the PC board vendors. These numbers will serve as a guide to set up and work through a typical design problem. For further technical information, refer to the reference section at the end of section 1, "System Design Considerations."

#### **DESIGN RULES**

The VMEbus™ specification recommends the following design rules for designing VME boards:

- Circuit traces from the DIN connectors to the onboard circuitry shall not have a length greater than 2".

- No more than one driver and one receiver (or one transceiver) may be connected to any VMEbus™ signal line.

- A standard termination should be used on each end of all VMEbus™ signal lines, as shown in Figure 2.10. A Thevenin equivalent for each termination is also shown.

#### **DESIGN CALCULATIONS**

The microstrip line backplane will be used for the bus lines. Also, the intrinsic impedance must be as high as possible, because  $Z_{O}$  will decrease due to loading.

Let us select:  $Z_O = 120 \Omega$  and w = 25 mils, then  $C_O = 18$  pF/ft or 1.5 pF/inch.

$$Z_{O}'=Z_{O}/\{\sqrt{1+(20/1.5)}\}$$

The bus is 20" long and has at most 20 pF of load on each connector. Hence, under fully-loaded conditions:

$$Z_{\Omega}' = 120/\sqrt{[1+(20/1.5)]} = 31.7 \Omega$$

The propagation delay time of a loaded line may be calculated from the following equation:  $t_{PD}' = t_{PD}\sqrt{1+(C_D/C_O)}$

The unloaded microstrip line has a propagation delay of 1.77 ns/ft.

So:

$$t_{PD} = (20/12) \cdot 1.77 = 2.95 \text{ ns}$$

And:  $t_{PD}' = 2.95 \sqrt{[1+(20/1.5)]} = 11.2 \text{ ns}.$

Thus, a bus line that is fully-loaded with boards, with each board presenting a load as dictated by design rules of no more than 20pF, has a propagation delay of 11.2 ns.

The total capacitive load presented by the bus line is approximately 20•(20) = 400 pF. The driver circuits of the V54/74ACT family will have a typical rise time of 10ns to drive this type of load. Thus, if the bus is driven from one end, the total propagation time for a round trip will be 2•tpD' = 2•11.2 = 22.4 ns. This implies that  $t_{RISE} < 2$ -tpD' and the reflected waveforms will cause a certain amount of ringing. This situation requires the use of termination networks. Reflection diagrams are drawn in Figures 2.11A and 2.11B to show the various voltage and current steps for low-to-high and high-to-low transitions.

## POWER DISSIPATION ADVANTAGE OF ACT PARTS OVER ALS PARTS FOR VMEBUS™ IMPLEMENTATION

Consider a VMEbus™ with transceivers driving the address lines A00-A31, data lines D00-D31, and transfer signals Am0-Am5. This would require nine part types for the full VMEbus™ at each interface. The bus is 20" long and has 20 other transceivers connected to it.

Power Dissipation Calculation: CMOS parts

From the specification sheet for 245s, the typical output capacitance of each output is known to be 10 pF. The total capacitance on the bus can be calculated

as (number of drivers)•(capacitance of each driver) = (20)•(10pF) = 200pF. The capacitance of the 20" bus itself is 20 pF, so the total capacitive load is 20 pF + 200 pF = 220 pF.

Assuming a 1 MHz switching rate and  $V_{CC} = 5V$ , the power dissipation per line can be found:

P =

$$V_{CC}^{2}$$

•f• $C_{L}$

= (25)•(1.0 x 10<sup>6</sup>)•(220 x 10<sup>-12</sup>)

$\approx$ 0.006 Watts

Therefore, each 245 component will use  $8 \cdot 0.008 = 0.048$  watts. For nine parts at each node, the power dissipation for the bus is  $9 \cdot 0.048$ W = 0.432 watts for the complete backplane. The components that are not driving the bus do not dissipate any significant power, having a typical quiescent current of  $10\mu A$ . Therefore, the total power dissipation is 0.576 watts/MHz.

Power Dissipation Calculation: ALS parts.

From specifications for the ALS 245 parts we find that I<sub>CC</sub> of the disabled parts = 63mA. The system has a total of 180 parts - 20 nodes times 9 per node. Therefore the total quiescent power dissipation = 63mA

x 180 parts x 5V = 56.7 watts. This does not include the extra power dissipated due to switching. Figure 2.12 compares the ALS and ACT power dissipations for this system over frequency. The CMOS implementation dissipates 0.576 W/MHz and is linear, while the ALS implementation has a quiescent DC power dissipation of 56.7 watts. This will increase over frequency similar to the CMOS implementation.

The preceding illustration demonstrates the advantage of the V54/74ACT series of parts over the bipolar parts in an actual system environment.

## CONCLUSION

In summary, a short description of a VMEbus™ specification was given, followed by calculations to illustrate how the V54/74ACT series of bus drivers/line transceivers would be used to drive the bus interface to the VMEbus™. The example used the fully-loaded and configured 20 slot VMEbus™. This is the worst-case situation that would be encountered. In a real-life situation, it may not be completely loaded. This would improve the rise/fall times, but also result in higher ringing. The bus should be as per the VME specification. Follow the general design criteria as

outlined in section 1, "System Design Considerations," to do a complete design of physical and electrical aspects of the system.

This section is a simple illustration of the complex task of designing bus interface circuits in a system environment. No timing, speed, performance, or power objectives were considered. The section illustrates that the V54/74ACT family of parts meets the general electrical specifications of the VMEbus™ specification and can be used to design a bus interface. The power dissipation illustration is a case of the overwhelming superiority of the V54/74ACT interface family over ALS and other TTL families.

## REFERENCES

- Kaupp, H.R., "Characteristics of Microstrip Transmission Lines," IEEE Transactions on Electronic Computers, Vol.EC-16, No.2, April 1967, pp.185-193.

- VMEbus™ Specification Manual, Rev.B, Aug 1982, Motorola Inc.

# NOTES

# POWER DISSIPATION FOR THE V54/74ACT FAMILY

#### INTRODUCTION

Extremely low power dissipation with high-speed, high drive capability is a unique feature of the V54/74ACT family of interface components. VTC's ACT series of parts draws three to five orders of magnitude less power than the equivalent ALS parts in the quiescent state. The input current is also less (several orders of magnitude) than that of the equivalent ALS parts, which the ACT series was designed to replace.

The main component of power consumed during switching is dynamic in nature. Dynamic power consumption is due to load capacitance, charging and discharging of internal capacitance, and, to a lesser extent, current spiking during switching.

This section will describe the various causes of power consumption and compare the power dissipation of the V54/74ACT and SN74ALS families of bus interface parts.

## QUIESCENT POWER CONSUMPTION

The V54/74ACT family is designed using advanced CMOS technology. The complementary nature of this technology prevents any direct current path to form between V<sub>CC</sub> and ground, under stable conditions.

Figure 3.1 shows a simple inverter in a steady state. Either the P or the N transistor is off, breaking any direct path between  $V_{CC}$  and ground. However, a small amount of leakage current will usually flow across the reverse-biased diode junctions of the inverter. This reverse-biased leakage current is a function of the thermally generated minority carriers. A change in temperature will cause a change in this current. This reverse-biased leakage current is also known as the quiescent supply current,  $I_{CC}$ . Table 3.1 lists typical

values of quiescent current for a V74ACT240 buffer over operating temperature.

Each device specification contains the quiescent supply current values for that device. This is a direct current that flows from  $V_{CC}$  to ground when the device is in its quiescent state:

All inputs = V<sub>CC</sub> or ground.

All outputs tristate and open.

| TABLE 3.1<br>SUPPLY CURR<br>VCC = 5 V | SUPPLY CURRENT I CC FOR V74ACT240 |    |  |  |  |  |  |  |

|---------------------------------------|-----------------------------------|----|--|--|--|--|--|--|

| Temperature CC Units                  |                                   |    |  |  |  |  |  |  |

| -55 <b>°</b> C                        | 0.01                              | μА |  |  |  |  |  |  |

| 25°C                                  | 0.20                              | μА |  |  |  |  |  |  |

| 125°C                                 | 7.00                              | μА |  |  |  |  |  |  |

The value of this current is a function of input voltage and is higher when the inputs are not at  $V_{CC}$  or ground. The higher quiescent current is caused by the input transistors partially conducting; thus, it is important that in a system environment, the input voltages stay as close as possible to  $V_{CC}$  or ground. This results in minimal current flow and power dissipation.

Figure 3.2 shows the typical quiescent current,  $I_{CC}$ , for various levels of input voltage. To obtain the quiescent power consumption, simply multiply  $I_{CC}$  by the supply voltage, typically 5 volts.

For V74ACT interface parts, the typical power dissipation is:  $5 \text{ V} \cdot 10 \mu\text{A} = 50 \mu\text{W}$

## DYNAMIC POWER CONSUMPTION

As mentioned earlier, the main components of the power dissipation in this family of interface parts are dynamic in nature. These dynamic components can be attributed to the following causes:

- Current flow during switching or switching currents.

- Internal currents due to capacitive switching.

- 3) Dissipation due to external load capacitance.

## 1) SWITCHING CURRENT:

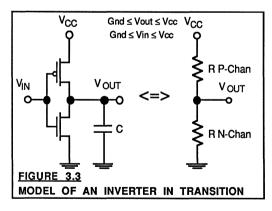

When the inputs to a gate make a transition, both P and N-channel transistors go through a state where one is turning on while the other is turning off. The length and duration of this state is dependent on the rise and fall times of the inputs. Figure 3.3 is a simplified diagram to show the electrical equivalent model of an inverter in transition. The partially on/off devices behave as resistors, allowing a current to flow from V<sub>CC</sub> to ground.

In a typical system environment the inputs rise or fall quickly, within 15 ns. In this situation, a current spike of

short duration occurs during switching. The total power dissipation in this condition is frequency dependent and can be lumped into the second component of power, namely the internal capacitive switching power.

It is difficult to evaluate these two components independently, so they are usually lumped together in an equivalent capacitance, represented by CPDØ, the charging and discharging of which would result in an equivalent power dissipation.

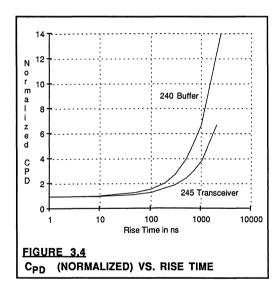

The relationship of interest is the dependence of the component of power dissipation on the rise and fall times of the inputs. If the inputs do not rise fast enough (typically  $\leq$  10 ns), the devices stay turned on for a longer duration. In this case, the base line power dissipation due to  $\mathsf{CPD}\varnothing$  is not adequate to account for the extra power. This can be compensated by varying the value of the capacitor with changes in the rise times of the inputs. Figure 3.4 shows a plot of this new capacitance,  $\mathsf{CpD}$ , normalized with respect to  $\mathsf{CpD}\varnothing$ , versus rise time. The two curves show  $\mathsf{CpD}$  for

transceivers and buffers respectively. All the interface parts will have an effective capacitance  $C_{PD}$  between these two curves. The total power dissipation due to switching frequency 'f' is given by:

$$P_D = C_{PD} \cdot V_{CC}^2 \cdot f$$

V<sub>CC</sub> is the supply voltage.

C<sub>PD</sub> is the effective capacitance due to internal capacitance and switching currents.

f is the frequency of the system.

PD is the total internal power dissipation.

# 2) INTERNAL CAPACITANCE TRANSIENT DISSIPATION:

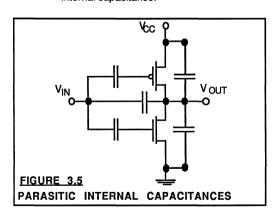

For interface buffers, latches, and transceivers, there exists a certain amount of capacitive load internal to the device itself. This capacitance is due to a variety of factors, such as the gate capacitance, Miller capacitance, and junction capacitance, which are shown in Figure 3.5.

All the capacitances get charged and discharged during the course of the circuits switching. These components of power dissipation are dependent on the technology used, the oxide thickness of the field and gate, and the topology of the individual component.

As mentioned above, any capacitive power dissipation is a function of the frequency of operation. The internal power dissipation is given by:

$$P_I = C_I \cdot V_{CC}^{2} \cdot f$$

V<sub>CC</sub> is the supply voltage.

f is the frequency of the system.

C<sub>I</sub> is the total internal equivalent capacitance.

P<sub>I</sub> is the internal power dissipation due to internal capacitance.

As mentioned earlier in relationship to switching current equivalent power dissipation, internal capacitance and switching current components of power dissipation are rather difficult to isolate. For all further discussion, they will be lumped together and represented by CpD. Note: CpD could be a function of rise time for rise times greater than 100 ns.

# 3) EXTERNAL LOAD CAPACITANCE TRANSIENT DISSIPATION:

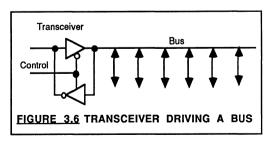

For the bus drivers and transceivers, external load capacitance is usually the biggest component of power dissipation in the system environment. The interconnect or bus lines present capacitance, and the various other devices present on the line also contribute their respective input or output capacitance.

Stray capacitance due to coupling and other factors is also present. All of these capacitors need to be charged and discharged during the normal course of signal switching. The power dissipation as a result of charging and discharging this external load capacitance can be evaluated by:

$$P_L = V_{CC}^{2} \cdot (C_{L1} \cdot f_1 + C_{L2} \cdot f_2 + C_{L3} \cdot f_3 + \dots C_{Ln} \cdot f_n)$$

C<sub>Ln</sub> are the various loads on the respective outputs.

fn are the respective switching frequencies for each output.

V<sub>CC</sub> is the supply voltage.

P<sub>1</sub> is the power dissipation due to the load.