# COMPUTER JUNE 1981 DESIGN THE MAGAZINE OF COMPUTER BASED SYSTEMS

**BUBBLE MEMORY CIRCUITS PROMOTE 3-DIMENSIONAL STACKING** IEEE 488 ERROR HANDLING TECHNIQUES: PROS AND CONS FPLA ARBITER CONCEPT ADAPTS TO APPLICATION NEEDS

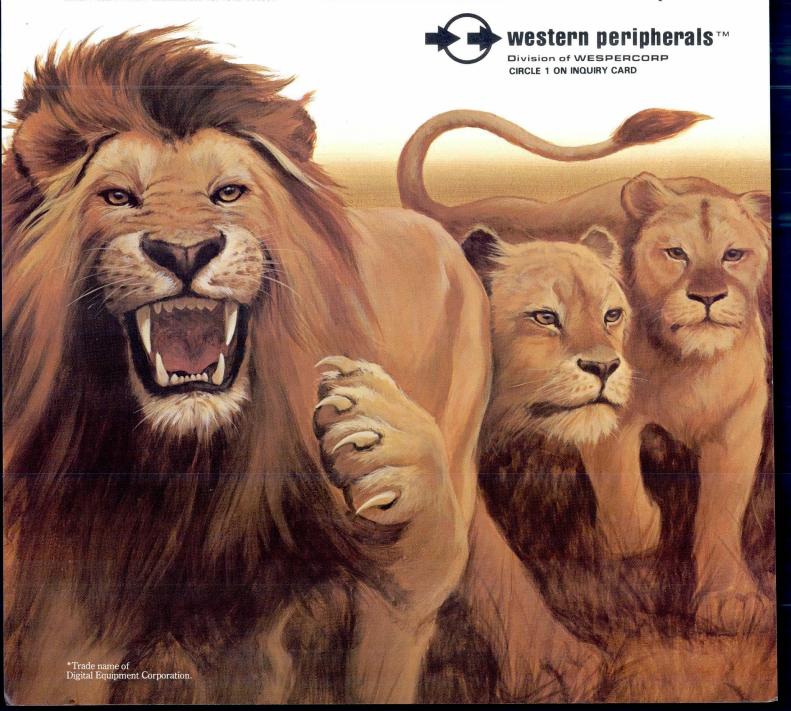

## Family pride.

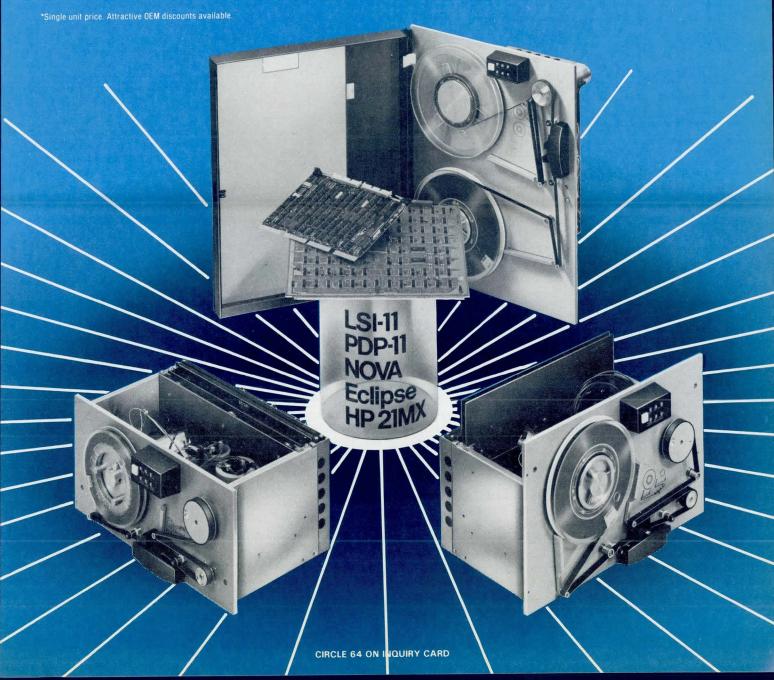

Now there's an advanced technology family of single board controllers for DEC\* computers from Western Peripherals—the number one name in controllers.

The TC-131 (for PDP-11s\*) is the first TM-11 emulating controller to combine PE and NRZ on one

standard hex board. It lets you mix 9-track, PE, NRZ or dual density tape units in any combination up to 125 ips. A 64 byte data buffer allows installation at any point on the unibus without consideration of NPR priority.

The TC-151 single board NRZI tape controller interfaces any industry-standard drive to the LSI-11\* Add a dual width Phase Encode Board for the same performance as the TC-131.

The DC-231 accommodates up to four SMD disc drives of 40 to 600 mb each with RMO2 emulation. Its four sector (2048 bytes) data buffer makes "data-late" errors a thing of the past. The advanced technology "micro-engine" allows a complete track to be written on a single drive revolution. A measurable performance advantage for your PDP-11.

All three controllers are software compatible. All have self test. All are backed by one of the best factory service organizations in the business. And all can be delivered in 30 days.

For more information, call or write today: Western Peripherals Division, Wespercorp, 14321 Myford Road, Tustin, CA 92680, U.S.A. (714) 730-6250. TWX: 910 595-1775. CABLE: WESPER

Number 1 in controllers for DEC and Data General computers.

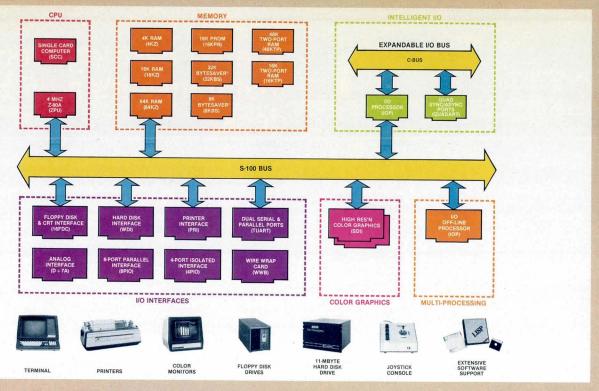

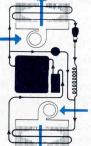

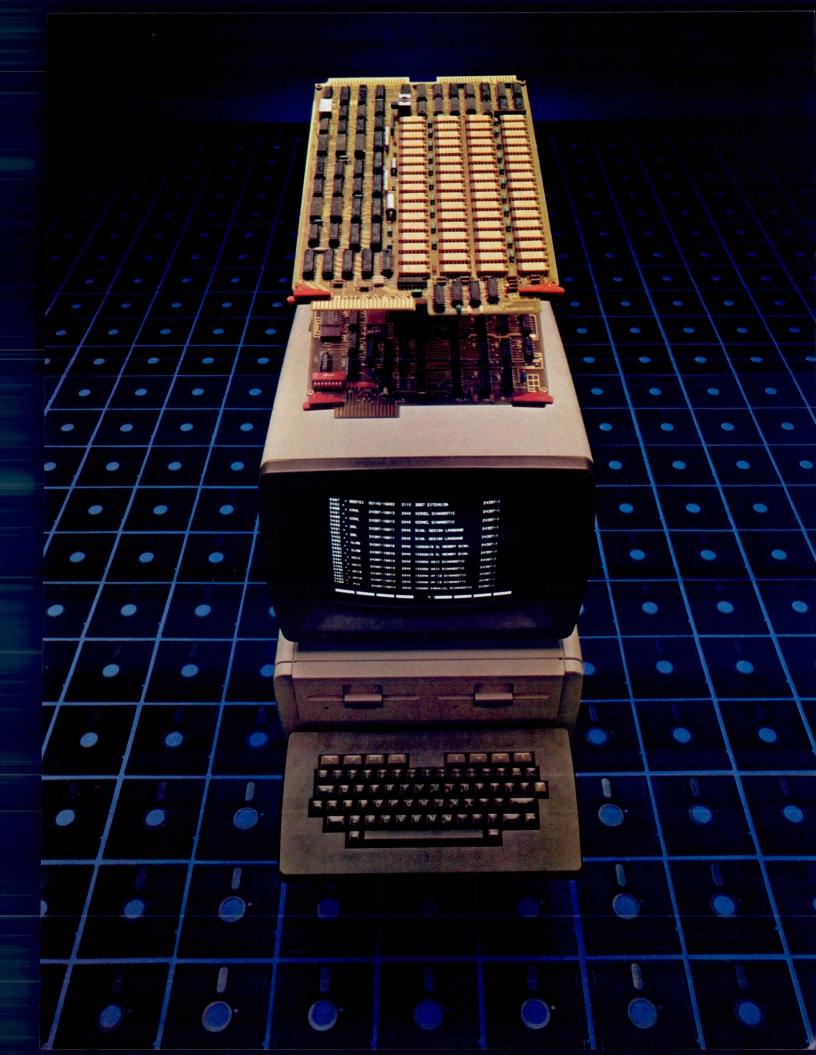

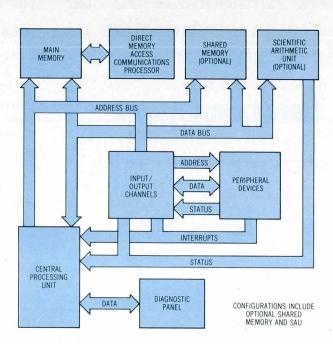

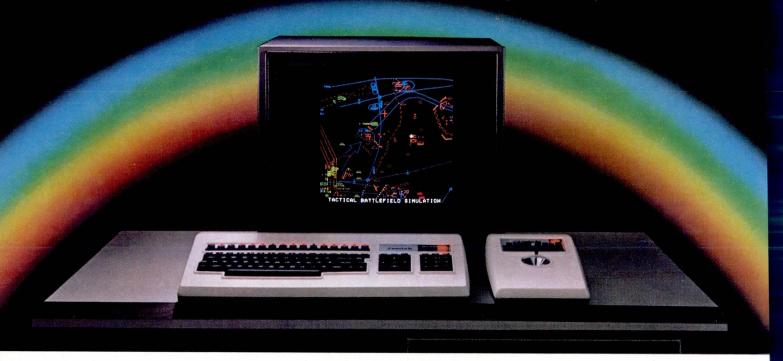

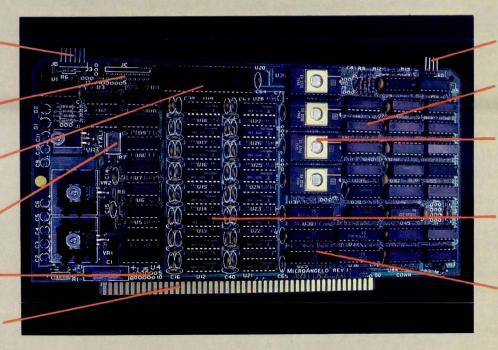

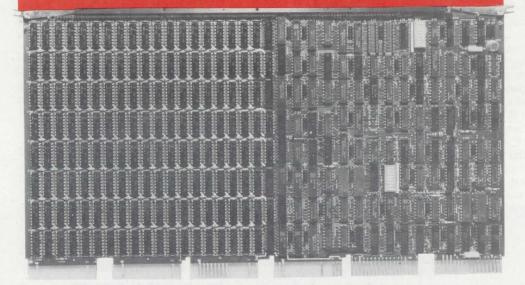

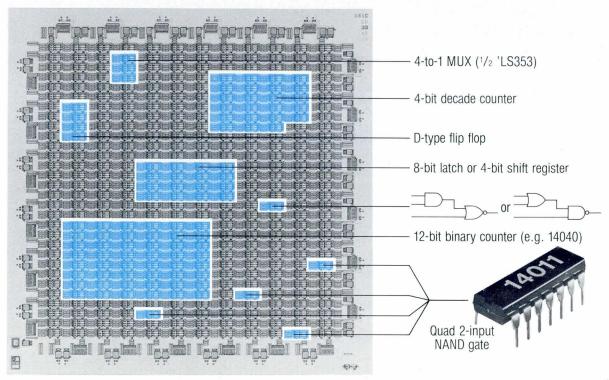

# What Cromemco computer card capability can do for you

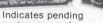

The above diagram shows in a functional way one of the most complete lines of computer cards in the industry.

Look it over carefully. It could be well worth your while.

These are all cards that plug into our S-100 bus microcomputers.

You can also assemble them into a custom system in convenient Cromemco card cages.

## MULTI-PROCESSING AND INTELLIGENT I/O

The range of capabilities and versatility you can draw upon is enormous.

In processors, for example, you have a choice of CPU's including our extremely useful new I/O Processor. This can be used as a satellite processor to do off-line processing, multi-processing, and to form intelligent I/O. It opens the door to a whole new group of applications and tasks. Ask us about it.

## HIGH RESOLUTION COLOR GRAPHICS

Again, you can have beautiful highresolution color graphics with our color graphics interface. You can select from over 4000 colors and have a picture with a resolution at least equal to quality broadcast-TV pictures.

You have an unprecedented selection of memory including our unusual 48K and 16K **two-port** RAMs which allow high-speed color graphics.

#### LOTS OF STORAGE

These days you often want lots of disk storage. So you can select from our disk controller card which will operate our 5" and 8" floppy disk drives (up to 1.2 megabytes). Or select our WDI interface to operate our 11-megabyte hard disk drives.

## POWERFUL SOFTWARE AND PERIPHERAL SUPPORT

There's much more yet you can do with our cards. And, of course, there's an easy way to put them to work in our 8-, 12-, and 21-slot card cages. Our PS8 power supply makes it simple to get the system into operation.

Finally, Cromemco offers you the strongest software support in the industry

with languages like FORTRAN, C, COBOL, ASSEMBLER, LISP, BASIC and others. There is also a wide choice from independent vendors.

To top it all off, you can draw from a substantial array of peripherals: terminals, printers, color monitors and disk drives.

#### **CONTACT YOUR CROMEMCO REP**

There is even more capability than we're able to describe here.

Contact your Cromemco rep now and get this capability working for you.

#### **CROMEMCO COMPUTER CARDS**

• PROCESSORS — 4 MHz Z-80 A CPU, single card computer, I/O processor • MEMORY — up to 64K including special 48K and 16K two-port RAMS and our very well known BYTESAVERS® with PROM programming capability • HIGH RESOLUTION COLOR GRAPHICS — our SDI offers up to 754 x 482 pixel resolution. • GENERAL PURPOSE INTERFACES —QUADART four-channel serial communications, TU-ART two-channel parallel and two-channel serial, 8PIO 8-port parallel, 4PIO 4-port isolated parallel, D+7A 7-channel D/A and A/D converter, printer interface, floppy disk controller with RS-232 interface and system diagnostics, wire-wrap and extender cards for your development work.

Cromemco

280 BERNARDO AVE., MOUNTAIN VIEW, CA 94040 • (415) 964-7400 Tomorrow's computers today

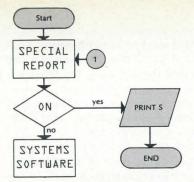

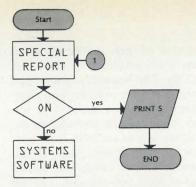

## COMPUTER DESIGN®

THE MAGAZINE OF COMPUTER BASED SYSTEMS

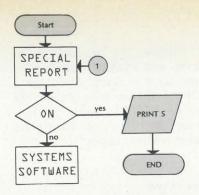

## SPECIAL REPORT ON SYSTEMS SOFTWARE

87

#### FEATURES

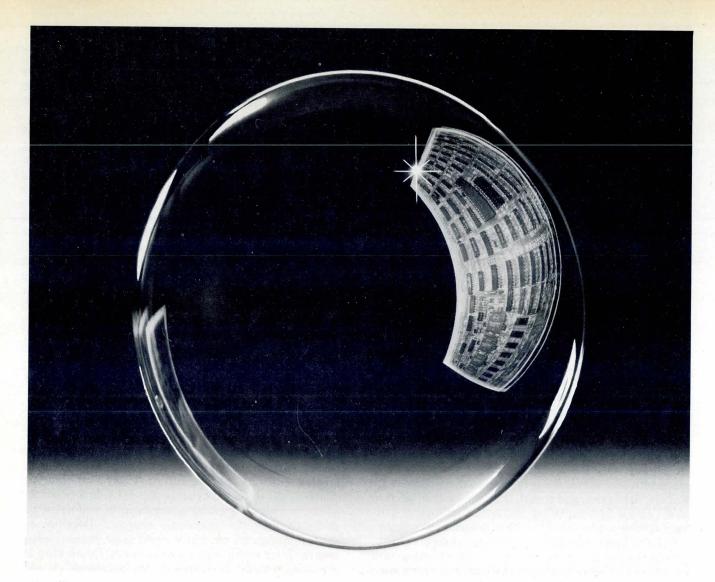

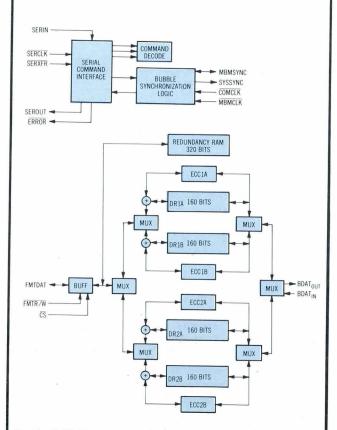

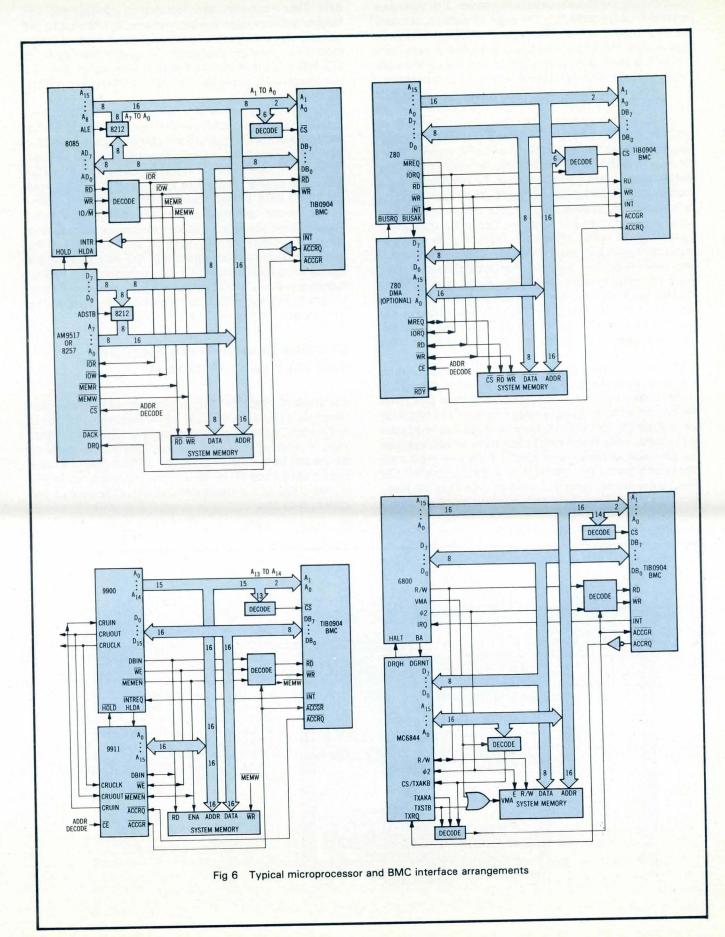

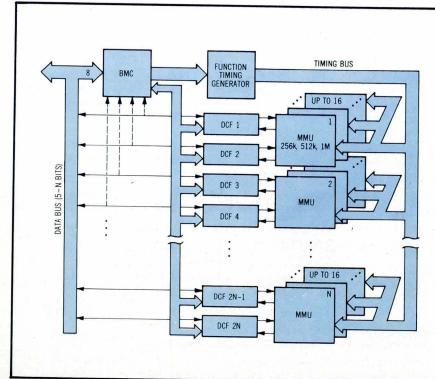

## BUBBLE MEMORY CIRCUITS PROMOTE 3-DIMENSIONAL STACKING

135

### by Russell MacDonald

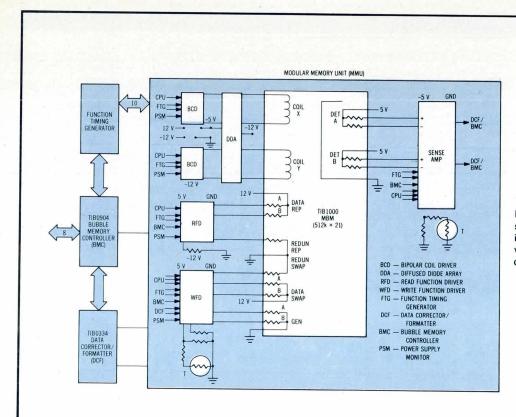

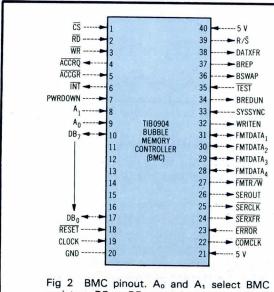

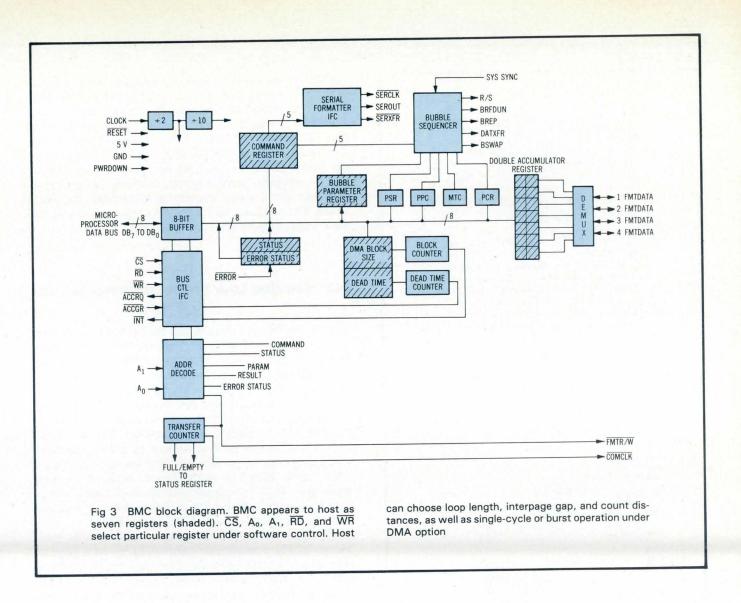

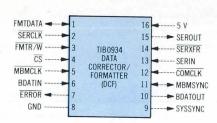

Interface circuit flexibility of high performance bubble memories gives designers a competitive edge in customizing transfer rate, storage capacity, and access technique for a variety of host processors and storage applications

## IEEE 488 ERROR HANDLING TECHNIQUES: PROS AND CONS by Louis F. Santora, Jr

Comparison of several methods to detect and report errors enables designers of IEEE 488 based instruments to reduce controller overhead without adding system integration constraints

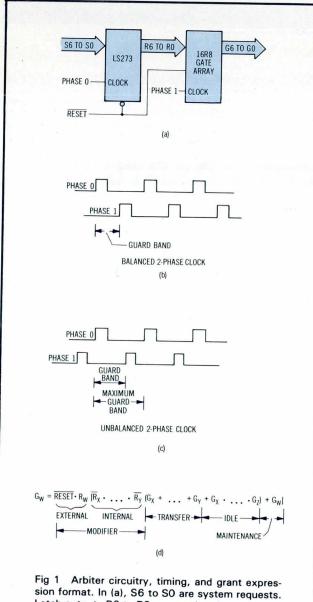

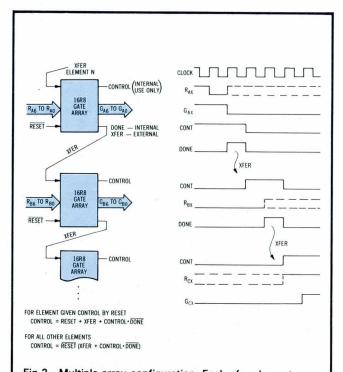

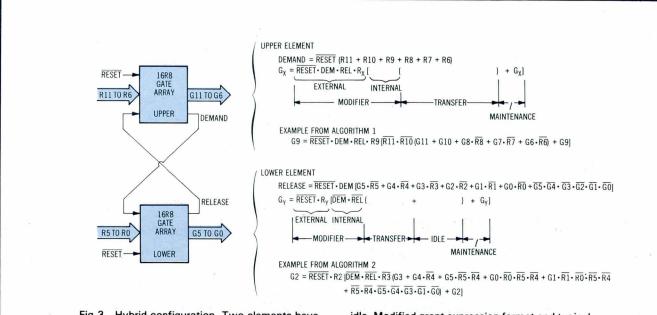

## FPLA ARBITER CONCEPT ADAPTS TO APPLICATION NEEDS 149 by Alan W. Bentley

Customizable arbiter concept uses versatile Boolean statement format to implement control protocol and grant algorithms in field programmable logic

## **JUNE 1981**

**VOLUME 20, NUMBER 6**

### DEPARTMENTS

- 9 EDITORIAL

- 14 CALENDAR

- 20 LETTERS TO THE EDITOR

- 25 COMMUNICATION CHANNEL

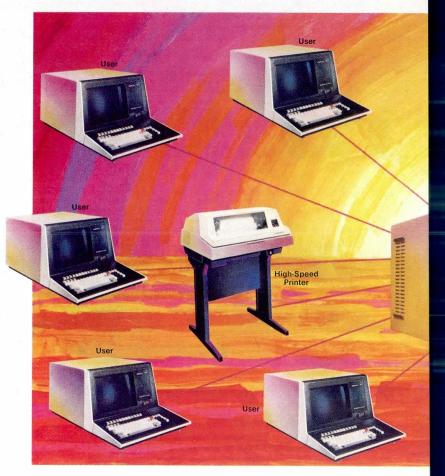

Statistical multiplexers have brought considerable sophistication to data communications and have added a number of features that enhance data network design. There are a few constraints that must be observed, however, before they are applied to a system

- 50 TECHNOLOGY REVIEW

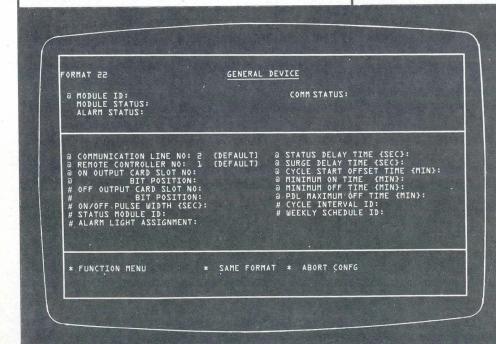

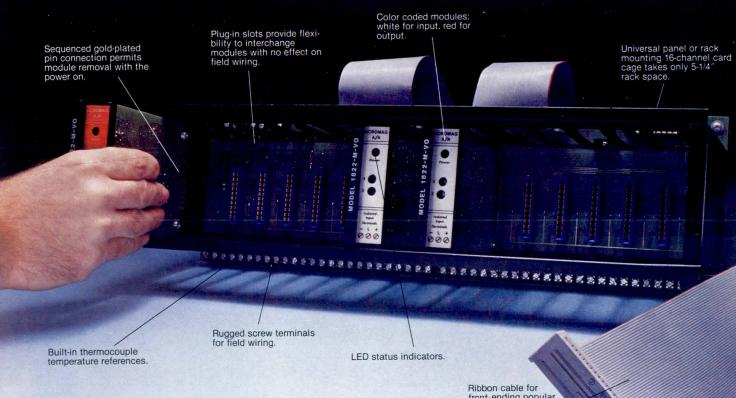

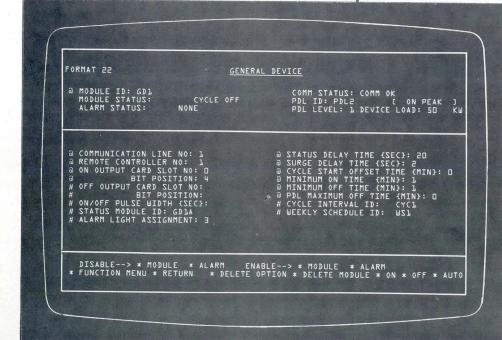

- 76 DIGITAL CONTROL AND AUTOMATION SYSTEMS

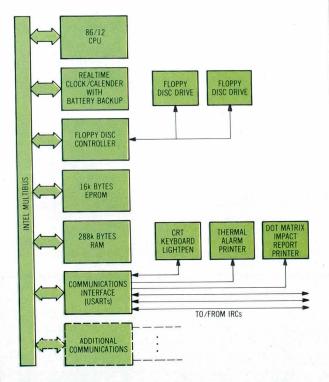

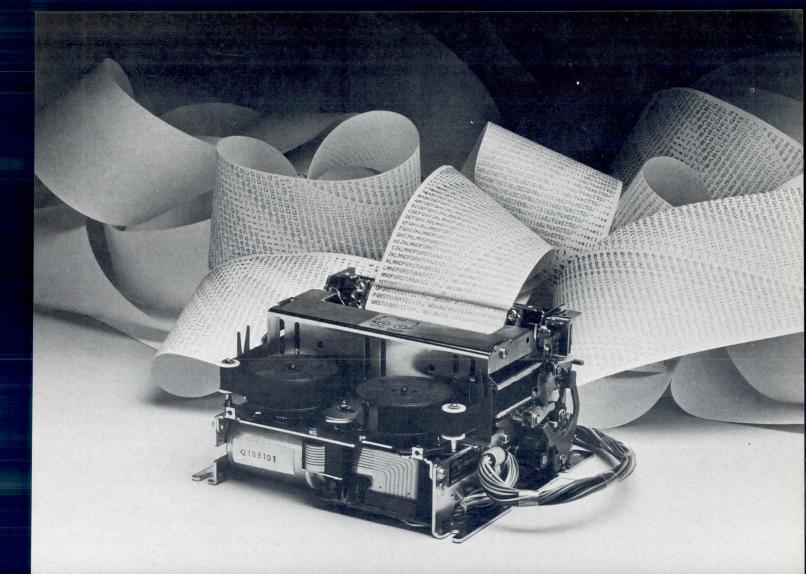

Microprocessor based user programmable plant management system employs intelligent remote controllers to reduce energy consumption throughout half million square foot complex

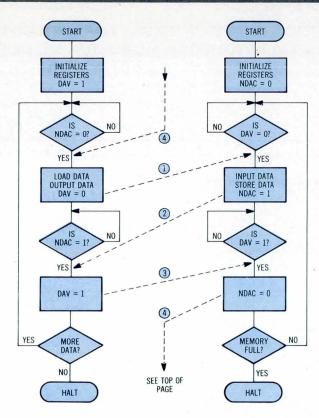

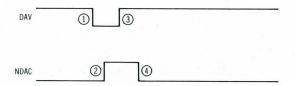

#### 156 MICRO DATA STACK

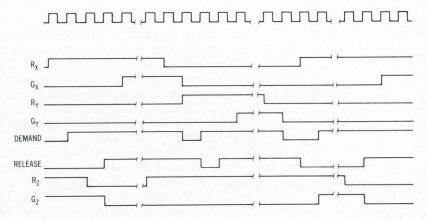

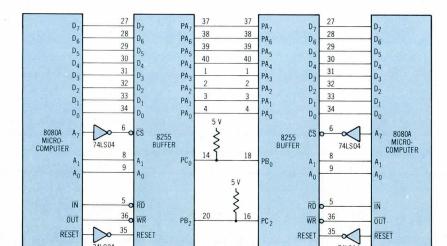

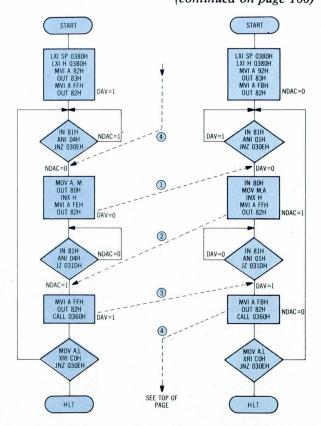

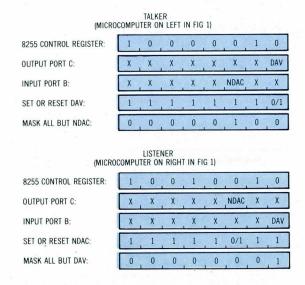

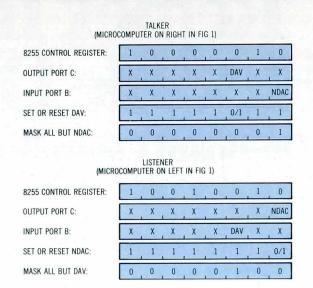

A 2-wire interlocked handshake procedure synchronizes data transfer between talker and listener 8080A based microcomputers in a double-buffered, conditional I/O system

#### 174 AROUND THE IC LOOP

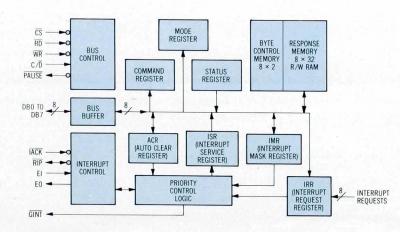

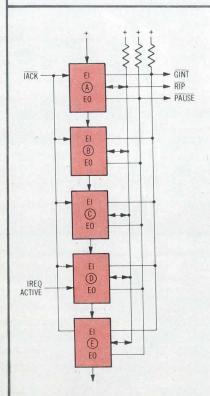

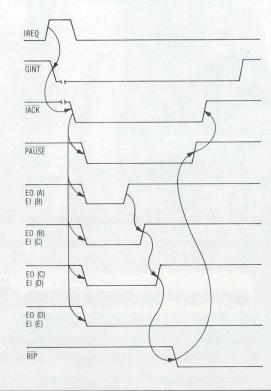

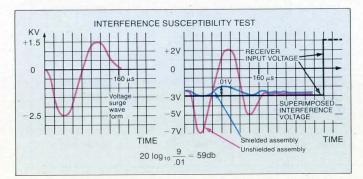

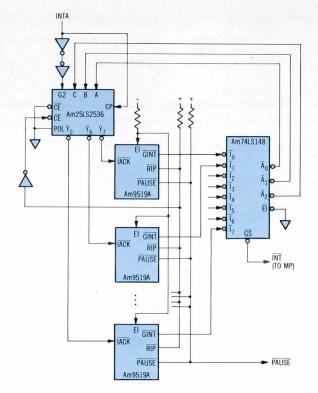

Peripheral to the central processor, universal interrupt controllers improve system throughput and response time by allowing external devices to asynchronously modify the instruction sequence

- 190 PRODUCTS

- 226 LITERATURE

- 229 SYSTEMS SHOWCASE

- 230 ADVERTISERS' INDEX

Reader Service Cards pages 233-236

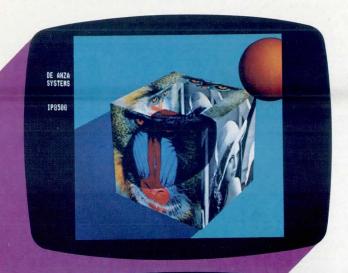

Cover Artist: Darcy Gerbarg Cromemco Time Arts Synthesis, Mountain View, Calif. John Dunn, Director **♥BPA**

Computer Design® is published monthly. Copyright 1981 by Computer Design Publishing Co, a division of PennWell Publishing Co. Controlled circulation postage paid at Tulsa, Okla. No material may be reprinted without permission. Postmaster CHANGE OF ADDRESS—FORM 3579 to be sent to Computer Design, Circulation Dept, PO Box A, Winchester, MA 01890. Subscription rate is \$30.00 in U.S.A., Canada, and Mexico, and \$50.00 elsewhere. Microfilm copies of Computer Design are available and may be purchased from University Microfilms, a Xerox Company, 300 N Zeeb Rd, Ann Arbor, MI 48106 (USPS 127-340)

Computer Design is a registered trademark of Computer Design Publishing Company

**CIRCLE 4 ON INQUIRY CARD**

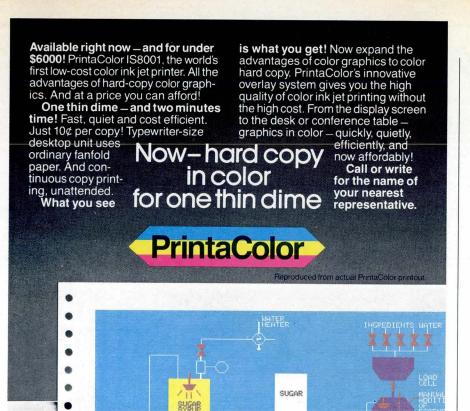

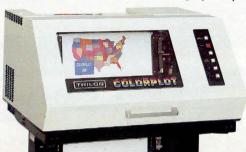

PrintaColor Corporation P.O. Box 52 Norcross, Georgia 30091 404/448-2675

### STAFF

Publisher Ronald W. Evans President & Founder **Robert Brotherston**

#### Editorial

Editor Saul B. Dinman

Managing Editor Sydney F. Shapiro

**Technical Editor** Shawn Spilman

Senior Editor Peg Killmon

Field Editor S. Calif & SW (213) 824-5438 Michael Chester

Field Editor N. Calif & NW (408) 371-8901 **Douglas Eidsmore**

Associate Editors James W. Hughes Colleen G. da Silva

Copy Editors

Debra M. Highberger Sue Paxman Debra M. Jun U. Smith

Editorial Advisory Board Brian W. Pollard Ralph J. Preiss Rex Rice

#### Circulation

Circulation Director Robert P. Dromgoole Data Control Manager Wanda Holt Circulation Manager Alma Brotherston

#### **Production**

**Production Manager** Linda M. Wright **Production Assistant** Lou Ann Sawyer Advertising Coordinators

Sally H. Bowers Cherie Cr Cherie Crosby Technical Art

Concents Unlimited

#### Marketing

Director of Marketing Gene Pritchard Marketing Services Manager Linda G. Clark **Promotion Manager Tom Hodges**

#### **Financial**

Administrative Director John O. McGillivray Controller David C. Ciommo

## Computer System

Research Director Wayne Newman

**Editorial & Executive Offices** 11 Goldsmith St, Littleton, MA 01460 Tel. (617) 486-8944/(617) 646-7872

Editorial manuscripts should be addressed to Editor, Computer Design, 11 Goldsmith St., Littleton, MA 01460. For details on the preparation and submission of manuscripts, request a copy of the "Computer Design Author's Guide."

\*(TM)

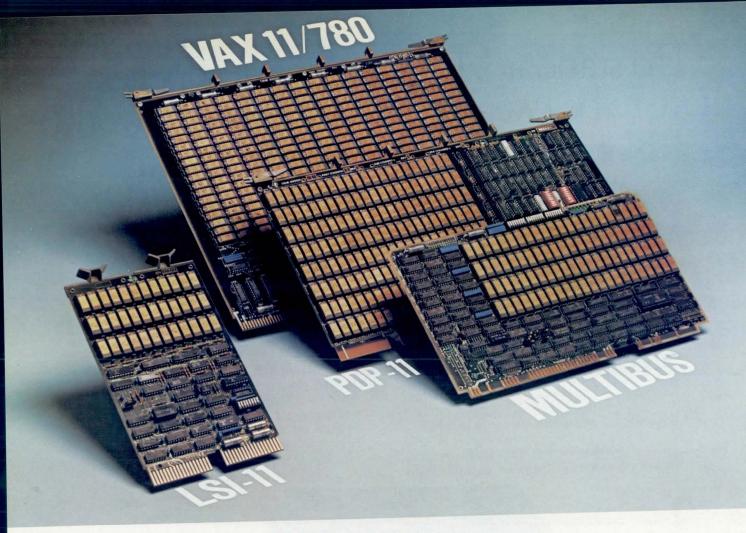

ALSO FROM DATARAM

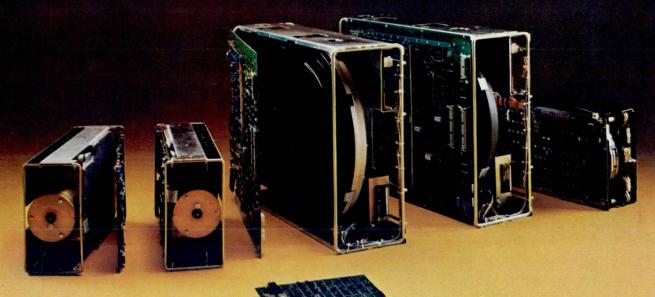

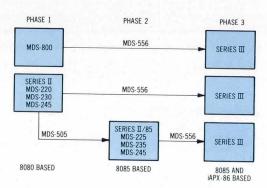

Now, from the company that delivers the industry's widest range of DEC-compatible memory products, a family of peripheral controllers that's second to none. From comparatively simple cartridge disk controllers to complex 300MB storage module drive (SMD) controllers.

An impressive array of state-of-the-art controllers, all built around high-speed bipolar microprocessors. All software compatible with the host LSI-11® or

PDP®-11 minicomputer...and all available now.

And Dataram's controllers are designed to save you money, and a lot more. Like space — our controllers typically occupy half the space required for the comparable controller from DEC. Doing it with a level of performance that makes any member of this family worth looking at.

Look at the chart of our current family of peripheral controllers, growing every Tel: 609-799-0071 TWX: 510-685-2542

day. If you don't see the controller you need, we're probably working on it right now. Call us and discuss your requirements.

DEC, LSI-II and PDP are registered trademarks of Digital Equipment Corporation

## CRPORATION

Princeton Road Cranbury, New Jersey 08512.

| DATARAM       | Magnetic Tape Controller |        |        |        | lge Disk<br>troller |        |        |        |        |        |        |

|---------------|--------------------------|--------|--------|--------|---------------------|--------|--------|--------|--------|--------|--------|

| CONTROLLER    | T03                      | T04    | T34    | C03    | C33                 | S03/A  | S03/B  | S03/C  | S33/A  | S33/B  | S33/C  |

| MINI          | LSI-11                   | LSI-11 | PDP-11 | LSI-11 | PDP-11              | LSI-11 | LSI-11 | LSI-11 | PDP-11 | PDP-11 | PDP-11 |

| COMPATIBILITY |                          | M11/TU | 10     | RI     | K05                 | RM02   | RK07   | RP06   | RM02   | RK07   | RP06   |

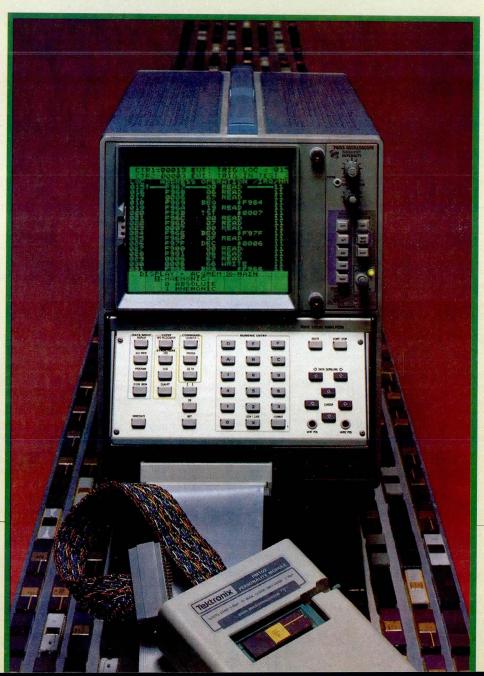

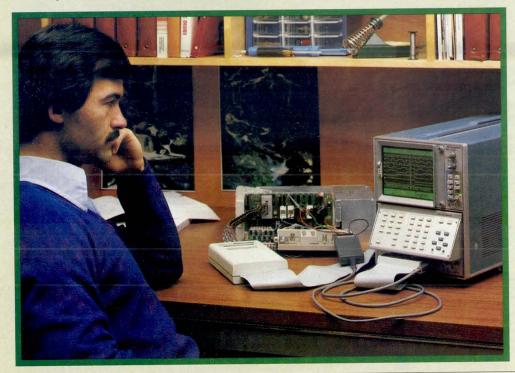

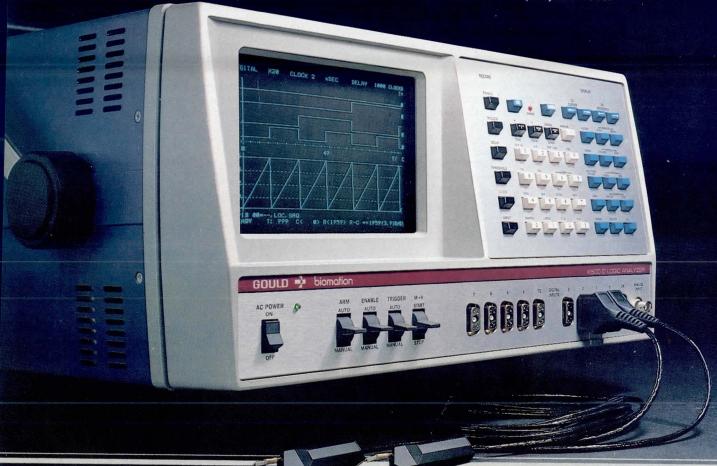

## The logic analyzer for

## The solution to your problems.

Now. A logic analyzer made expressly for microprocessor-based design.

## The Tektronix 7D02.

An instrument that provides solutions instead of compounding problems. That cuts design time and improves cost-effectiveness.

## Look at just a few examples:

**Design Problem:** Adapting your logic analyzer to work with a specific processor.

**7D02 Solution:** Just plug the  $\mu$ P-specific 7D02 probe directly into the prototype microprocessor socket and press START. Acquired data is immediately disassembled and displayed in your processor's own mnemonics.

**Design Problem:** Sorting error-related data from other program flow.

**7D02 Solution:** Programmable data and clock qualification filters the data and stores only information pertinent to the problem.

**Design Problem:** Relating hardware activity to program flow.

**7D02 Solution:** State and timing sections are included in a single logic analyzer, with each section able to trigger or qualify data acquisition by the other.

**Design Problem:** Monitoring I/O activity on the system bus.

**7D02 Solution:** Acquire both synchronous and asynchronous data through interactive triggering to examine both slides of an I/O transaction.

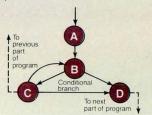

**Design Problem:** Tracking program flow through non-sequential algorithms with conditional branches to pinpoint an error.

**7D02 Solution:** The 7D02 can monitor multiple events and conditionally branch as part of its trigger or data qualification sequence. As a result, it can detect an error condition anywhere in your program flow.

## microprocessor-based design.

## 7D02. The solution.

No matter how you look at it, the 7D02 has what you need for faster, more efficient microprocessorbased design.

A series of probe modules adapt the 7D02 to major 8-bit and 16-bit processors, both now and in the future. There's also a general purpose probe for use with microprocessors not specifically supported today. It may also be used like a conventional logic analyzer for troubleshooting the peripheral elements of the system you're designing.

You can have up to 52 channels of synchronous data acquisition, of which 8 channels can be used to acquire asynchronous data at speeds to 50 MHz for timing analysis.

Data acquisition resources include four word recognizers and two interactive counters that can be reset on the fly. Also several modes of both data and clock qualification.

You get two levels of glitch triggering with a resolution of 5 ns, and a separate glitch memory. Plus separate acquisition and reference memories for quick data comparisons.

And all the 7D02's resources are quickly and clearly configurable through a simple user language. One that lets you trigger right on a problem instead of around it. Minimum programming input yields maximum insight into your prototype's software and hardware activity.

For more information on the 7D02, contact your Tek Sales Engineer or call us toll-free. 1-800-547-6711.

## You'll wonder how you ever designed without it.

For further information, contact:

U.S.A., Asia, Australia, Central & South America, Japan Tektronix, Inc. PO. Box 4828 Portland, OR 97208 Phone: 800/547-6711 Oregon only 800/452-6773 Telex: 910-467-8708 Cable: TEKTRONIX

Europe, Africa, Middle East Tektronix International, Inc. European Marketing Centre Postbox 827 1180 AV Amstelveen The Netherlands Telex: 18312

Canada Tektronix Canada Inc. P.O. Box 6500 Barrie, Ontario L4M 4V3 Phone: 705/737-2700

> Circle 7 for Literature Circle 147 for Sales Call

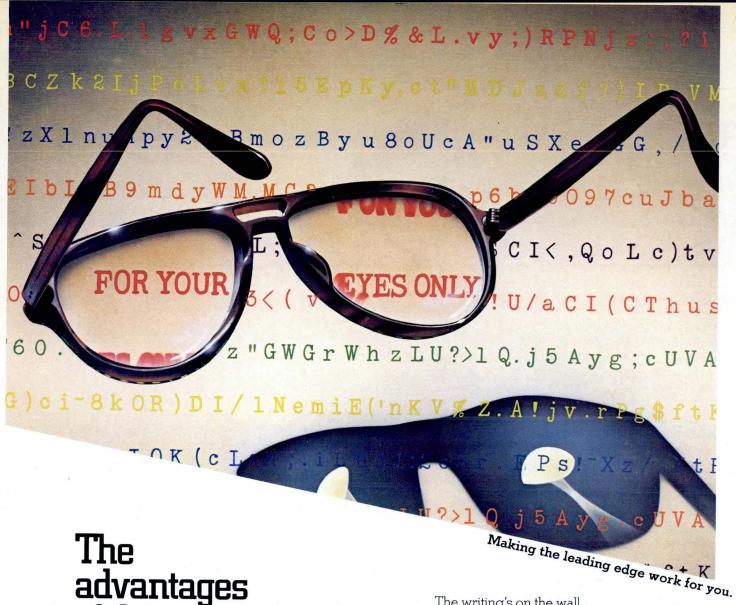

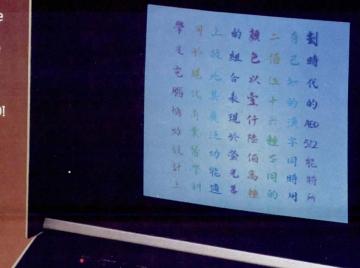

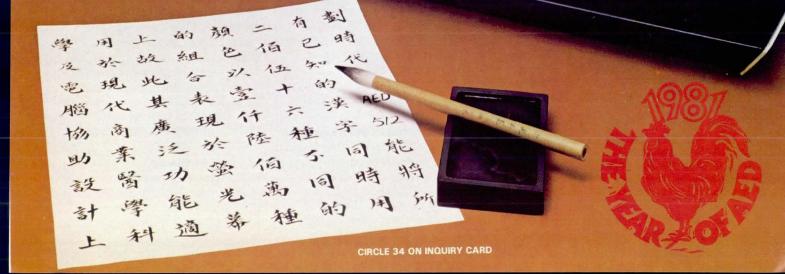

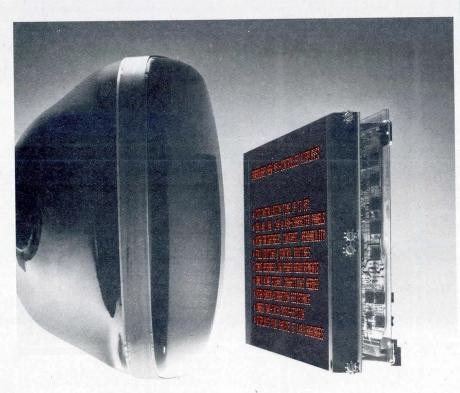

The advantages of data encryption are now plain to see.

The writing's on the wall.

File security is the feature more and more end-users are demanding. Especially in word processing and small business systems.

And that can translate into a significant product advantage. If you make the effort to include data encryption in your next design.

Fact is, implementation's never been easier. Or more cost-effective. Thanks to Western Digital's WD 2001 data encryption device.

Based on the NBS Data Encryption Algorithm, our compact WD 2001 is a single-chip solution that delivers full NBS certification, a 1.3 Mb/s throughput rate and can be bus or hardware controlled. It's also available for immediate delivery.

So contact Western Digital for your own set of WD 2001 specs. And all the latest on our CryptoPrimer™ development kit.

There's more profit in seeing things our way.

## **WARNING:** emi radiation could be hazardous to your company's health

My attention was recently redirected to FCC Rules and Regulations parts 2 and 15 as amended to encompass digital equipment. While attending NCC, I thought it might be interesting to take a quick straw poll on the floor of the show to see what, if any, is the level of awareness of the FCC emi (electromagnetic interference) regulations. The variety of answers received was interesting, and a casual check of the backs of various pieces of equipments that are already subject to parts of the new

ing requirements that have been in effect since January 1, 1981.

Briefly, those amendments to parts 2 and 15 set forth restrictions on the level of permissable emi that a piece of digital equipment may generate. The law comes in two flavors: one for commercial equipment and a more stringent version for equipment used in the home.

If you have any doubts whether or not digital devices radiate rf energy, try this simple test (probably invented by an old IBM 704 operator). Take one of the currently popular calculators (the more complex, the better), turn it on, and hold a small pocket radio near it. Tune the dial on the radio and listen to the assortment of squawks and squeaks—that's emi. Chances are that the only activities going on are a keyboard scan loop and the display multiplexing—think what happens when one of those plasticencased desktop micro wizards is doing an ISAM update!

These FCC regulations could have the same earmarks of a potential disaster for our industry as did the early EPA automobile emission standards for the automobile industry. It is also a pretty safe bet that they are not going to disappear into a haze of

deregulation.

We'd like to take a quickie editorial poll of you, our readers, while there is still time before the commercial equipment (class A) deadline of October 1, 1981. We will tabulate the results on our own noise generating system and promise to lose everyone's identity. We will keep you informed on the results as we compile them and use them to guide us in the selection of future articles on the subject.

Please indicate your answers by circling the appropriate numbers in the score box of

the reader service card.

Saul B. Dinman Editor

Circle 426 Yes, I am aware of the new FCC emi regulations.

Circle 427 We are in the process of complying.

Circle 428 No, I am not aware of them.

Circle 429 I would like to see more information on the subject in print.

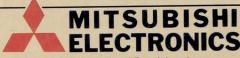

# Independent benchmarks MC68000 is first choice

The MC68000 consistently and significantly outperformed both the Z8000 and the i8086 in **three** current independent benchmark studies. Evaluations by engineers on the associated with any microprocessor supplier demonstrate that the microprocessor system with the best overall performance is the M

the best overall performance is the MC68000, making it the clear choice for new designs.

And it's clear that the MC68000 is now recog-

And it's clear that the MC68000 is now recognized as the competitive edge for end-use systems. Design engineers recently confirmed that it is the first choice among 16-bit microprocessors in two independent product preference polls.\*

## Benchmarks measure MC68000 performance advantages.

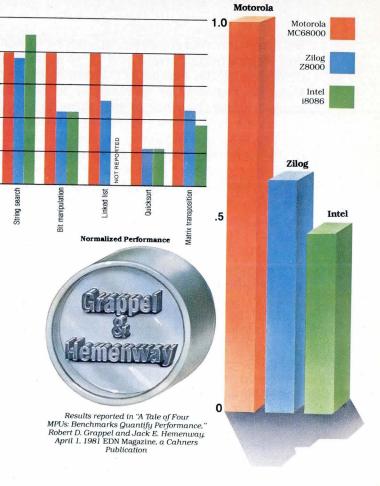

Results of a performance comparison for a digital filter application by V.P. Nelson and H. T. Nagle, published in *IEEE Micro*, find the MC68000 nearly twice as fast as the Z8000 and almost three times as fast as the i8086.

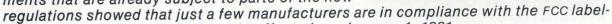

A variety of benchmarks from the Carnegie-Mellon series as reported in *EDN* magazine by Grappel and Hemenway show that the MC68000 is significantly faster than each of these devices in handling routines for Bit Test/Set/Reset, Linked Lists,†Quicksort, and Boolean Matrix. In the same study, it also compares favorably for I/O interrupts. Overall, it outperforms the i8086 by 2.16 to 1.0 and the Z8000 by 1.71 to 1.0, even with the MC68000 addressing its full 16-Megabyte address space and the other two MPUs addressing only 64K.

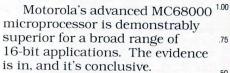

Benchmarks from the Blacksburg Group, being published by Howard W. Sams and Co., indicate that the MC68000 is two times to three times as fast in four‡out of five routines compared, including Sorts, Square Root, and Sine Look-up.

Still other benchmarks give the edge to the MC68000 for execution of multiprecision binary and BCD arithmetic operations, 32-bit array scans and string translations. Floating Point arithmetic operations can be carried out almost as fast as hardware implementations.

## Memory address, 32-bit features enhance performance.

The performance advantages of the MC68000 demonstrated in the studies are impressive. And the MC68000 has still other capabilities of equal importance in helping keep you ahead of your competition.

The MC68000 has seventeen 32-bit multipurpose registers, with data and address registers separated for parallel operation. All registers can be used as index registers, and all address registers can be used as stack pointers.

No other 16-bit MPU can match the 16-Megabyte direct memory addressing, and programmers need not worry about segmentation and the overhead associated with it.

The simple, efficient instruction set includes 56 powerful types designed to minimize the number of mnemonics a programmer must know. Software development costs are minimized because addressing modes are usable with all applicable instructions.

One other thing. The MC68000 provides, in one high-quality device, what is often found in multi-

<sup>\*</sup>Annual Minicomputer Survey. November 1980, with permission of DATAMATION MAGAZINE, G.S. Grumman/Cowen & Co.

<sup>\*</sup> Electronics 1980 Product Preference Poll, with permission of ELECTRONICS MAGAZINE. McGraw-Hill, Inc.

$<sup>\</sup>dagger Not$  reported for i8086, but Motorola data indicates the MC68000 is more than 20% faster.

<sup>‡</sup>No report for Z8000 on Linked List.

# demonstrate why the for 16-bit MPU applications.

chip arrangements requiring more interconnects, bus coordination, space and cost.

## Keep your systems state-of-the-art.

In addition to the MC68000 microprocessor, Motorola's well-rounded family of existing and future VLSI peripherals is designed so that you can keep your M68000-based systems state-of-the-art for years. And, the 8-bit M6800 Family peripherals interface directly with the MC68000, broadening support with an attractive low-cost, medium-performance option.

Future, extra-performance versions of the MC68000 will be completely bus- and object code-compatible with the present MPU. Upgrading or expanding your system is achieved without making your software obsolete, regardless of the language in which it is written.

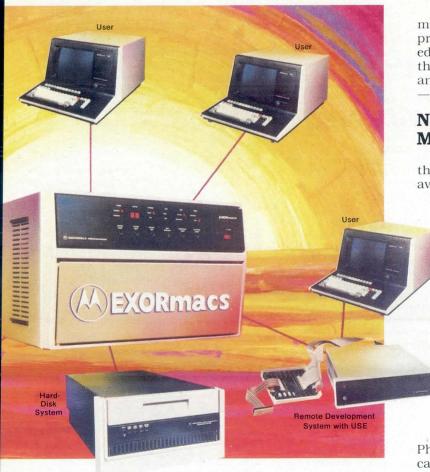

The M68000 Family is supported by EXORmacs™, the multiuser development system created for the 16-bit and 32-bit M68000 Family designs, and beyond.

For more information on the MC68000 and the M68000 Family, complete and mail the coupon or send your written request to Motorola Semiconductor Products, Inc., P.O. Box 29012, Phoenix, AZ 85036.

Use the MPU that can make your 16-/32-bit system a winner. Commit yourself to leadership with the M68000 Family in

Innovative systems through silicon.

| Please send me infor | mation on N | 1CE | 800 | 0. | CD6/8 |

|----------------------|-------------|-----|-----|----|-------|

| Name                 |             |     |     |    |       |

| Title                | Tel.: (     |     | )   |    |       |

| Company              | 73          |     |     |    |       |

| Address/Mail Drop    | 4 4 1 1     |     | 4   |    |       |

| City                 |             |     |     |    |       |

| State                |             | ZIP |     |    |       |

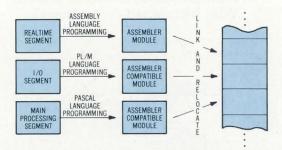

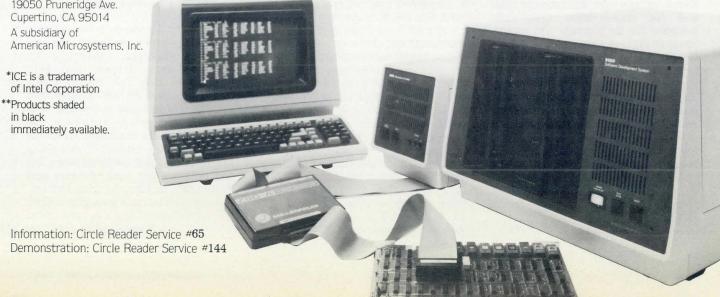

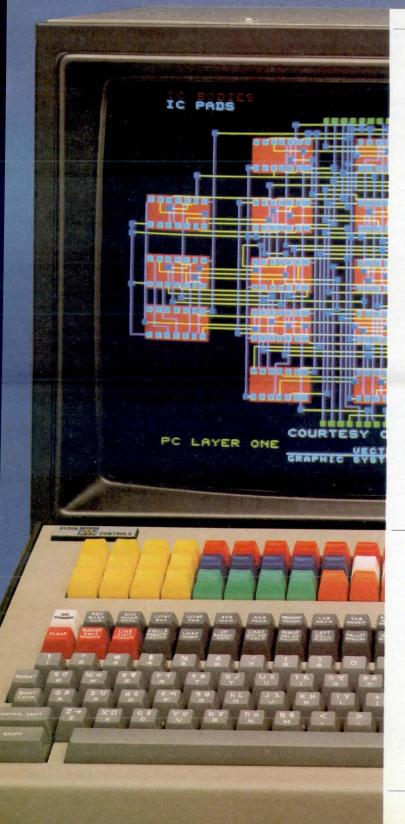

# EXORmacs. The one advanced system for Motorola's

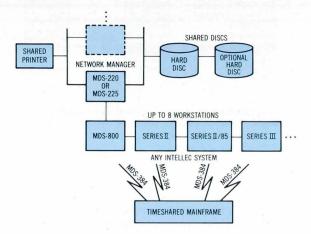

One versatile, comprehensive software and hardware development system is designed for maximum efficiency and productivity in support of the advanced 16-/32-bit M68000 Family of VLSI microprocessors and peripherals. Motorola's EXORmacs™.

EXORmacs is available in either a singleuser or multiuser system configuration for complete support of today's M68000 Family. VERSAbus™, Motorola's new-generation 32-bit address and data bus, is designed for equally thorough support of future M68000 Family variations and for 32-bit microprocessors to come. Growth for these future 32-bit systems is built in.

## Multiple use builds high productivity.

Maximum cost effectiveness is achieved in the multiuser system configuration. A single package, consisting of the EXORmacs chassis, up to 192 megabytes of mass storage in the hard disk subsystem, and a high-speed line printer, accommodates as many as eight users doing simultaneous hardware/software system development. Optional add-ons such as our new Real-Time Bus State Analyzer and Remote Development Station also promote increased productivity in system development tasks.

The result is highly efficient project management in one system. Multiple users are simultaneously updated with each software revision and get all the benefits of timesharing.

## Advanced Real-Time Operating System — VERSAdos $^{\text{TM}}$ .

EXORmacs uses a real-time multitasking, multiuser operating system called VERSAdos, in which a real-time executive provides essential task services and supports hardware memory management for memory allocation and protection. The input/output structure of the operating system supports device independence, logical as well as physical I/O, and overlapped I/O and computation.

The combination of bus arbitration logic and a sophisticated multilevel priority interrupt structure supports flexible multiprocessing capability.

## System bus meets high-performance requirements.

VERSAbus is Motorola's advanced computer bus designed to meet requirements of a new generation of microprocessor-based systems. It

supports a wide variety of 8-bit to 32-bit MPU architectures with high data transfer rates, and provides a flexible, economical architecture for serving industrial control, communications or general business applications.

And VERSAbus easily accommodates multipleuser terminals interfaced via the EXORmacs system's MC6801-based multichannel serial communications modules. All EXORmacs peripheral device controllers are based on Motorola's Intelligent Peripheral Controller (IPC) architecture. This relieves the main MC68000 processor of I/O processing details and increases the raw computer power available.

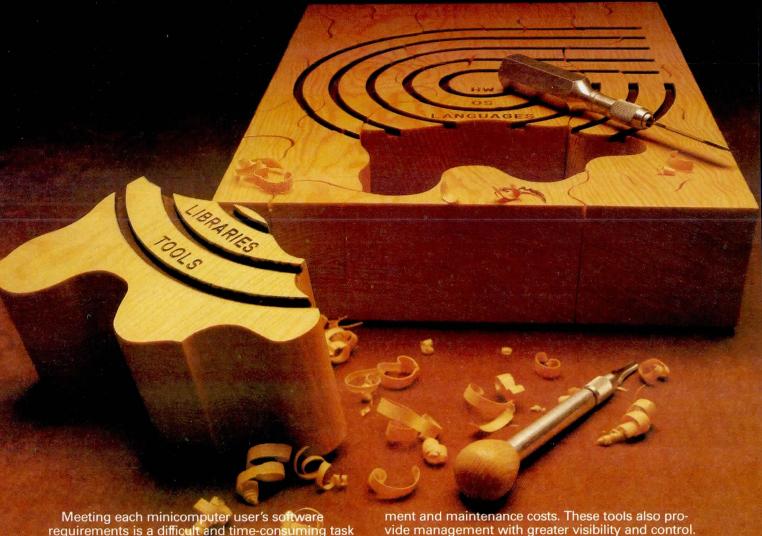

## High-efficiency software tools.

EXORmacs software is as advanced and practical as the hardware. The Pascal compiler is self documenting and promotes efficient programming technique, simplifying program maintenance. Motorola extensions of the

# multiuser development M68000 Family... and more.

user-oriented Pascal high-level language include string operations, runtime error checking, long/short integers, runtime file assignment and separate compilaton and linking. A structured macro-assembler, a CRT-oriented text editor and a linkage editor for combining modularly-written procedures also are included.

The M68000 User System Emulator (USE), enables the user to extend the EXORmacs development system resources into his target system. It supports system software debug in real time and provides convenient circuit isolation for fault detection.

System debug activities also are streamlined by the new optional Remote Development Station (RDS), a separate chassis with USE capability which is interconnected to the main EXORmacs chassis through a serial link. Hardware and software development activities can proceed independently at one or more RDS units without conflict with ongoing software development at other user terminals.

Possibly the greatest impact of the multiuser EXORmacs system is in the productivity of its software resources. Faster editing, compilation and assembly, the high throughput of the hard disk, the efficiency and power of the VERSAdos operating system — all help curb spiraling software costs.

## New EXORmacs software for M6800 family support.

A Macro assembler and linkage editor for the MC6809 are scheduled for mid-1981 availability, with similar development support for the MC6800, MC6801, and MC6805 to be offered by year end.

In short, multiuser EXORmacs is an all-round effective system which reduces equipment and space requirements, reduces the average cost per user and maximizes software productivity. EXORmacs also supports VERSAmodule<sup>™</sup> 16-bit board-level system design.

EXORmacs has one final advantage. No other development system can match it in supporting M68000 Family microprocessors and VLSI peripherals. Only EXORmacs is from Motorola. For additional information, write

to Motorola Semiconductor Products Inc., Microsystems, P.O. Box 20912, Phoenix, AZ 85036, use the coupon below or call (602) 244-5714.

The EXORmacs advanced development system is designed to make it easy for you to

apply MPUs from 8 bits to 32 bits in

## Innovative systems through silicon.

| Please send me II<br>88 CD 6/81<br>Name | nformation on EXORmacs™ |

|-----------------------------------------|-------------------------|

| Title                                   | Tel.: ()                |

| Company                                 |                         |

| Address                                 |                         |

| City                                    |                         |

| State                                   | ZIP                     |

## CONFERENCES

JULY 21-22—Sym on Reliability in Distributed Software and Database Systems, Pittsburgh, Pa. INFORMATION: Marie S. Hreha, LRDC Bldg, U of Pittsburgh, Pittsburgh, PA 15260. Tel: 412/624-4908

AUG 3-5—Pattern Recognition and Image Processing, Sheraton Hotel, Dallas, Tex. INFORMATION: PRIP, PO Box 639, Silver Spring, MD 20901. Tel: 301/589-3386

AUG 3-7—ACM (Assoc for Computing Machinery) Siggraph '81, Dallas, Tex. INFORMATION: Dr Anthony Lucido, Intercomp, 1201 Dairy Ashford, Houston, TX 77079. Tel: 713/497-8400

AUG 5-7—SYMSAC '81 (Assoc for Computing Machinery), Snowbird Ski Resort, Salt Lake City, Ut. INFORMATION: Prof B. F. Caviness, Dept of Mathematical Sciences, Rensselaer Polytechnic Inst, Troy, NY 12181. Tel: 518/270-6731

AUG 11-14—Electronics '81, Mexico City, Mexico. INFORMATION: Franc D. Manzolillo, Proj Mgr, Rm 6015, U.S. Department of Commerce, Washington, DC 20230. Tel: 202/377-2991

AUG 12-15—NYCE (New York Computer Expo), Sheraton Centre, New York, NY. INFORMATION: NYCE, 110 Charlotte PI, Englewood Cliffs, NJ 07632. Tel: 201/569-8542

AUG 18-21—VLSI (Very Large Scale Integration) '81 Internat'l Conf, University of Edinburgh, Edinburgh, Scotland. INFORMATION: Secretariat, VLSI '81 Internat'l Conf, 26 Albany St, Edinburgh EH1 3QH, Scotland

AUG 24-28—IFAC (Internat'I Federation for Automatic Control) World Congress, Kyoto, Japan. INFORMATION: IFAC '81 Secretariat, Kinki Hatsumei Ctr, 14 Kawahara-cho, Yoshida, Sakyo-ku, Kyoto 606, Japan

AUG 24-28—Internat'I Joint Conf on Artificial Intelligence, Vancouver, British Columbia, Canada. INFORMATION: Richard Rosenberg, Computer Science Dept, U of British Columbia, Vancouver, BC V6T 1W5, Canada. Tel: 604/228-3061

AUG 25-28—1981 Internat'I Conf on Parallel Processing, Shanty Creek Lodge, Bellaire, Mich. INFORMATION: Dr M. T. Liu, Dept of Computer and Information Science, Ohio State U, Columbus, OH 43210. Tel: 614/422-1837

AUG 26-29—Nat'l Small Computer Show, New York Coliseum, New York, NY. IN-FORMATION: Nat'l Small Computer Show, 110 Charlotte PI, Englewood Cliffs, NJ 07632. Tel: 201/569-8542 SEPT 8-9—Internat'l Conf on Computer Hardware Description Languages and Their Applications, Kaiserslautern University, Federal Republic of Germany. INFOR-MATION: Prof Melvin Breuer, Dept of Electrical Engineering, USC, Los Angeles, CA 90007. Tel: 213/743-2308

SEPT 14-17—Software Info '81 (The Nat'l Software Package Conf and Expo), Merchandise Mart Expocenter, Chicago, III. INFORMATION: Software Info, 1730 N Lynn St, Suite 400, Arlington, VA 22209. Tel: 703/521-6209

SEPT 14-18—COMPCON FALL '81, Capital Hilton Hotel, Washington, DC. IN-FORMATION: Harry Hayman, IEEE Computer Society, PO Box 639, Silver Spring, MD 20901. Tel: 301/589-3386

SEPT 15-17—WESCON '81, Brooks Hall and Civic Auditorium, San Francisco, Calif. INFORMATION: Dale Litherland, Electronic Conventions Inc, 999 N Sepulveda Blvd, El Segundo, CA 90245. Tel: 213/772-2965

OCT 19-23—JEMIMA (Japan Electric Measuring Instruments Manufacturers' Assoc) Internat'I Exhibition, Tokyo Internat'I Trade Ctr, Tokyo, Japan. INFORMATION: 19th JEMIMA Internat'I Exhibition, Secretariat of the Administration Committee, 1-9-10, Toranomon, Minato-ku, Tokyo 105, Japan. Tel: 03/502-0601, X4

NOV 5, 12, AND 17—Invitational Computer Conferences, Amsterdam, The Netherlands; Paris, France; AND Milan, Italy. INFORMATION: B. J. Johnson & Assocs, Inc, 2503 Eastbluff Dr, Suite 203, Newport Beach, CA 92660. Tel: 714/644-6037

NOV 9-13—IECI '81 (Internat'I Conf and Exhibit on Industrial Control and Instrumentation—Applications of Mini- and Microcomputers), Hyatt Regency Hotel, San Francisco, Calif. INFORMATION: J. D. Irwin, Electrical Engineering Dept, Auburn U, Auburn, AL 36830. Tel: 205/826-4330

## SEMINARS

SUMMER-FALL '81—Introductory, 8080/8085 and 8086/8088 Systems Design, Single-Chip Microcomputer, Peripheral Chip Design, and Development Systems Workshops, various locations. INFORMATION: Intel Training Ctr, San Francisco, Calif, tel: 408/734-8102; Chicago, III, tel: 312/981-7250; or Boston, Mass, tel: 617/256-1374

SPRING-SUMMER '81—Data Communications and Computer Graphics Series, various locations. INFORMATION: Karen Smolens, Ctr for Management Research, 850 Boylston St, Chestnut Hill, MA 02167. Tel: 617/738-5020

SEPT 7-8—Microprocessor Workshop on Microprocessor Applications, Liverpool University, Liverpool, England. INFORMATION: Dr M. J. Taylor, Microprocessor Workshop, Computer Laboratory, University of Liverpool, PO Box 147, Liverpool L69 3BX, England

#### SHORT COURSES

SUMMER '81—Inst in Computer Science, various locations. INFORMATION: Mrs Cynthia Johnson, Faculty Offices, Wang Inst of Graduate Studies, Tyng Rd, Tyngsboro, MA 01879. Tel: 617/649-9731, X355

JULY 20-22 AND JULY 23-24—Microcomputers in Control Systems AND Microcomputer Interfacing Methods, George Washington U, Washington, DC. INFORMATION: Dir, Continuing Engineering Education, George Washington U, Washington, DC 20052. Tel: 202/676-6106

AUG 10-14—Contemporary Data Communication Networks: Planning Analysis and Design, U of Michigan, Ann Arbor, Mich. INFORMATION: Dixon R. Doll, Continuing Engineering Education, 300 Chrysler Ctr, N Campus, Ann Arbor, MI 48109. Tel: 313/764-8490

Announcements intended for publication in this department of *Computer Design* must be received at least three months prior to the date of the event. To ensure proper timely coverage of major events, material should be received six months in advance.

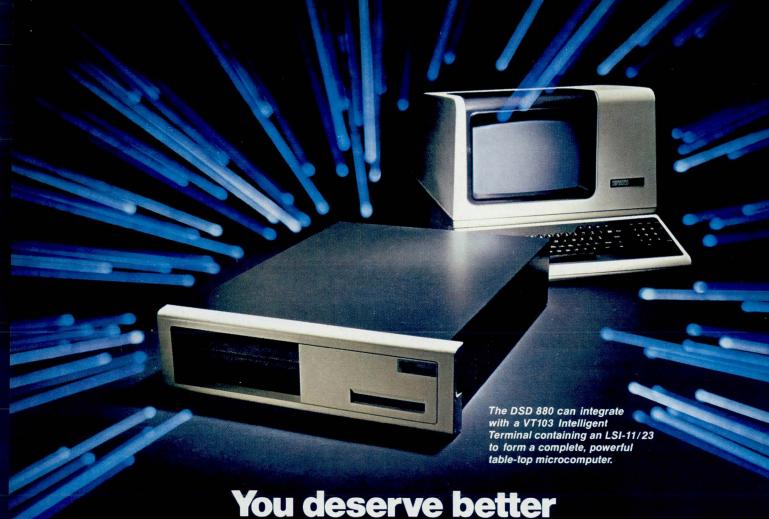

## You deserve better data storage than you get from DEC.

## For your LSI-11 or PDP®-11, bigger isn't better when it comes to data storage.

DEC® builds great computers. But if you want 7.8 megabytes of data storage, they give it to you in two ungainly boxes 21 inches high. Data Systems Design gives you one compact package 5¼ inches high, with an ultra-reliable 7.8 megabyte Winchester drive and a 0.5 megabyte single-sided floppy (or 1 megabyte double-sided) for I/O and integral backup, plus onboard diagnostics and lots of extras.

## A superb buy—the DSD 880 DEC-compatible Winchester/Floppy Disk System.

Offering far better value than RX02 and RL01 combos or dual-RL01 or -RL02 disk drives, the DSD 880 provides more bytes per buck than any DEC alternative. And you save in other ways.

Less rack space means lower cabinetry costs.

The 880 backplane interfaces require 70% less backplane space than a similar DEC configuration.

The comprehensive Hyper-Diagnostics \*\* panel and library of microprogrammed routines, in conjunction with Data Systems Design's Rapid Module Exchange \*\* program and HyperService \*\* service contracts, deliver more uptime for less than half the cost of a DEC service contract.

#### Fully compatible three ways.

DSD 880 is hardware compatible. It's the *only* high-capacity storage.

system that integrates with a VT103. And it integrates with any DEC LSI-11 or PDP-11 computer, or any DEC-computer-based system.

It's software compatible. You can use RT-11 or RSX-11 operating systems with RL01 (Winchester) and RX02 (floppy) handlers without modification. The DSD 880 runs all applicable DEC diagnostics and utilities.

And it's media compatible. Its floppies utilize DEC double-density or IBM single-density formats.

Want to know more? For full technical details, contact your regional sales office: Western (408) 727-3163; Eastern (617) 769-7620.

Data Systems

The Intelligent Alternative to DEC Disk Systems

International Sales: Australia: Melbourne [03] 543-2077. Sydney [02] 848-8533; Canada [416] 625-1907; Denmark 01/83 34 00; Finland 90/88 50 11; France 03/95681 42; Israel 03/298783; Italy 02/4047648; Japan: Osaka [06] 323-1707. Tokyo [03] 345-1411; Netherlands 020/45 87 55; New Zealand 4/693-008; Norway 02/78 9460; Sweden 08/38 03 70; Switzerland 01/730 48 48; United Kingdom 01/207-1717; West Germany and Austria [089] 1204-0.

\*\*HyperDiagnostics. HyperService and Rapid Module Exchange are trademarks of Data Systems Design. ® DEC and PDP are registered trademarks of Digital Equipment Corp.

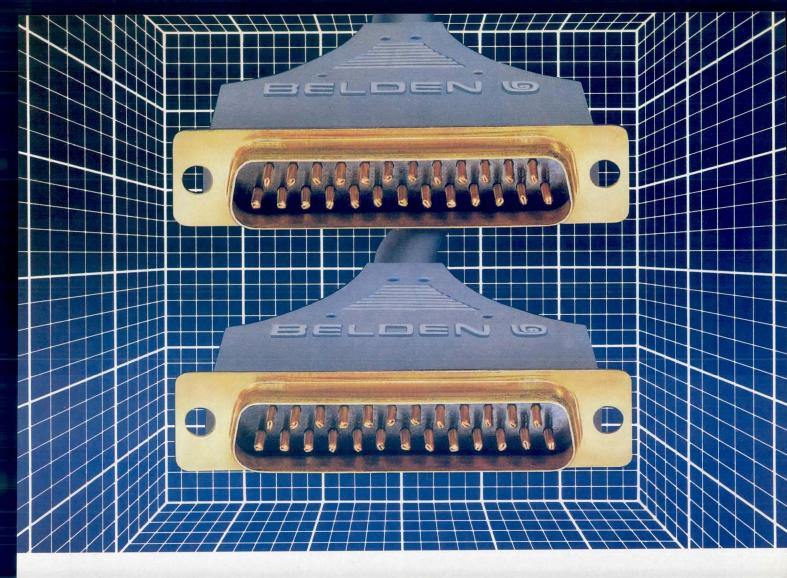

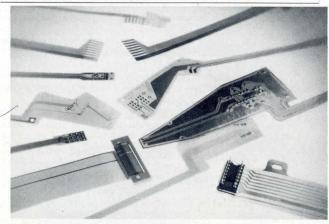

# Discover Belden's New World of Flat Cable

# ...at these Value-Added Flat Cable & Connector Distributors

California Switch & Signal 13717 South Normandie Gardena, CA 90249 (714) 522-8600 Control Master Products 1062 Sherry Circle Concord, CA 94518 (415) 939-3600

#### **Ratel Electronics**

1791 Reynolds Ave. Irvine, CA 92714 (714) 549-8611 (213) 637-0839

#### **Ratel Electronics**

2717 North First Street San Jose, CA 95134 (408) 946-4300

#### **Electronic Parts**

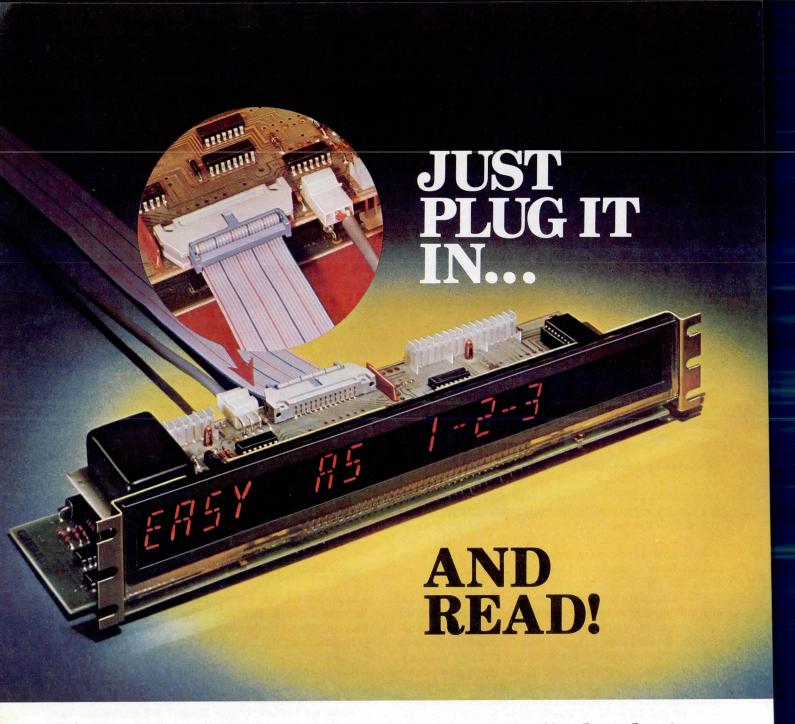

1212 South Broadway Denver, CO 80210 (303) 744-1992 You can search far and wide, but you won't find a better line of flat cable and connector systems than Belden. You won't find more responsive distributors, either.

Belden cable and connectors are designed for total compatibility—that's why we call them "systems." And that's also why you can count on them for fast, easy, dependable mass terminations.

Every cable, connector and assembly tool is built to Belden's exacting quality standards. It's the kind of quality that keeps your total costs down to earth.

And, of course, all these quality products are backed by Belden's value-added flat cable distributors. Whether filling an order or providing custom and value-added flat cable products, our distributors go the extra mile to serve you better.

Discover Belden's great New World of Flat Cable and Connector Systems. Belden Corporation, P.O. Box 1980, Richmond, IN 47374. Phone: (317) 983-5200.

KSM Electronics, Inc. 2207 Northwest 29th St. Ft. Lauderdale, FL 33311 (305) 739-5880

L-Comp 1115 W. National Ave. Addison, IL 60101 (312) 628-1400

QPL Electronic Dist. Inc. 47 Calvary Street Waltham, MA 02154 (617) 891-0460 Starks Electronic Supply 401 Royalston Ave. North Minneapolis, MN 55405 (612) 332-1325

Federated Purchaser 155 US Route 22 Springfield, NJ 07081 (201) 376-8900

Vertex Electronics, Inc. 150 Schmitt Boulevard Farmingdale, NY 11735 (516) 293-9880 Simcona Electronics 275 Mt. Read Blvd. Rochester, NY 14611 (716) 328-3230

Philadelphia Electronics 112 North 12th Street Philadelphia, PA 19107 (215) 568-7400

Sterling Electronics 11090 Stemmons Freeway Dallas, TX 75229 (214) 243-1600

© 1980 Belden Corporation

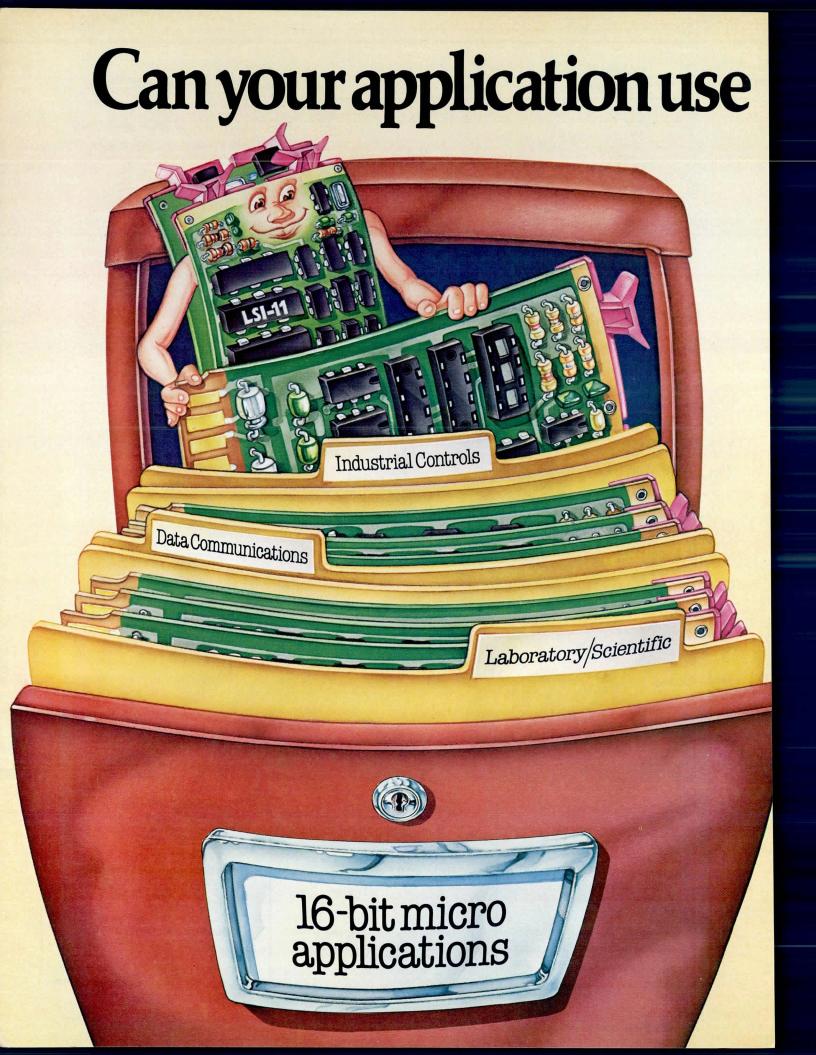

## a \$653\*16-bit micro?

If your system design is stretching the capabilities of 8-bit performance, take the step into 16-bit micros

without sacrificing cost efficiency.

And at the same time, get all the advantages of a more powerful and proven instruction set. Faster processing. Larger addressing capability. Expandability which allows your system to grow as your needs grow, without changing system architecture. And without appreciably changing your software requirements.

Chances are, you can use Digital's \$653 16-bit micro

in your application.

For full information, fill out the coupon or call toll free (800) 225-9220. In MA, HI, AK and Canada call (617) 467-7000. Or simply contact the Hamilton/Avnet or Harvey Electronics office near you.

\*In quantities of 50. Single unit price is \$990. Domestic U.S. prices only.

| □ Data C<br>□ Indust | ntory/Scient<br>Communicat<br>crial Controls     | ions<br>s (please spe | ecify)            |     |

|----------------------|--------------------------------------------------|-----------------------|-------------------|-----|

| □ Other              | (please spec                                     | cify)                 |                   |     |

| Name                 |                                                  |                       |                   |     |

| Title                |                                                  |                       |                   |     |

| Compan               | у                                                |                       |                   |     |

| Street               |                                                  |                       |                   |     |

| City                 |                                                  |                       |                   |     |

| State                | Zip                                              | Tel. (                | )                 |     |

| Microcor             | <b>quipment C</b><br>nputer Prod<br>n Way, Marlb | ucts Group            | , MR2-2/M6<br>752 | 65, |

We change the way the world thinks.

To the Editor:

The article "Making PL/M Programs More Understandable" (Computer Design, Nov 1980, pp 169-176) recommends replacing PL/M keywords with personal mnemonics. Allowing this practice means de-standardization. As stated on p 176, at the top of the last column, "it may come down to a matter of personal taste." It may come down, indeed, to everyone having his own PL/M dialect! Adopting dialects, instead of a standard language, decreases readability for experienced PL/M programmers and hence decreases maintainability of any software written in such a dialect. Replacement of keywords should therefore be forbidden, except perhaps for such widely used abbreviations as DCL for DECLARE and LIT for LITERALLY.

Replacing a call to a subroutine by another symbol, which is defined

WHEN YOU NEED

DEC...

TERMINALS

• VT-100 • VT-103

• LA34 • LA120

• LA180

PDP 11/03

PDP 11/23

SYSTEMS

LSI/11 MODULES

Demand...Delivery

Demand...Delivery

Demand...Discounts

Demand...UNITRONIX

(201) 231-9400

197 Meister Ave.

Somerville, NJ 08876

TELEX: 833184

in a LITERALLY declaration, may improve the readability for people not familiar with PL/M. But for experienced PL/M programmers, the improvement will be marginal. Keeping maintainability in mind, we will not recommend the burden such a practice will impose. Replacing commas in an argument list with pseudo-keywords looks very nice to nonprogrammers, but a goodsounding sentence can give the argument sequence a false appearance of correctness. Besides, what is the ultimate program text the compiler has to deal with? A comma too many? A comma too few? This practice may introduce errors difficult to detect, and for reasons of maintainability, we do not recommend it.

The only instance in which LITERALLY declarations should be used, and in our opinion must be used, is in the definition of constants, as in the following example:

DECLARE READ\$ACCESS LITERALLY '1'; DECLARE MAX\$REC\$NO LITERALLY '1234'; DECLARE LF LITERALLY 'OAH'/\* LINE FEED \*/;

Rienk S. Doetjes and Jan Duits SKF Engineering & Research Center B.V. Nieuwegein, Netherlands

### The Author Replies:

I do not advocate *replacing* PL/M keywords except in the case of substituting WORD for ADDRESS, which I consider to be poorly chosen. Besides, if the substitution of keywords is to be forbidden, why make an exception for abbreviations like DCL or LIT, which themselves may be contrary to the spirit of readability?

I propose simply to introduce *new* keywords that may make a program easier to understand. Clearly, if an experienced PL/M programmer is more comfortable with the basic syntax, that's his prerogative. In any given environment, the number of additional keywords should be relatively small so that the effort of

learning them is not too great. Of course, the new keywords must be properly documented, like any good software. Furthermore, portability requires that the keyword declaration files be transported along with the programs.

As for maintainability, I fail to see how making a program easier to understand can make it harder to maintain. The problem, of course, is to be sure that the program writer and maintainer agree on what is understandable. Nor can I get too upset over the notion of "de-standardization," since PL/M is not a standard and, to my knowledge, no one is working to make it one. Even within Intel there are syntactic differences between the 8080/85 and 8086 versions of PL/M.

Also, I would like to comment on John M. Pantone's letter in the February issue. The notion that a DO UNTIL block always executes at least once derives from Pascal syntax. In Pascal, one writes

REPEAT sequence of statements UNTIL condition.

and the statements execute before the condition is tested; therefore, they always execute at least once. In PL/M, one must write

DO UNTIL condition; sequence of statements; END;

Here the condition is tested before the statements execute and, therefore, they may not execute if the condition is true on entry. In other words, it is not the keyword UNTIL that guarantees that the block will be executed once, but rather the placement of the block relative to the condition test.

Douglas L. Abbott Zentrallabor für Electronik Jülich, Federal Republic of Germany

> Letters to the Editor should be addressed: Editor, Computer Design 11 Goldsmith St Littleton, MA 01460

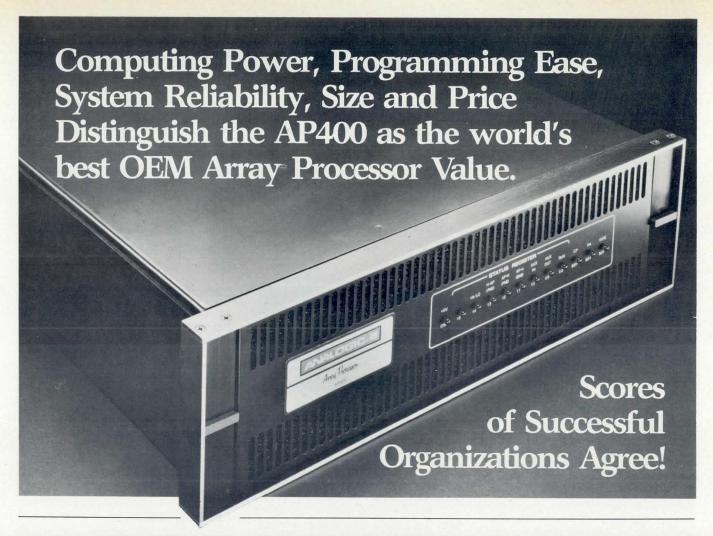

# CSPI Array Processors bring speed to scientific and engineering computation

CSPI's MAP FAMILY IS DESIGNED FOR SPEED. Our 32- and 64-bit floating point array processors enhance the computational speed of 16- and 32-bit minicomputers by 10 to 200 times. MAP gives FAST results through parallel processing which permits arithmetic operations to proceed at peak speed while I/O data is rushing through. MAP maintains 12 MFLOPS of arithmetic with up to 18 megabytes per second of concurrent I/O. Arithmetic and I/O proceed at peak rates while the host minicomputer stays free for other activity. MAP's unique multiprocessor architecture supports up to 8 of our standard analog and digital peripheral device interfaces. The results — real time processing for your most demanding requirements.

MAP SPEEDS YOUR RESULTS BY SIMPLIFYING YOUR JOB. An easy to use FORTRAN library of more

than 200 signal processing, math, I/O, and support functions is available. A cross-assembler and simulator support the development of special functions you may wish to add.

IN 500 INSTALLATIONS WORLDWIDE, MAP'S ARE DELIVERING FAST RESULTS. We price our array processors economically — as low as \$30,500 complete

— and ship them within 60 days ARO. Speed. It's the whole idea behind array processing.

Challenge us with your benchmarks. Call Ed Arsenault at (617) 272-6020.

CSPI

THE ARRAY PROCESSORS

40 Linnell Circle, Billerica, Massachusetts 01821 • 617/272-6020 • TWX: 710-347-0176

WORLDWIDE SALES OFFICES: Cedar Rapids, Chicago, Cleveland, Dallas, Dayton, Denver, Detroit, Ft. Pierce, Houston, Indianapolis, Kansas City, Milwaukee, Minneapolis, New York City, Philadelphia, Pittsburgh, Redondo Beach, Rochester, Scottsdale, St. Louis, Downsview, Montreal, Ottawa, Vancouver, Amsterdam, Frankfurt, Geneva, London, Madras, Milan, Paris, Stockholm, Sydney, Tel Aviv, Tokyo, Wellington.

## Intel's Series 90/iQX. The memory

Intel's new Series 90/iQX is the first standard Intelligent Memory System to offer continuous operation and high maintainability at low cost.

Now, for the first time, OEMs can design systems with built-in protection against errors, downtime, and excessive maintenance costs. How? With Intel's new Series 90/iQX.

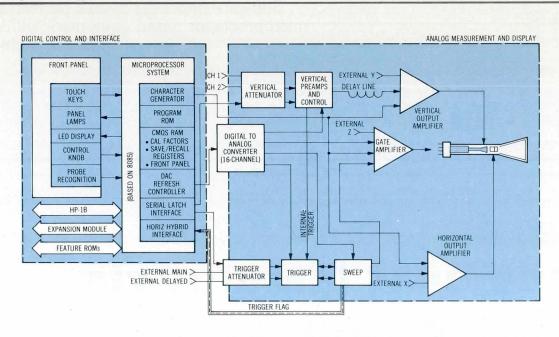

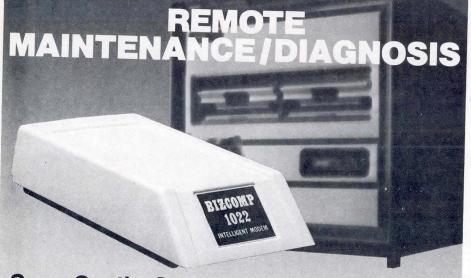

Series 90/iQX Intelligent Memory System

The iQX controller adds the intelligence of an iAPX 86 microcomputer

to the standard Series 90 Memory System. Intelligence that monitors memory operation directly, detects and corrects errors, runs local or remote diagnostics, and reallocates memory space as required. All without burdening the host system.

## Fault-tolerant operation

Hard errors or soft, Series 90's iQX controller uncovers them. Soft errors are simply "scrubbed" and corrected. In case of hard errors or device failure, the controller routes data around the problem, allocating spare memory as needed. It then logs the error for future reference.

With protection like this, the Series 90 system will continue operating uninterrupted until all spare memory is filled.

And thanks to the iQX's memory status reporting, your customer will know well in advance of memory resource problems. Which not only improves data integrity, but increases reliability and reduces maintenance dramatically.

## **Instant diagnostics**

To keep users continually apprised of conditions within their memory system, the iQX controller provides easy access to its complete diagnostic file. Information can be accessed by the host system either automatically via a simple message-driven software interface, or manually, using the iQX's Service Communicator. This detachable terminal allows technicians to instantly retrieve diagnostic data in plain English through a compact, alphanumeric keyboard/display. With no interruption of the host computer's operation.

For fast, simple maintenance, system diagnostics inform the user of any

## machine with non-stop intelligence.

errors it has tracked—soft or hard, correctable or avoidable—and their precise location by row and column.

Many problems can also be solved using the iQX's memory tasking capability to move data blocks as required. Then too, the iQX monitors the system's power supply and signals a warning if voltages drop critically. As a final, double protection, the iQX controller even diagnoses its own operation continuously.

## Diagnosing from a distance

To reduce maintenance costs for remote systems and networks, iQX diagnostics can be accessed over phone lines through a single diagnostic station. By being able to analyze problems from afar, you'll eliminate unnecessary service visits and shorten those that are required. And since one diagnostic station can easily serve up to 150 installations, the set-up and ongoing diagnostic costs are contained as well.

## Consider the economics

The iQX's protection features offer important economic advantages for systems OEMs. Because of the increased demand for fault tolerance in today's marketplace, systems equipped with iQX capability add significant value to your products. In fact, many applications simply could not be justified economically without such self-healing and remote maintenance. Now, through Intel's leadership in 16-bit microprocessing, the Series 90/iQX brings you this capability at an incremental price only nominally above that of ECC alone.

In sum, iQX gives your systems state-of-the art fault protection, reduced maintenance costs, and therefore increased value. Best of all, Intel is delivering Series 90 systems with iQX right now. For detailed information, return the coupon to Intel Corporation, 3065 Bowers Avenue, Santa Clara, CA 95051. Telephone (408) 987-8080. For hot line service, call (800) 538-1876.

| My needs are immediate; have a Sales Engineer call.                                                     |      |

|---------------------------------------------------------------------------------------------------------|------|

| Please rush me – by first-class mai<br>Series 90/iQX technical literature.                              | il — |

| Name                                                                                                    |      |

| Title                                                                                                   |      |

| Organization                                                                                            |      |

| Address                                                                                                 |      |

| City/State/Zip                                                                                          |      |

| Telephone ( )                                                                                           |      |

| Mail to:                                                                                                | CD6  |

| Intel Corporation                                                                                       |      |

| 3065 Bowers Avenue<br>Santa Clara, CA 95051<br>(408) 987-8080                                           |      |

| Europe: Intel International, Brussels, Belgium.<br>Japan: Intel Japan, Tokyo. United States and Canadia | n    |

| L Idelivers                                                                                             |      |

| inta delivers solution                                                                                  | 0    |

| Solution                                                                                                | 13   |

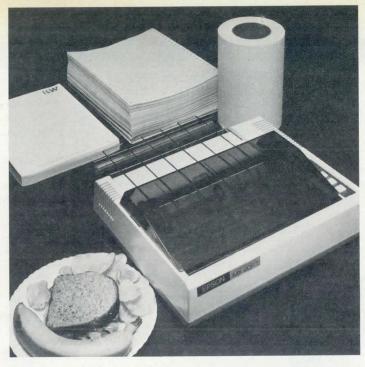

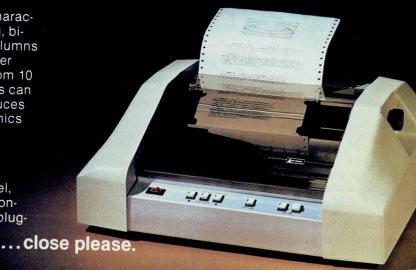

# New Spinwriter 3500 Series.

## Birth of a new concept in letter-quality output.

NEC's new Spinwriter™ 3500 series is the first comprehensive printing system in the letter-quality office printer/terminal market. The Spinwriter 3500 series includes eight new models.

Starting with a new medium-speed 35 CPS print mechanism, the Spinwriter 3500 printer family adds five pioneering dimensions to letter-quality printers.

One: simple, elegant design. Each new Spinwriter 3500 is 30% smaller and lighter, uses 60% fewer parts, single-board electronics, a one-piece universal power supply and digital controls that replace many mechanical functions. It's the size of an office typewriter.

Two: integral forms handlers. Ten of them, designed with the mechanism. All are user changeable. Some are user up-

gradeable: like a single-bin sheet feeder that can add a second bin or envelope feeder. There's also a cut-sheet guide, bi-directional tractor, push tractor with tear bar and copy separator, manual inserter and bottom feed.

Three: new uptime standards. The Spinwriter 3500 has a 3,000-hour

MTBF, which means about two years between failures.

And no preventive maintenance or routine lubrication. Ever.

With only three major spares, MTTR is reduced to 15 minutes!

Four: word processing assist. Lets the terminal perform WP systems tasks like automatic bi-directional printing, auto PS printing, auto underlining, shadowing and bold printing. Using all the Spinwriter type styles of up to 128-character thimble print elements.

Five: immediate attachability. The Spinwriter 3500 comes in eight printer or terminal models with Qume, Diablo, Centronics, RS-232C interfaces, and is functionally compatible with Spinwriter 7700 and 5500 Series.

Find out more about the light, quiet, compact, reliable Spinwriter 3500 series. Superior in every way.

## NEC Information Systems, Inc.

Home Office: 5 Militia Drive, Lexington, MA 02173, (617) 862-3120 Eastern Office: 36 Washington Street, Wellesley, MA 02181, (617) 431-1140 Central Office: 551G Tollgate Road, Elgin, IL 60120, (312) 931-1850 West Coast Office: 8939 S. Sepulveda Blvd., Los Angeles, CA 90045, (213) 670-7346

NEC. Going after the perfect printer.

## Contemporary Multiplexing Techniques—Part 2: Statistical Multiplexers, Criteria and Constraints

James F. Kearney

Timeplex, Incorporated

One Communications Plaza, Rochelle Park, NJ 07662

The first part of this series dealt with multiplexer theory and design concepts and discussed basic types of multiplexers and how they differ. In this concluding part, a number of network design problems is shown in the context of some typical, real world network situations.

Equipment in remote locations often differs from that at the host site—eg, an IBM host and a Data 100 or other look-alike in the field. The vendor of the look-alike equipment will have an emulation program, and these programs handle data somewhat differently. Therefore it is important to know the particulars of an emulation program before putting a statistical multiplexer into the system.

#### **Protocol Problems**

If, for example, an IBM host sends traffic to an emulated IBM 3780 terminal, embedded sync characters could cause a problem. Under the IBM system these characters are normally stripped out, but with many emulated systems this is not the case. Such embedded characters can lengthen a data block considerably. Since emulated terminals usually have limited buffer space, at times the user runs the risk of overflowing the end buffer. In most look-alikes, there is a version of the emulation package that does strip away the embedded sync characters.

It is also necessary to examine operation on the host side of the system. When first configured, many systems grew out of a local environment, where a very high speed line came from a local cluster controller or terminal directly into the high speed bus of the mainframe. Poor file structure or system partitioning may not have caused any apparent deficiencies because of the high speed data transfer between local cluster con-

troller and mainframe. However, these inefficiencies become quite evident when a communications facility is involved, especially if the number of associated lines increases to the point at which a statistical multiplexer (stat mux) is used.

For example, consider eight 2400-bit/s 3270 terminals in a local environment involving one or two local cluster controllers. The eight lines are connected to eight channels of a stat mux. Long delays can result if provision has not been made for balancing out the partitions so that online software gets a high priority, and if the associated files have not been structured to accommodate the number of tasks being performed by the system.

### **Buffering**

Buffering concepts have changed over the past few years. Until recently, multiplexers employed static random access memory (RAM) that allocated a specific amount of buffering to each channel. When this amount was exceeded, traffic control was activated to stop the channel, provided the multiplexer had this control; if it didn't, data were lost. To insure against the loss of data, larger amounts of buffer were assigned to each channel. In the same way that time division multiplexer (TDM techniques waste bandwidth, this arrangement wasted buffer; the large storage capacities were not often needed.

Dynamic buffering was the next step. This assigns common buffer in each module to whichever of the channels associated with the module needs it. However, under the error condition known as "streaming," when a steady stream of erroneous characters is induced into the line with no pauses such as are encountered with live transmission, the stream quickly fills the buffer for the whole module. This can trigger traffic control prematurely and knock out all channels associated with the module.

The most recent variation provides an override to dynamic buffering. This assigns a buffer access priority to each channel within the module. The modular construction limits the ability of one channel in a streaming mode to interrupt other channels. The priority system further limits this effect only to the channel causing it. The rule of thumb generally used in assigning priorities is to give lowest priority, with access to 256 bytes of buffer space, to the low speed asynchronous channels operating on character by character or very small block mode; next giving access to one-fourth of the buffer pool to the 2400bit/s interactive terminals that may have blocks of 400 to 1000 characters; and top priority, with access to all buffers in the pool, to remote job entry (RJE) terminals having a larger number of blocks to be transmitted.

(continued on page 26)

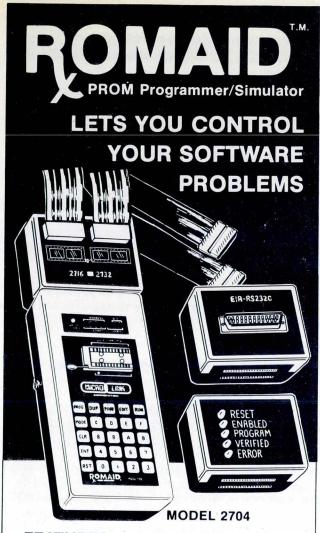

#### **FEATURES:**

- in circuit simulation of popular 2758. 2716, 2732 and 2764 PROMS

- programs popular 5 volt PROMS

- RS422 / RS232 / 20mA, data loading capability

- simulates up to four 2716's, two 2732's or one 2764 PROM's simultaneously

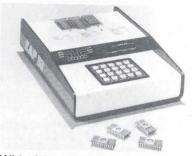

Ease of operation and program manipulation, portability and versatility will make the ROMAID PROM Programmer/Simulator the answer to your software debugging problems.

The ROMAID PROM Programmer/Simulator lets you put downtime at a minimum when software problems arise. It features in-circuit emulations of the most popular 1K, 2K, 4K and 8K X 8 PROM's and has full 8 digit hexidecimal display for address and data information.

And we're saving the best till last... Price! ROMAID costs less than other PROM Programmer/Simulators on the market today. Let us tell you more about how this revolutionary software "debugger" can save you time and money.

Write today to:

Micro Link Corporation 624 S. Range Line Road Carmel, Indiana 46032 Phone (317) 846-1721

## COMM CHANNEL

These are recommended guidelines, not requirements. The point to remember is that there will be problems in a communications network. The fundamental question facing the network designer is how to minimize the exposure generated by a particular problem. Buffer allocation should be regarded as a way of preventing one user from tying up an entire system.

### Clocking

Some front ends and terminals require a clocking function. Synchronous systems require clocking; therefore, multiplexers used in such systems will have a capability to supply or receive clocking. Clocking has not been a factor in asynchronous systems until recently. However, the higher speed terminals that are emerging for asynchronous systems depend on clocking. In a normal IBM environment, for example, with any asynchronous port of more than 1200 bits/s, the front end must receive clock. This requirement is often ignored when systems are being upgraded. A system that cannot supply clocking is mistakenly acquired, and without a clock the front end and/or terminal will not operate.

On some stat muxes clocks can be changed on a channel basis. On others they can only be changed on a module basis, which means not only that each clock setting must apply to all terminals connected on the module, but that there will be a limitation in the way that channels can be associated within an individual module. This could present a problem when trying to assign channels to modules on a traffic basis.

Flexibility in clocking might also be needed on a nodal basis. If the clocks are set for internal timing on the multiplexer at the host end, which means that a clock is being generated there for the front end, must clock also be generated to the remote hardware? There may be cases in which this is not desirable, when an external clock is called for. For example, clock may or may not be wanted from a tail circuit modem.

These are all examples of how the current generation of stat muxes is closing a large gap that has troubled those trying to put together a communications network. The stat mux can make it possible to combine within the same network dissimilar equipment that could not previously have been interconnected. The user can now tie a terminal that does not use clocking at all to an IBM front end at 4800 bits/s. supplying clock to the front end through the multiplexer that is inputting data from a variety of pieces of equipment.

## **Data Speeds**

Usually programmed on a per channel basis, data speeds are not varied in a synchronous environment. However, auto speed or adaptive speed may be required in an asynchronous environment. With this

(continued on page 28)

## FROM STATISTICAL MULTIPLEXORS COMPLETE DATACOMM NETWORKS,

DCA protects your initial investment in statistical multiplexors with the lowest-cost network growth in the industry. So you can start with a small datacomm net-

work today, and expand or modify it to meet your needs tomorrow.

Our System 115 statistical multiplexor can be used in point-topoint networks to support from 2 to 32 asynchronous terminals at a HOST CPU DCA point-to-point networks support from 2 to 32 ports. Our System 105 supports from 2 to 8 ports.

remote site. DCA's statistical multiplexing assures excellent response time, character transparency and error-free transmission.

DCA's multipoint multiplexing configuration serves a number of remote terminal locations with just a single telephone line, for substantial savings in phone-line and hardware costs. DCA users

have benefited from multipoint multiplexing since January 1979.

DCA's System 205 is a statistical multiplexor designed for DEC UNIBUS\*-based computers. The 205 requires only one UNIBUS slot to emulate up to 16 DEC

DZ11 modules and a 128-port stat mux. This greatly lowers hardware costs and improves response time as well.

DEC HOST 205 DCA's multipoint multiplexing permits several

Because of DCA's unique modular design, all of the above networks could easily expand into larger, more powerful networks. As the master HOST CPU network processor, System 355 gives terminal users access to any dca host computer anywhere in the network. In addition, the 355 sup-Complete system compatibility allows DCA ports up to 126 ports, 62 networks to grow without growing obsolete. of which can be highspeed synchronous trunk links. Several 355's can 205 be combined to greatly expand this support. Fea-

tion, switching, unlimited routing, X.25 support and a wide array of network management tools.

Total system access and unlimited network growth at very low cost — that's the DCA advantage. For complete information, call or write for our 16-page brochure.

\*TM Digital Equipment Corporation

HOST CPU

tures include port conten-

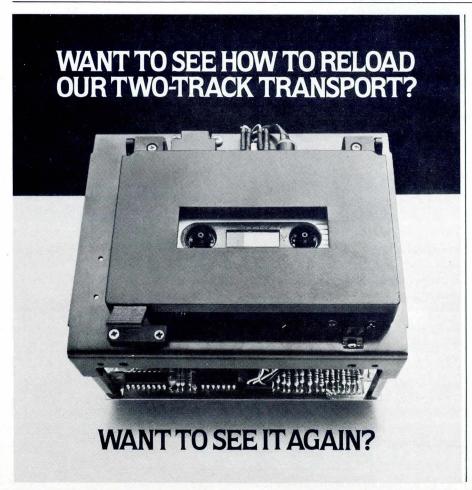

# IDT Provides The Right Tape System

IDT subsystems give you many important advantages, including:

**Wide Selection** — Choose from nine IDT 1050 models with 7 or 9-track ½-inch tape reels, plus twelve IDT 3000 models with ¼-inch tape cartridges

**Superior Design** — Get sophistication plus reliability, ensured by self-test firmware . . . MTBF specifications of 8000 hours

**Numerous Options** — Select built-in formatter/controller for data formatting (ANSI, ECMA, IBM-compatible), plug-in interfacing, and control of four tape subsystems

**Dedicated Configurations** — Satisfy OEM, minimicro or one-of-a-kind requirements

## COMM CHANNEL

option the channel speed is shifted from 150 to 1200 bits/s. The remote multiplexer initiates the changes when it samples the first incoming character (usually a carriage return) and detects the speed to which to shift the channel. Once that shift is made, a character or status word is signaled to the remote unit to indicate that a change should be made. The word is also passed on to the host unit, telling it that it is getting 1200 bits/s rather than 150 bits/s. An optional adaptive speed attachment available on some multiplexers uses the large buffer capacity at the remote end to hold data so that the host can remain in a constant speed mode. In this way much of the firmware that would be associated with the mainframe is avoided. In cases of crisis in large systems with different types of front ends that recognize different characters, when one mainframe is down, a shift over to another system, with no exposures, is facilitated. The multiplexer is compensating for the speed changes in the system. All ports on the mainframe can be set for 1200 bits/s; the multiplexer on the remote end, making the necessary compensations, will be able to accept from 150 to 1200 bits/s.

#### **Traffic Control**

When a channel buffer is filled, traffic control automatically stops a sender in order to avoid losing data. It is generally available on stat muxes. (See the Table, "Traffic Control Options.") The user should be sure that the traffic control allows him to retain the flexibility in network configuration that he needs. Many traffic control arrangements are programmed per module rather than per channel. Where this is the case, if the user wants to program a clear to send (CTS) function to go low when traffic control is enabled, it is necessary to program all of the channels in the module, both local and remote, in the same way. When the multiplexer can be programmed independently for each channel end, the user has a means of establishing a functional communications link, where before it was impossible.

## Number of Channels on the Line

In an asynchronous environment, limitations on the kinds of channels and traffic volumes that can be associated in a single stat mux are seldom a problem. Problems begin when bisynchronous data are introduced. Because of the polling overhead and the constant reference to each channel of some sort of data, whether live or polled, the processors are kept busy. Thus, more 4800-bit/s asynchronous channels than 4800-bit/s synchronous channels can be run on the same line.

The problem is not encountered in the medium speed ranges, but appears when the user tries to run 7200 and 9600 bits/s over one 9600-bit/s line.

(continued on page 30)

## HIGH QUALITY

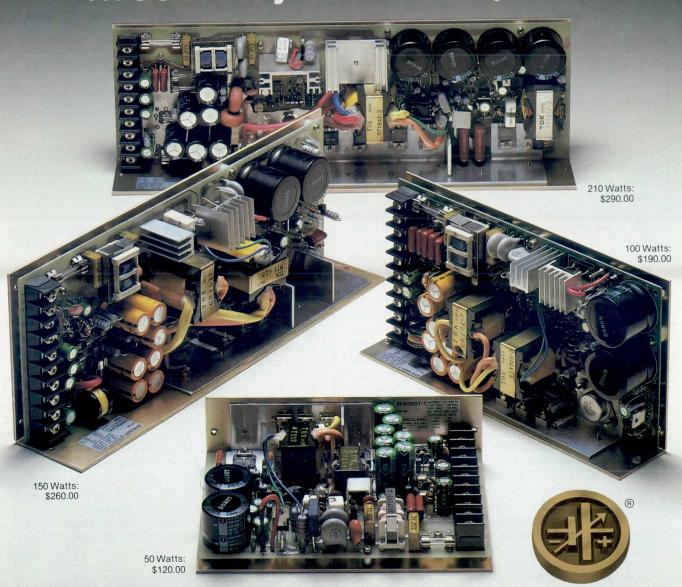

## open frame SWITCHING POWER SUPPLIES

... at a very attractive price

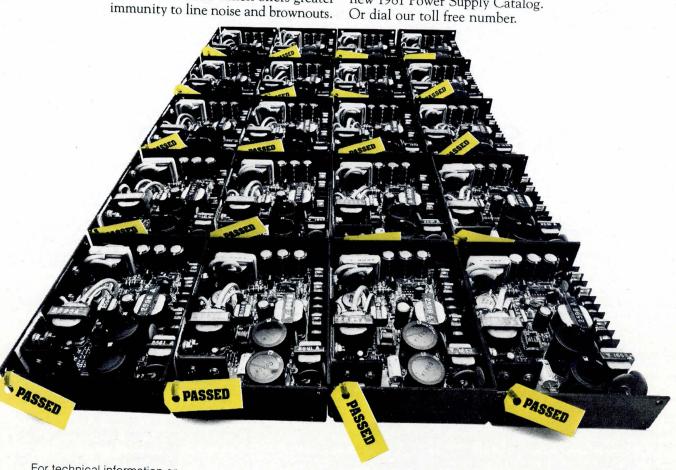

Single board, multiple-output, open frame switch-mode power supplies offer you high efficiency, well regulated power at a very attractive price.

The listed prices are for single unit quantities. Please contact us for quantity pricing and a demonstration.

For complete specifications, write Dept. DBF-79

#### TRAFFIC CONTROL OPTIONS

## Stat Mux Controls External Equipment

| Туре   | Character/Function     | Operation                             |

|--------|------------------------|---------------------------------------|

| Inband | X-OFF/X-ON             | Transmits X-ON/X-OFF sequence         |

| Inband | Programmable           | Transmits user selected sequence      |

| EIA    | Clear to send          | Transmits high or low CTS level       |

| EIA    | F3 (connector pin 22)* | Transmits high or low level on pin 22 |

#### **External Equipment Controls Stat Mux**

| Туре   | Character/Function     | Operation                               |

|--------|------------------------|-----------------------------------------|

| Inband | X-OFF/X-ON             | Responds to X-OFF/X-ON sequence         |

| Inband | Programmable           | Responds to user selected sequence      |

| EIA    | Clear to send          | Responds to high or low CTS level       |

| EIA    | F3 (connector pin 25)* | Responds to high or low level on pin 25 |

<sup>\*</sup>Control function on F3, pin 22 or 25 of EIA RS-232-C connector; polarity of start/stop signals is user selectable

Trouble starts with the sampling of data, and even if all the data do get in, the volume will continue to upset matters because of the limitations of the high speed line itself. Even with two high speed links, only about 2400 chars/s can be sent. If an RJE terminal that is transmitting a 1000-character block and has a number of interactive terminals associated with it that possibly present 3000 to 4000 characters at any given time, the system will go into a queuing cycle. The result is that users are waiting.

In that situation the timeout factors associated with the host system must be very high. The multiplexing environment adds overhead to the system and in any case expands the timeout parameters within the mainframe. When too much data are introduced in addition to all this, chances of timeouts are greatly increased. This condition is cumulative. The mainframe sends out a block of data and gets neither acknowledgment (ACK) or negative acknowledgment (NAK). This causes the mainframe to go into a timeout and it will continue to try to retransmit the data. If this continues, the terminal will be, in many cases, knocked offline and the mainframe will assume that the terminal no longer exists. When it comes up, the system will no longer recognize it.

It must be remembered that a stat mux is a means to collect and continuously multiplex data over a high speed link, usually a 9600-bit/s line. It is not a large concentrator that collects, assembles, and transmits data over wideband lines. A concentrator is primarily used to collect very large blocks of data and send them over a number of 9600-bit/s lines or over a 56k-bit/s link. Concentrators have the memory capacity to accomplish this and, in some cases, will also do local ACKs and NAKs. However, they are more expensive—in the order of \$70,000 instead of

the \$2500 or so for a stat mux. On the other hand, the stat mux is designed primarily for interactive application.

## **Network Configuration**

Distributing channels to modules on the basis of utilization is the key to configuring networks. If the type of data that are coming over a particular channel is known, it should be assigned to modules according to their efficiencies; that is, what other channels it will be associated with. The effect is to make sure that one module and its channels are not tied up with scanning, buffering, and handling large amounts of data while others are sitting comparatively idle.

In earlier systems where one master controller (the CPU) governed the scan going out to particular channels, it was common practice to give the highest speed channel to channel one, where the scan starts, and the others to two, three, four, and so on in the order of decreasing traffic. With more recent modular concepts, there is one scanner for each module and each has its own associated buffer. Traffic analysis enables particular channels to be associated with given modules and ensure, for example, that all of the RJE terminals are not on one channel module while all of the interactives are on another.

## Response Time

Concerns about response times are often based on a combination of poor understanding of what the user's own needs are and a lack of understanding of the real world. Even on a one-to-one connection the overhead in a stat muxing environment will introduce delays, although these will probably not be (continued on page 36)

# POWER TO YOUR COMPUTER

Continental Power Systems presents a unique new design in uninterruptible power sources for all mini, small business and small/medium computers.

The PoweRotor™ UPS System keeps your computer on-line through common power problems such as momentary interruptions, erratic voltages and transient spikes. Yet the PoweRotor generator maintains absolutely constant output frequency essential to computer operation. During a utility

outage, the system provides 10 to 30 seconds ride-through for orderly downsequencing or switching to back-up power.

- Installation is easy, with only small footprint area required.

- Lower installed cost than static inverter/battery systems.

- Superior ride-through over motor generator sets.

- Only UPS with 3 year warranty.

Get the complete story

on the better UPS from Continental Power Systems, Inc., One Landmark Square, Stamford, CT 06901. 800-243-9145.

## Continental Power Systems, Inc.

A member of The Continental Group, Inc.

An international packaging, forest products, insurance and energy company.

CIRCLE 31 ON INQUIRY CARD

# SHUGART A REVOLUT

Choice.

If you've been looking at disk drives for desktop systems, you may have thought you had only one choice: take it or leave it.

Not any more. Now you can get everything you need from a single source. And get the added convenience of doing business with one company.

Say you want a reliable, entry-level drive, but cost is critical. The ideal choice? Our SA400, the original Minifloppy.™

Or maybe you need more capacity, but you don't want to give up low cost. Try our double-sided Minifloppy, the SA450.

Then too, you may want to move up to even higher speeds and capacities — up to a megabyte — in a Minifloppy-size package. For that, choose our 96-TPI SA410 single-sided or SA460 double-sided drives.

But what if your desktop system demands the high performance and reliability of a

# INTRODUCES IONARY IDEA.

top market, that's a revolution-Winchester? Then specify our new 5.25-inch fixed disk drive, ary idea. To find out more about your the SA600. It's got ten times desktop alternatives, contact the throughput of a floppy, and Shugart Associates, 475 Oakcapacities from 3.33 to 10 megamead Parkway, Sunnyvale, bytes. And by teaming it with CA 94086. Telephone a Minifloppy, you get dupli-(408) 733-0100. Or cate file backup too. Hamilton/Avnet, Now that's choice. Which authorized dismeans you get just the right tributor. combination of cost and Shugart capacity for your application. And in the desk-Right from the very start. Sales and Service: Sunnyvale CA, Costa Mesa CA, Minneapolis MN, Richardson TX, Framingham MA, Landing

NJ, Atlanta GA, Toronto Ontario, Paris France, Munich Germany.

CIRCLE 22 ON INQUIRY CARD

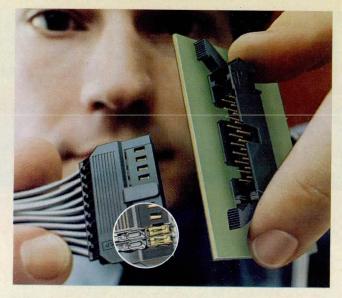

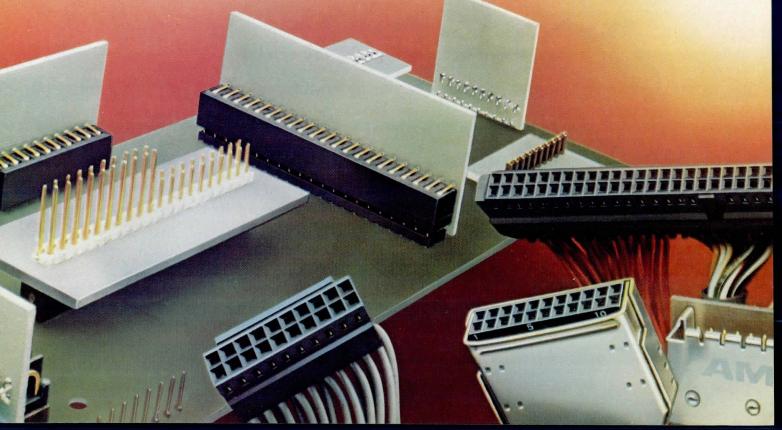

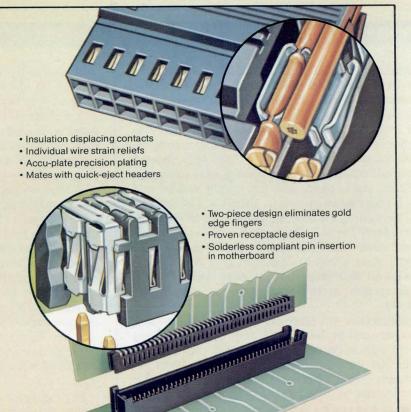

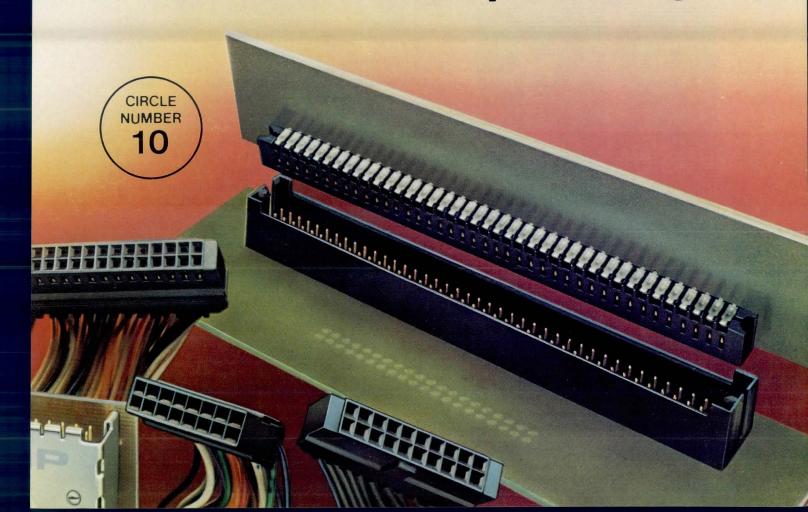

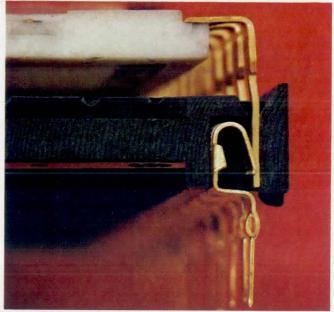

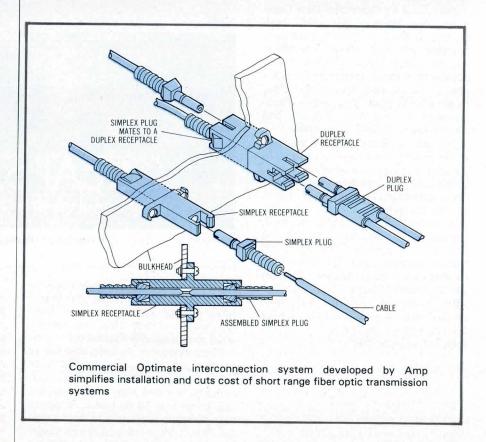

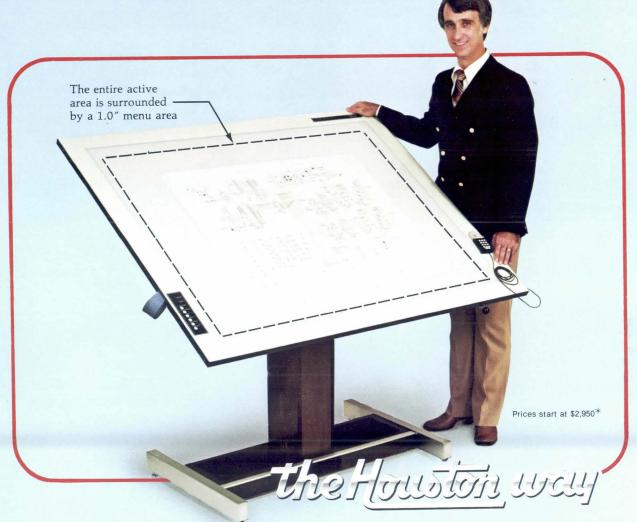

# Mass termination comes to the world's most popular interconnection system.

Now you can have the money-saving benefits of mass termination with the design advantages of our universal board-to-board, wire-to-board and wire-to-wire AMPMODU interconnection system.

The AMPMODU MT connector.