A PennWell Publication

FEBRUARY 1984

# PUTER DESIGN

SPECIAL REPORT:

DATA COMMUNICATIONS

**NEW!** from out of the West...

# DEC COMPATIBLE CONTROLLERS

The Wespergroup Dimension series expands twofold in three dimensions. Wespergroup introduces six exciting new additions to the tape and disk dimension series:

THE TAPE DIMENSION Q-BUS COUPLERS TDQ-I AND TDQ-II. These couplers easily support the new tri-density "formatted tape drives" both in Start/Stop or Streaming modes. The TDQ-I supports Pertec interface tape drives, while the TDQ-II supports high speed Pertec, STC and Telex interface tape drives using a 64k byte data buffer. Both couplers emulate the DEC TSVO5.

THE DISK DIMENSION DEC UNIBUS CONTROLLERS DD-I AND DD-II. These controllers sustain up to four industry standard SMD interface disk drives. The DD-II handles up to two megabyte/second data transfer rate of the new SMD interface disk drives. The DD-I and DD-II

emulate DEC RM02/03, RM05, and RP06 disk drives.

THE TAPE DIMENSION DEC UNIBUS COUPLERS TD-III AND TD-IV. These couplers support the new "formatted tape drives" with either STC, Telex or Pertec interfaces in Start/Stop or Streaming modes. The TD-IV includes a 64k byte multi-stage data buffer to upgrade the efficiency of the Streaming Drive in the write mode. Both couplers emulate the DEC TS II drives.

Call or write today for the complete Wespergroup catalog. WESPERGROUP, Div. of WESPERCORP (USA), 14321 New Myford Road, Tustin, CA 92680, Tel: (714) 730-6250, Cable WESPER, TWX 910-595-1775, Telex 4720629. (Germany) GmbH, Tel: 089 982420. (U.K.) Tel: (44) 0276-20934.

DEC, Unibus and Q-Bus are registered trademarks of Digital Equipment Corporation.

WESTERN PERIPHERALS WESPER INTERNATIONAL

WESPERGROUP

Division of WESPERCORP

CIRCLE 1

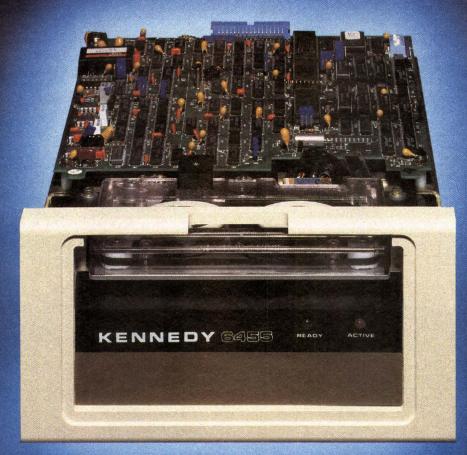

DATASYSTEMS WESPERLINE Model 6455 Cartridge Tape System

# Loaded with Features — Loaded with Benefits.

Kennedy products have always provided innovative new features. And these features have always provided added benefits and convenience for the user. For instance, our Model 6455 offers these features and benefits:

Feature: Start/Stop Operation

Benefit: Drive can emulate a ½" tape drive by providing the ability to perform selective file back-ups,

file-restructuring, journaling and software

updates.

The drive is effectively a 1/2" Tape Drive in a

smaller package.

Feature: Hard Read Error Spec. of 1 in 10" bits.

Benefit: Best data reliability of any tape cartridge drive.

Gives the user confidence in the integrity of the

back-up medium.

Feature: On-board Diagnostics

Benefit: Drive can be tested off-line with no test

equipment required. Use of S.A. also lowers the

MTTR.

Feature: Cartridge Jam Protection

Benefit: Protects the cartridge from damage if cartridge

jams. This is accomplished by sensing a current surge and then disabling the motor, thus

insuring that the cartridge will not be damaged.

Feature: High Density Recording

Benefit: Storage capacity of 23 MB on a single cartridge.

Feature: Optional industry standard 1/2" tape interface.

Benefit: Operates with existing tape couplers and software.

The drive operates as though it were a  $\frac{1}{2}$ " tape drive without having to modify existing

hardware or software.

By now you can see what we're driving at. Model 6455 is full of unique features and benefits for you. For the complete story, write or call us today.

# KENNEDY

An Allegheny International Company

1600 Shamrock Ave., Monrovia, CA 91016 (818) 357-8831 • ITT TELEX 472-0116 KENNEDY TWX 310-472-0116 KENNEDY

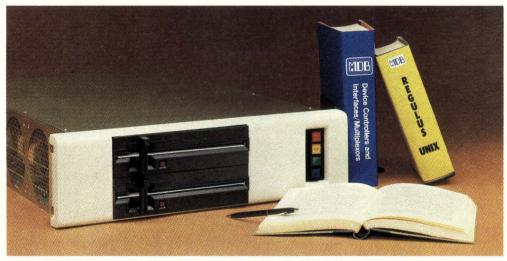

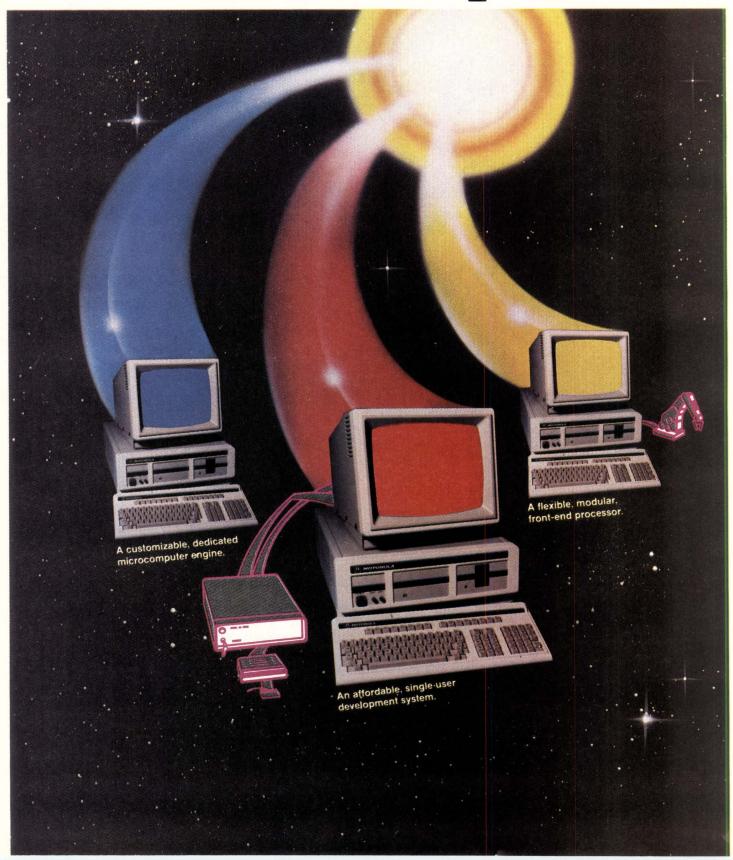

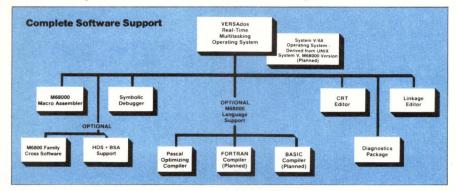

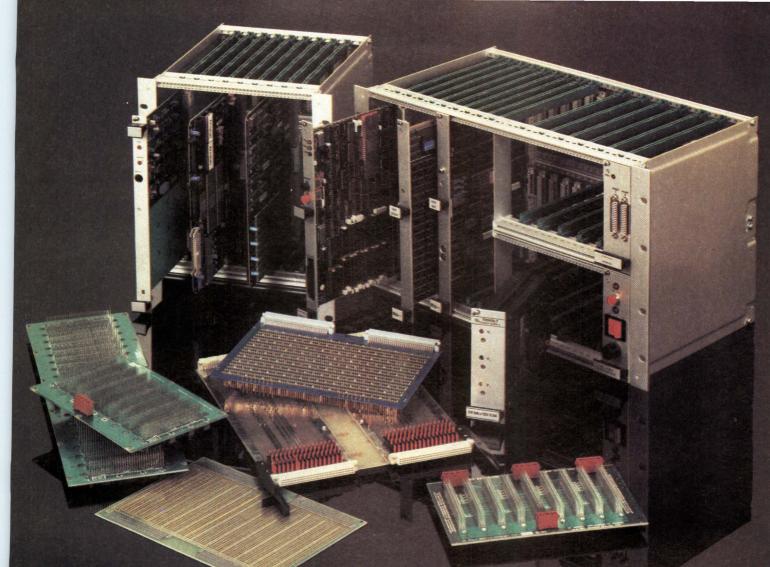

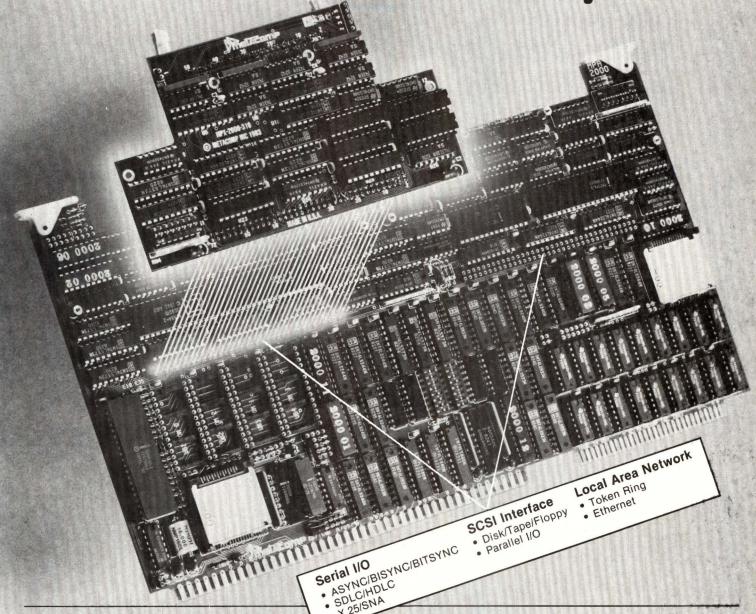

## You've asked for a 32-bit computer system with \* unlimited expansion capabilities...one that is low-cost and compact yet powerful enough for multi-user, multi-tasking requirements.

So we created the MDB Micro/32 an MC68000\*\* based system with 512KB memory (expandable to 4MB). This powerful system combines MDB's REGULUS\*\*\* with the incredible expansion capability of our in place Q-Bus\*\*\*\* repertoire of peripheral controllers...as well as our interfaces/ multiplexors for all communication modes, protocols and disciplines.

The result: speed, power and versatility of systems design you can't get anywhere else!

REGULUS is MDB's UNIX...the

most advanced and powerful version in the world. Featuring user source compatibility with UNIX V6, 7, and System III, REGULUS offers complete support of all UNIX kernel features, multi-key B-tree ISAM and VAX/ PDP-11\*\*\*\* cross support, and a host of operating systems and command functions not available in any other UNIX.

We speak your language too. Under REGULUS you can also have BASIC, FORTRAN, COBOL, PASCAL and DIBOL, in addition to most other popular compilers, utilities and special software packages.

Best of all, you don't have to wait. It's all available now. Call us today for complete information.

\*UNIX is a Trademark of Bell Laboratories.\*\*MC68000 is a registered Trademark of Motorola, Inc. \*\*\*REGULUS is a Trademark of Alcyon. \*\*\*\*\*Q-BUS, VAX PDP-11 are Trademarks of Digital Equipment Corporation

THE WORLD'S LARGEST INDEPENDENT MANUFACTURER SYSTEMS INC. OF COMPUTER INTERFACES.

Corporate Headquarters

1995 N. Batavia Street, Box 5508 Orange, California 92667-0508 714-998-6900 TWX: 910-593-1339 FAX: 714-637-4060

MDB Systems Europe, Inc. 9 route des Jeunes CH-1227 Geneva (Switzerland) Tel. (41) (22) 439410 Telex 421341 mdb ch FAX (41) (22) 439414

MDB Systems, U.K., Ltd. Everitts House

426 Bath Road Slough, Berkshire (England) SL1 6BB Tel. (06286) (67377) Telex (847185) WWTSLO FAX (41) (2812) (3507)

Circle 185 for LSI-11

Circle 186 for Micro/32

Circle 187 for REGULUS

# **UP FRONT**

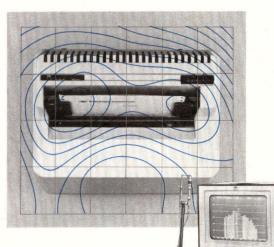

# French private branch exchange enters U.S. market

Although it is fashionable to expound on the "upcoming next generation" of equipment (see staff report, p 149), some companies are content to nibble away at a "real" market by offering equipment of a "before-the-next" generation caliber. For example, Jistel of Stamford, Conn has introduced a family of analog and digital private branch exchanges (PBXs) with which the company hopes to capture a 4- to 6-percent share of the U.S. market by 1987. (Jistel is a division of JS of America Inc, which in turn is a subsidiary of Jeumont-Schneider of Puteaux, France.) The U.S. PBX market—40 percent of that worldwide—is relatively free of the restrictions imposed in European countries. Also, the breakup of the Bell Telephone System offers an even more lucrative target for competitive companies.

Two analog voice-only systems available this quarter are time division multiplex switches using pulse amplitude modulation techniques. Jistel 95 has a capacity for 16 trunk lines and can accommodate 80 stations, while the Jistel 200 handles 32 trunk lines and 208 stations. Both products have been in use in France and other European countries for several years, but are reconfigured to adhere to U.S. FCC regulations and to match U.S. PBX competitive features. Two digital products, the 150 and 500, to be available in the last quarter of 1984, will be able to route both voice and data at a 56-kbit/s rate.

# "Concept-processing" workstation links to powerful computing

For the most part, array-based schemes favored for developing artificial intelligence, robotics, vision systems, and signal processing applications have been ideas in search of a practical development tool. To that end, Analogic Corp (Wakefield, Mass) has created its APL Machine, which turns an unmodified IBM PC into a programmer's workstation fronting its 10-MFLOPS, 32-bit AP500 array processor. Under a Unix-derived operating system, the PC runs the International Standards Organization-validated APL written on its own or outside hardware. The APL interpreter runs in the 12.5-MHz, 16/32-bit micro control processor; primitive functions and operators of APL reside in pipeline microcode. In addition, the company provides Unix-like shells that incorporate non-APL code for applications using compiled or assembled code.

# Macintosh or Granny Smith?

The high stakes personal computer game gets yet another raise in the form of Apple's long-awaited Macintosh. By spurning the pack and IBM PC compatibility, Apple is clearly drawing a line in the dirt. The 68000-based machine will have a Lisa-like operating environment such that Macintosh programs will run on the Lisa but not vice versa. The machine should also give a big boost to acceptance of the 3½-in. floppy disk that Hewlett-Packard is already using in its PC-compatible model 150. Apple is emphasizing support for independent software developers, and at the price of \$2495, Macintosh (if it makes it in the initial post-introduction phase), should give the competition a real run for the money. The basic price includes a word processing program (MacWrite) and a graphics package (MacPaint). Apple has also introduced three new models of Lisa: Lisa 2, 2/5, and 2/10, all software compatible with the Macintosh.

# Seeq to produce high endurance EEROM

One million write cycles per byte is to be the new standard for electrically erasable ROMs produced by Seeq Technology (San Jose, Calif). The 5516A, a 16-Kbit (2-K x 8) EEROM, will hopefully encourage more design-in by designers wary of write limitations in EEROMs. The part has an onchip timer and a write cycle time of 10 ms. Seeq offers the million-write version as a high endurance version of its existing 2816A. Future products will include high endurance versions of existing parts as well as yet unannounced million-write EEROMs and other ICs incorporating the high endurance "Q cell" technology onchip.

# UP FRONT

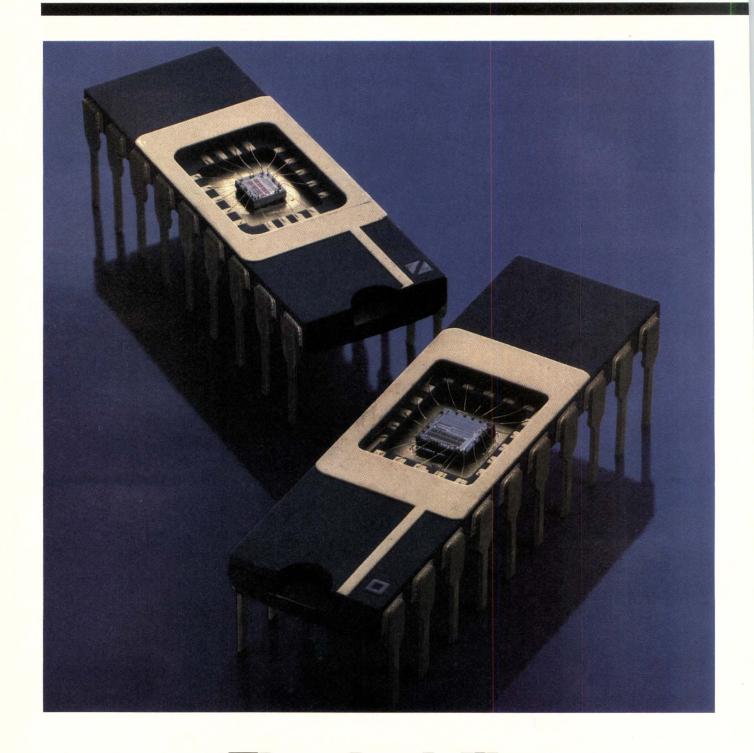

# Motorola completes CMOS RAM tests for VHSIC program

Engineers at Motorola Semiconductor (Phoenix, Ariz) have completed tests on a 4-port silicon-gate CMOS RAM as part of phase I for the Department of Defense's very high speed integrated circuit (VHSIC) program. The 4-Kbit chip is believed to be the first bulk CMOS part manufactured using Motorola's 1.25-µm HCMOS design rules. In operation, the RAM can have two independent addresses read out while two other independent addresses are being written into it, all using a single 25-MHz clock. The part is slated for an electronic warfare application for which Motorola's VHSIC partner, TRW Inc (Redondo Beach, Calif), is supplying the brassboard. The memory IC is functionally compatible with TRW's triple-diffused bipolar parts, with both types of circuits operating off a 3.3-V power supply. With 12 transistors/memory cell, the 290- x 313-mil memory chip contains a total of 59,700 transistors. This translates to a functional throughput rate (FTR) of 10<sup>11</sup> gate•Hz/cm<sup>2</sup> which, in turn, requires 300 mW of power to dissipate. The next challenge for Motorola engineers is to build a 6-Kbit CMOS gate array chip that will also be compatible with the other chips on TRW's brassboard. (Sperry Corp is a third member of the program team.)

## IBM PC backs Unix

IBM Information Systems Group (Rye Brook, NY) has announced its flavor of Unix for the IBM PC. Known as the personal computer interactive executive system (PC/IX), the operating system implements a superset of Unix System III with an interactive full-screen editor. The minimum configuration needed is 256 Kbytes of RAM, a single 320-Kbyte floppy disk drive, and a 10-Mbyte rigid disk drive. The Unix port was done by Interactive Systems (Santa Monica, Calif). It will be ready for release at the beginning of

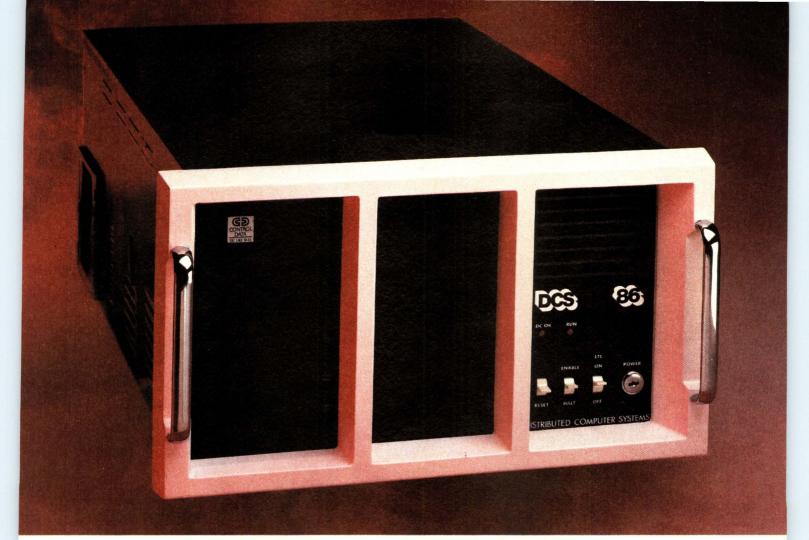

# Industrial computer slides in processing capability

Departing from the traditional shared logic approach of single CPU systems, Indocomp, Inc's (Drayton Plains, Mich) IMP-68000 depends on independent processors. Each processor runs its own operating system and executes its own application programs. This prevents one processor crash from affecting other running processes. Slide-in processor boards (all front accessible) consist of a standard processor section and a customized I/O section. Current I/O sections include both digital and analog boards as well as a development board with predrilled holes and a large wirewrap area.

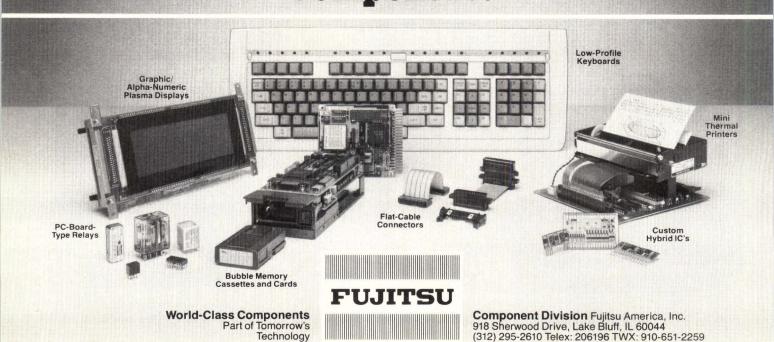

# TI and Fujitsu to alternate source bipolar, CMOS arrays

At a still-unannounced future date, Texas Instruments (Dallas, Tex) will supply gate array products based on design and fabrication information from Fujitsu Ltd (Santa Clara, Calif). This alternate-source agreement between the American and Japanese semiconductor giants covers both bipolar and CMOS devices. Specifically, these will be bipolar Schottky TTL arrays with 1.9-ns delays in densities ranging from 240 to 1100 gates; and H-series and VH-series CMOS arrays in densities from 440 to 8000 gates. Both TI and Fujitsu have proprietary computer aided design systems and design languages. To aid customers, each company will provide the means to accept circuit descriptions written in the other's language and convert them to produce guaranteed compatible parts. The companies emphasize that Fujitsu is giving TI parameters for producing compatible designs rather than actual process technology.

COMPUTER DESIGN©1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell Street, Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elsewhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. POSTMASTER: CHANGE OF ADDRESS-FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (USPS 127-340).

Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101: P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President/Finance; L. John Ford, Vice President.

COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

# 200 MB/second!

# World's Fastest Bulk Memory System

It's true. WIDE WORD, Dataram Corporation's new, third generation of its popular BULK SEMI memory systems, delivers an incredible data rate of 200 MB/sec! Achieved by utilizing a word length of 80 or 160 bits and four-way interleaving.

Much faster than even the fastest minicomputers can handle...but not too fast for your real-time applications, image processing, array processing or data acquisition needs.

Dataram's WIDE WORD BULK SEMI is ready to perform for you. Now! Multi-port capability makes it possible to interface WIDE WORD BULK SEMI to your host minicomputer: Connect one port to your high-speed input; the other to your mini.

A library of dedicated interfaces — for Digital Equipment Corporation, Data General, Ampex, Control Data, CSPI, Honeywell, Intel, MODCOMP, Perkin-Elmer, ROLM, and SEL — make it easy to interface to most minicomputers.

WIDE WORD BULK SEMI. 32 MB of high-performance memory in a compact 153/4" system. Word lengths up to 160 bits. And, of course, a data rate of 200 MB/second.

Our 16-page BULK MEMORY brochure will tell you more. And you can have it at no charge by completing the coupon at right, or calling us at (609) 799-0071.

Princeton Road

Cranbury, NJ 08512 (609) 799-0071 TWX: 510-685-2542

## WHAT'S THE BIG IDEA?

□ Send me your 16-page brochure detailing BULK SEMI.

□ Please call me to discuss my application.

Name \_\_\_\_\_\_Title \_\_\_\_

Company \_\_\_\_\_

Company \_\_\_\_\_

Address \_\_\_\_\_\_State \_\_\_\_ Zip \_\_\_\_

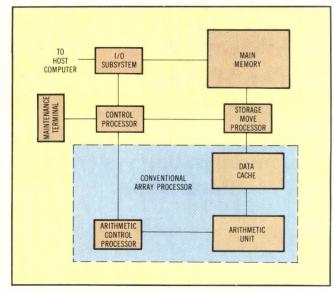

Telephone

Minicomputer \_\_\_\_\_

# **COMPUTER DESIGN®**

# System technology

Page 56

- 27 Interface:

Thirty-two bit system designers face decision time

- **49 Software:**Local area networks proliferate while standards lag

- 56 Integrated circuits:

Chip finds degree of similarity between strings

- **64 Data communications:**Terminals move to X.25 transparent to host

# System design

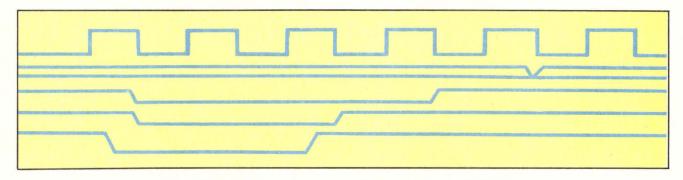

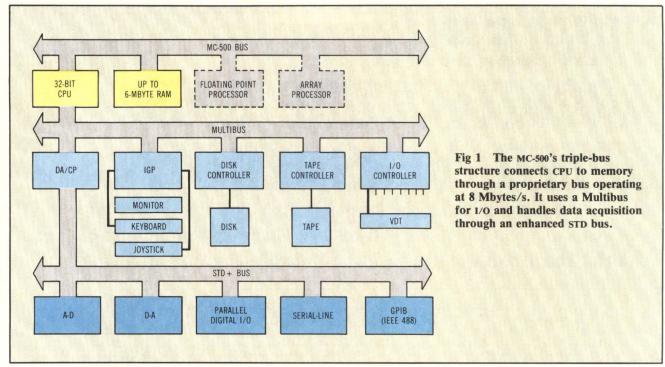

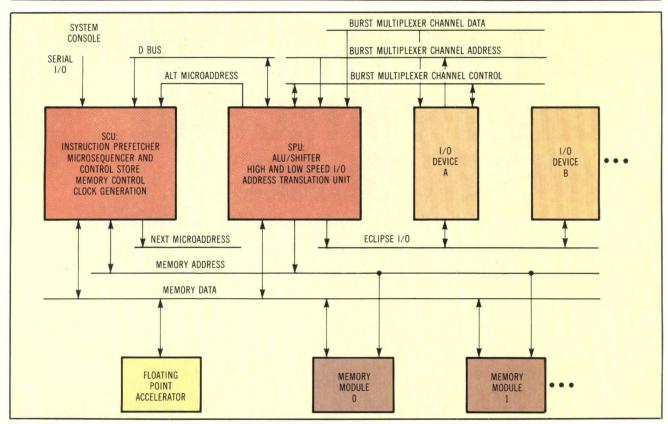

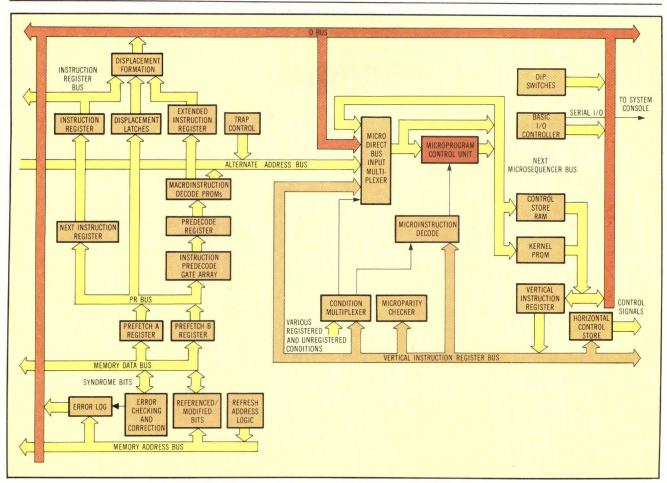

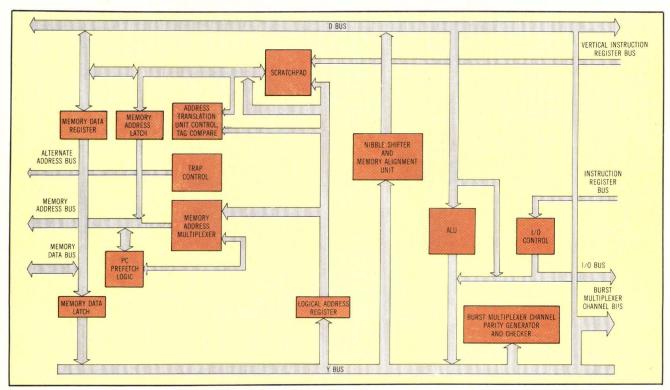

- 73 Microprocessors/microcomputers: Triple-bus architecture gains speed, versatility

by Dave Cane and Steve Mullen—Both problems and opportunities lurk for designers of realtime minicomputer systems. A three-pronged approach attacks the problems inherent to single-bus architecture.

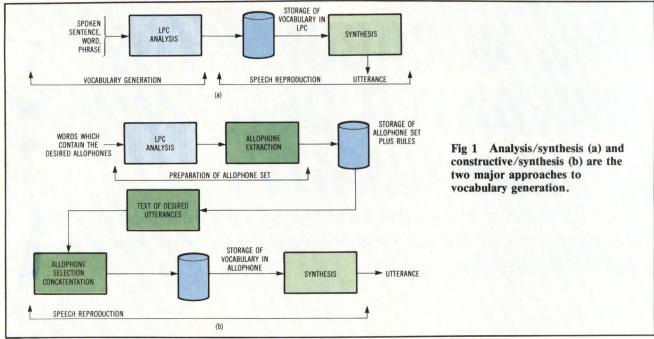

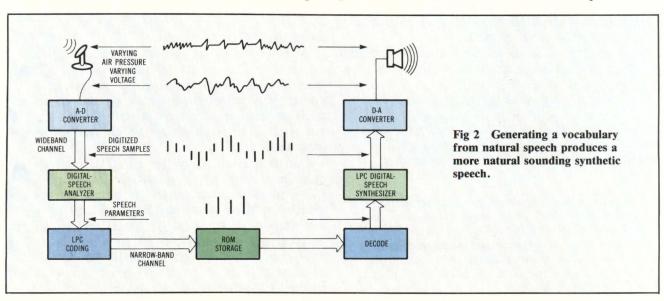

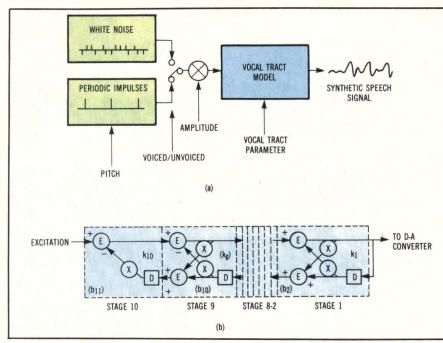

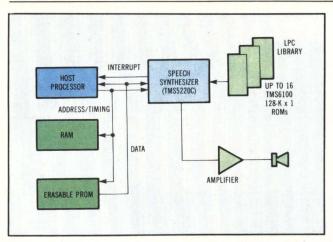

- 89 Data conversion: How vocabulary is generated determines speech quality by Michael W. Hutchins and Lee Dusek—Synthetic speech vocabulary can be generated by analyzing natural speech or by artificial construction from phonetic parts, with differing results.

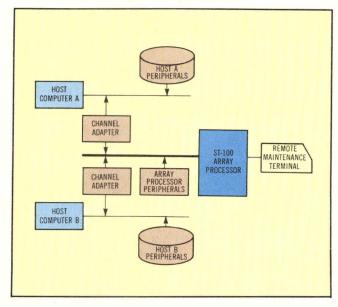

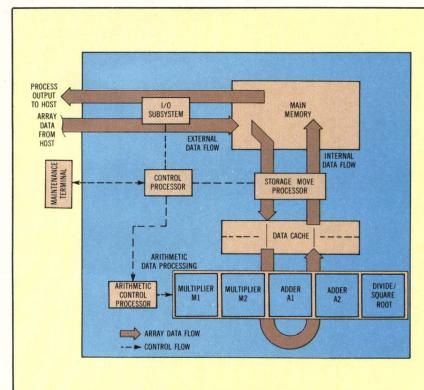

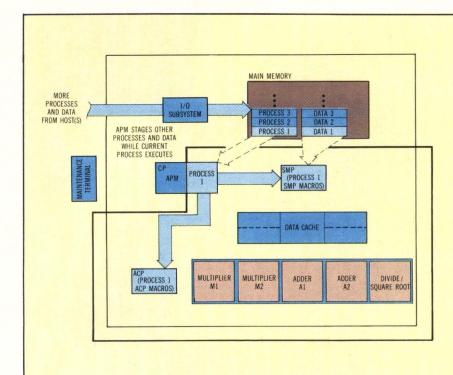

- 105 Computers: Array processor achieves 100 MFLOPS by Robert Hausman and Phil Cannon—Parallel architecture and fast hardware team up with a resident operating system to speed data flow and minimize host communication.

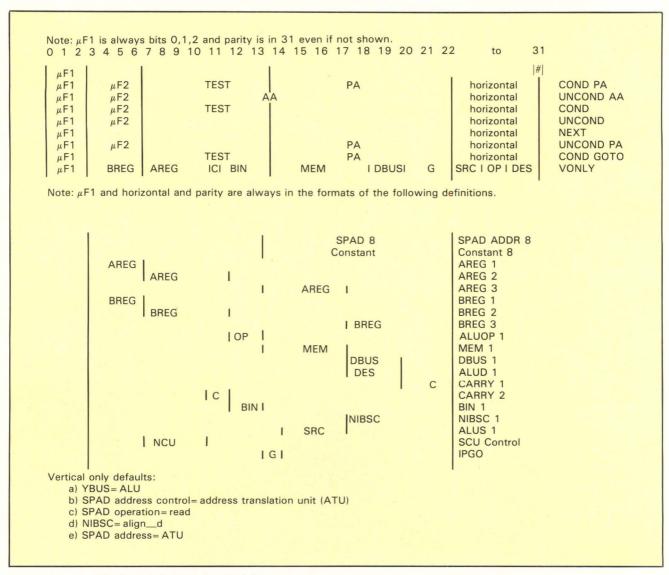

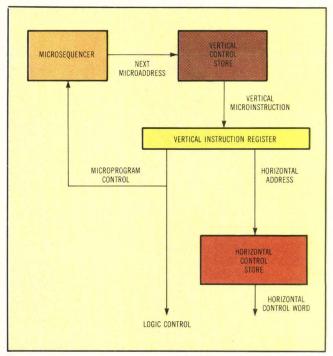

- 121 Computers: Using an efficient microarchitecture achieves goals by Kenneth Burns and David M. Burns—Careful microarchitecture planning enables design engineers to achieve dual goals of low cost and high performance in a 32-bit computer.

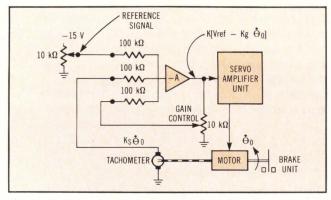

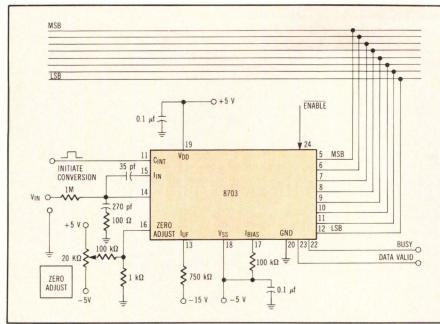

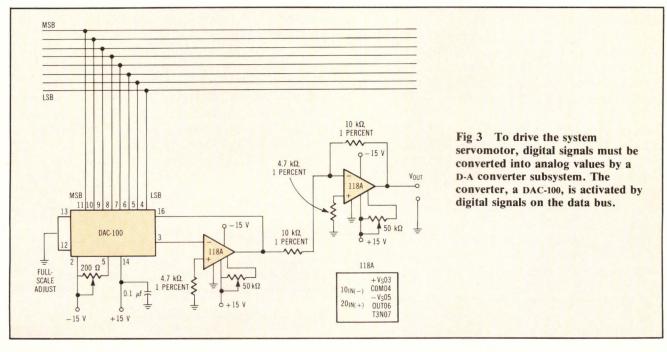

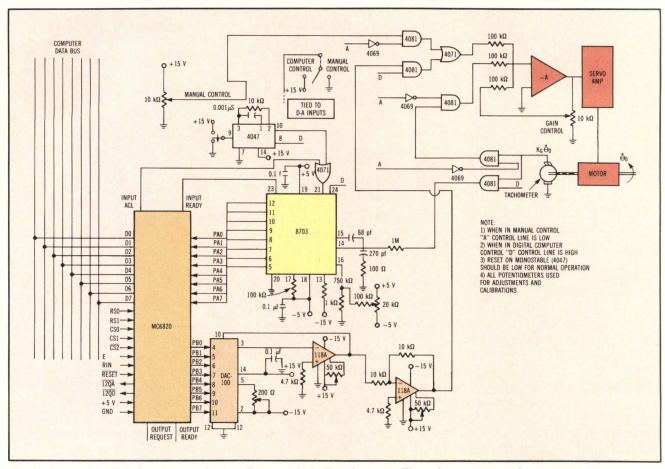

- 137 Microprocessors/microcomputers: Motor control system design hinges on processor delays

by Manuel R. Cereijo—Microprocessors are a boon to motor-speed controllers, but certain limitations of the devices must be accounted for in system designs.

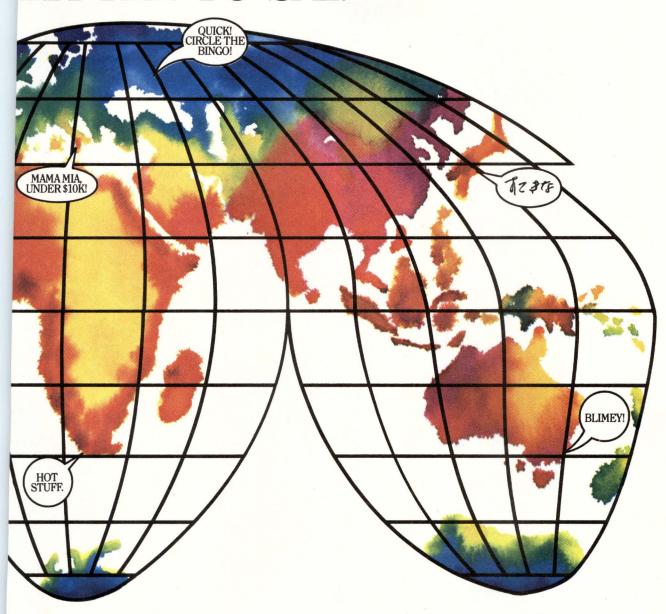

# Special report on data communications

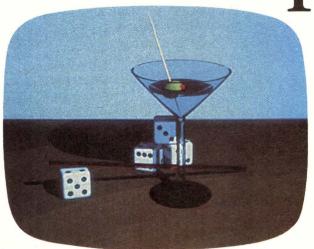

145

This month's data communications report includes many of the same local network topics discussed here a year ago. A few new choices and some extra flavored ingredients for the established entrees, however, add spice to the computer designer's menu. With digital PBXs giving LANs a run for their money, and LSI chips making the final choice between the two ever so difficult, the engineer will have to study this year's menu carefully before making the "right" selections. Bon appetit!

This month's cover was created and designed by Mark Lindquist on the Digital Effects Video Palette III and D-48 high resolution camera system.

# **System components**

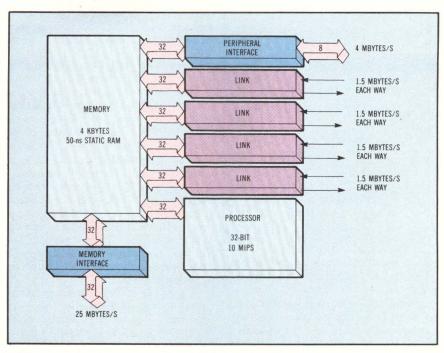

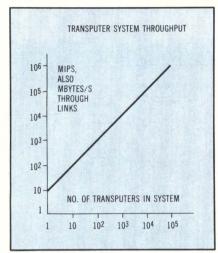

243 Transputer—a programmable component that gives micros a new name

246 Graphics system functionality swells with million addressable points

246 Low cost plotter combines graphics command set and offline operation

248 Laser-based optical disk drive stores 1 million bytes

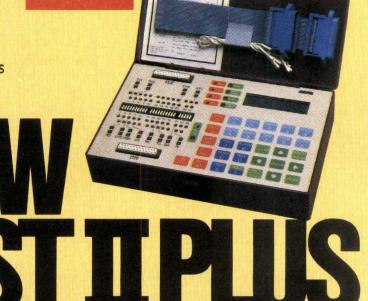

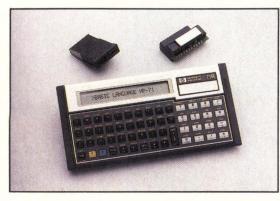

248 Open architecture characterizes programmable handheld computer

250 Compact station engineers hierarchical VLSI design system

250 Condensing architecture makes small system perform big

252 Winchester/floppy controller rules over diverse disk selections

252 Portable operating system easily adapts to specific microcomputers

259 Data communications 274 Integrated circuits

260 Interface 275 Software

262 Test & measurement 278 Interconnection & packaging

264 Memory systems 280 Computers

265 Peripherals 282 System elements

267 Microprocessors/microcomputers 289 Control & automation

268 Data conversion 291 Power sources & protection

270 Development systems

# **Departments**

| 3   | Up front              | 300 | Designer's bookcase    |  |

|-----|-----------------------|-----|------------------------|--|

| 11  | Editorial             | 303 | System showcase        |  |

| 17  | Letters to the editor | 306 | Advertisers' index     |  |

| 294 | Calendar              | 315 | Reader inquiry card    |  |

| 297 | Literature            | 315 | Change of address card |  |

Editorial reviewer for part of this issue:

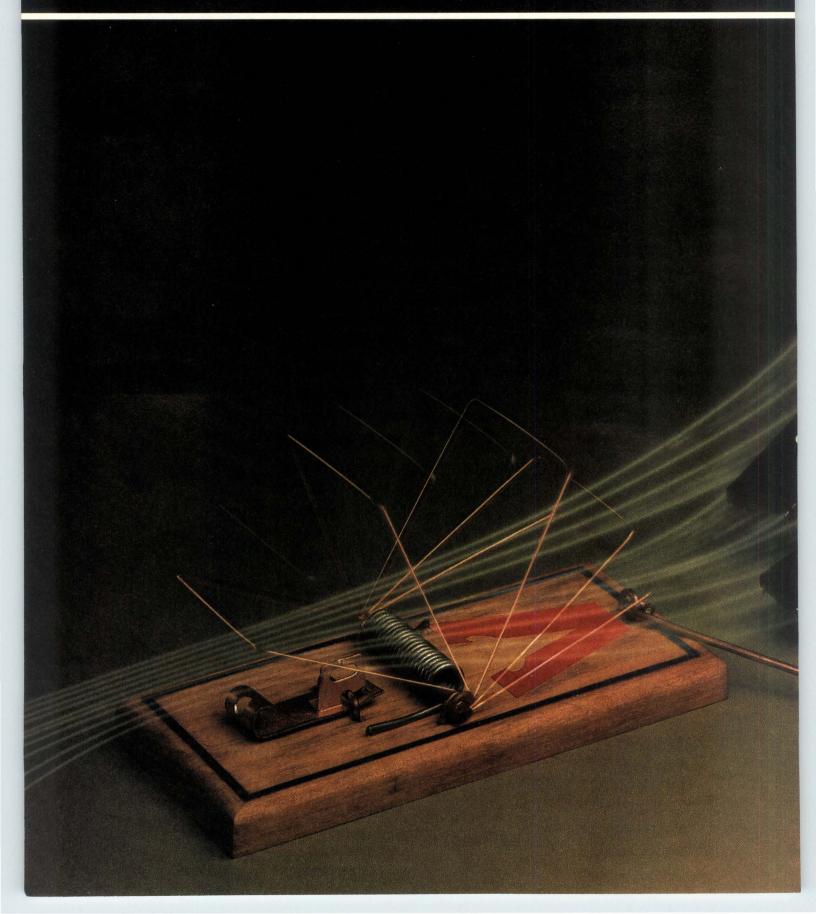

# You'll never get trapped into dead-end designs with

# Zilog's high-speed Z80B CPU's and Peripherals.

Here's more proof that nobody does more to extend the life of your 8-bit designs than Zilog. Because now you can increase 8-bit Z80\* performance up to 6 MHz with the high-speed Z80B CPU and its family of peripherals. You can join the hundreds of design engineers that have already tested this claim with winning results. Or wonder...

Is there something here they know that you don't?

Like the fact that the Z80B CPU has the same 158 instruction set and the elegant registers and interrupts that you're used to working with, but runs them 50 percent faster than the Z80A chip?

That the Z80B processor is completely software compatible with the rest of the Z80 family, permitting you to upgrade to higher performance without getting trapped into software redevelopment? That software compatibility also means you can use the Z80B device in co-processing and/or multi-processing environments along side our other Z80 processors?

And consider the fact that you can surround our Z80B CPU's with a complete family of Z8400 and Z8500 peripherals and really boost system performance. They help you keep your parts and space requirements to a minimum and increase system throughput because we build more functions into every device. The peripherals include a PIO, a CTC, an SIO, an SCC, an FIO, an FIFO, a CIO, and a UPC.

For complete specifications and applications data on the Z80B and peripherals, fill out the coupon and mail to: Zilog, Inc., Components Tech. Publications, 1315 Dell Avenue, MS C2-6, Campbell, CA 95008. Or call our TOLL FREE Literature Hot Line at 800-272-6560. For information on Zilog's other components, call (408) 370-8000.

Z80 is a registered trademark of Zilog, Inc.

| ☐ I'd like more inform☐ Please have a salesn |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Name                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| Title                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| Company                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| Address                                      | <b>一种的基础</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| City                                         | State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Zip     |

| Phone/ Z80B/Peripherals                      | 的 100 mg | CD 2/84 |

Zilog an affiliate of EXON Corporation

Pioneering the Microworld

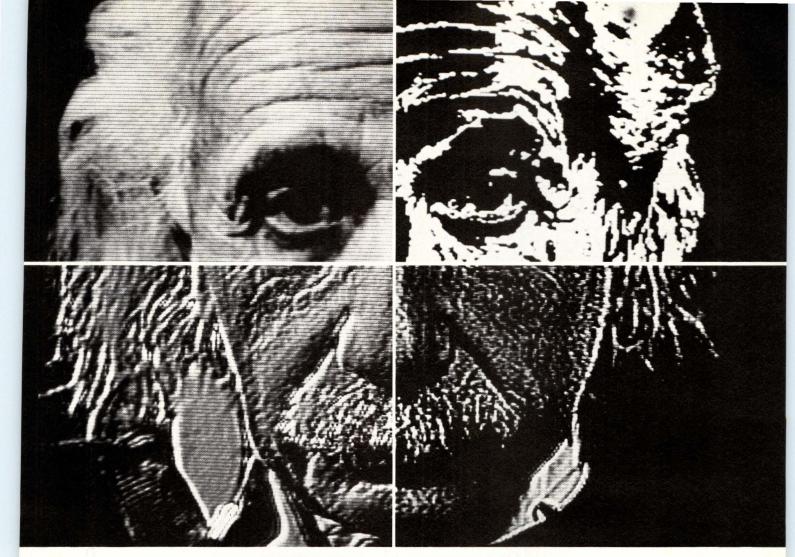

# the technology is...

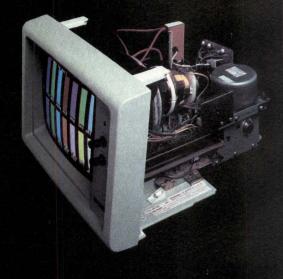

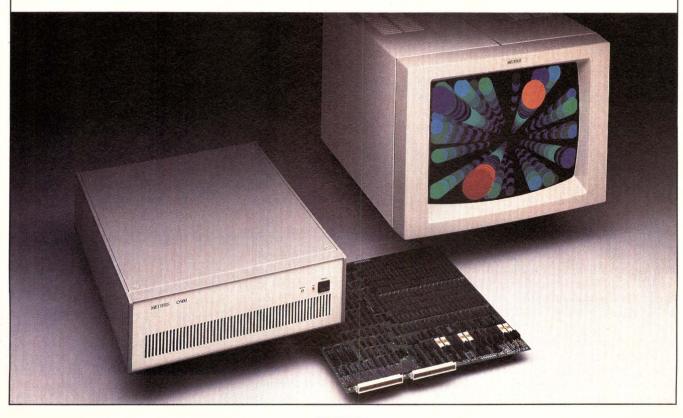

Hitachi introduces the new standard in Hi-Resolution. That standard is embodied in our new HM-4619 RGB Color Monitor.

The HM-4619 delivers flicker-free images with  $1280 \times 1024$  resolution at 60 Hz. Hitachi tube technology leadership has created a new inline gun delivering high brightness with sharper focus. All of this is enhanced by our Digital Dynamic Convergence™ of 0.1/0.3 mm.

The Hitachi line of RGB Color Monitors is rapidly becoming the clear choice of OEM's throughout the world. We feel our new, top of the line, HM-4619 is the unit which will set the standard by which all other color monitors will be judged.

- New In-Line Gun with Hi-Brightness and Sharp Focus

- 1280 × 1024 Resolution at 60 Hz

- 0.1/0.3 mm Misconvergence

- 100 MHz Video Bandwidth

- Compact Design

- Cost Effective State of the Art Technology Plus the Strength of Hitachi Worldwide Support

## The Image Speaks for Itself

Hitachi America, Ltd. 59 Route 17S, Allendale, NJ 07401 (201) 825-8000 (201) 825-8000

3540 Arden Road, Hayward, CA 94545

(415) 783-8400

Hitachi Europe, Ltd., Lee House (10th Floor)

London Wall, London EC245AS

(01) 606-7831

Hitachi Denshi Canada, Ltd. 65 Melford Drive

Scarborough Ontario, Canada MIB 2G6

(416) 299-5900

H-I® Hitachi America, Ltd. computer graphic courtesy of METHEUS Corporation, Hillsboro, Oregon

# THE COMPUTER ILLITERACY THREAT

Many years ago, we knew a fellow who sold encyclopedias. His selling technique was brutal but quite effective. Usually, he would work low income neighborhoods, going from door to door. If the prospects had children, he would ask if they wanted their kids to grow up as poor and uneducated as their parents. Except in those cases where the door slammed in his face, it was then surprisingly easy for him to convince the concerned parents that the purchase of a set of encyclopedias on an easy payment plan virtually guaranteed that their kids would become prosperous geniuses.

Today, unfortunately, many personal computers are being sold in a similar fashion. Now we are starting to read and hear a lot about "computer literacy" without which, it is said, our

children will not be able to survive in an increasingly competitive and computerized world. Yet, although many people talk about computer literacy, nobody ever bothers to define it. Therefore, we are not sure whether it means the ability to play a fair game of Pac-Man, or the ability to write device drivers in assembly code. Either way, however, the skill does not seem to have any particular relevance to survival in tomorrow's business world.

Computer system designers know that, by the time today's schoolchildren join the work force, a business computer will be no more difficult to use than a typewriter or telephone. Tomorrow's computer users will not have to worry about the subtle quirks of operating systems, just as today's users do not have to get Cobol programs keypunched onto decks of cards. Yet, the public seems to have been brainwashed by the computer literacy argument that has been pounded home by repeated TV commercials. People today ask engineers not whether they should buy a personal computer, but only which one to buy.

In a few years, it is very possible that personal computers will provide convenient educational workstations at which children can learn, draw, write, and calculate. So far, however, most educational software is so abysmal that a computer is a needlessly expensive replacement for a conventional blackboard and textbooks.

Apart from maintaining the financial health of computer companies, therefore, we see no urgent need to accelerate the introduction of personal computers into the school or home. Certainly, we see no overwhelming national benefit in such proposed legislation as HR701—a bill introduced by Congressman Fortney Stark of California—which would give computer makers a double tax write-off for donating their computers to schools. If we as engineers push too vigorously for such legislation—in the misguided hope that it will aid the computer industry—we may find that we have lost our professional credibility when the fad has passed and unused personal computers are littered around like Rubik's Cubes or Pet Rocks. Yes, computers should have a bright future in business, the classroom, and the home—but not if we kill the industry with premature and excessive hype.

Michael Elphick Editor in Chief

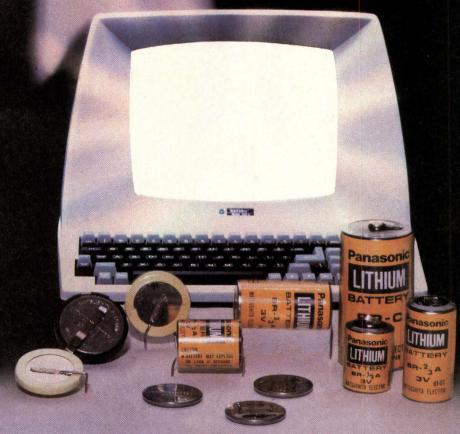

# MEMORIES.

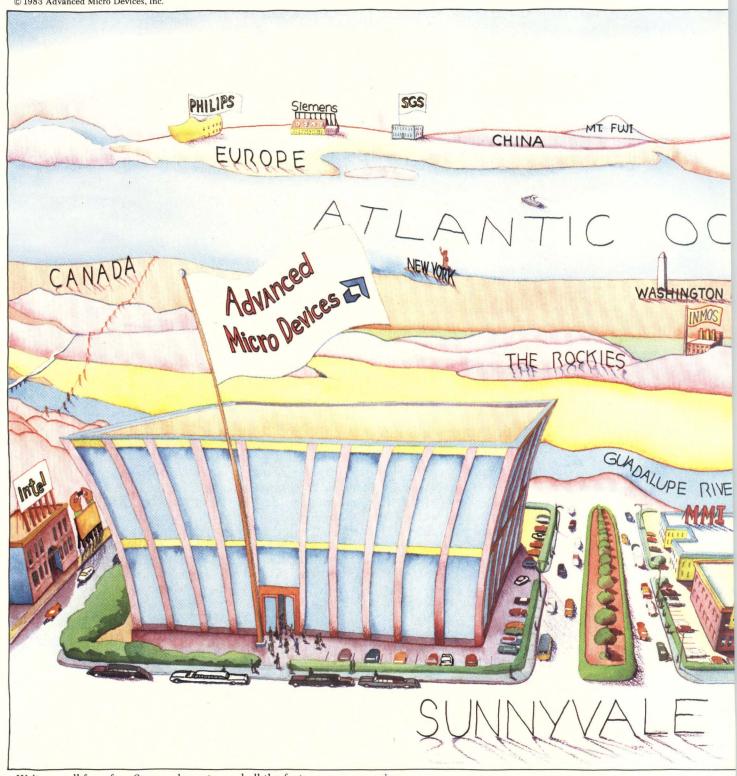

© 1983 Advanced Micro Devices, Inc.

Write or call for a free Sunnyvale poster and all the facts on our memories.

# A WORLD PERSPECTIVE.

If you're looking for the world's fastest MOS static RAMs, don't look in Holland.

Searching for the world's fastest bipolar PROMs? Forget Texas or Arizona.

And you won't find the world's fastest EPROMs anywhere near Mt. Fuji.

They're all right here in Sunnyvale. At Advanced Micro Devices.

# Everything we make is fast. Including the Am27256, the world's fastest 256K EPROM.

The Am27256 is 170ns fast. It's the only EPROM quick enough to keep up with a 10MHz MPU without a wait state.

And we've got the 40ns Am27S43A, the world's fastest 32K bipolar PROM. And the 35ns Am2167, the world's fastest 16K static RAM.

With leading-edge parts like these, it's no wonder memories account for half our total sales.

And our other products are just as hot. Controllers. Bipolar and MOS microprocessors. Communications circuits. Signal processors. We've got 'em all, and then some.

And every single chip meets or exceeds the International Standard of Quality.

Next time your design demands high performance memories, or any highperformance parts, look us up.

We put high performance on the map.

# Advanced Micro Devices 2

901 Thompson Place, P.O. Box 3453, Sunnyvale, CA 94088 For direct factory response call (408) 749-5000. Outside California, call toll free (800) 538-8450, ext. 5000.

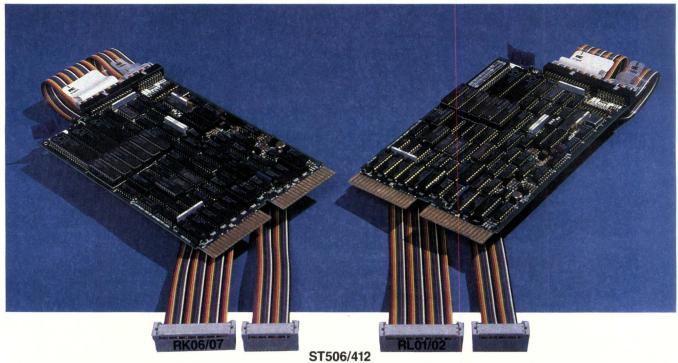

# **MORE STORAGE FOR LESS**

DEC USERS

LSI-11 COMPATIBLE

# **EMULATION RK06/RK07**

## **EMULATION RL02**

42MB Winchester/Floppy (8") ... \$6995.00 70MB Winchester/Floppy (8") ... \$7495.00

10MB Winchester/Floppy (8")..... \$4495.00 20MB Version Add . . . . . . . . . \$ 500.00

140MB Winchester/Floppy (8") ... \$9995.00

ALL SYSTEMS CONTAIN 2MB OF FLOPPY BACKUP

\* NEW \*

MORE MEMORY ON A SINGLE CARD THEN ANY OTHER MANUFACTURER 512KB TO 2MB QBUS ERROR DETECTING AND CORRECTING MEMORY

\* NEW \*

CALL FOR MORE DETAILS!

"OFFERING QUALITY WITH AFFORDABLE PRICING"

# Chrislin Industries,

31352 Via Colinas • Westlake Village, CA 91362 • 213-991-2254 TWX 910-494-1253 (CHRISLIN WKVG)

RK06, RK07, RL02, QBUS, DEC, LSI-11 are trademarks of Digital Equipment Corporation.

CIRCLE 8

# FREE **PUBLICATIONS**

Use the handy order form in the tax package to obtain free IRS publications on over 90 different tax topics.

A PUBLIC SERVICE MESSAGE FROM THE INTERNAL REVENUE SERVICE

# **COMPUTER DESIGN**

Editor in Chief, Michael Elphick Managing Editor, Sydney F. Shapiro

Senior Editors, John Bond Peg Killmon

Senior Associate Editor, Deb Highberger

Associate Editor, Malinda E. Banash

Chief Copy Editor, Leslie Ann Wheeler

Copy Editors, Helen McElwee Lauren A. Stickler Jack Vaughan

New York Field Office

Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin 230 Park Ave, Suite 907, New York, NY 10169, Tel: 212/986-4310

Western Field Offices

Managing Editor, Tom Williams 540 Weddell Dr, Suite 8, Sunnyvale, CA 94086, Tel: 408/745-0715

Field Editor, Sam Bassett 1714 Stockton St, San Francisco, CA 94133 Tel: 415/398-7151

Field Editor, Joseph A. Aseo 331 Freeway Center Bldg, 3605 Long Beach Blvd, Long Beach, CA 90807, Tel: 213/426-1172

Publisher, Gene Pritchard

Marketing Director. Robert A. Billhimer

Circulation Director, Robert P. Dromgoole

Production Assistant, Philip Korn

Design Coordinator, Lou Ann Morin

Technical Art, Designline

# **DennWell**

Advanced Technology Group 119 Russell Street. Littleton, MA 01460 Tel: 617/486-9501

H. Mason Fackert, Group Vice President

Saul B. Dinman, Editorial Director

David C. Ciommo, Controller

Steve Fedor, Promotion Director Linda G. Clark,

Marketing Services/PR Manager Linda M. Wright, Production Director Wanda Holt, Data Services Manager

Pat Armstrong, Administrative Services Manager

# It's just not fair to claim that TEMPLATE® is the best graphics software available. Our competition's already discouraged.

And we like competition. We really do. It's just that it's difficult, if not impossible, to find graphics software as efficient and functional as TEMPLATE. Try as you might. TEMPLATE is the hands-down winner. With true device-independence and intelligence, total graphics functionality for CAD, scientific analysis, seismic work, process control, molecular modelling, and a host of other applications.

In almost any environment, whether it's batch or interactive, 2D or 3D, TEMPLATE wins. Benchmark tests prove it. TEMPLATE, besides being a true 3D graphics package for 32-bit or larger computers, features powerful commands that provide matchless productivity. TEMPLATE makes optimal use of available computer resources, giving you fast, efficient computer graphics program execution. And it supports over 125 graphics devices, from dumb termi-

nals to sophisticated systems.

We also provide on-site installation and training, continuous updates, a regular flow of new device drivers, and ongoing documentation. What's more, we back you up with a telephone hotline so TEMPLATE software specialists can provide help if you need it.

But let's be fair. If you're looking for graphics software, call our competitors first. Find out what they have to say about theirs. Then call us, and find out why TEMPLATE really has no competition.

And why the competition has been so discouraged for so long.

World Headquarters • 9605 Scranton Road • San Diego, California 92121 • 619/455-5590 • TWX: 910-337-1270 European Headquarters • 34, avenue du Tribunal-Fédéral • CH-1005 Lausanne, Switzerland • Telephone: 41/21/20 70 55 • Telex: 25 037 mega ch

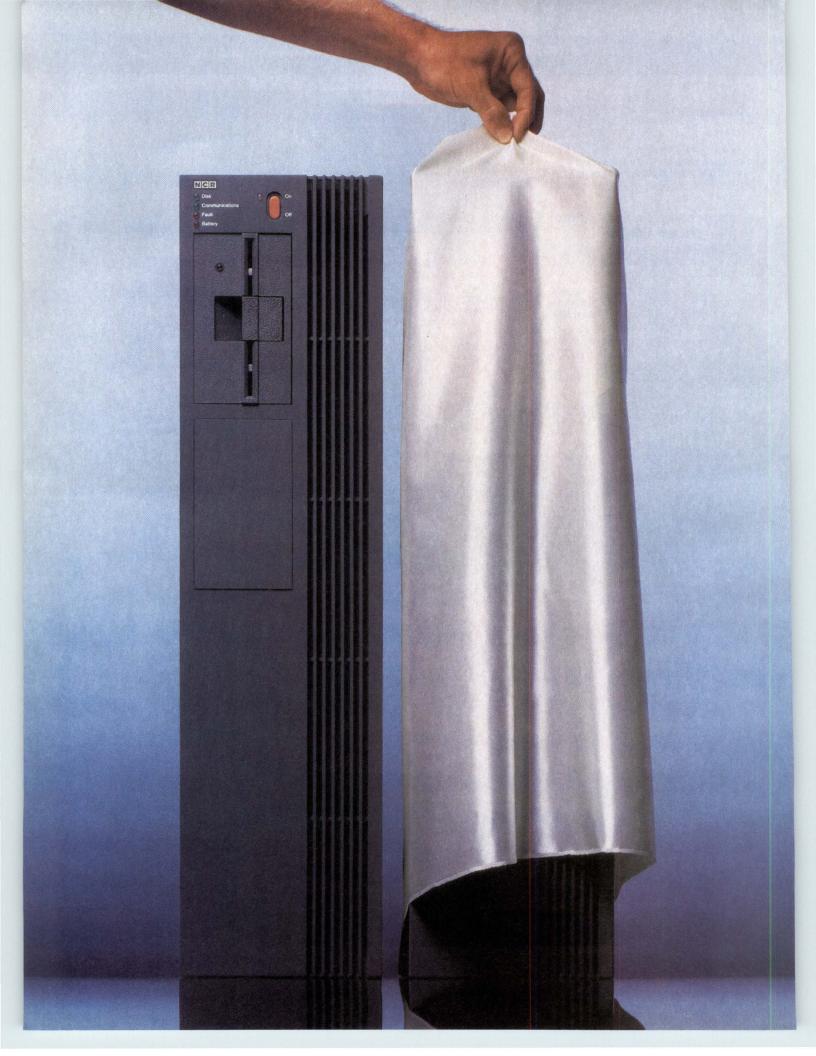

# Like DEC's.

DATARAM

\$8,845 system price\*

256 KB minimum... up to 4 MB!

Media and software compatibility with DEC's RX02 8" floppy (vs. Micro/PDP-11's non-compatible 51/4" floppy)

8-quad slot Q-BUS card cage

Supports RT-11, RSTS, RSX-11M-PLUS, UNIX, and TSX-PLUS

> Two fans in card cage area (vs. one in Micro/PDP-11)

> > Cartridge tape capability

DEC, LSI-11, Micro/PDP, PDP, RSTS, RSX, and RT-11 are trademarks of Digital Equipment Corporation. TSX-PLUS is a trademark of s&h computer systems, inc. UNIX is a trademark of Bell Laboratories.

**CIRCLE 11**

RL02-compatible 51/4" Winchester disk; 10 MB, 20 MB, or

40 MB capability

Only better.

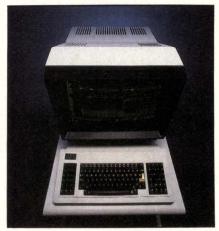

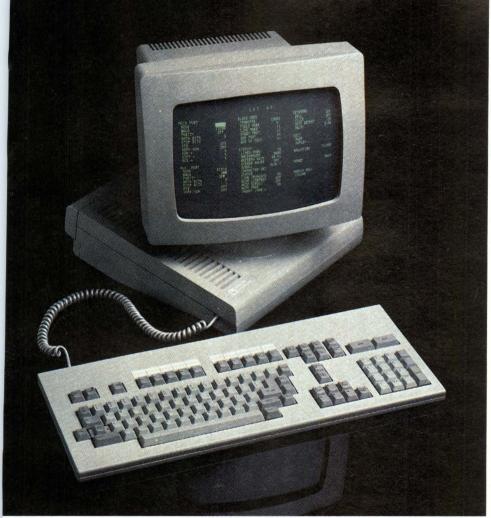

You can buy DEC's Micro/PDP-11 with its impressive array of features...or you can get Dataram's A22 -an LSI-11/23 based minicomputer that gives you a whole lot more...for a lot less dollars! Like an 8" RX02-compatible floppy. 40 MB 5¼" Winchester and ¼" cartridge tape capability. And two fans that provide push-pull air flow in the card cage area. For more information, forward this coupon to us, or, for faster response, call (609) 799-0071.

- ☐ Send information.

- ☐ Contact me immediately.

1.0 MB floppy disk

back-up (vs. 2 x 400 KB

for Micro/PDP-11)

Name

Company

Address

State

Dataram Corporation, Princeton Road, Cranbury, NJ 08512

Zip

\*\$8,845 is single-quantity domestic price for A22 with LSI-11/23, 256 KB, 10 MB Winchester and RX02-compatible 8" floppy.

Dataram Corporation □ Princeton Road □ Cranbury, New Jersey 08512 □ Tel: 609-799-0071 □ TWX: 510-685-2542

# **LETTERS TO THE EDITOR**

## Identifying management differences

This is written in response to your editorial (Oct 4, 1983) entitled "Wa Versus the Gunslingers." I believe that you identified the main point of management style differences. American managers seem to love a crisis where they can fumble or manage their way through it. Japanese managers consider a crisis, any crisis, a management failure. Simple, isn't it? But what a difference.

Eugene S. Redner Digital Equipment Corp 146 Main St Maynard, MA 01754

#### Another look at the IEEE...

Congratulations on the Nov 1983 editorial "Democratizing the IEEE." I am sure that Mr Elphick has done the IEEE and the profession a great service by airing some of our dirty laundry in public. Perhaps this will lead to less dirty laundry.

The editorial was of special interest to us in Rochester, because Malcolm "Mac" Drummond is a Rochesterian, and is active in local Section activities. With your kind permission, I would like to reprint your editorial in *The Rochester Engineer*. It is a monthly publication of the Rochester Engineering Society, and carries several pages of IEEE news, as well as news from other member engineering societies. The total circulation is, I believe, in excess of 3000, including about 1400 IEEE members.

I hope that you are able to continue to present, on occasion, an unsanitized view of the IEEE. The only other unbiased source of information on IEEE doings seems to be *EE Times*.

Jacob Z. Schanker IEEE, Rochester Section 65 Crandon Way Rochester, NY 14618

I just got to the Nov 1983 IEEE editorial. I hope you voted for Irwin Feerst and also sent his committee a contribution. Perhaps your editorial and others will help get IEEE back on track, but I doubt it. I quit several years ago and haven't had any second thoughts.

Jonathan A. Titus The Blacksburg Group, Inc PO Box 242 Blacksburg, VA 24060 The Nov 1983 editorial, "Democratizing the IEEE," was terse and to the point. Simply put, the IEEE does not support the group that supports it—the working engineer.

Your identification of Edward J. Doyle (IEEE's former VP for Professional Activities as of Dec 31, 1983) as the villain in the RCA pension dispute was correct. And in the furor surrounding the "return home" clause of the pending immigration bill (which would require that all foreign graduates of American colleges return home for at least two years) you were also correct. So long as this important position is selected by IEEE's Board of Directors and not elected by the membership, there is little hope that the VP for Professional Activities will reflect the wishes of the membership.

For this reason, we are sponsoring an amendment to IEEE's constitution that would make this position an elective one. Interested readers may obtain a copy of the petition form by writing to the undersigned.

Irwin Feerst Committee of Concerned EEs PO Box 19 Massapequa Park, NY 11762

#### . . . A different look at the IEEE

The perennial gadfly, Irwin Feerst, has received so much unwarranted press coverage, the effect is nauseating. The Nov 1983 issue of *Computer Design* carries another of his unsubstantiated diatribes. Not only that, Mr Michael Elphick, editor in chief, joins him in belittling IEEE procedures and policies. I expect more mature journalism.

IEEE is by no means perfect, but as many times as Irwin Feerst has run and been rejected by the majority of its members, he and Michael Elphick ought to be getting the message. While Mr Elphick may have a valid point in the case of Mr Lewis and Mr Drummond, he cannot be trusted if he associates himself with Mr Feerst. Computer Design ought to be able to do better.

Jens J. Jonsson Brigham Young University Electrical Engineering Science Dept Provo, UT 84602 The Nov 1983 editorial, "Democratizing the IEEE" is in tune with the loud noise exerted by the street people who are always fortified by "coke" and weeds. Legislation requiring alien engineering students to return home upon graduation is a pathetic political attempt to rectify inexorable economic facts. The logic behind it is equivalent to saying that we had better ship Einstein back to Germany, because he is competing unfairly with Americans.

Legislating import quotas for computers, autos, and engineers is simply a frank admission of mediocrity. It is untenable in a free market. Trying to "democratize" IEEE will have no effect whatsoever. Your editorial efforts will be more appreciated if you will stick to developing better guidelines for computer design.

Frederick Marich Amdahl Corp 110 Seville Way San Mateo, CA 94402

In my editorial, I never took a position either for or against a return-home clause for foreign engineering students. I merely proposed that the IEEE should be responsive to the wishes of the majority of its members. In the absence of a formal referendum, we still do not know the majority position on this issue. Apparently, the IEEE's Professional Activities Committee changed its position without consulting the membership. This indecisiveness undermined the credibility of any position the IEEE might adopt and also forced the resignation of an energetic volunteer worker. If the IEEE persists in taking positions on major issues without polling the membership, its leadership must take full responsibility for their actions. This makes them fair game for editorial comment and for criticism from people like Irwin Feerst who suspect they are motivated by narrow corporate and academic interests.

Michael Elphick Editor in Chief

(continued on page 20)

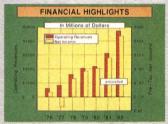

# CONTROL DATA: AFTER 25 YEARS, STILL THE LEADER IN THE PERFORMING ARTS.

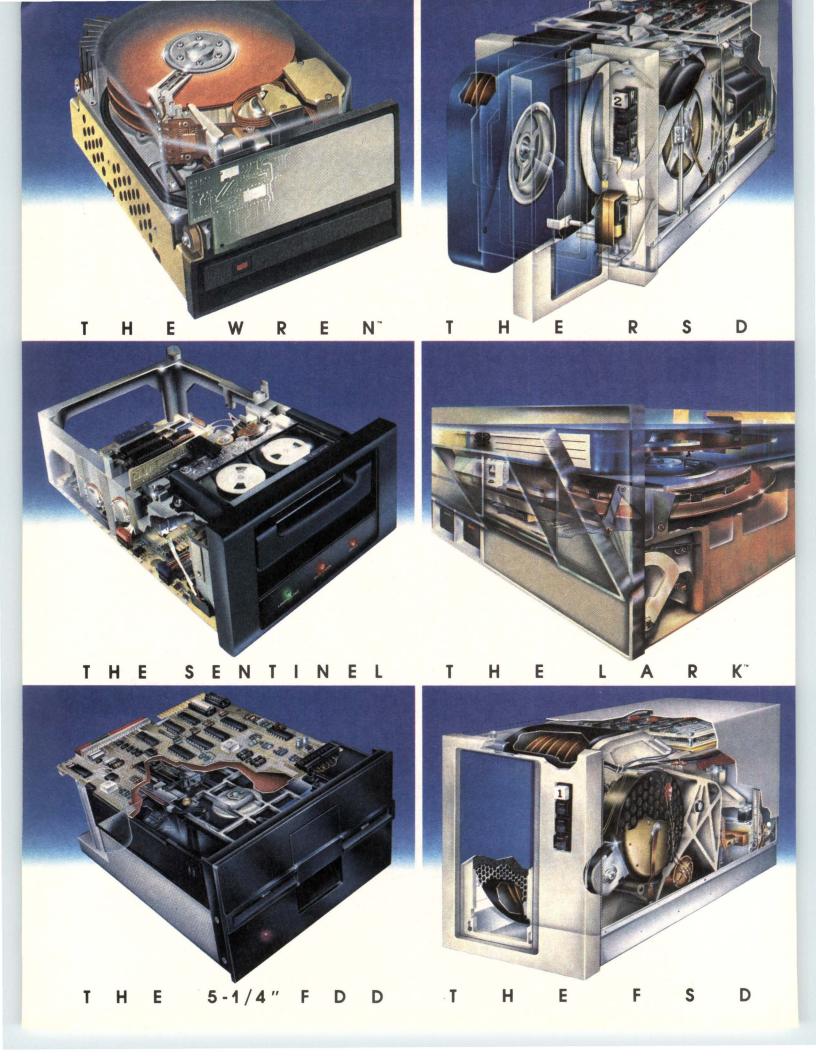

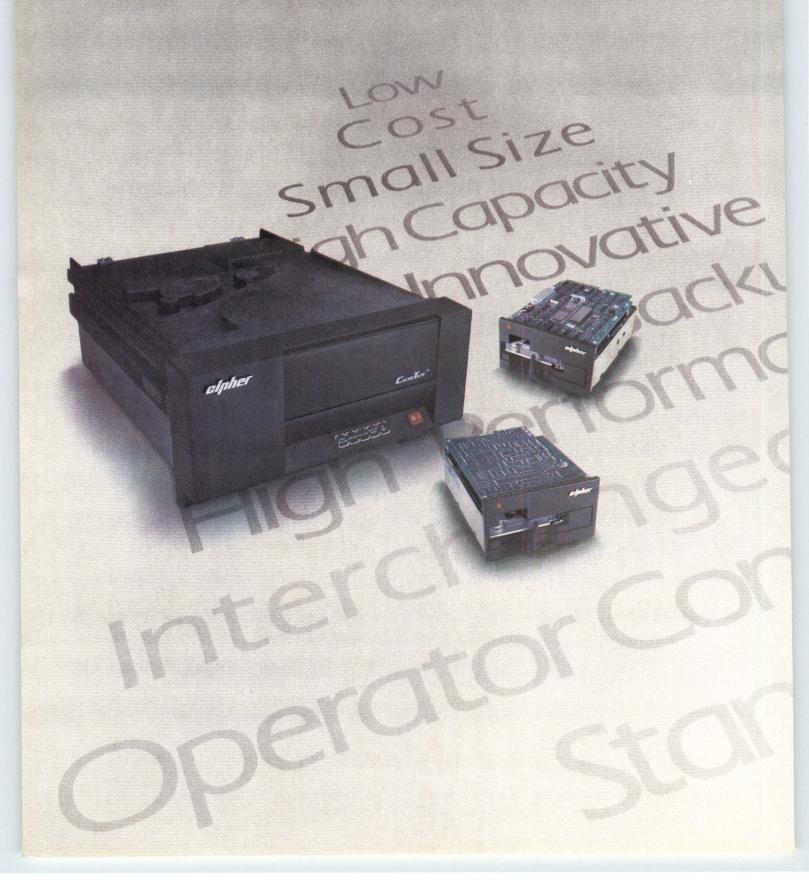

Designing peripherals with exceptional performance is as much an art as a science. We know. We've been doing it since 1962. From the beginning, we've been dedicated to giving you solutions to on-line and back-up storage needs. Example: the Storage Module Drive (SMD) we introduced became the industry standard for removable media disk drives. The SMD is just one of the high-performance products that helped make us the world's leading independent supplier of storage peripherals.

We're still adding star performers to our product family. The LARK with a combined 50 Mbytes of fixed and removable media. The WREN high-performance 5-1/4" winchester drive. The Sentinel 1/4" cartridge streaming tape drive and the RSD that provides 80 Mbytes of removable media in a unit one-half the size of the original SMD.

Today there are more than 35 different products designed to help you meet any storage or back-up requirement, with maximum reliability and low cost of ownership built right in.

There's more—the direct support that Control Data offers.

We can deliver maintenance on everything we make. So wherever your customers are, Control Data peripherals can be counted on for less downtime and more

productivity than unsupported products. Our spare parts programs help ensure that your reputation for excellent service with your customers is backed to the hilt, 24 hours a day,

365 days a year. In the

United States and around the globe.

Add to this the commitment to research, to development and to manufacturing quality that a corporation the size of Control Data contributes, and you're looking at precisely the kind of performance that makes our OEM peripherals top-rated in independent preference studies year after year.

Every performance needs a program. We'll send you one free: our new 48-page OEM products catalog. Write OEM Product Sales, Control Data Corporation, P.O. Box 0, HQN08H, Minneapolis, MN 55440.

**GD** CONTROL DATA

(continued from page 17)

#### Marketing chip sets

I find it necessary to elaborate on a statement made in Joseph Aseo's article, "Processors Divorced from Peripherals with Separate I/O Bus" (Nov 1983, p 64). The statement "NCR Corp also shows an interest in marketing chip sets" is somewhat ambiguous. NCR Corp was one of the earliest promoters of the SCSI standard, as appreciable marketplace advantages would be available with the creation of this SCSI "universal bus with generic commands" standard. In fact, NCR Corp's Microelectronics Div was the first semiconductor manufacturer to bring a commercially available SCSI protocol controller packaged in a 48-pin DIP to the OEM marketplace.

The NCR 5385 SCSI protocol controller, supporting the 1.5-Mbyte/s data transfer rate and arbitration, was first press released in Electronic Design (Apr 1983). Since then, the device has been available directly from NCR's Microelectronics Div Colorado Springs facility, as well as through distribution. As you can see, not only is NCR Corp interested in marketing this standard device, we are actively pursuing it.

Michael B. Burchman NCR Corp Microelectronics Div 1635 Aeroplaza Dr Colorado Springs, CO 80916

#### Forth is core of CATS-1 system

In the report by Nic Mokhoff, entitled "Artificial Intelligence Systems Make Their Mark" (Nov 1983, p 33), Lisp is described as the core language in expert systems. The accompanying photograph identifies the CATS-1 system for locomotive repair as an example of an expert system. The CATS-1 system was programmed in Forth. For references, see the article by Harold E. Johnson and Piero P. Bonissone, "Expert System for Diesel Electric Locomotive Repair," The Journal of Forth Application and Research, vol 1, no. 1, Sept 1983.

Harvey Glass University of South Florida College of Engineering Tampa, FL 33620

The article "Artificial Intelligence Systems Make Their Mark" (Nov 1983, p 33) conveys two misconceptions. First, the expert system used in the CATS-1 system of General Electric was actually implemented in Forth and not Lisp, as the article implies. Nowhere in the article is it mentioned that any environment other than Lisp is suitable for artificial intelligence, whereas in fact many other environments are used. The Japanese, for instance, are scheduled to use Prolog.

Secondly, a consequence of the first misconception is the impression that the best machines for development work in artificial intelligence are optimized for Lisp. Since expert systems are very small when implemented in Forth, and since Forth is implemented on more different machines than any other high level language, there is a good chance that the particular machine already available to the knowledge engineers will probably be cheaper to configure for artificial intelligence (in time and money) than a new dedicated Lisp processor. In fact, Lisp itself has been implemented in Forth, and could still be used if necessary.

Paul Thomas Inner Access Corp PO Box 888 Belmont, CA 94002

#### Updating specifications

As a communicator for Gould CSD, I am constantly working with our development and product planning people to keep abreast of changes in our product line. It is not easy. We work in an industry where specifications and performance figures are constantly being revised upward as a result of enhancements in hardware and software. Therefore, I can understand how difficult it is to keep up with the specifications for multiple vendors when doing a report like "Superminis: Changing Direction for the Future," by Peg Killmon (Nov 1983, p 167). For the record, however, I would like to correct some factual errors in the report.

First, in recent benchmark tests, the Gould Concept 32/87 computer performed 5.6 million Whetstone instructions per second (MIPS). This is a significant improvement over the 4-MIPS level indicated in the report, and was achieved using our new Fortran 77 compiler and Multiply Accelerator.

Also, the report implied that the 4-MIPS performance level was achieved using "dual processing units." This is not true. The 5.6-MIPS performance was achieved by the Concept 32/8750 computer, a single processor. The Concept 8780, which features our unique CPU/IPU combination, is capable of performing 10 MIPS. This represents an 80-percent improvement over a single CPU configuration.

Another part of the report states that the 75-ns cycle time of 100-K ECL logic "doubles or triples the performance potential over Schottky TTL or other ECL families." This is not entirely correct either. The Concept 32/87 computer uses 10-K ECL and it too has a 75-ns cycle time. Furthermore, although 10-K ECL logic is a mature technology, it is still viable and will continue to be so for vears to come.

Joe Barcheski Gould Inc SEL Computer Systems Div 6901 W Sunrise Blvd Fort Lauderdale, FL 33310-9148

#### Speaking out for Forth

I am a user of Forth and as such would like to reply to John D. Stanley's letter about the flaws of the Forth language (Sept 1983). Certainly one cannot deny that Forth is slower than well-written assembly language code. As one who has written many thousand lines of assembly code I would be the first to admit this. But. I don't agree that this represents a weakness of Forth.

The point is that Forth is not assembly language but a higher level language of admirable speed and compactness. Not only is it faster than many other higher level languages, but it also produces more compact code than assembly language for complex programs.

Forth can support user defined interrupt handling. Bryte-Forth is an implementation currently available for the Intel 8031 microcontroller that not only allows interrupt handlers defined in Forth or machine code but also supports runtime reassignment of handlers, systems time/ date, fully buffered interrupt driven serial I/O, user defined error handling, and selfstarting, ROM-resident user applications. What more could a realtime application programmer need?

On the subject of readability, I contend that "unreadable" programs can be (and are) written in any higher level language or assembly language. Readability is influenced most by the ability of the programmer and the experience of the reader. Well-written Forth is very readable because of the ability to build a problemoriented vocabulary of mnemonic words or phrases.

Forth is a fine language. Those just learning should read a good book on the concepts and programming techniques of the Forth language.

Christopher K. Johnson Bryte Computers, Inc PO Box 46 Augusta, ME 04330

October/Fall designer's preference study winner: Duke W. Okes, TRW-Winner of an HP 41CV programmable calculator.

# NS32032

The First True

32-Bit Microprocessor

to Become Reality.

# NS32032

The first commercially available microprocessor to feature:

- 1. Full 32-bit architecture

- 2. Full 32-bit internal implementation3. Full 32-bit data bus to memory

The industry's consensus: with the introduction of the NS32032, the NS16000™ microprocessor family has become the foundation for the next generation of high-performance, low-cost computers.

Any software developed for the 32-bit NS32032 will run just as well on the 16-bit NS16032 or the 8-bit NS08032, and vice-versa. And it will also run on future NS16000 32-bit CPUs. Consider this absolute downward-upward object code compatibility in contrast to the upward-only compatibility of other microprocessor families, which will make their 16-bit processors obsolete when they add 32-bit processors to their product line.

The NS16000 microprocessor family already includes peripherals compatible with its CPUs, and each is in full production: the NS16201 Timing Control Unit (TCU), the NS16202 Interrupt Control Unit (ICU), the NS16081 Floating Point Unit (FPU), and the NS16082 Memory Management Unit (MMU). Since the FPU and MMU interfaces are almost entirely invisible to NS16000 programs, the decision to include or omit floating point or memory management hardware (for cost/performance reasons) will not affect NS16000-based systems' software compatibility.

The billions of bytes of existing mainframe software can now be easily ported to run on NS16000-based systems. The NS16000 family's mainframe-in-silicon architecture (designed specifically to support high level language programming), its full high-speed floating point arithmetic capability, its integral support for Demand Paged Virtual Memory, and the NS32032's 32-bit data bus to memory combine to make this possible for the first time.

Elegance, you see, is everything.

Think about it.

The only limits on NS16000based applications are those of the imagination.

The full 32-bit architecture of the NS32032 (shared by all NS16000-family CPUs) sets no bounds to programmers' productivity or creativity.

No other processor family—micro, mini, or mainframe—has an architecture designed to fully support the use of high level languages, with a structure and behavior corresponding directly to the objects and operations of HLLs.

Its powerful features:

- A compactly encoded, completely symmetrical, two-address instruction set.

- Thirteen addressing modes (many not found in other microprocessors) designed for the kinds of accesses compilers generate.

- Indexing automatically scaled to argument size (1, 2, 4, or 8 bytes), applicable to any addressing mode.

- Instructions to implement high level language constructs such as case statements, loops, and calls, as well as bit-field and string manipulation.

- A fully integrated floating point instruction set, supported by hardware.

The 32-bit architecture of the NS32032 (like that of the other NS16000 CPUs) is fully implemented, without exception or restriction.

Simply stated, physical limitations in processing or packaging technology have not constrained internal implementation. All NS16000 CPUs have a full 32-bit Arithmetic Logic Unit (ALU), a full 32-bit register set, and a full 32-bit internal data bus to the input/output control block.

The value of such elegant implementation? An example: competitive microprocessors take eight to twenty internal steps to execute the expression evaluation "A = A \* X + Ai," commonly used in high-performance technical and scientific applications.

The NS32032 takes four.

The NS32032's full 32-bit data bus to memory increases memory bus bandwidth—and thus the speed at which data can be transferred.

In simple systems (CPU and memory), the NS32032's ability to access a full 32 bits of external data dramatically increases the rate at which instructions and data are processed, while leaving bus time available for system peripherals.

Because it requires less than 50% of the available bus bandwidth in standard applications, the NS32032 is also ideally suited to complex *multi*-processor systems, DMA transfers, and high-speed graphics.

In the NS16000 family of CPUs, the primary feature that distinguishes one processor from another is the width of the data bus to memory.

The fact that the NS08032 and the NS16032, with their 8-bit and 16-bit data buses, share identical 32-bit architecture and 32-bit implementation with the NS32032 means that it is now possible to develop 8- and 16-bit systems with all the benefits of 32-bit software performance. The same software can now be implemented on all the systems within a product family; an enormous benefit to programmers and systems designers.

Future 32-bit CPUs planned for the NS16000 family will feature improved performance—bettering the NS32032's 1 MIPS tenfold by 1988—yet these future CPUs will also be compatible. This clear migration path guarantees the preservation of your initial software investment while providing for significant enhancement in your product line.

No other family of microprocessors shows such forethought or foresight.

TYPICAL EXECUTION TIMES (in µs at 10MHz)

|             |          | Register-to<br>Register       | Memory-to-Memory |         |         |

|-------------|----------|-------------------------------|------------------|---------|---------|

| Instruction |          | NS08032<br>NS16032<br>NS32032 | NS08032          | NS16032 | NS32032 |

| Mov         | Byte     | 0.3                           | 1.7              | 1.7     | 1.7     |

|             | Word     | 0.3                           | 2.5              | 1.7     | 1.7     |

|             | Dbl.word | 0.3                           | 4.2              | 2.6     | 1.7     |

| Add         | Byte     | 0.4                           | 2.0              | 2.0     | 2.0     |

|             | Word     | 0.4                           | 3.2              | 2.0     | 2.0     |

|             | Dbl.word | 0.4                           | 4.7              | 2.3     | 2.0     |

| Mul         | Byte     | 3.8                           | 4.3              | 4.3     | 4.3     |

|             | Word     | 5.4                           | 7.0              | 5.8     | 5.8     |

|             | Dbl.word | 8.6                           | 12.0             | 9.6     | 8.4     |

Additional reasons why the NS16000 family now leads in microprocessor design-wins:

1. Hardware development can begin immediately. All three CPUs are available right now. So are all the necessary peripherals in the family.

2. Software development can begin immediately. Appropriate evaluation tools, and both resident- and cross-support packages, are available now, as is an extensive list of third-party software.

Our SYS16™—a multi-user, multitasking development system—incorporates the *complete* family of NS16000 chips (CPU, TCU, ICU, FPU, and MMU), and therefore gives up to eight programmers a true, native environment to work in.

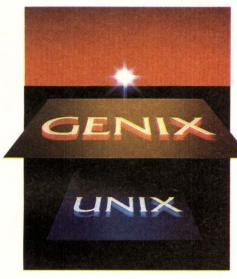

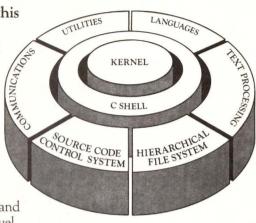

GENIX,™ a product of our software engineering group, is the first microprocessor operating system capable of implementing Demand Paged Virtual Memory.

The NS16000 microprocessor family.

Adapted from the Berkeley 4.1 bsd version of UNIX, it has been elegantly tailored to optimize the NS16000 architecture. (We also offer source code under license for GENIX and its utilities.) Together, the SYS16 and GENIX demonstrate that the NS16000 microprocessor family makes the best "UNIX engine" on the market today.

For customers with VAX-11™ systems under UNIX, our GCS™ (GENIX Cross Software) contains the C compiler and other NS16000 tools from the SYS16. For VAX-11 systems running the VMS™ operating system, our NSX-16™ cross software provides full NS16000 family support.

To help complete your development cycle simply and quickly, all of our development tools provide support for our easy-to-work-with ISE/16.™ An elegant development tool in its own right, the ISE/16 allows real-time evaluation of the NS16000 chips, for testing and debugging hardware and software in your own hardware environment, and requires no target-system modification.

3. Every resource imaginable to help you get your NS16000-based application to market first is available now. We are totally committed—with in-house hardware, software, and systems expertise; with service, documentation, and customer training. We are backing the NS16000 microprocessor family to a degree unparalleled in the history of the semiconductor industry.

But then, there has never been anything like the NS16000 microprocessor family before.

VAX and VMS are trademarks of Digital Equipment Corporation UNIX is a trademark of Bell Laboratories. NS16000, SYS16, GENIX, GCS, NSX/16, and ISE/16 are trademarks of National Semiconductor Corporation.

# NS16000 Elegance is everything.

# See it.

The NS16000 microprocessor family will be on exhibition at *Uniforum* and *Electro*.

# Talk with us.

Please call the National Sales Representative nearest you for more information, and the answers to your questions. Ask to meet with one of our Field Applications Engineers, too. Or, circle the number below.

# Read about it.

For more information, please request a copy of NS16000: The Specifics of 32-Bit Architecture. And for practical experience, ask for a copy of NS16000 Training, detailed information on available courses.

NS16000: The Specifics of 32-Bit Architecture

# manipulations in seconds, not hours.

With Mini-MAP...The Array Processor For The Graphics OEM

Courtesy of Al Barr, Raster Technologies, Inc.

For tough image processing problems like pixel rotation, image reconstruction, or hidden line removal from wire frame models, Mini-MAP gets results in seconds, not hours. Attach a Mini-MAP to a PDP-11 or VAX UNIBUS and you have an interactive number cruncher that is ideal for image processing, CAD/CAM, solid modeling, medical imaging, and animation.

Shared memory simplifies programming and provides the unprecedented throughput necessary for truly interactive image processing of complex algorithms. 32-bit DEC floating point arithmetic, along with 7 MFLOPS of number crunching power, ensures that accurate results are available quickly.

A scientific subroutine library of over 225 **FORTRAN** callable routines

including an expanding selection of image processing algorithms

is available for Mini-MAP. For optimum performance, high-level FORTRAN control languages are provided for both the host and Mini-MAP.

Memory is expandable up to 16 MBytes. Configurations include a four-board set with DEC-type backplane or fully packaged systems.

System integrators are finding Mini-MAP is the most cost-effective number crunching solution for image manipulation. Write for information or call toll free 1 800 325-3110 for fast action.

- 32-bit floating point precision

- Compiler/Assembler/Linker/Debugger

- 225 FORTRAN callable arithmetic routines

- Up to 16 MBytes of memory

- 1024 x 1024 2-D real FFT in 8.8 seconds

- 1280 x 1024 4-color image rotation (Raster Scan Storage Format) in 27.5 seconds.

DEC, PDP-11, VAX, and UNIBUS are trademarks of Digital Equipment Corp. Mini-MAP is a trademark of CSPI

# Thirty-two bit system designers face decision time

Computer system designers and system integrators producing leading edge equipment in the next five years will often opt for powerful 32-bit microprocessors, or 32-bit microprocessor-based boards and systems. They must hook these chips, boards, and boxes together with a 32-bit bus if they want to take full advantage of 32-bit machine functionality.

Designers can choose an open system bus, whose specifiers will cooperate with other firms to generate industry support in the form of interface, driver, and other chips needed to run a bus. Third-party firms will also produce single- and multi-board computers, software, memory, peripheral driver boards, and the like, for open buses.

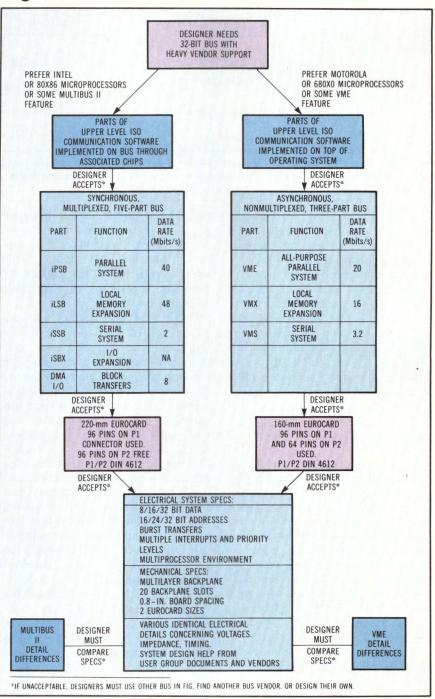

Today, there are two major open bus choices—the Multibus II from Intel (Hillsboro, Ore) and the Versa Module Europa (VME) bus from the Motorola (Phoenix, Ariz), Signetics (Sunnyvale, Calif), Mostek (Carrollton, Tex) troika. In addition, there is the NuBus from Texas Instruments (Dallas, Tex), a 32-bit bus from Digital Equipment Corp (Maynard, Mass) and a 32-bit bus standard from the IEEE.

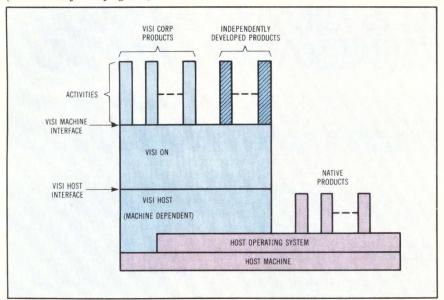

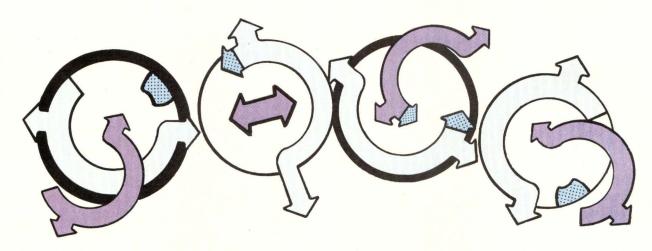

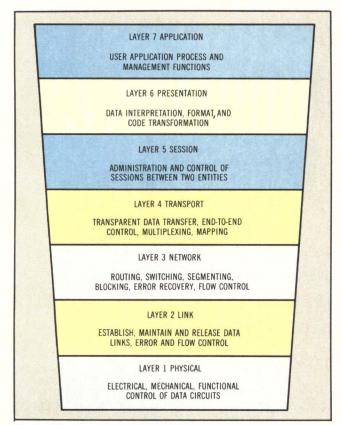

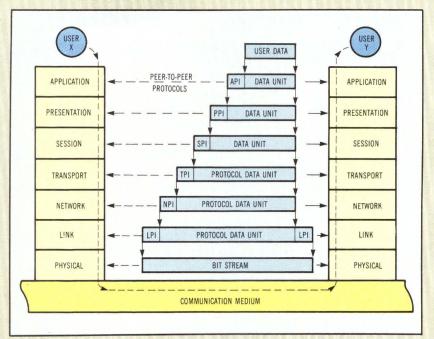

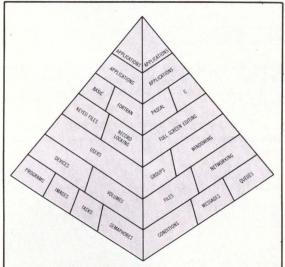

To help make an intelligent decision as to which bus to choose for a computer system's lifetime, designers should be cognizant of major and minor differences between the buses. It is equally important to be aware of how they evolved into their present form, and what they can be expected to offer from both the technical and marketing points of view. Finally, designers understand that a bus is really a local network in a small geographical area. As such, like any local network, it can be designed much like an implementation of the International Standards Organization (ISO) seven-layer model for computer communications—the Open Systems Interconnection (OSI) model.

Significantly, the Multibus II specification addresses how to implement not only the usual layers 1 and 2 of this model (the physical and

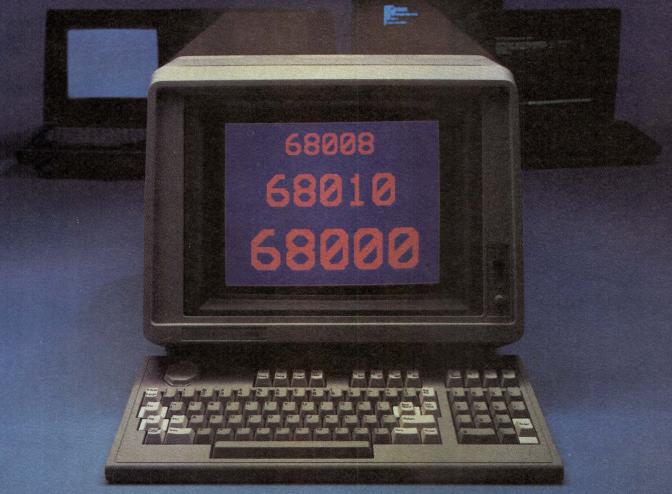

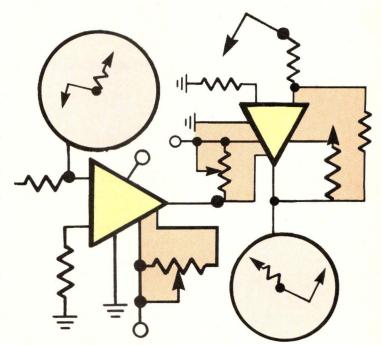

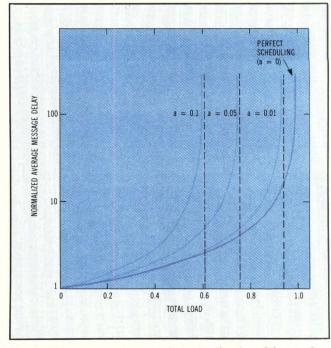

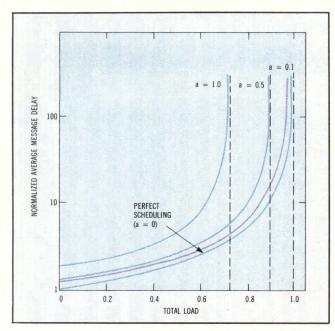

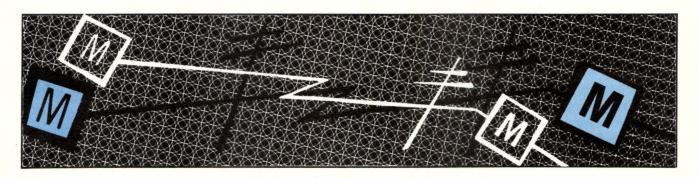

Fig 1 Computer system designers who must choose between Multibus II and VMEbus can help their engineering intuition with the data shown. If the data is not enough to reach a decision, a detailed analysis of the bus specifications is necessary.

data link layers), but also parts of the higher, software-based layers. In contrast, the VMEbus confines itself to implementing the first two layers in the bus with the higher layers taken care of by microprocessor operating system software. Of (continued on page 28)

## Designers face decision time (continued from page 27)

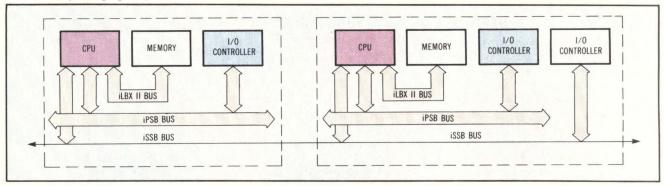

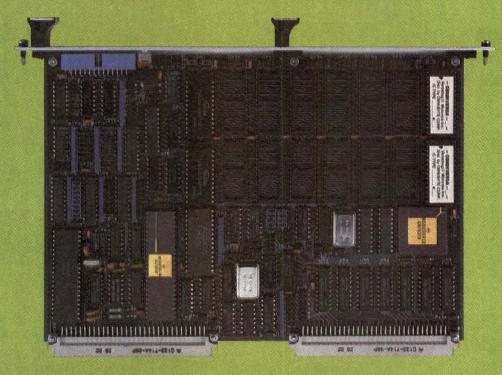

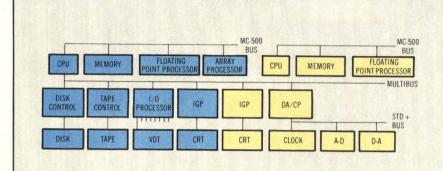

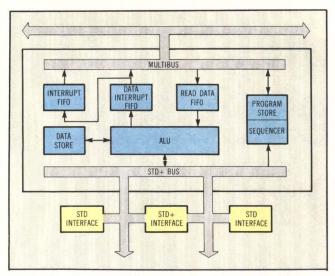

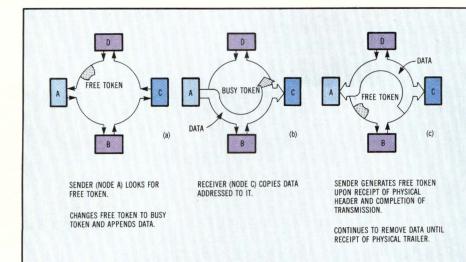

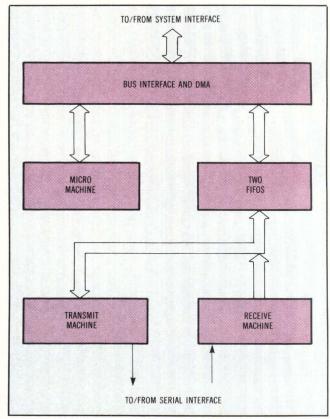

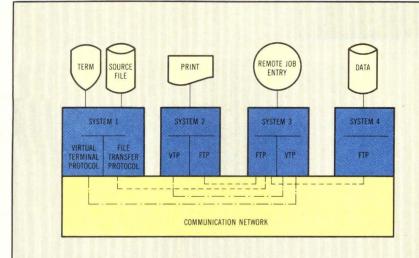

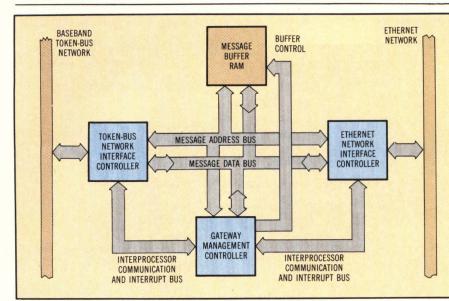

Fig 2 The five different buses designed by Intel to form Multibus II can be configured in various ways. They include a parallel system bus, a local memory bus, a serial bus for message passing, and two buses adapted from Multibus I. These I/O buses handle DMA and I/O expansion.

course, the different approaches have advantages and disadvantages.

Multibus II, (riding on the bustails of the successful Multibus I for 8- and 16-bit processors), and the VMEbus are the main contenders for new 32-bit products. Their specifications have been published, and their backers and advocates are making a major marketing effort. Given the 8- and 16-bit history of these buses, industry support is likely to follow.

Both the Multibus II and the VMEbus have made their start toward implementation and the development of complementary products. VME has had a head start and has been specified as a 32-bit bus since 1981. For example, members of its backing troika have announced sample availability for certain bus chips. Vendors making VME-based, 32-bit boards have also been able to make prototypes for some time with 16-bit processors.

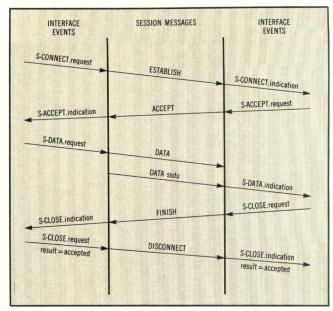

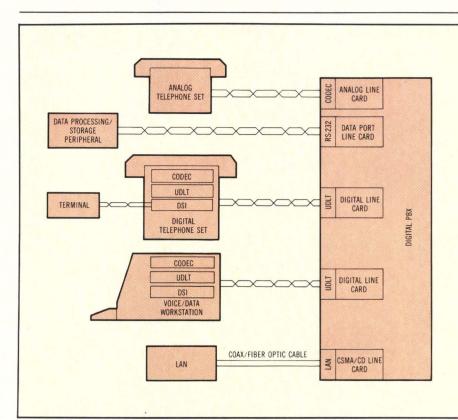

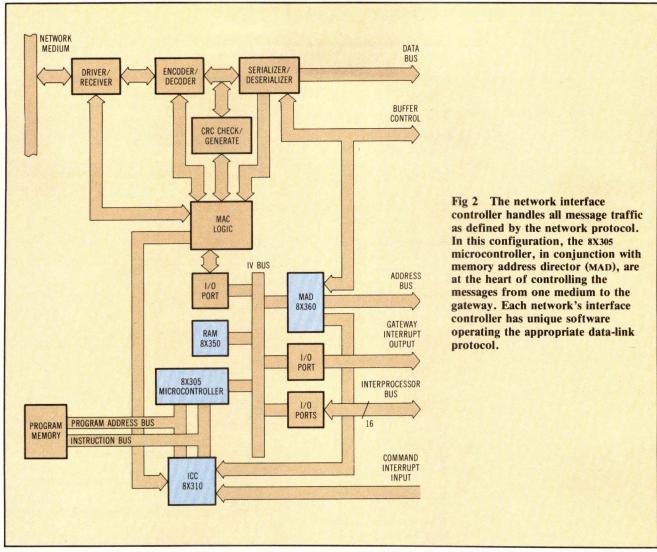

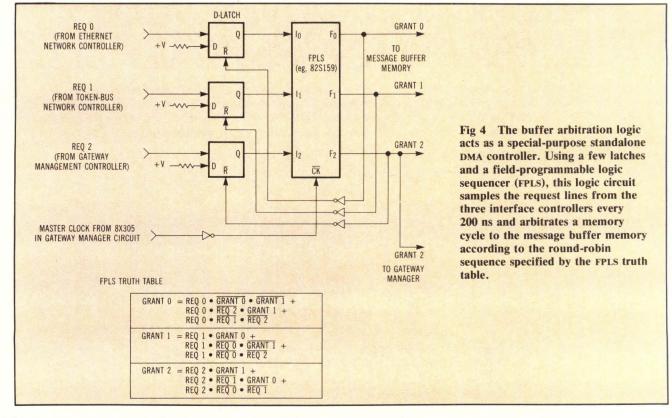

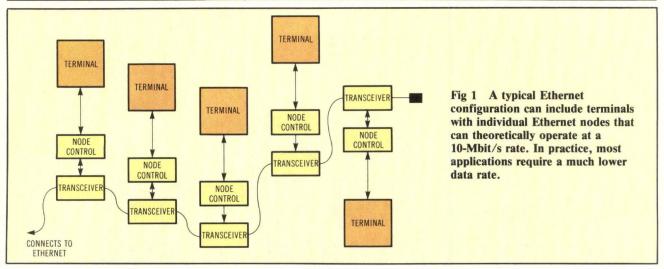

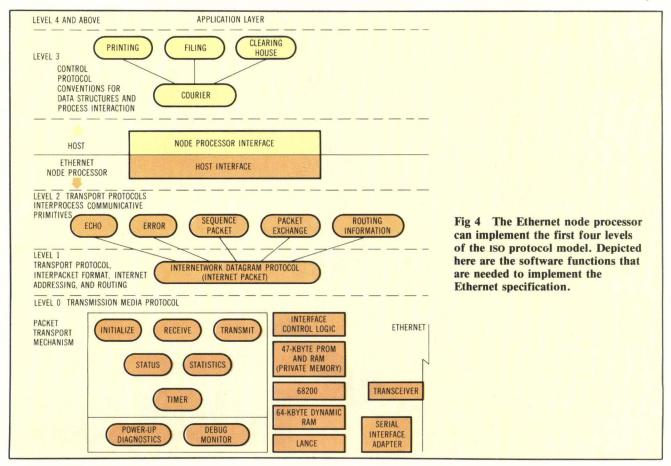

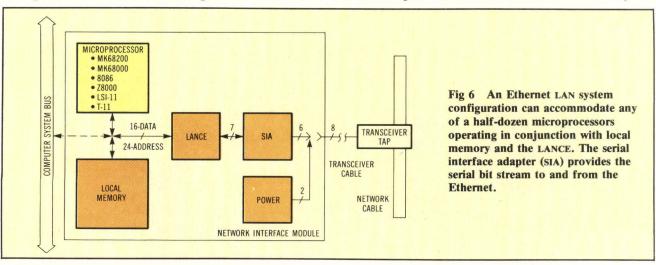

The Multibus II enjoys the support of Hewlett-Packard (Palo Alto, Calif) Siemens (West Germany) Tektronix (Beaverton, Ore) and Advanced Micro Devices (Sunnyvale, Calif) as well as a host of other companies. For its part, VME has been blessed by Philips Gloeilampenfabrieken in The Netherlands (Signetics' parent firm), France's Thompson-CSF, and its own list of major and minor companies.