Catalog No. 1809550-03 Issued: November 1983

## ADO AMPEX DIGITAL OPTICS

SERVICE MANUAL

AMPEX CORPORATION AUDIO-VIDEO SYSTEMS DIVISION

### Prepared by

AVSD Technical Publications Ampex Corporation 401 Broadway Redwood City, California 94063

Copyright 1983 by Ampex Corporation Catalog No. 1809550-03 Issued: November 1983

### TABLE OF CONTENTS

### PARAGRAPH NO.

### TITLE

### PAGE NO.

### SECTION 1 GENERAL INFORMATION

| 1-1  | Scope of Manual                    | 1-1 |

|------|------------------------------------|-----|

| 1-2  | Related Publications               | 1-1 |

| 1-3  | Intended Use and Capabilities      | 1-1 |

| 1-4  | Functional Description             | 1-2 |

| 1-5  | Physical Description               | 1-3 |

| 1-6  | Control Unit                       | 1-3 |

| 1-7  | Signal System Chassis              | 1-3 |

| 1-8  | Software                           | 1-4 |

| 1-9  | Options, Accessories, and Supplies | 1-4 |

| 1-10 | Specifications                     | 1-4 |

### SECTION 2 INSTALLATION

| 2-1 | Unpacking                           | 2-1 |

|-----|-------------------------------------|-----|

| 2-2 | Location and Mounting               | 2-1 |

| 2-3 | Signal System Chassis Rack Mounting | 2-1 |

| 2-4 | Power and Signal Connections        | 2-5 |

### SECTION 3 OPERATION

| 3-1 | Introduction                  | 3-1 |

|-----|-------------------------------|-----|

| 3-2 | Controls and Indicators       | 3-1 |

| 3-3 | Starting the System           | 3-5 |

| 3-4 | Diskette Handling and Storage | 3-5 |

| 3-5 | Menu Monitor Display          | 3-5 |

### SECTION 4 MAINTENANCE

| 4-1  | Introduction                  | 4-1 |

|------|-------------------------------|-----|

| 4-2  | Test Equipment                | 4-1 |

| 4-3  | Circuit Breakers and Fuses    | 4-1 |

| 4-4  | Access and Disassembly        | 4-3 |

| 4-5  | Analog Section Electronics    | 4-3 |

| 4-6  | Analog Section PWAs           | 4-3 |

| 4-7  | Analog Section Fans           | 4-4 |

| 4-8  | Analog Section Power Supplies | 4-6 |

| 4-9  | Digital Section Electronics   | 4-6 |

| 4-10 | Digital Section PWAs          | 4-6 |

### TABLE OF CONTENTS (Continued)

### PARAGRAPH NO.

### TITLE

PAGE NO.

### SECTION 4 MAINTENANCE (Continued)

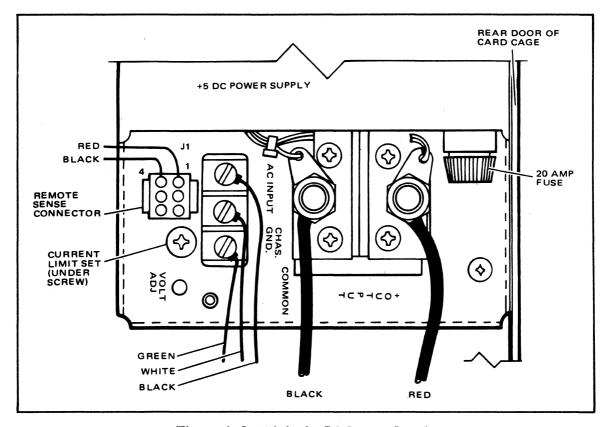

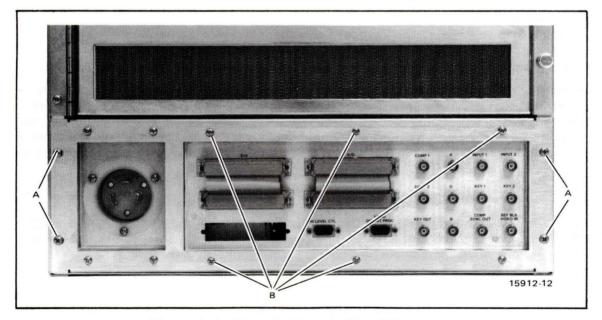

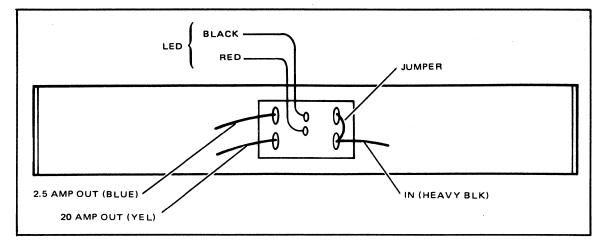

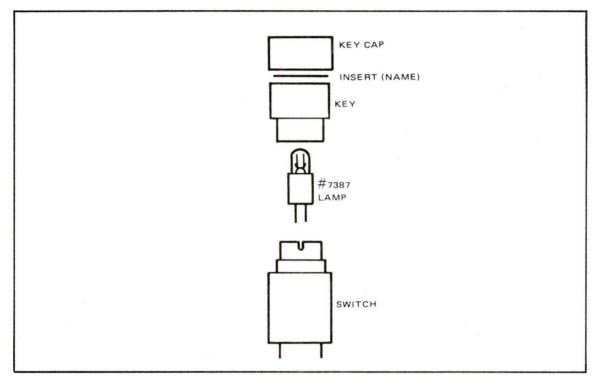

| Digital Section Electronics (Continued)4-11Digital Section Fans.4-64-12Digital Section +5V Power Supply4-104-13Rear Connector Panel Removal4-114-14Circuit Breaker Panel4-124-15Control Unit4-124-16Lamp Replacement4-124-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-174-24Power Distribution4-17                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-12Digital Section +5V Power Supply4-104-13Rear Connector Panel Removal4-114-14Circuit Breaker Panel4-124-15Control Unit4-124-16Lamp Replacement4-124-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                  |

| 4-13Rear Connector Panel Removal4-114-14Circuit Breaker Panel4-124-15Control Unit4-124-16Lamp Replacement4-124-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                          |

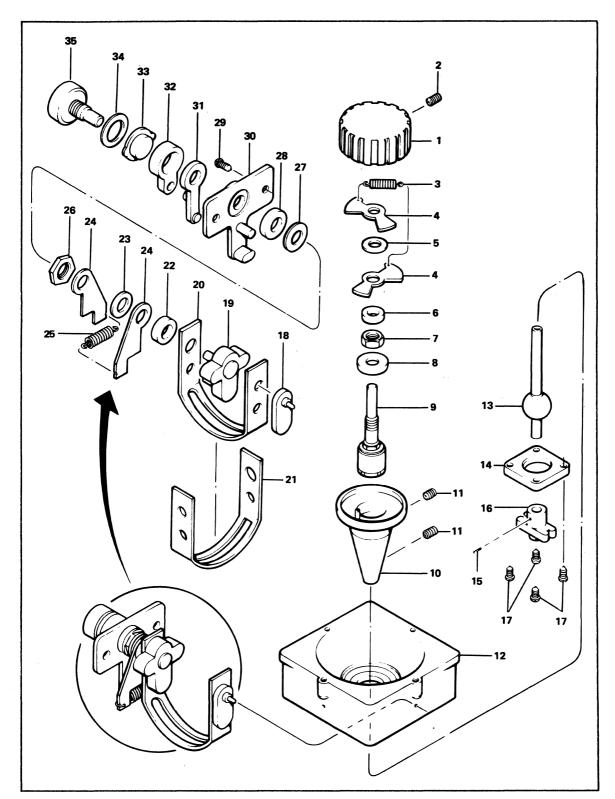

| 4-14       Circuit Breaker Panel       4-12         4-15       Control Unit       4-12         4-16       Lamp Replacement       4-12         4-17       Keyboard Disassembly       4-12         4-18       Joystick Disassembly       4-12         4-19       Menu Monitor Disassembly       4-16         4-20       Menu Monitor CRT Removal       4-16         4-21       Disk Drive Removal       4-17         4-22       Menu Monitor Power Supply Removal       4-17         4-23       Chassis Assembly Removal       4-17 |

| 4-15Control Unit4-124-16Lamp Replacement4-124-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                           |

| 4-16Lamp Replacement4-124-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                               |

| 4-17Keyboard Disassembly4-124-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                                                       |

| 4-18Joystick Disassembly4-144-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                                                                                   |

| 4-19Menu Monitor Disassembly4-164-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                                                                                                               |

| 4-20Menu Monitor CRT Removal4-164-21Disk Drive Removal4-174-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                                                                                                                                               |

| 4-21Disk Drive Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4-22Menu Monitor Power Supply Removal4-174-23Chassis Assembly Removal4-17                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4-23 Chassis Assembly Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4-25 Electrical Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4-26 Analog Section Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4-27 Comb Filter PWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4-28 Input Reference PWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

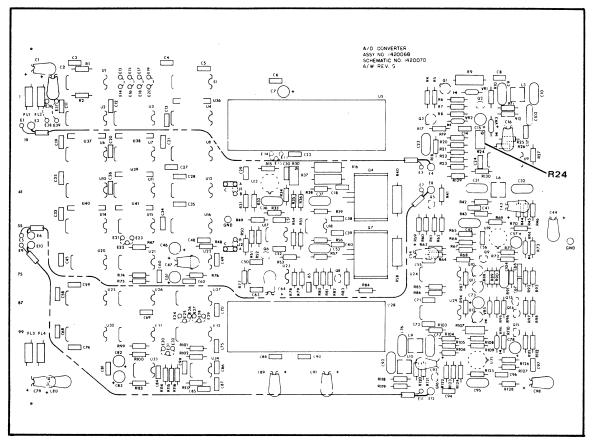

| 4-29 A/D Converter PWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

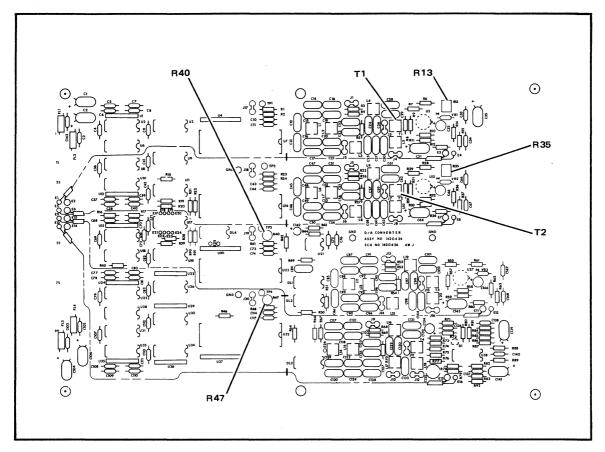

| 4-30 D/A Converter PWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4-31 Video Output Processor PWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4-32 Digital Section Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4-33 Output Control Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4-34 HLC Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-35 LLC Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

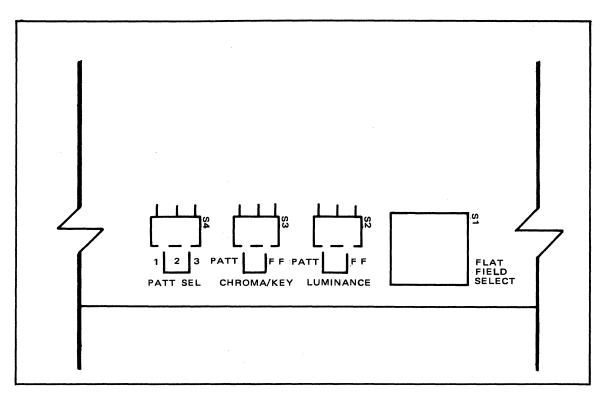

| 4-36 Digital Test Signal Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4-37 Required Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4-38 Controls and Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4-39 Pattern Select Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4-40 Flat Field Select Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4-41 Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

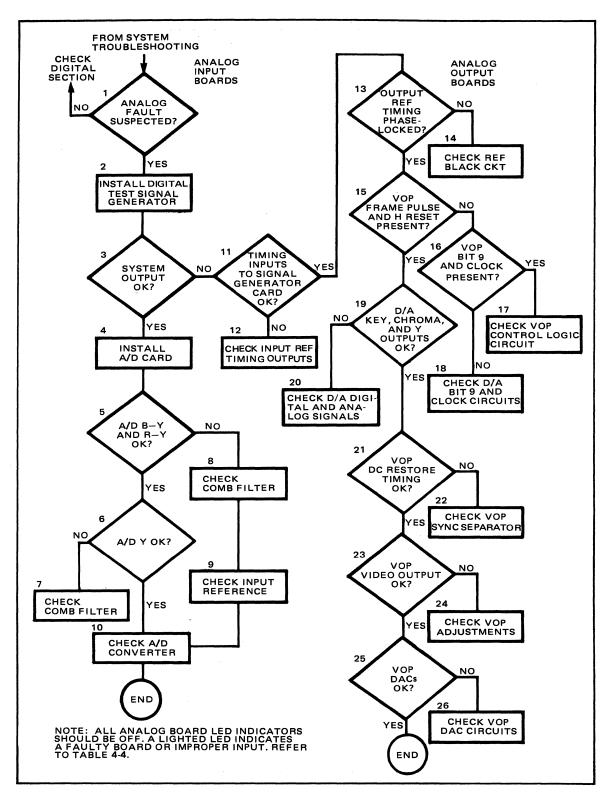

| 4-42 Analog Section Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

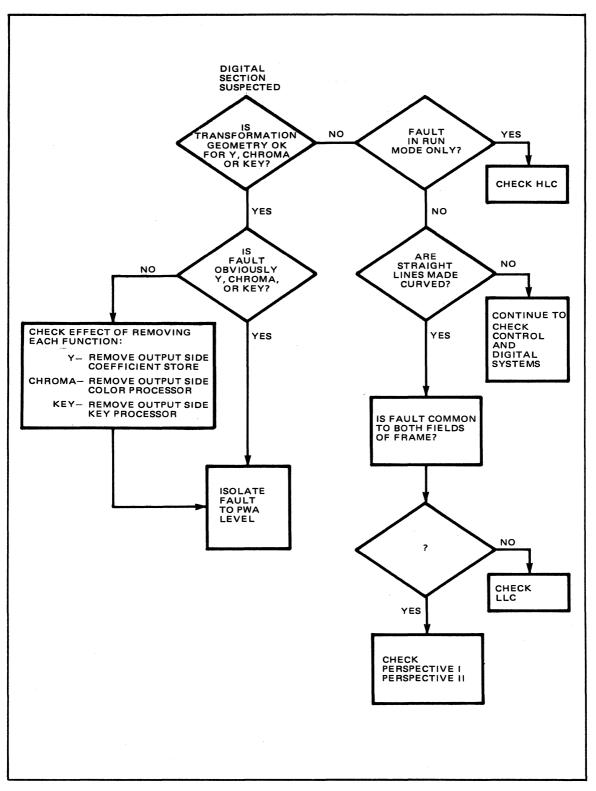

| 4-43 Digital Section Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4-44 Digital Troubleshooting Flowchart 4-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4-45 Fault Isolation Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4-46 Luminance Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-47 Miscellaneous Fault Indications 4-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### TABLE OF CONTENTS (Continued)

### PARAGRAPH

NO.

### TITLE

PAGE NO.

### SECTION 5 THEORY OF OPERATION

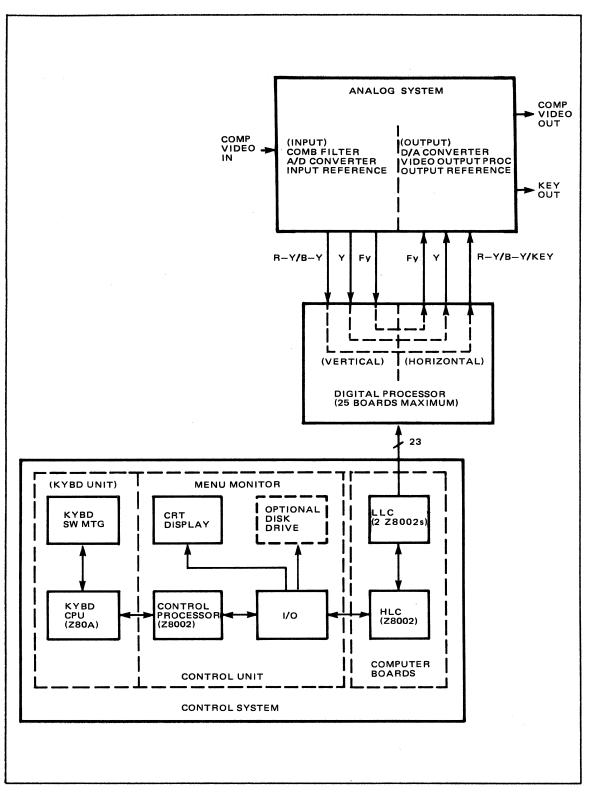

| 5-1  | Introduction                        | 5-1  |

|------|-------------------------------------|------|

| 5-2  | System                              | 5-1  |

| 5-3  | Subsystem Functional Description    | 5-1  |

| 5-4  | Control System                      | 5-1  |

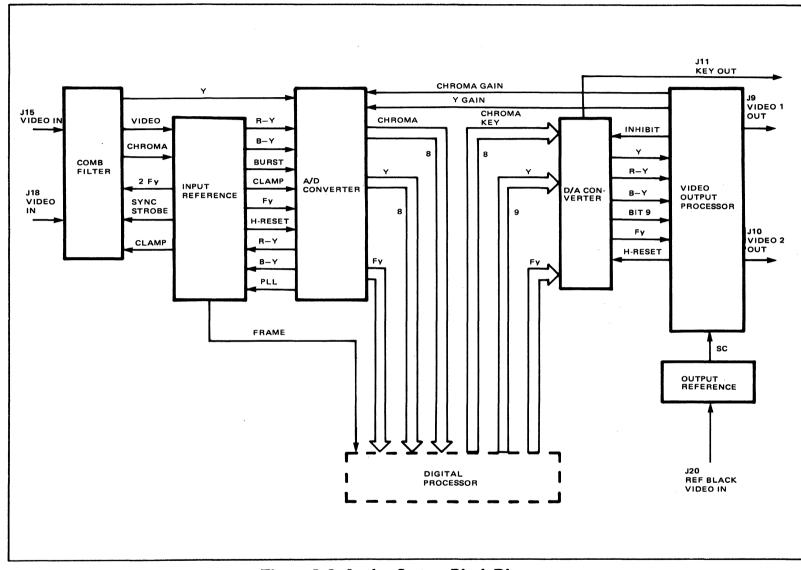

| 5-5  | Analog System                       | 5-3  |

| 5-6  | Digital Processor                   | 5-5  |

| 5-7  | Analog System PWAs                  | 5-5  |

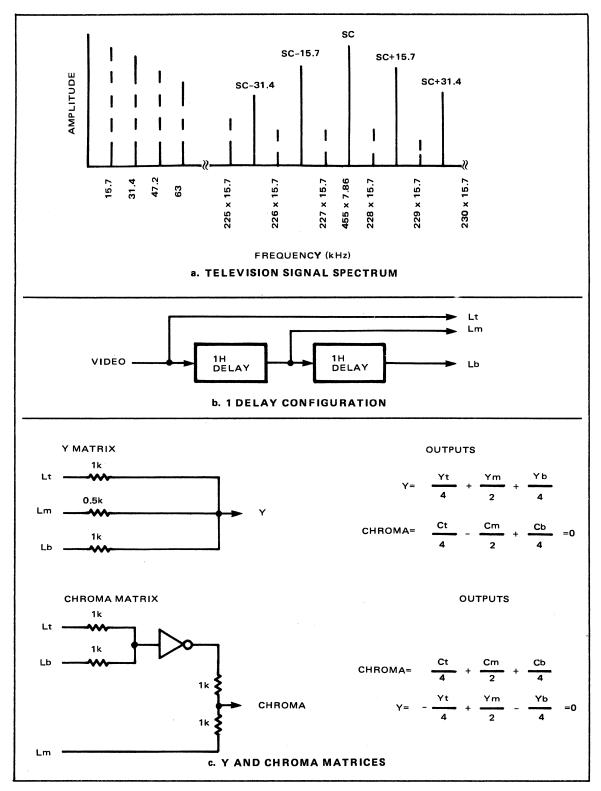

| 5-8  | Comb Filter                         | 5-5  |

| 5-9  | Comb Filter Theory                  | 5-5  |

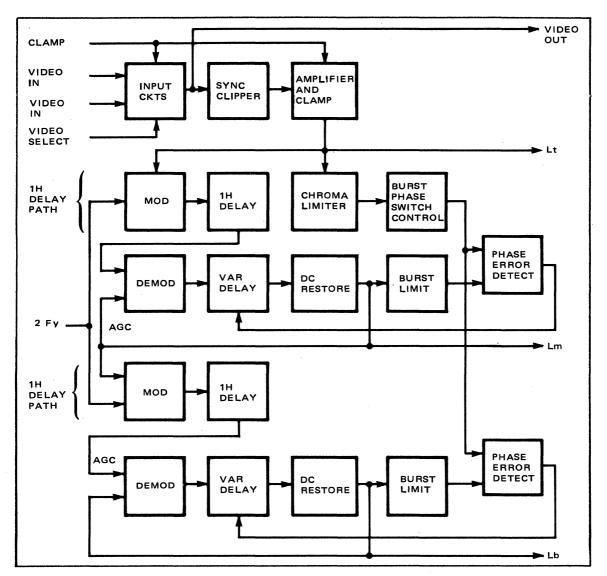

| 5-10 | Input Processing and 1H Delay Paths | 5-6  |

| 5-11 | Input Processing Circuits.          | 5-6  |

| 5-12 | 1H Delay Path                       | 5-9  |

| 5-13 | Y & Chroma Matrices                 | 5-10 |

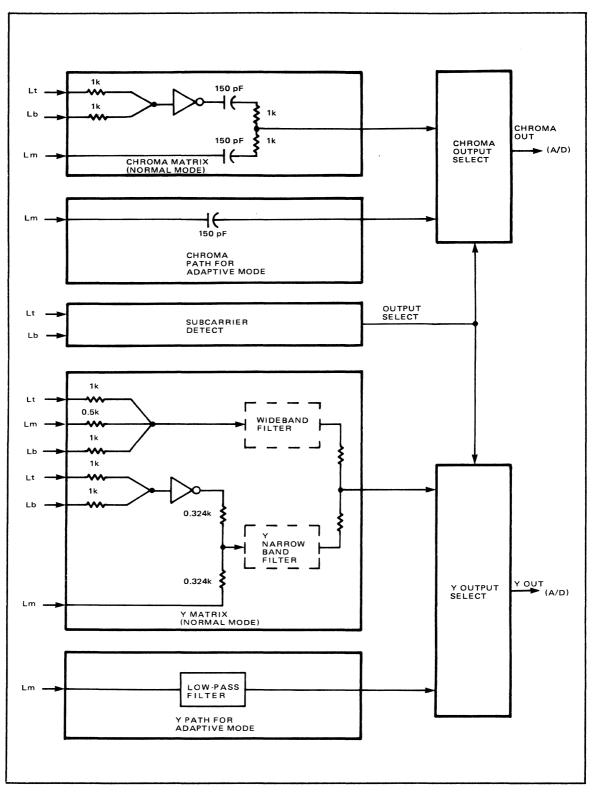

| 5-14 | Y Matrix                            | 5-10 |

| 5-15 | Chroma Matrix                       | 5-12 |

| 5-16 | Subcarrier Detector                 | 5-12 |

| 5-17 | Adaptive Mode Circuits              | 5-13 |

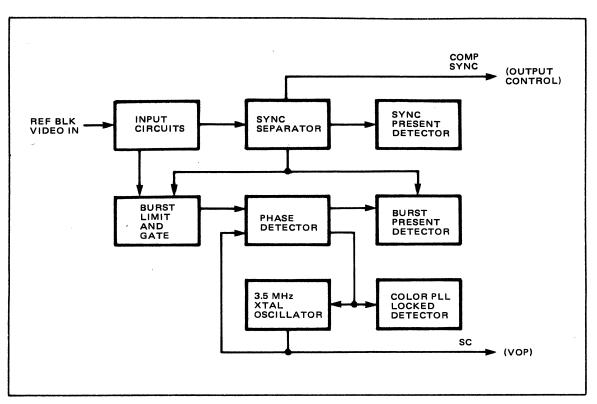

| 5-18 | Input Reference                     | 5-13 |

| 5-19 | Video Timing Signals                | 5-13 |

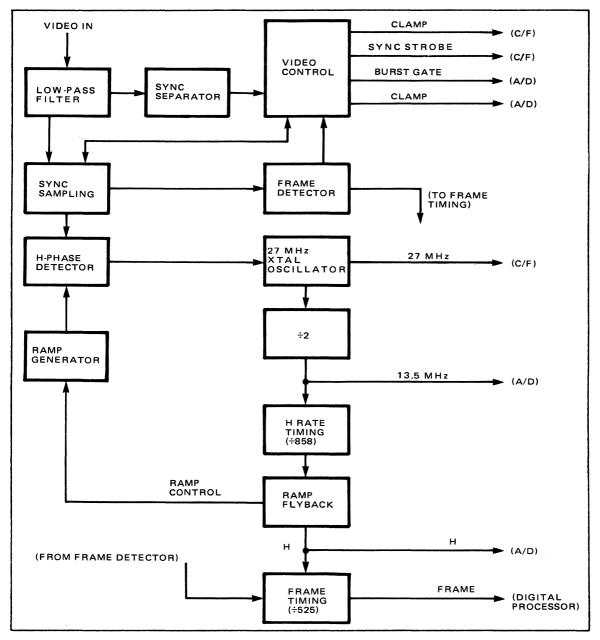

| 5-20 | Video Control                       | 5-13 |

| 5-21 | Sync Sampling                       | 5-14 |

| 5-22 | Frame Detector                      | 5-15 |

| 5-23 | H Phase Detector                    | 5-15 |

| 5-24 | 27 MHz Oscillator                   | 5-15 |

| 5-25 | H Rate Timing                       | 5-16 |

| 5-26 | Ramp Flyback                        | 5-16 |

| 5-27 | Ramp Generator                      | 5-16 |

| 5-28 | Frame Timing                        | 5-16 |

| 5-29 | Demodulation                        | 5-16 |

| 5-30 | Burst Limit and Gate                | 5-17 |

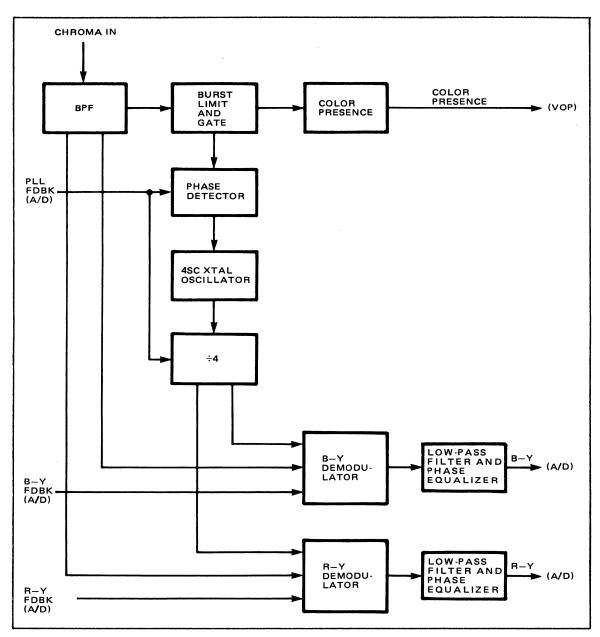

| 5-31 | Color Presence                      | 5-18 |

| 5-32 | Phase Detector                      | 5-18 |

| 5-33 | ASC Crystal Oscillator              | 5-18 |

| 5-34 | B-Y Demodulator/LPF/Phase Equalizer | 5-18 |

| 5-35 | R-Y Demodulator/LPF/Phase Equalizer | 5-18 |

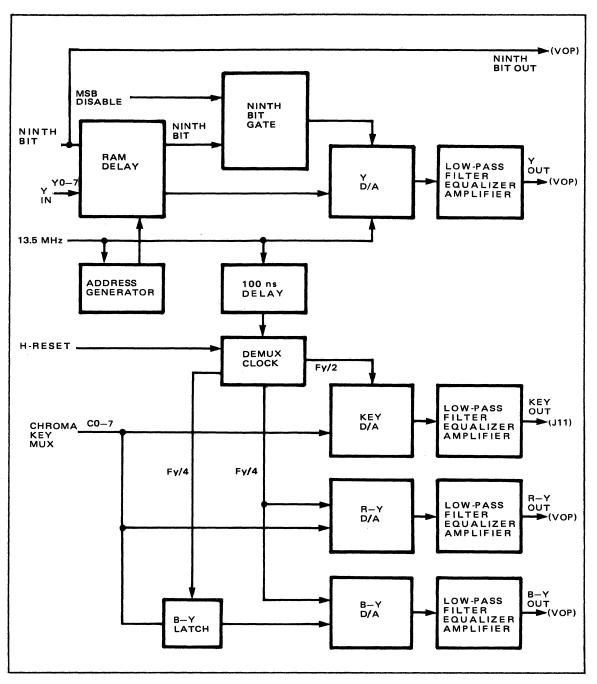

| 5-36 | A/D Converter                       | 5-18 |

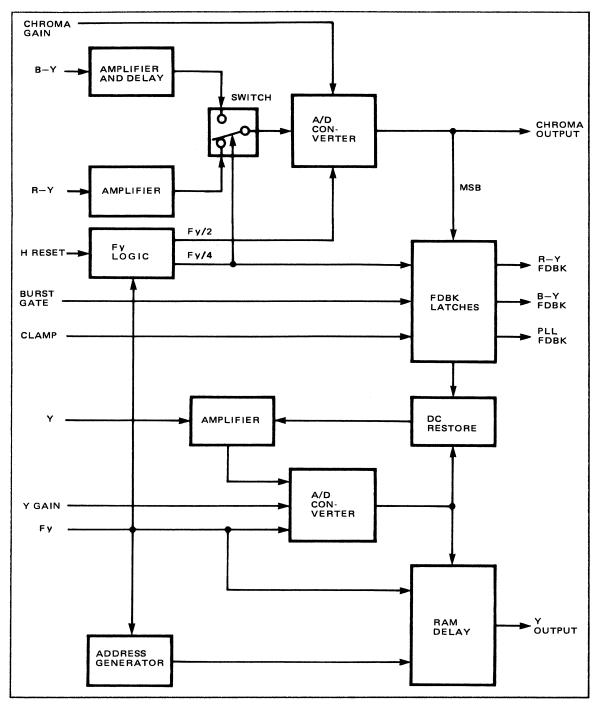

| 5-37 | Chroma Path                         | 5-20 |

| 5-38 | Fy Logic and Feedback Latches       | 5-20 |

| 5-39 | Y Path                              | 5-20 |

| 5-40 | DC Restore                          | 5-21 |

### TABLE OF CONTENTS (Continued)

#### PARAGRAPH NO.

### TITLE

PAGE NO.

#### SECTION 5 THEORY OF OPERATION (Continued)

Analog Systems PWAs 5-41 5-21 5-42 5-21 5-43 5-23 5-44 5-23 5-45 5-24 5-46 5-25 5-47 5-25 5-48 5-25 5-49 5-25 5-50 Digital Circuits. 5-25 5-51 5-27 5-52 5-28 5-53 5-28 5-54 5-28 Keyboard Switch Mounting . . . . . . . . . . 5-55 5-28 5-56 5-30 5-57 Menu Monitor 5-30 5-58 5-31 5-59 Menu Monitor Control Processor (CPP). . . . 5-31 5-60 Menu Monitor Input/Output (I/O) . . . . . . . 5-34 5-61 5-35 5-62 Computer PWA Functions . . . . . . . . . . . 5-36 5-63 5-36 5-64 5-38

### APPENDIX A VENDOR MANUALS AND ADDRESSES

### APPENDIX B KRAFT JOYSTICK ASSEMBLY

### APPENDIX C LUMINANCE CONVERSIONS

### LIST OF ILLUSTRATIONS

| FIGURE<br>NO.                                                                                | TITLE                                                                                                                                                                                                                                                                                       |                                                                                              |  |  |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

| 1-1<br>1-2                                                                                   | ADO Simplified Functional Diagram                                                                                                                                                                                                                                                           | 1-2<br>1-3                                                                                   |  |  |  |

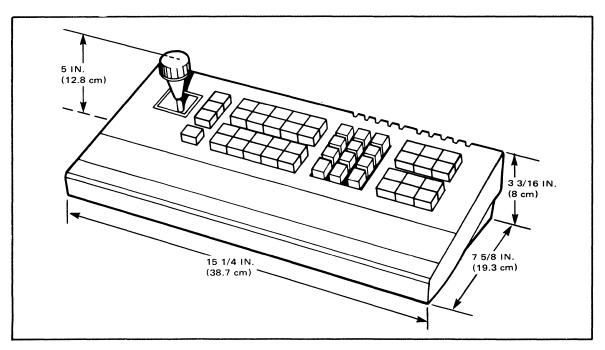

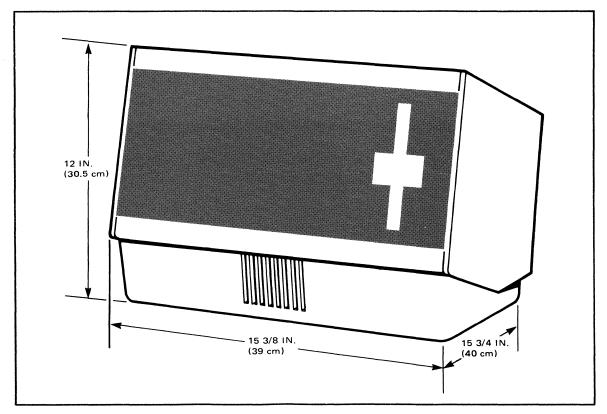

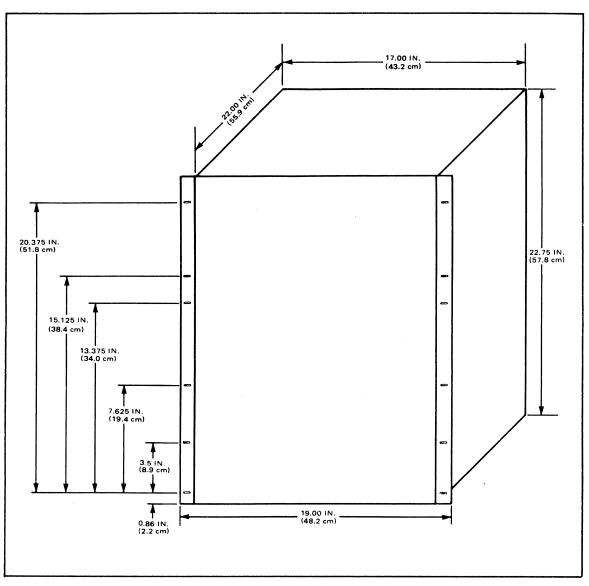

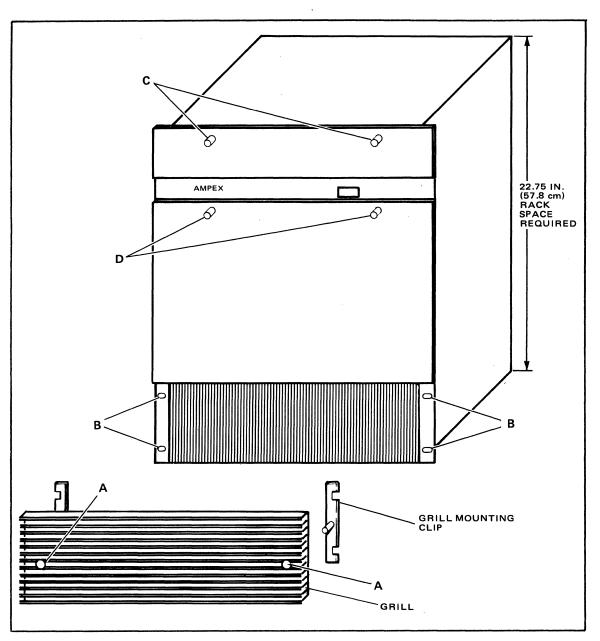

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6                                                       | Keyboard Unit DimensionsMenu Monitor DimensionsSignal System Chassis DimensionsSignal System ChassisADO System Basic InterconnectionHi Level Control to Channel 5 Cable                                                                                                                     | 2-2<br>2-2<br>2-3<br>2-4<br>2-9<br>2-10                                                      |  |  |  |

| 3-1<br>3-2<br>3-3<br>3-4                                                                     | Keyboard Controls                                                                                                                                                                                                                                                                           | 3-1<br>3-6<br>3-7<br>3-8                                                                     |  |  |  |

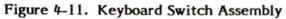

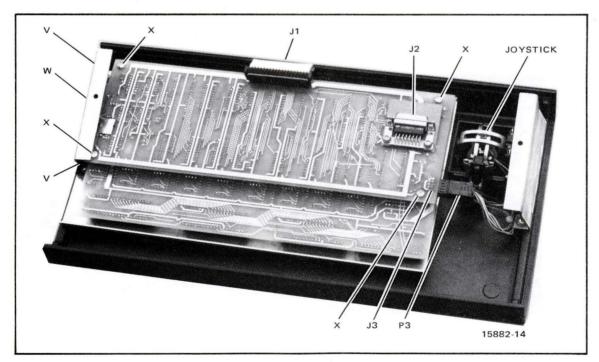

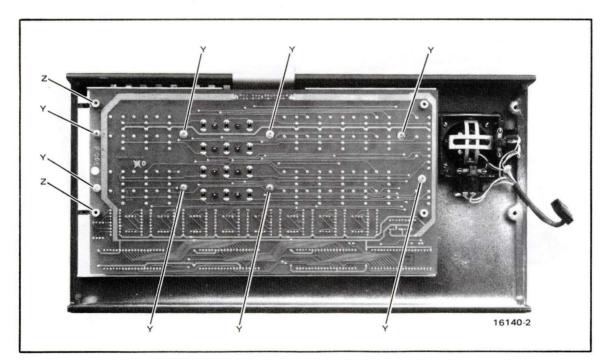

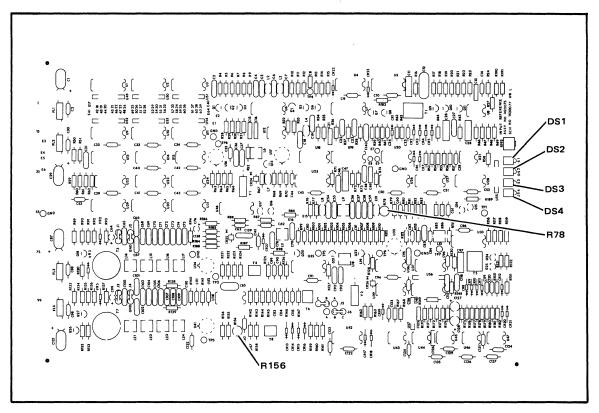

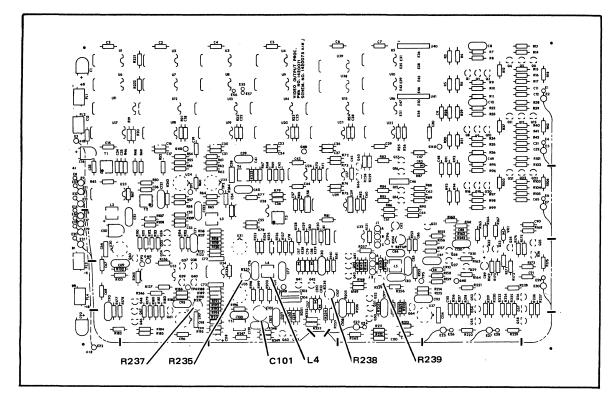

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12          | Circuit Breaker and Fuse Locations                                                                                                                                                                                                                                                          | 4-2<br>4-3<br>4-4<br>4-5<br>4-5<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-13        |  |  |  |

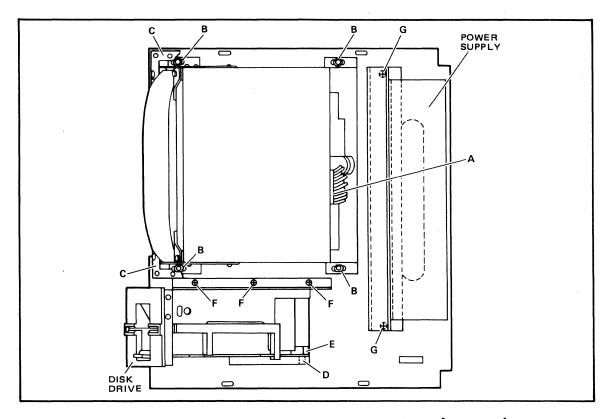

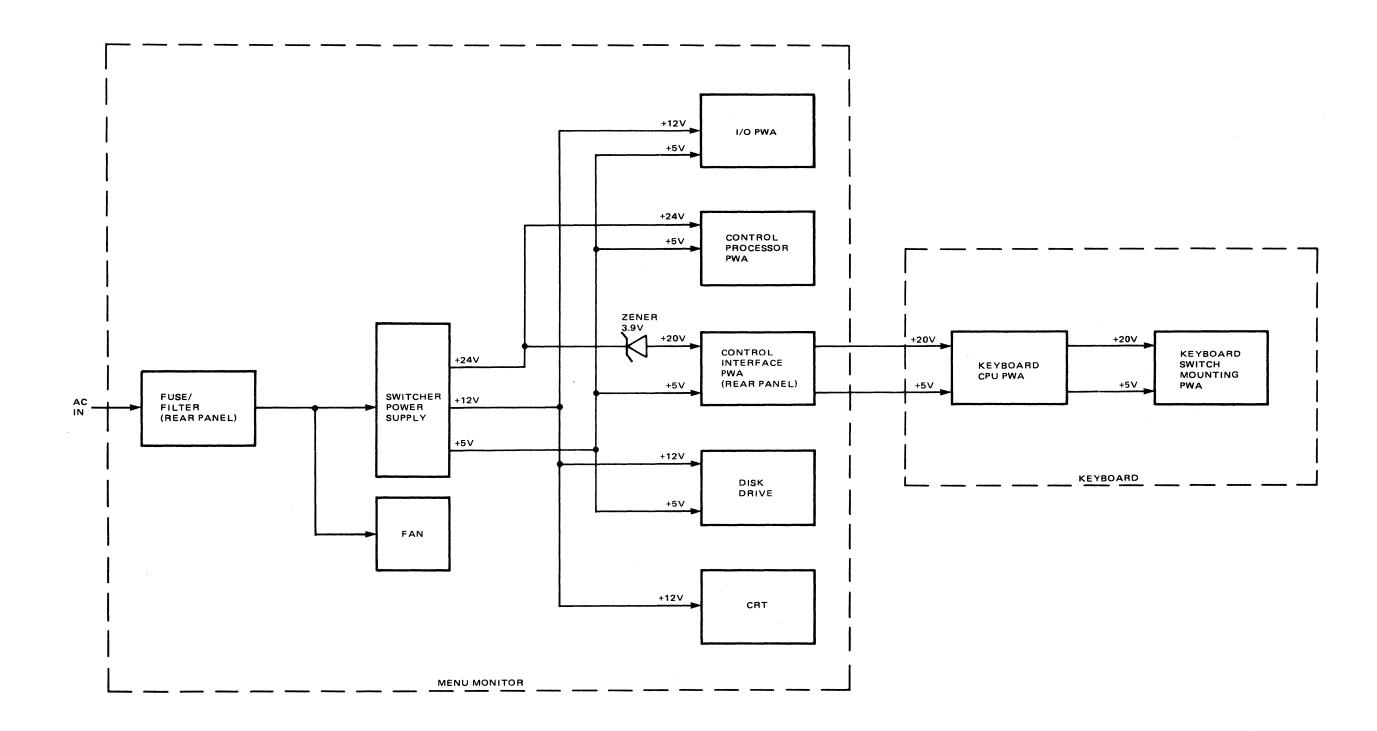

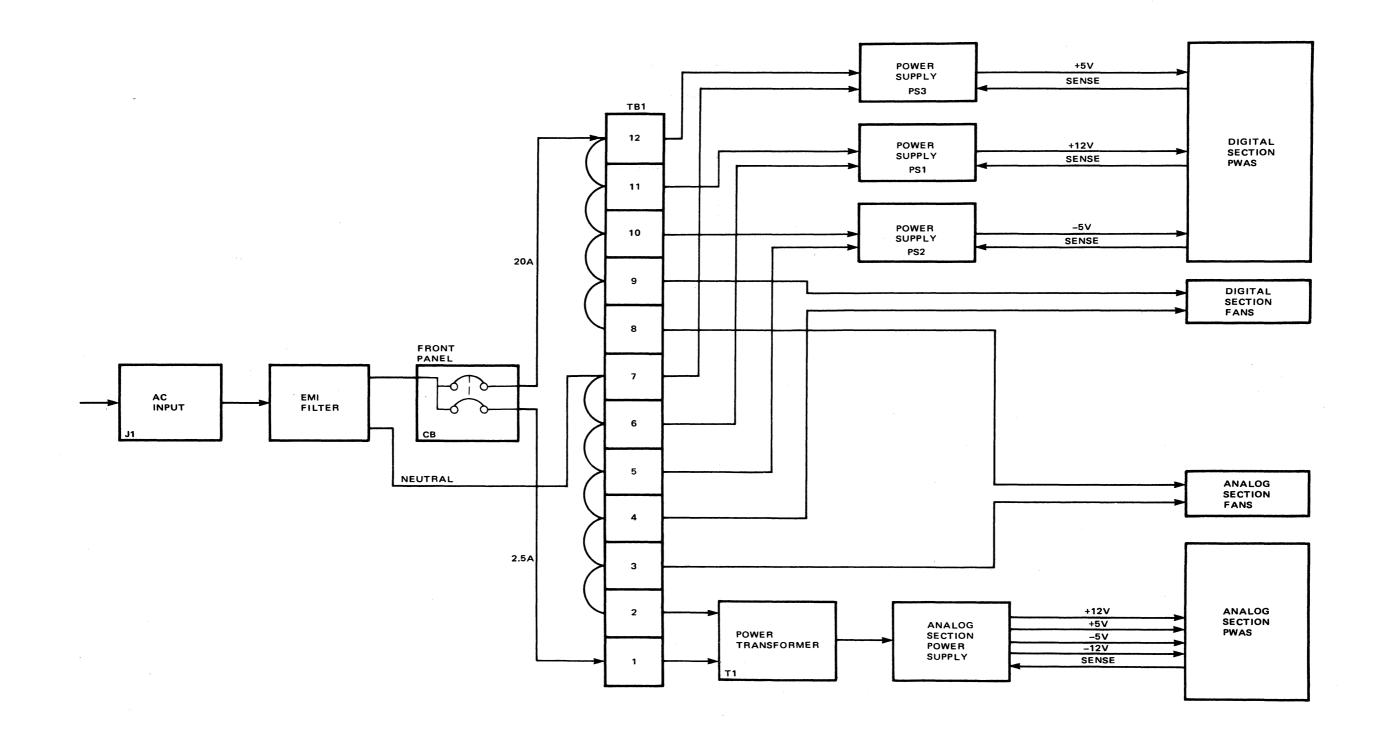

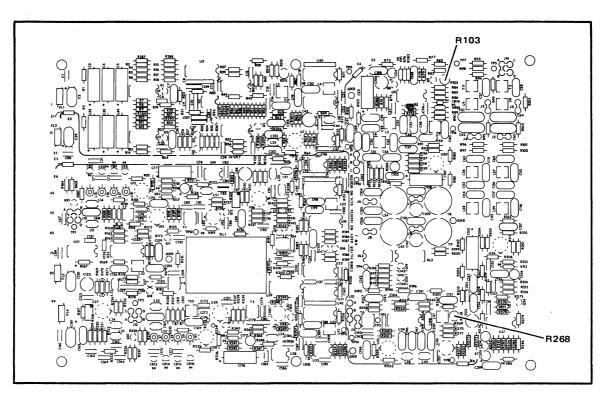

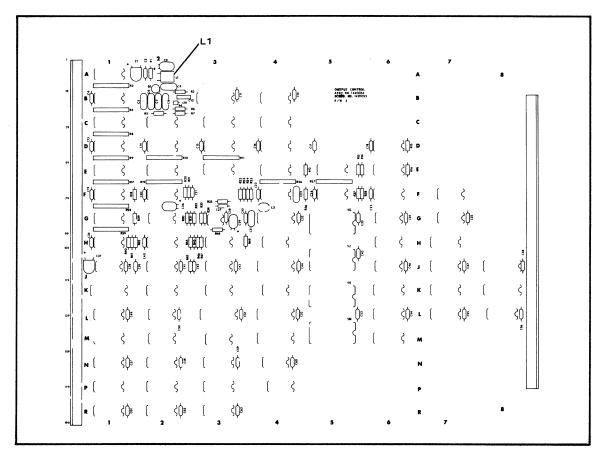

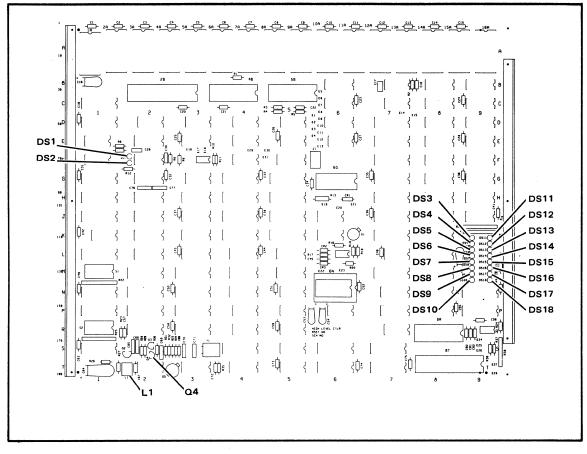

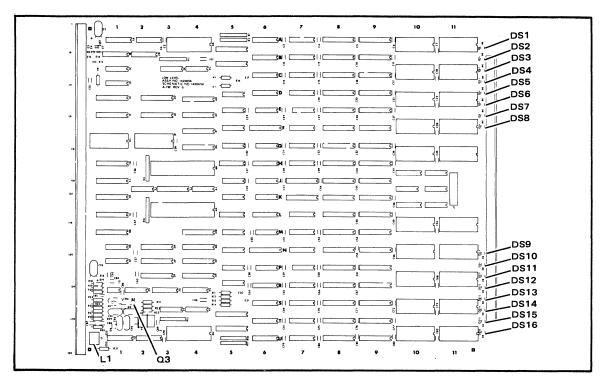

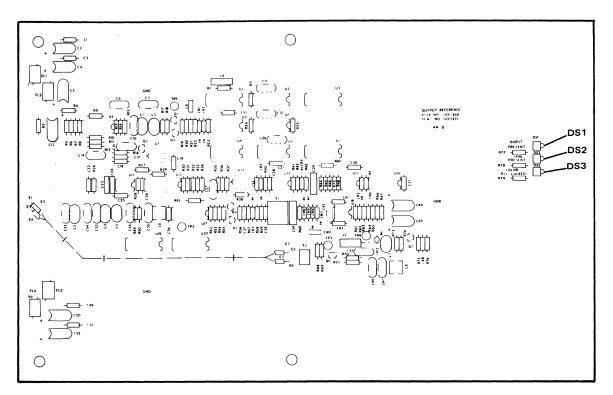

| 4-13<br>4-14<br>4-15<br>4-16<br>4-17<br>4-18<br>4-19<br>4-20<br>4-21<br>4-22<br>4-23<br>4-24 | Keyboard Internal AssemblyJoystick AssemblyMenu Monitor Internal AssembliesControl Unit Power DistributionSignal System Chassis Power DistributionComb Filter PWAInput Reference PWAA/D Converter PWAD/A Converter PWAVideo Output Processor PWAOutput Control PWAHigh Level Controller PWA | 4-14<br>4-15<br>4-16<br>4-20<br>4-21<br>4-22<br>4-22<br>4-23<br>4-24<br>4-26<br>4-27<br>4-28 |  |  |  |

| 4-25<br>4-26                                                                                 | Low Level Controller PWA                                                                                                                                                                                                                                                                    | 4-28<br>4-29<br>4-30                                                                         |  |  |  |

### LIST OF ILLUSTRATIONS (Continued)

| FIGURE<br>NO.                                        | TITLE                                  |                                                          |  |  |

|------------------------------------------------------|----------------------------------------|----------------------------------------------------------|--|--|

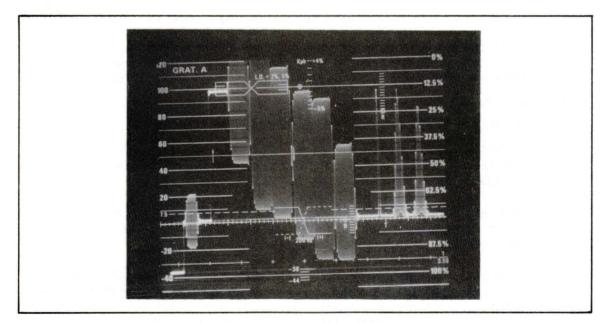

| 4-27<br>4-28                                         | Analog Troubleshooting Flowchart       | 4-32<br>4-33                                             |  |  |

| 4-29<br>4-30<br>4-31                                 | Digital Troubleshooting Flowchart      | 4-38<br>4-39<br>4-39                                     |  |  |

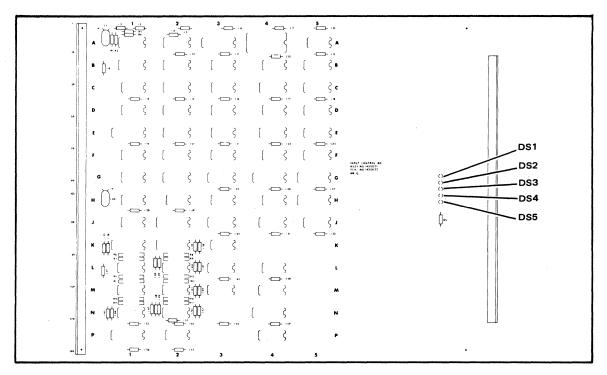

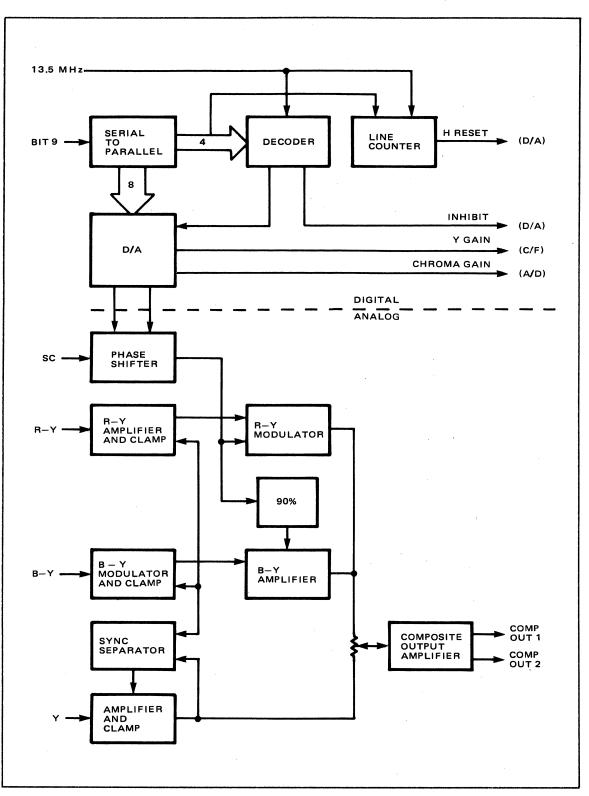

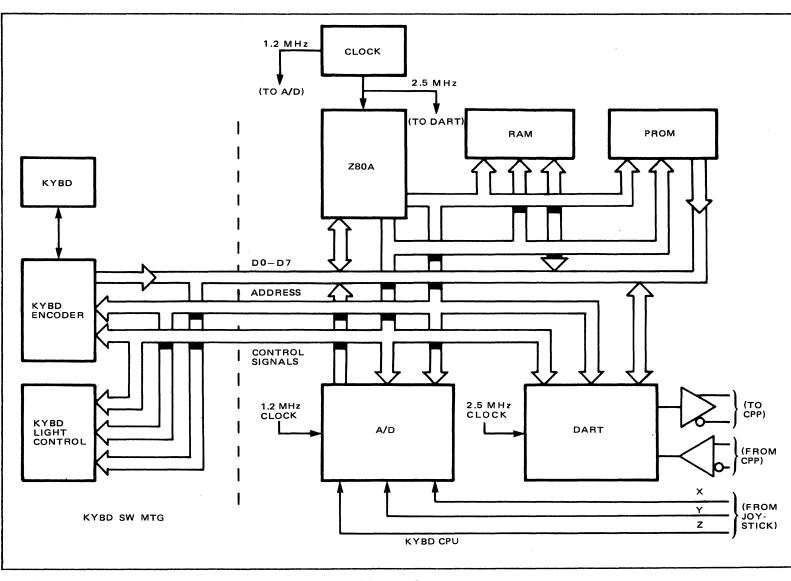

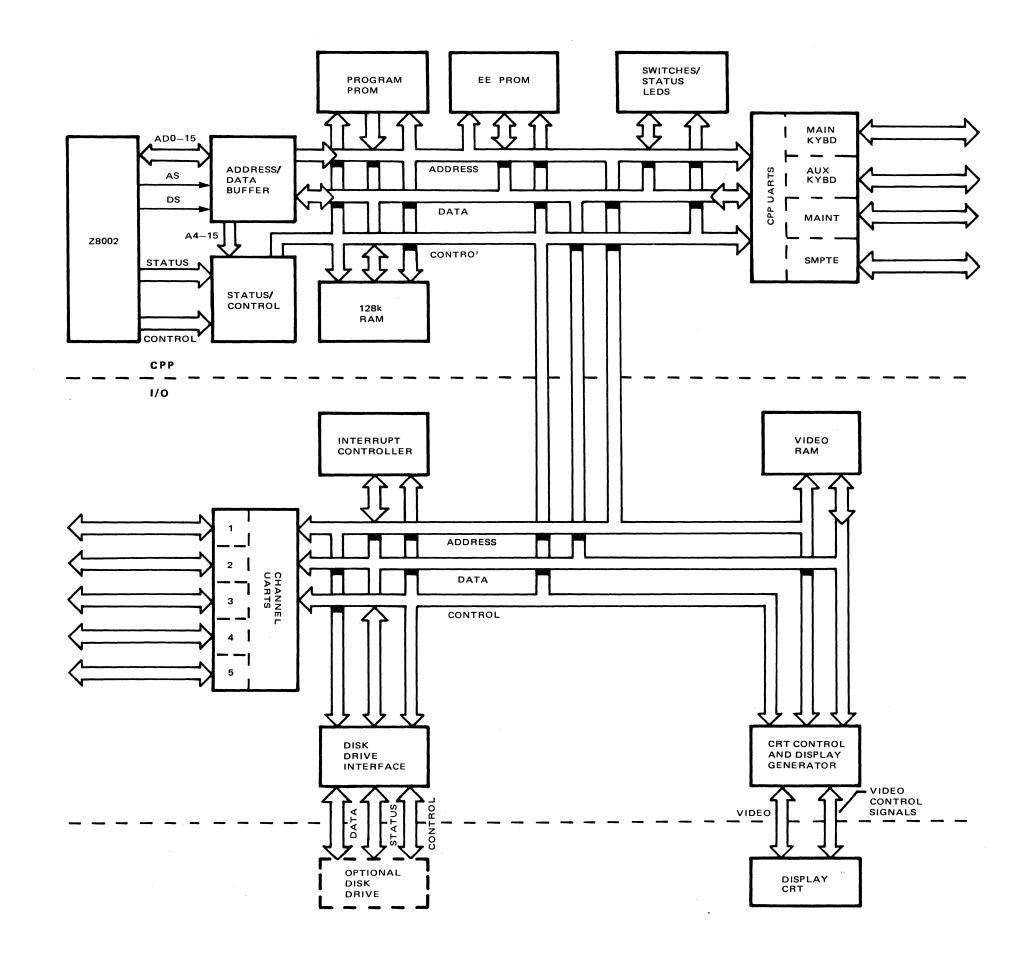

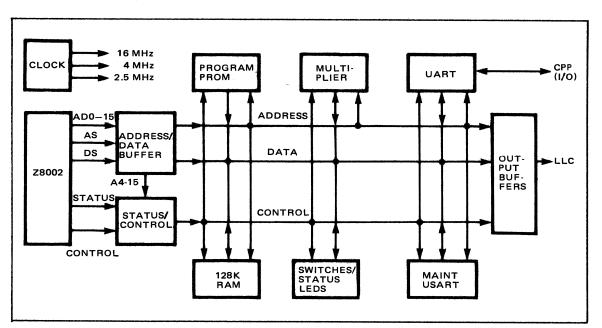

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8 | ADO System Functional Diagram          | 5-2<br>5-4<br>5-7<br>5-8<br>5-11<br>5-14<br>5-17<br>5-19 |  |  |

| 5-9<br>5-10<br>5-11<br>5-12<br>5-13<br>5-14<br>5-15  | D/A Converter PWA Output Reference PWA | 5-22<br>5-24<br>5-26<br>5-29<br>5-33<br>5-36<br>5-39     |  |  |

### LIST OF TABLES

| TABLE<br>NO. | TITLE                            | PAGE<br>NO. |

|--------------|----------------------------------|-------------|

| 1-1          | ADO Specifications               | 1-4         |

| 2-1<br>2-2   | Menu Monitor Connector Panel     | 2-5<br>2-7  |

| 3-1          | Keyboard Controls and Indicators | 3-2         |

| 4-1<br>4-2   | Typical Test Equipment           | 4-1<br>4-2  |

| 4-3          | Digital Electronic PWA Locations | 4-7         |

| 4-4          | Flat Field Values                | 4-31        |

| 4-5          | Signal System Chassis Indicators | 4-37        |

| 4-6          | Miscellaneous Fault Indications  | 4-42        |

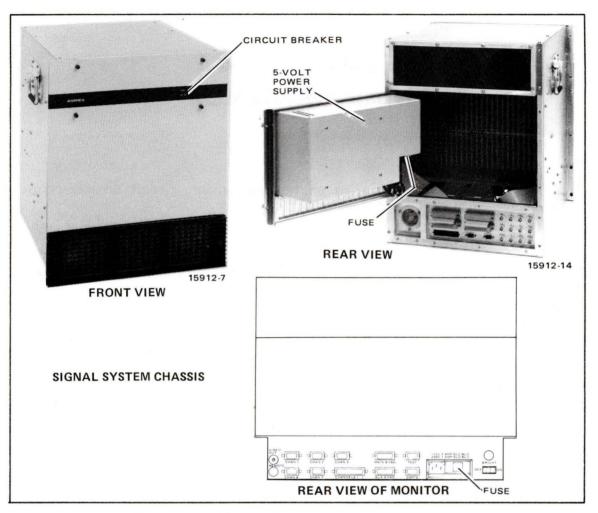

ADO System Components

# SECTION 1 GENERAL INFORMATION

### 1-1 SCOPE OF MANUAL

This manual provides the following information about the ADO (Ampex Digital Optics) System, NTSC, Ampex Part Number 1420200:

- Section 1, General Information, describes the general characteristics and functions of the ADO System.

- Section 2, *Installation*, provides instructions for mounting and interconnecting the System.

- Section 3, Operation, provides simplified operating instructions.

- Section 4, *Maintenance*, provides information about test equipment, disassembly, circuit breakers and fuses, and adjustments and trouble-shooting.

- Section 5, Theory of Operation, provides system-level and PWA-level theory descriptions.

In the theory section of this manual the analog circuitry is described at the system level. Detailed theory for the image processing PWAs will be included in a future manual. Adjustment and troubleshooting procedures are presented for the analog section. The control system PWAs, primarily software-dependent computer PWAs, are also described at the system level. PWA theory descriptions of the analog PWAs and control unit PWAs will be provided in an addendum to this manual.

Although electrical maintenance and theory descriptions in this manual have been prepared from NTSC documentation, they are useful for PAL models as well. Circuit differences consist of PROM coding, PAL/NTSC jumper selections, and minor circuit changes. Documentation for PAL circuit differences will be given in an addendum to this manual, to be provided later.

### 1-2 RELATED PUBLICATIONS

ADO System related publications are listed below. See Appendix A for vendor publications.

- ADO Operator's Guide, Ampex Catalog No. 1809551

- ADO Parts Lists and Schematics, Ampex Catalog No. 1809564

### 1-3 INTENDED USE AND CAPABILITIES

The ADO system is used to transform the geometry of video pictures at real-time video rates. The transformations include translation, compression, expansion,

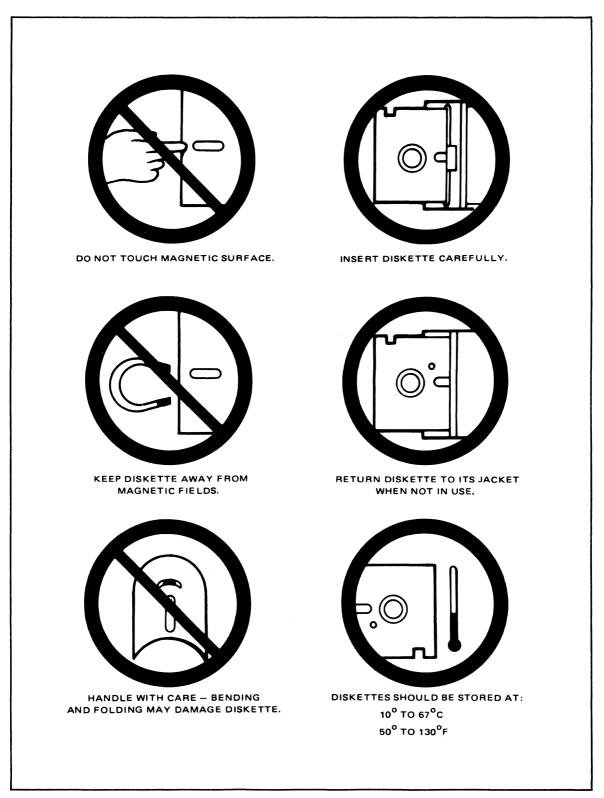

rotation, perspective projection, and combinations of these. To create a visual sequence, the operator uses a keyboard and a joystick control in conjunction with a menu displayed on a CRT monitor. An optional 5-1/4-inch floppy disk system provides storage of operating control sequences.

### 1-4 FUNCTIONAL DESCRIPTION

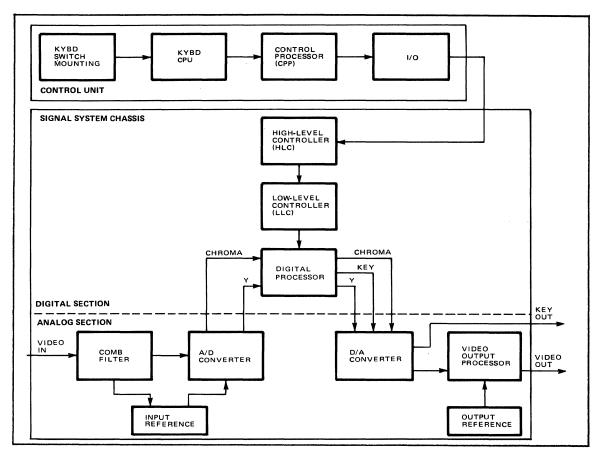

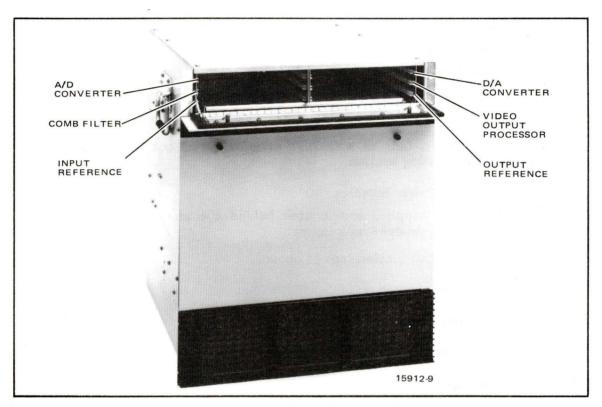

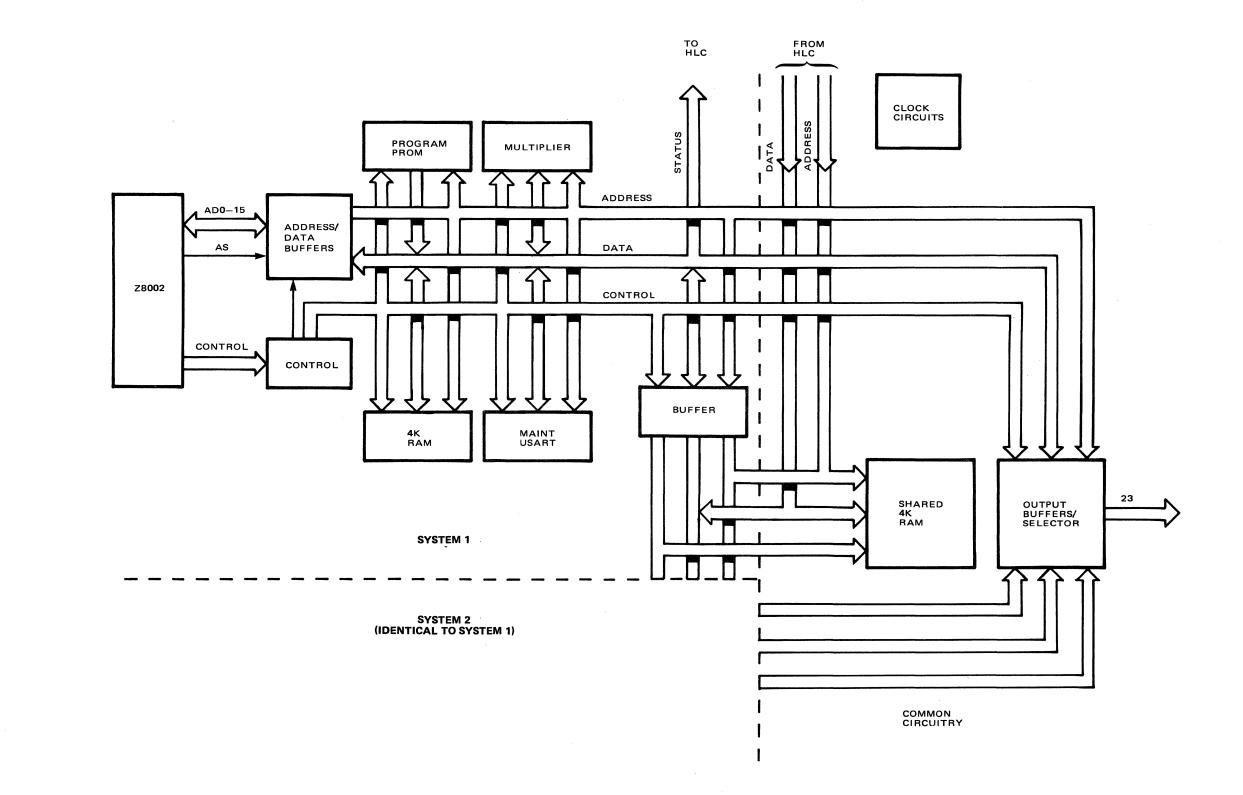

The ADO System consists of a control unit and a signal system chassis (Figure 1-1). The composite video input is converted to its luminance (Y) and chrominance (R-Y, B-Y) components which are then digitized. The digitized Y and chroma data is manipulated by the digital processor to provide the desired transformations. The processed digital information is then converted back to composite analog video. The digital processor also provides a key signal.

The keyboard CPU (Central Processing Unit) passes operator selection information to the CPP (Control Processor). The CPP controls the menu monitor display and optional disk drive and passes data to the HLC (High Level Controller) via the I/O PWA. The HLC drives the LLC (Low Level Controller), which directly controls the digital processor. The ADO System uses five microprocessors, two within the control unit, one within the HLC, and two within the LLC.

### 1-5 PHYSICAL DESCRIPTION

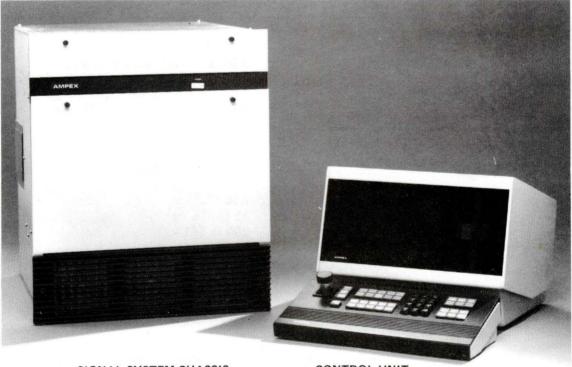

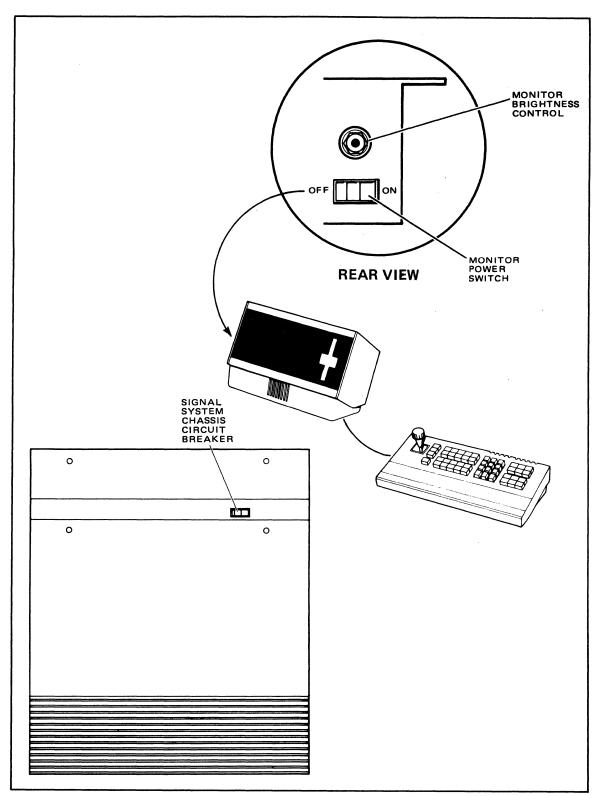

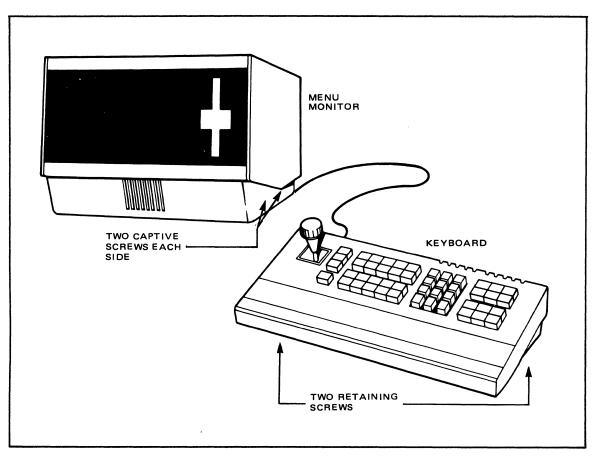

The main components of the ADO System are shown in Figure 1-2. The control unit includes a keyboard and a CRT menu monitor which can be located on a desk or console for convenient use by the operator. The signal system chassis can be mounted in a 19-inch rack. Note that the ADO Parts Lists and Schematics manual refers to the signal system chassis as the "basic channel assembly."

#### 1-6 Control Unit

The control unit components are:

- The keyboard, which contains a joystick and pushbutton keys used for entering ADO information; some of the keys are assigned by software.

- The menu monitor, which contains a CRT display, space for a floppy disk system, and a microprocessor.

The control unit is connected to the signal system chassis by serial data links. Additional ports are provided for connection to associated equipment.

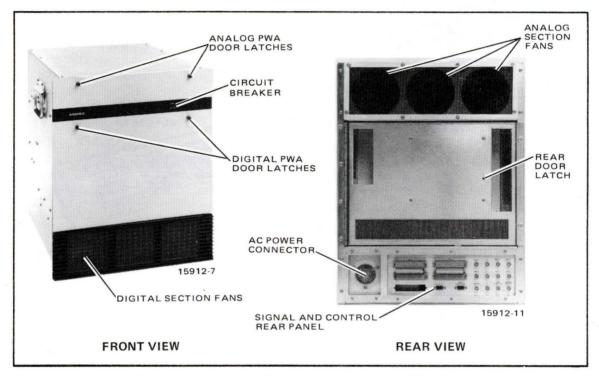

### 1-7 Signal System Chassis

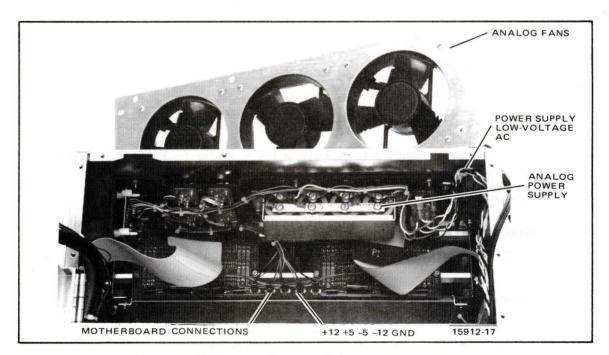

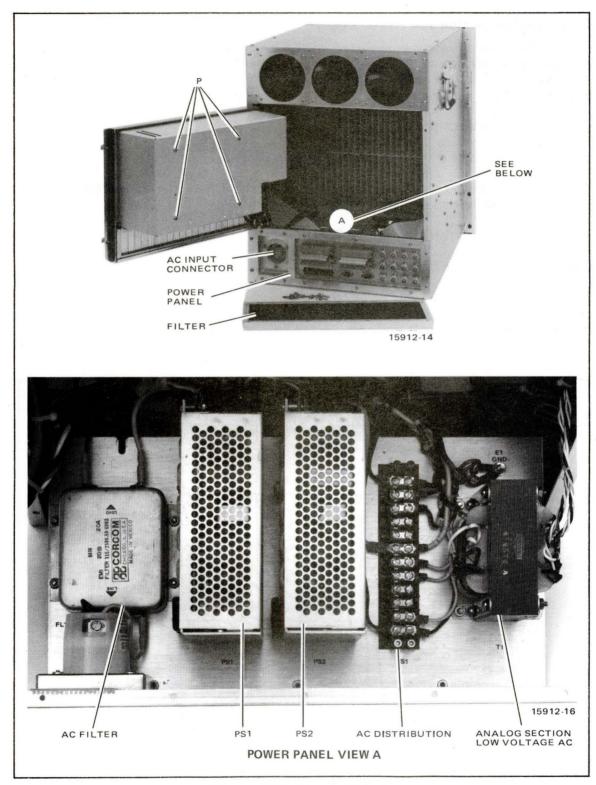

The signal system chassis contains analog and digital sections, power supplies, and cooling fans. The upper portion of the unit consists of the analog section, which

SIGNAL SYSTEM CHASSIS

CONTROL UNIT

15829-2

Figure 1-2. ADO System Components

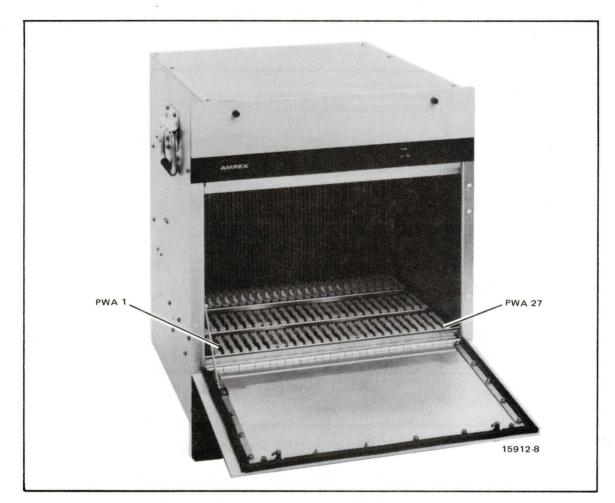

contains six PWAs (listed in Figure 4-4). The lower portion consists of the digital section. This section is accessed by a separate hinged panel and has provisions for 27 PWAs (listed in Figure 4-6). All connections to the signal system chassis are made by connectors located at the rear of the unit.

### 1-8 Software

All ADO software is contained in PROMs used within five microprocessors. Software in the menu monitor unit controls the ports used to connect the system to associated equipment. Required software changes can be provided by means of PROM exchanges.

### 1-9 OPTIONS, ACCESSORIES, AND SUPPLIES

Present and future options include the floppy disk drive, address generator, rotation, and concentrator. The Perspective I and II PWAs are also documented as options. However, these two PWAs are required for system operation at present, until other address generator PWAs are available. Analog and digital extender PWAs are provided with the basic PWAs, for servicing the unit. Supplies include the floppy disks for the optional disk drive.

### **1-10 SPECIFICATIONS**

Physical dimensions and power requirements are given in Table 1-1.

| Size (HWD)                       |            |                                                                |  |  |

|----------------------------------|------------|----------------------------------------------------------------|--|--|

| Keyboard Un                      | it:        | 5 in. x 15-1/4 in. x 7-5/8 in.<br>(126 mm x 387 mm x 194 mm)   |  |  |

| Menu Monito                      | er:        | 12 in. x 15-3/8 in. x 15-3/4 in.<br>(305 mm x 390 mm x 400 mm) |  |  |

| Signal Syster                    | n Chassis: | 22-3/4 in. x 19 in. x 22 in.<br>(578 mm x 483 mm x 560 mm)     |  |  |

| Weight                           |            |                                                                |  |  |

| Keyboard Un                      | it:        | 6 lb (2.7 kg)                                                  |  |  |

| Menu Monito                      | or:        | 35 lb (16 kg)                                                  |  |  |

| Signal System Chassis:           |            | 200 lb (91 kg)                                                 |  |  |

| Power Requirements               |            |                                                                |  |  |

| Control Unit                     | :          | 115V @ 150W                                                    |  |  |

| Signal Syster                    | n Chassis: | 115V @ 2500W                                                   |  |  |

| Video                            |            |                                                                |  |  |

| Input:<br>Output:<br>Key Output: |            |                                                                |  |  |

| 1                                |            |                                                                |  |  |

### Table 1-1. ADO Specifications

Ampex 1809550-03

# SECTION 2

This section provides information for unpacking, inspection, mounting, and interconnection of the ADO System.

### 2-1 UNPACKING

The System is shipped from the factory in a specially constructed packing case. Caution should be exercised in unpacking to prevent damage to the cabinet finish or associated parts. Check contents of the packing case and check packing materials for accessory items. Check all items against the packing list to ensure shipment is complete. Carefully examine the contents for damage that may have occurred during shipment. Notify the carrier and the Ampex representative of any shortage or damages. If it is anticipated that equipment will be moved or reshipped, retain all shipping containers and packing materials.

### 2-2 LOCATION AND MOUNTING

The ADO keyboard unit and menu monitor can be mounted on any flat surface of suitable size. The signal system chassis can be mounted in a 19-inch rack. Refer to Table 1-1 for physical dimensions and power requirements. The area chosen for the System should be adequately ventilated and relatively dust free. Cooling air is drawn into the front of the System and is discharged at the rear. The System should not be close to any strong electromagnetic fields. Common sources of interference include fluctuating loads on nearby high-current lines, fluorescent lighting, heavy duty transformers, elevator motors, and radio, television, and amateur radio transmitting equipment.

For determining mounting-space requirements, physical dimensions for each major component are shown in Figures 2-1 through 2-3. When considering location, be certain to provide adequate access space at the rear of the CRT monitor and signal system chassis for cable connections and servicing. The keyboard unit and menu monitor can be located up to 2,000 ft (607 m) from the signal system chassis.

### 2-3 SIGNAL SYSTEM CHASSIS RACK MOUNTING

### WARNING

BECAUSE OF THE WEIGHT OF THE SIGNAL SYSTEM CHASSIS TWO OR MORE PERSONS ARE NEEDED TO LIFT THE UNIT INTO PLACE IN THE RACK. FOR CONVENIENCE WHILE INSTALLING THE RACK-MOUNTING SCREWS, USE A BLANK PANEL OR OTHER SUPPORT FOR THE UNIT TO REST ON.

Figure 2-1. Keyboard Unit Dimensions

Figure 2-2. Menu Monitor Dimensions

Figure 2-3. Signal System Chassis Dimensions

The signal system chassis is designed to mount in a standard 19-inch (483 mm) rack and occupy 22.75 inch (578 mm) of vertical rack space. For signal system chassis dimensions, refer to Figure 2-3. Allow adequate space behind the unit for cable connection, air flow, and servicing.

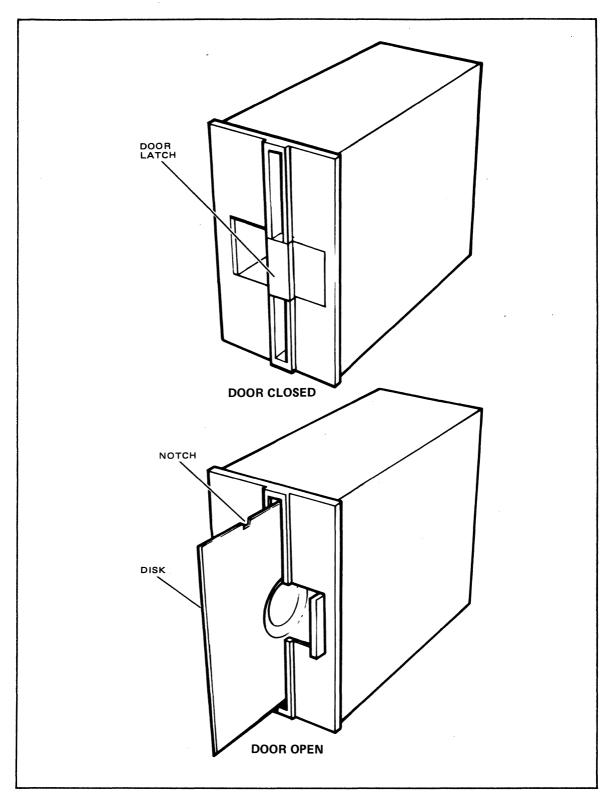

Mount the unit into a rack as follows:

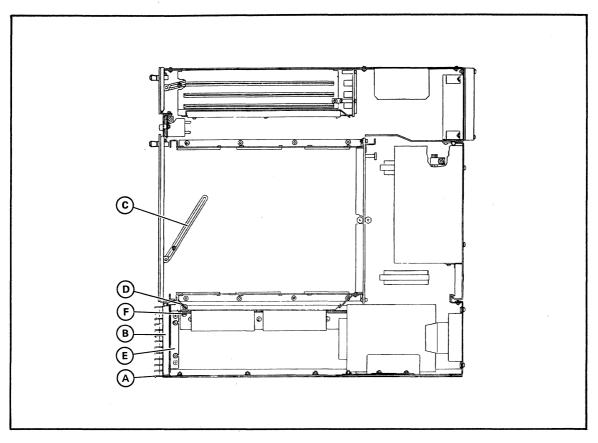

- STEP 1 With the two doors closed, remove the two screws (A) that hold the grill to the bottom front of the cabinet. (See Figure 2-4.)

- STEP 2 Remove the two screws (B) that hold each of the two grill mounting clips.

Ampex 1809550-03

Figure 2-4. Signal System Chassis

Note

It is necessary to remove handles from sides of cabinet before mounting unit into rack (four screws each handle).

- STEP 3 Place unit into the 19-inch rack and secure with four screws (B).

- STEP 4 Turn latches (C) counterclockwise to release top door. Open door and install two mounting screws, one each side. Close and secure door.

- STEP 5 Turn latches (D) counterclockwise to release bottom door. Open door and install six mounting screws, three each side. Close and secure door.

- STEP 6 Loosen bottom four screws and install the slotted grill mounting clips. Tighten screws.

- STEP 7 Reinstall grill (two screws).

### 2-4 POWER AND SIGNAL CONNECTIONS

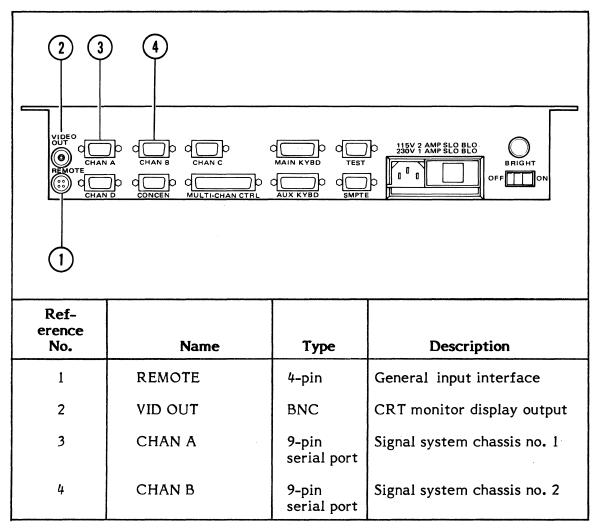

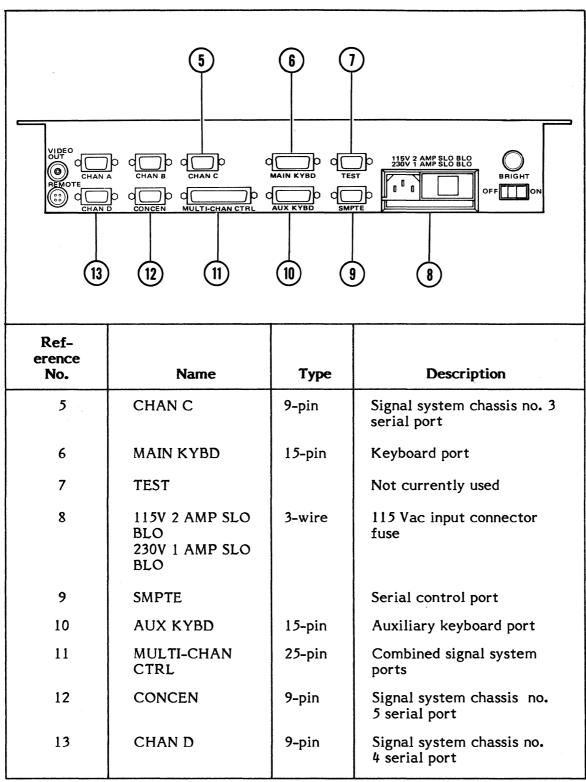

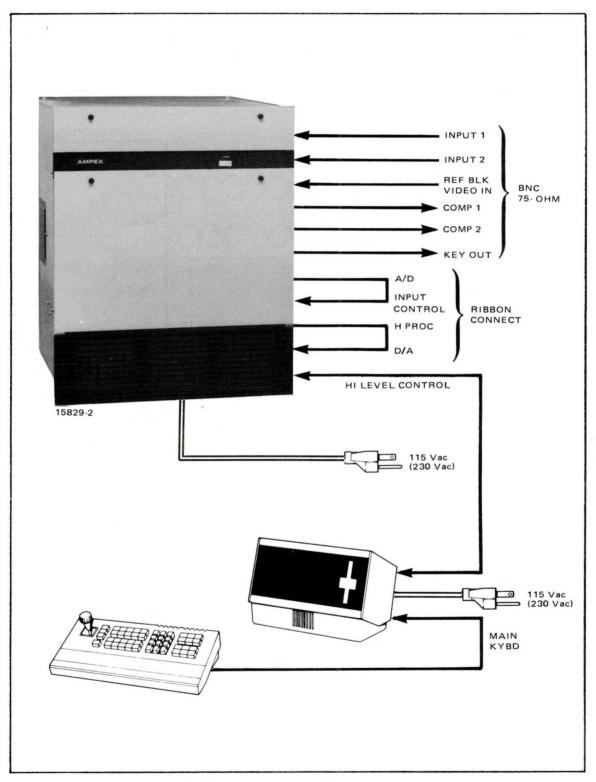

All connections to and from the ADO System are made to connectors at the rear of the menu monitor and the signal system chassis. These connections for a single-channel system are listed and described in Tables 2-1 and 2-2. Figure 2-5 is a basic system interconnection diagram.

Table 2-1. Menu Monitor Connector Panel

(Continued next page)

Table 2-1. Menu Monitor Connector Panel (Continued)

| 1         2         3         4         5         6           1         2         3         4         5         6           1         2         3         4         5         6           1         0         3         4         5         6           1         0         3         4         5         6           1         0         3         3         3         6         6           1         1         1         1         1         1         1         1           1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |        |                         |                          |                                    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|--------------------------|------------------------------------|--|

| Ref-<br>erence<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Number | Name                    | Туре                     | Description                        |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J1     | 115 VAC                 | Three-<br>prong<br>power | Power_input                        |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J2     | D/A                     | Ribbon                   | Digital input to analog section    |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J3     | H PROC                  | Ribbon                   | Digital processor output           |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J4     | -                       | -                        | Not used                           |  |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J5     | A/D                     | Ribbon                   | Digital output from analog section |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J6     | INPUT<br>CONTROL        | Ribbon                   | Digital processor input            |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J7     | HI LEVEL<br>CTL         | 9-Pin,<br>Type D         | Serial port to CRT menu<br>monitor |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J8     | VIDEO<br>OUTPUT<br>PROC | 9-Pin,<br>Type D         | For concentrator option            |  |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J9     | COMP 1                  | BNC                      | Composite video output 1           |  |

Table 2-2. Signal System Chassis Connector Panel

(Continued next page)

| 12     13     15       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1     1     1       1     1 |        |                     |          |                                              |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|----------|----------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | r      |                     | <b>Г</b> |                                              |  |

| Ref-<br>erence<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Number | Name                | Туре     | Description                                  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J10    | COMP 2              | BNC      | Composite video output 2                     |  |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J11    | KEY OUT             | BNC      | Key output (noncomposite)                    |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12     | R                   | BNC      | Red output (OPTIONAL)                        |  |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J13    | G                   | BNC      | Green output (OPTIONAL)                      |  |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J14    | В                   | BNC      | Blue output (OPTIONAL)                       |  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J15    | INPUT 1             | BNC      | Composite video input 1<br>(Input A)         |  |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J16    | KEY 1               | BNC      | Key video input 1 (Input A)<br>(OPTIONAL)    |  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J17    | COMP SYNC<br>OUT    | BNC      | Composite sync output<br>(OPTIONAL)          |  |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J18    | INPUT 2             | BNC      | Composite video input 2<br>(Input B)         |  |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J19    | KEY 2               | BNC      | Key video input 2 (Input B)<br>(OPTIONAL)    |  |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J20    | REF BLK<br>VIDEO IN | BNC      | Station reference black burst<br>video input |  |

Table 2-2. Signal System Chassis Connector Panel (Continued)

Figure 2-5. ADO System Basic Interconnection

2-9

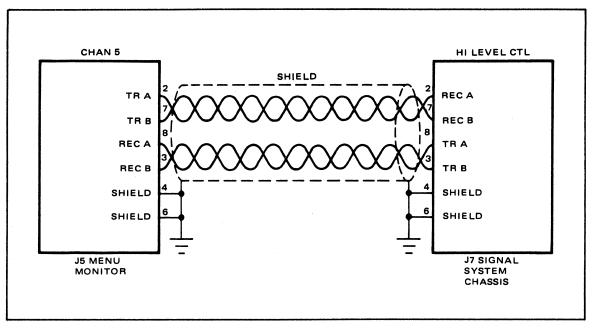

The connection between the connector HI LEVEL CTL on the rear of the signal system chassis and the CHAN 5 connector on the CRT display unit can be up to 2,000 ft (607 m) in length. Figure 2-6 is a wiring diagram of this cable.

Figure 2-6. High Level Control to Channel 5 Cable

# SECTION 3 OPERATION

### 3-1 INTRODUCTION

1

This section of the manual presents operating procedures and the locations and functions of operating controls and indicators. For detailed operating information, refer to the ADO Operator's Guide.

### 3-2 CONTROLS AND INDICATORS

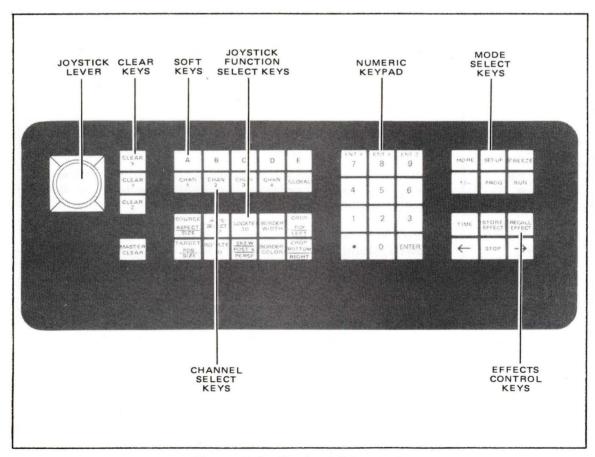

Primary operating controls are located on the control unit. These controls are shown in Figure 3-1. Simplified descriptions of the controls are presented in Table 3-1. Refer to the ADO Operator's Guide for detailed descriptions.

Figure 3-1. Keyboard Controls

| Description                         | Function                                                                                                                                                                                                                                                                       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Joystick Lever<br>and Knob          | Joystick lever is used to control the type of effect, its direction, and degree.                                                                                                                                                                                               |

|                                     | The type of effect is selected by the Joystick Function<br>Select Keys and the axis of deflection is controlled by the<br>joystick lever.                                                                                                                                      |

|                                     | The X axis is controlled by deflecting the lever left or right.                                                                                                                                                                                                                |

|                                     | The Y axis is controlled by deflecting the lever forward or back.                                                                                                                                                                                                              |

|                                     | The Z axis is controlled by rotating the lever clockwise or counterclockwise.                                                                                                                                                                                                  |

|                                     | All parameters of the effect are controlled by the amount of deflection of the joystick.                                                                                                                                                                                       |

| CLEAR X<br>(or Y or Z)              | Removes any effect of the selected function present in the X (or Y or Z) axis. When in rotate mode, the CLEAR X (or Y or Z) key provides an additional function: when pushed once it clears to the nearest 90° of X (or Y or Z) rotation; when pushed again it clears to zero. |

| MASTER<br>CLEAR                     | Removes all effects present in the X, Y, and Z axis of the video, and returns the picture to normal 1 to 1 ratio.                                                                                                                                                              |

| A,B,C,D,E<br>soft keys              | The five soft keys initiate functions as determined by the ADO System internal program. Available functions are displayed on the menu monitor.                                                                                                                                 |

| CHAN 1,2,3,4<br>GLOBAL              | Channel keys select individual channels in a multiple<br>channel system; the GLOBAL key selects all channels. The<br>GLOBAL key causes an overall configuration to be trans-<br>formed rather than the individual key frames.                                                  |

| Joystick<br>Function<br>Select Keys | The ten joystick function select keys are mutually exclusive<br>but can be performed serially. The joystick is used to<br>manipulate the three axes of the video picture according to<br>the function selected.                                                                |

| SOURCE<br>ASPECT/<br>SIZE           | When this key is pressed, the joystick is used to change the aspect ratio of the video picture along the X (horizontal) or Y (vertical) axis; joystick rotation changes the overall size of the picture.                                                                       |

| Table 3-1. | Keyboard | Controls a | and Indicators |

|------------|----------|------------|----------------|

|------------|----------|------------|----------------|

(Continued next page)

| Description                            | Function                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AXIS SELECT<br>3D                      | Joystick selects key frame axis of rotation (X, Y, Z).                                                                                                                                                                                                                                                                                                                                                                |

| LOCATE 3D                              | Establishes joystick control of image movement with<br>corresponding visual presentation of image area seen in<br>new perspective (X, Y, Z axis—three dimensions). Changes<br>the relative point of view of the ADO System image.                                                                                                                                                                                     |

| BORDER<br>WIDTH                        | Selects border width. Border width entered through numeric keypad.                                                                                                                                                                                                                                                                                                                                                    |

| CROP<br>TOP/LEFT                       | Sets the top and left edges of the crop; only X-axis and Y-axis controls are active.                                                                                                                                                                                                                                                                                                                                  |

| TARGET<br>POS/SIZE                     | Allows operator to move picture in a horizontal (X) or a vertical (Y) direction. Knob rotation controls the size of the picture.                                                                                                                                                                                                                                                                                      |

| ROTATE 3D                              | Permits operator to rotate image around any axis (X,Y,Z).                                                                                                                                                                                                                                                                                                                                                             |

| SKEW<br>POST X/<br>PERSP               | Joystick in X-axis skews (slants) the picture to right or left;<br>or in the Y-axis executes the post-X function. This function<br>is an advanced special effect X rotation not obtain-<br>able by use of the rotate 3D key; it operates in target space<br>rather than in source space. (Refer to ADO Operator's<br>Guide.) Rotating the joystick knob adds or subtracts de-<br>grees of perspective in the picture. |

| BORDER<br>COLOR                        | Selects border color. Color entered through numeric keypad.                                                                                                                                                                                                                                                                                                                                                           |