# Reference Manual

Volume 2

Burroughs cannot accept any financial or other responsibilities that may be the result of your use of this information or software material, including direct, indirect, special or consequential damages. There are no warranties extended or granted by this document or software material.

You should be very careful to ensure that the use of this software material and/or information complies with the laws, rules, and regulations of the jurisdictions with respect to which it is used.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this publication should be forwarded using the Remarks form at the back of the manual, or may be addressed directly to Corporate Documentation-West, Burroughs Corporation, 1300 John Reed Court, City of Industry, California 91745, U.S.A.

### LIST OF EFFECTIVE PAGES

| Page           | Issue    |

|----------------|----------|

| Title          | Original |

| ii             | Original |

| iii            | Original |

| iv             | Blank    |

| v thru xix     | Original |

| XX             | Blank    |

| xxi thru xxii  | Original |

| 1-1 thru 1-22  | Original |

| 2-1 thru 2-15  | Original |

| 2-16           | Blank    |

| 3-1 thru 3-101 | Original |

| 3-102          | Blank    |

| 4-1 thru 4-22  | Original |

| A-I thru A-II  | Original |

| A-12           | Blank    |

| B-1 thru B-83  | Original |

| B-84           | Blank    |

| C-1 thru C-19  | Original |

| C-20           | Blank    |

# TABLE OF CONTENTS

| Section | Title                                  | Page  |

|---------|----------------------------------------|-------|

|         | INTRODUCTION                           | xxi   |

| 1       | DATA STRUCTURES                        | 1-1   |

|         | General Information                    | 1-1   |

|         | Even-Tag Words                         | 1-2   |

|         | Operands (Single-and Double-Precision) | 1-2   |

|         | Numeric Operands                       | 1-5   |

|         | Boolean Operands                       | 1-5   |

|         | Tag-4 Word                             |       |

|         | Tag-6 Word (Uninitialized Datum)       | 1-6   |

|         | Odd-Tag Words                          | 1-7   |

|         | Program Code Words                     | 1-7   |

|         | Segments                               | 1-8   |

|         | Descriptors                            | . 1-8 |

|         | Data Segment Descriptor                | . 1-8 |

|         | Code Segment Descriptor                | 1-10  |

|         | Stack Segments                         | 1-11  |

|         | Paged Segments                         | 1-11  |

|         | References                             | 1-12  |

|         | Address Couples                        | 1-12  |

|         | Fixed-Fence Address Couples            | 1-12  |

|         | Variable-Fence Address Couples         | 1-12  |

|         | Lexical Links                          | 1-13  |

|         | IRW (Indirect Reference Word)          | 1-13  |

|         | NIRW (Normal Indirect Reference Word)  | 1-13  |

|         | SIRW (Stuffed Indirect Reference Word) | 1-13  |

|         | IndexedDD (Indexed Data Descriptor)    | 1-14  |

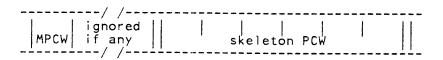

|         | PCW (Program Control Word)             | 1-16  |

|         | Stack Linkage Words                    | 1-16  |

|         | MSCW (Mark Stack Control Word)         | 1-17  |

|         | RCW (Return Control Word)              | 1-18  |

|         | TSCW (Top of Stack Control Word)       |       |

|         | Interlocks                             |       |

|         | Tags 8-15                              | 1-21  |

| 2       | STACK CONCEPT AND PROCESSOR STATE      | 2-1   |

|         | General Information                    | 2-1   |

|         | Stacks                                 | 2-1   |

|         | Code Segment Dictionaries              |       |

|         | Addressing Granularity                 | 2-1   |

|         | Program Addressing Environment         | 2-2   |

|         | Memory Addressing                      | 2-3   |

|         | Expression Stack                       | 2-7   |

|         | Executable Code Streams                | 2-8   |

|         | General Boolean Accumulators           | 2-10  |

|         | Miscellaneous Processor State          | 2-10  |

|         | Processor State Component Sizes        | 2-11  |

|         | Addressing Environment State:          | 2-11  |

|         | Memory Addressing State:               | 2-11  |

| Section | Title                                          | Page   |

|---------|------------------------------------------------|--------|

| 2       | Expression Stack State:                        | . 2-12 |

| (Cont)  | Code Stream Pointer:                           |        |

|         | Execution State Attributes:                    | . 2-12 |

|         | General Boolean Accumulators:                  | . 2-12 |

|         | Miscellaneous State:                           | . 2-12 |

|         | System Control                                 |        |

|         | Programming Restrictions Due to Hidden State   |        |

| 3       | OPERATOR SET AND COMMON ACTIONS                | . 3-1  |

|         | General Information                            | . 3-1  |

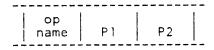

|         | Operators and Code Streams                     | . 3-1  |

|         | Primary, Variant and Edit Operators            | . 3-2  |

|         | Common Actions: common action                  | . 3-2  |

|         | Initial and Restart State                      | . 3-2  |

|         | Checks and Interrupts                          | . 3-3  |

|         | Expression Stack Control                       | . 3-3  |

|         | Top-of-Stack Push Operations                   | . 3-3  |

|         | Top-of-Stack Pop Operations                    | . 3-4  |

|         | Descriptor Interpretation                      |        |

|         | Computational Operators                        | . 3-5  |

|         | Numeric Operand Interpretation                 | . 3-5  |

|         | Representable Operand Formats                  | . 3-6  |

|         | Single-Precision Operand Values                | . 3-6  |

|         | Double-Precision Operand Values                | . 3-6  |

|         | Automatic Arithmetic Functions                 | . 3-6  |

|         | Numeric-Interpretation Operators               | . 3-7  |

|         | Arithmetic Operators                           | . 3-7  |

|         | ADD (add)                                      | . 3-7  |

|         | SUBT (subtract)                                |        |

|         | MULT (multiply)                                |        |

|         | MULX (extended multiply)                       |        |

|         | DIVD (divide)                                  |        |

|         | IDIV (integer divide)                          | . 3-8  |

|         | RDIV (remainder divide)                        | . 3-8  |

|         | NORM (normalize)                               |        |

|         | AMIN and AMAX (arithmetic minimum and maximum) |        |

|         | Relational Operators                           | . 3-9  |

|         | LESS (less than)                               |        |

|         | LSEQ (less than or equal to)                   |        |

|         | EQUL (equal to)                                |        |

|         | NEQL (not equal to)                            |        |

|         | GREQ (greater than or equal to)                |        |

|         | GRTR (greater than)                            |        |

|         | Range Test Operators                           | -      |

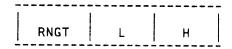

|         | RNGT (range test)                              |        |

|         | DRNT (dynamic range test)                      | . 3-10 |

|         | Numeric Type-Transfer Operators                | . 3-10 |

|         | NTIA (integerize truncated)                    | . 3-10 |

|         |                                                |        |

| Section | Title                                                         |                       | Pa                    | age                |

|---------|---------------------------------------------------------------|-----------------------|-----------------------|--------------------|

| 3       | NTGR (integerize rounded)                                     |                       | 3                     | -11                |

| (Cont)  | SNGL (set to single-precision rounded)                        |                       | 3                     | -î î               |

|         | SNGT (set to single-precision truncated)                      |                       | 3.                    | -11                |

|         | NTTD (integerize double-precision truncated) .                |                       | 3                     | -11                |

|         | NTGD (integerize double-precision rounded)                    |                       | 3                     | -12                |

|         | aISX (integer subset exception action)                        |                       | 3                     | -12                |

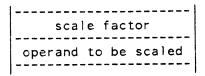

|         | Scale Left                                                    |                       | 3.                    | -12                |

|         | SCLF (scale left)                                             |                       | 3.                    | -13                |

|         | DSLF (dynamic scale left)                                     |                       | 3.                    | -13                |

|         | Scale Right                                                   |                       | 3.                    | -13                |

|         | SCRS (scale right save)                                       |                       | 3.                    | -1 <i>3</i><br>-14 |

|         | DSRS (dynamic scale right save)                               |                       | 3.                    | -14                |

|         | SCRT (scale right truncate)                                   |                       | 3                     | -14                |

|         | DSRT (dynamic scale right truncate)                           | • • • • • • • • •     | 3.                    | -14<br>-14         |

|         | SCRR (scale right rounded)                                    |                       | 3                     | -1 <del>-1</del>   |

|         | DSRR (dynamic scale right rounded)                            |                       | 3                     | -1 <i>5</i><br>-15 |

|         | SCRE (scale right final)                                      |                       | 3-                    | -1 <i>5</i><br>-15 |

|         | SCRF (scale right final)                                      |                       | 3.                    | -13<br>-15         |

|         | DSRF (dynamic scale right final) Binary to Decimal Conversion |                       | 3-                    | -15<br>-16         |

|         | BCD (binary convert to decimal)                               |                       | 3-                    |                    |

|         | DBCD (dynamic binary convert to decimal)                      |                       | 3-                    | -16<br>-17         |

|         | Rit Vector Interpretation                                     | • • • • • • • • •     | 3-                    |                    |

|         | Bit Vector Interpretation                                     |                       |                       | -17                |

|         | Logical Operators                                             | • • • • • • • •       | 3-                    | -17                |

|         | LNOT (logical not)                                            | • • • • • • • • •     | 3-                    | -17                |

|         | LAND (logical and)                                            | • • • • • • • • •     |                       | -17                |

|         | LOR (logical or)                                              | • • • • • • • •       | • • 3-                | -18                |

|         | LEQV (logical equivalence)                                    |                       |                       | -18                |

|         | Relational Operator                                           |                       | 3-                    | -18                |

|         | SAME (logical equality)                                       |                       | 3-                    | -18                |

|         | Literal Operators                                             |                       | 3-                    | 18                 |

|         | ZERO (insert literal zero)                                    |                       | 3-                    | -18                |

|         | ONE (insert literal one)                                      |                       | 3-                    | -18                |

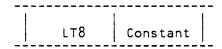

|         | LT8 (insert 8 bit literal)                                    |                       | 3-                    | 18                 |

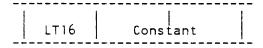

|         | LT16 (insert 16 bit literal)                                  | · · · · · · · · · · · | 3-                    | 18                 |

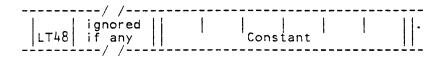

|         | LT48 (insert 48 bit literal)                                  |                       | 3-                    | 19                 |

|         | Bit-Vector Type-Transfer Operators                            |                       |                       | 19                 |

|         | STAG (set tag)                                                |                       | 3-                    | 19                 |

|         | XTND (set to double-precision)                                |                       |                       | 20                 |

|         | JOIN (set two singles to double)                              |                       |                       | 20                 |

|         | SPLT (set double to two singles)                              |                       |                       | 20                 |

|         | Evaluate Word Structure Operators                             |                       |                       | 21                 |

|         | RTAG (read tag)                                               |                       |                       | 21                 |

|         | CBON (count binary ones)                                      |                       | 3-                    | 21                 |

|         | LOG2 (leading one test)                                       |                       | 3-                    | 21                 |

|         | Word Manipulation Operators                                   |                       | 3-                    | 21                 |

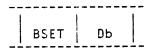

|         | BSET (bit set)                                                |                       | $\cdot \cdot \cdot 3$ | 22                 |

|         | DBST (dynamic bit set)                                        |                       | 3-                    | 22                 |

| Section | Title                                                            | Page |

|---------|------------------------------------------------------------------|------|

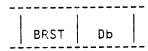

| 3       | BRST (bit reset)                                                 | 3-22 |

| (Cont)  | DBRS (dynamic bit reset)                                         | 3-22 |

|         | ISOL (field isolate)                                             |      |

|         | DISO (dynamic field isolate)                                     | 3-23 |

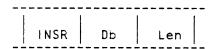

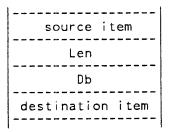

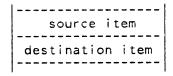

|         | INSR (field insert)                                              | 3-23 |

|         | DINS (dynamic field insert)                                      | 3-24 |

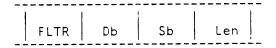

|         | FLTR (field transfer)                                            |      |

|         | DFTR (dynamic field transfer)                                    |      |

|         | CHSN (change sign)                                               |      |

|         | Linear Index-Function Operator                                   |      |

|         | OCRX (occurs index)                                              |      |

|         | Reference Generation and Evaluation Operators                    |      |

|         | Double Precision                                                 |      |

|         | Stack references                                                 |      |

|         | Lexical Link Evaluation                                          |      |

|         |                                                                  |      |

|         | aLXLK (evaluate lexical link)                                    |      |

|         | Lexical Chains                                                   |      |

|         | aLXCH (traverse lexical chain)                                   |      |

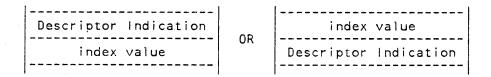

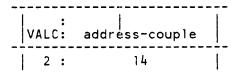

|         | Address-Couple Evaluation                                        | 3-27 |

|         | Evaluation of References                                         |      |

|         | Address Couple Parameters                                        |      |

|         | NIRWs                                                            |      |

|         | SIRWs                                                            |      |

|         | IndexedWordDDs                                                   |      |

|         | PCWs                                                             |      |

|         | IRW Chains                                                       |      |

|         | Reference Chains                                                 |      |

|         | Reference Generation Operators                                   |      |

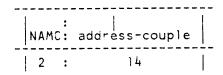

|         | NAMC (name call)                                                 |      |

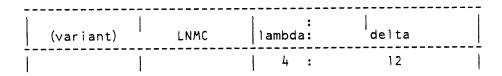

|         | LNMC (long name call)                                            |      |

|         | STFF (stuff)                                                     |      |

|         | INDX (index)                                                     |      |

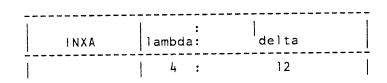

|         | INXA (index by means of address-couple parameter)                |      |

|         | MPCW (make PCW)                                                  |      |

|         | Read Evaluation Operators                                        |      |

|         | aFOP (Fetch Operand)                                             | 3-34 |

|         | aCPY (fetch copy descriptor)                                     | 3-34 |

|         | VALC (value call)                                                | 3-35 |

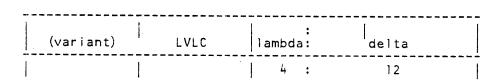

|         | LVLC (long value call)                                           | 3-36 |

|         | NXLV (index and load value)                                      | 3-36 |

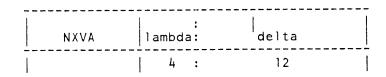

|         | NXVA (index and load value by means of address-couple parameter) | 3-37 |

|         | NXLN (index and load name)                                       | 3-37 |

|         | EVAL (evaluate)                                                  | 3-38 |

|         | LOAD (load)                                                      | 3-39 |

|         | LODT (load transparent)                                          | 3-39 |

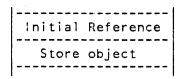

|         | Store Evaluation Operators                                       | 3-41 |

|         | Normal Store Operators                                           |      |

|         | STOD (store delete)                                              |      |

| Section | Title                                                                   | Page |

|---------|-------------------------------------------------------------------------|------|

| 3       | STON (store non-delete)                                                 | 3    |

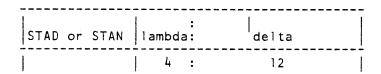

| (Cont)  | STAD and STAN (store delete/non-delete by means of address-couple)      | 3-   |

|         | Overwrite Operators                                                     | 3-   |

|         | OVRD (overwrite delete)                                                 | 3-   |

|         | OVRN (overwrite non-delete)                                             | 3-   |

|         | RDLK (read and lock)                                                    | 3-   |

|         | Interlock Operators                                                     | 3-   |

|         | LOK (lock interlock)                                                    | 3-   |

|         | UNLK (unlock interlock)                                                 | 3-   |

|         | LOKC (conditional lock interlock)                                       | 3-   |

|         | LKID (read interlock status)                                            | 3-   |

|         | Processor State Operators                                               | 3-   |

|         | Code Stream Pointer Distribution                                        | 3-   |

|         | aPRCW (distribute PCW/RCW code-stream pointer)                          | 3-   |

|         | Branching Operators                                                     | 3-   |

|         | Static Branches                                                         | 3-   |

|         | BRUN (branch unconditional)                                             | 3-   |

|         | BRTR and BRFL (branch true and branch false)                            | 3-   |

|         | Dynamic Branches                                                        | 3-   |

|         | DBUN (dynamic branch unconditional)                                     | 3-   |

|         | DBTR and DBFL (dynamic branch true and dynamic branch false)            | 3-   |

|         | Stack Structure Operators                                               | 3-   |

|         | Display Update                                                          | 3-   |

|         | Procedure Entry Operators                                               | 3-   |

|         | MKST (mark stack)                                                       | 3-   |

|         | MKSN (mark-stack bound to name-call)                                    | 3-   |

|         | IMKS (insert mark stack)                                                | 3-   |

|         | ENTR (enter)                                                            | 3-   |

|         | Completing the MSCW                                                     | . 3- |

|         | Constructing the RCW                                                    | . 3- |

|         | Initializing the Processor State                                        | . 3- |

|         | aACCE (accidental entry)                                                | . 3- |

|         | aINTE (interrupt entry)                                                 | . 3- |

|         | Procedure Exit Operators                                                | . 3- |

|         | EXIT (exit)                                                             | . 3- |

|         | RETN (return)                                                           | • 3- |

|         | Stack Environment Operator                                              | . 3- |

|         | MVST (move to stack)                                                    | . 3- |

|         | Deactivating the Current Stack                                          | . 3- |

|         | Changing the Addressing Environment and Identifying the Destination Sta |      |

|         | Restoring Destination Stack State                                       | _    |

|         | Updating the Lexical Environment State                                  |      |

|         | Top-of-Stack Operators                                                  | . 3- |

|         | DLET (delete top-of-stack)                                              | . 3- |

|         | EXCH (exchange top-of-stack)                                            |      |

|         | DUPL (duplicate top-of-stack)                                           | -    |

|         | RSUP (rotate stack up)                                                  | _    |

|         | (                                                                       | . 3- |

| Section | Title                                      |   |   |   |   |   |  |  |  |  |    | Page |

|---------|--------------------------------------------|---|---|---|---|---|--|--|--|--|----|------|

| 3       | RSDN (rotate stack down)                   |   |   |   |   |   |  |  |  |  |    | 3-65 |

| (Cont)  | Processor-State Manipulation Operators .   |   |   |   |   |   |  |  |  |  | ٠. | 3-65 |

|         | Read State Operators                       |   |   |   |   |   |  |  |  |  |    | 3-66 |

|         | RTFF (read true-false flip-flop)           |   |   |   |   |   |  |  |  |  |    | 3-66 |

|         | RSNR (read SNR)                            |   |   |   |   |   |  |  |  |  |    | 3-66 |

|         | WHOI (read processor id)                   |   |   |   |   |   |  |  |  |  |    | 3-66 |

|         | WATI (read machine identification)         |   |   | Ċ |   |   |  |  |  |  |    | 3-66 |

|         | RTOD (read time of day clock)              | Ċ |   |   |   |   |  |  |  |  |    | 3-67 |

|         | RPRR (read processor register)             |   |   |   |   |   |  |  |  |  |    | 3-67 |

|         | RIPS (read internal processor state)       |   |   |   |   |   |  |  |  |  |    | 3-67 |

|         | Set State Operators                        |   |   |   |   |   |  |  |  |  |    | 3-68 |

|         | SXSN (set external sign flip-flop)         |   |   |   |   |   |  |  |  |  |    | 3-68 |

|         | EEXI (enable external interrupts)          |   |   |   |   |   |  |  |  |  |    | 3-68 |

|         | DEXI (disable external interrupts)         |   |   |   |   |   |  |  |  |  |    | 3-68 |

|         | SINT (set interval timer)                  |   |   | • | • |   |  |  |  |  | -  | 3-68 |

|         | WTOD (write time of day clock)             | i |   | · |   |   |  |  |  |  |    | 3-68 |

|         | SPRR (set processor register)              | • | • | • | • | • |  |  |  |  |    | 3-69 |

|         | RUNI (indicate running)                    |   |   |   |   |   |  |  |  |  |    | 3-70 |

|         | WIPS (write internal processor state) .    |   |   |   |   |   |  |  |  |  |    | 3-70 |

|         | ZIC (zero Interrupt_Count)                 |   |   |   |   |   |  |  |  |  |    | 3-70 |

|         | Read and Set State Operator                |   |   |   |   |   |  |  |  |  |    | 3-70 |

|         | ROFF (read and reset overflow flip-flop)   |   |   |   |   |   |  |  |  |  |    | 3-70 |

|         | Data Array Operators                       |   |   |   |   |   |  |  |  |  |    | 3-71 |

|         | Searching Operators                        |   |   |   |   |   |  |  |  |  |    | 3-71 |

|         | LLLU (linked list lookup)                  |   |   |   |   |   |  |  |  |  |    | 3-71 |

|         | SRCH (masked search for equal)             |   |   |   |   |   |  |  |  |  |    | 3-72 |

|         | Pointer Operators                          |   |   |   |   |   |  |  |  |  |    | 3-73 |

|         | element_size conventions                   |   |   |   |   |   |  |  |  |  |    | 3-73 |

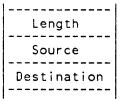

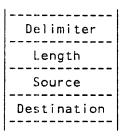

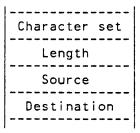

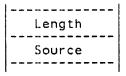

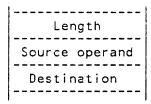

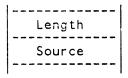

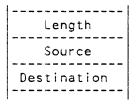

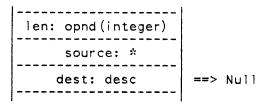

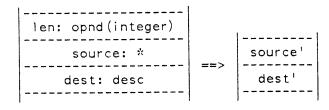

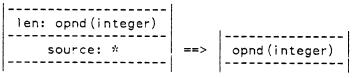

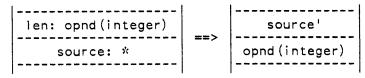

|         | Length Argument                            |   |   |   |   |   |  |  |  |  |    | 3-74 |

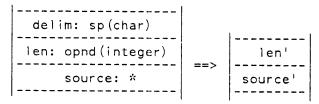

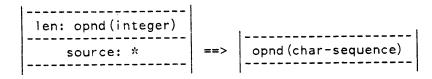

|         | Source Argument                            |   |   |   |   |   |  |  |  |  |    | 3-74 |

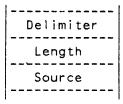

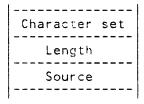

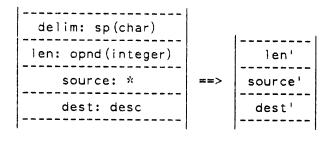

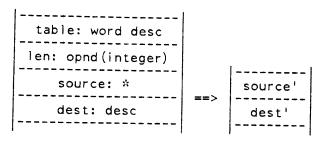

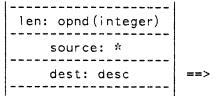

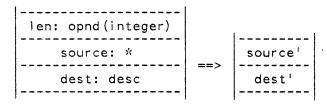

|         | Short-Source Operators                     |   |   |   |   |   |  |  |  |  |    | 3-74 |

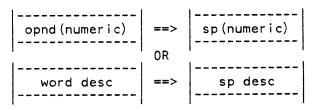

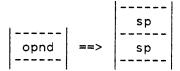

|         | Destination Argument                       |   |   |   |   |   |  |  |  |  |    | 3-75 |

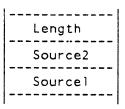

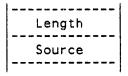

|         | Sourcel and Source2 Arguments              |   |   |   |   |   |  |  |  |  |    | 3-75 |

|         | Overlapping Source and Destination         |   |   |   |   |   |  |  |  |  |    | 3-75 |

|         | Update Of Pointer-Operator Arguments       |   |   |   |   |   |  |  |  |  |    | 3-77 |

|         | Unconditional Character-Transfer Operators |   |   |   |   |   |  |  |  |  |    | 3-78 |

|         | Character-Relational Operators             |   |   |   |   |   |  |  |  |  |    | 3-78 |

|         | Scan Operators                             |   |   |   |   |   |  |  |  |  |    | 3-79 |

|         | Transfer Operators                         |   |   |   |   |   |  |  |  |  |    | 3-80 |

|         | Character-Sequence Compare Operators .     |   |   |   |   |   |  |  |  |  |    | 3-81 |

|         | Character Set-Membership Operators         |   |   |   |   |   |  |  |  |  |    | 3-82 |

|         | Scan Operators                             |   |   |   |   |   |  |  |  |  |    | 3-82 |

|         | Transfer Operators                         |   |   |   |   |   |  |  |  |  |    | 3-83 |

|         | Character-Sequence Extraction Operator .   |   |   |   |   | • |  |  |  |  |    | 3-83 |

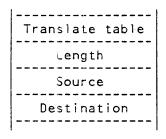

|         | Character Translate Operator               |   |   |   |   |   |  |  |  |  |    | 3-84 |

|         | Decimal-Character-Sequence Operators       |   |   |   |   |   |  |  |  |  |    | 3-85 |

|         | Pack Operators                             |   |   |   |   |   |  |  |  |  |    | 3-86 |

| Section | Title                                                | Page          |

|---------|------------------------------------------------------|---------------|

| 3       | Unpack Operators                                     | 3-87          |

| (Cont)  | Unpack-Unsigned Operators                            | 3-87          |

|         | Unpack-Signed Operators                              | 3-88          |

|         | Input-Convert Operators                              | 3-89          |

|         | Word-Transfer Operators                              | 3-90          |

|         | Word-Transfer-Protected Operators                    | 3-90          |

|         | Word-Transfer-Overwrite Operators                    | 3-90          |

|         | Primitive Display Operator                           | 3-91          |

|         | SHOW (primitive display)                             | 3-91          |

|         | Edit Operators                                       | 3-91          |

|         | Enter-Edit Operators                                 | 3-92          |

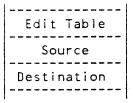

|         | Table edit-mode                                      | 3-92          |

|         | Single edit-mode                                     | 3-92          |

|         | Enter-Table-Edit Operators                           | 3-92          |

|         | Enter-Single-Edit Operators                          | 3-94          |

|         | Edit-Mode Operators                                  | 3-95          |

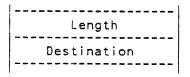

|         | Character Skip Operators                             | 3-95          |

|         | Skip Forward                                         | 3-95          |

|         | Skip Reverse                                         | 3-95          |

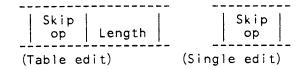

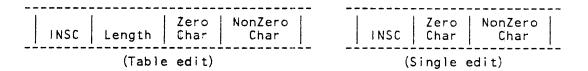

|         | Character Insert Operators                           | 3-96          |

|         | INSU (insert unconditional)                          | 3-96          |

|         | INSC (insert conditional)                            | 3-96          |

|         | INOP (insert overpunch)                              | 3-96          |

|         | INSG (insert display sign)                           | 3-96          |

|         | ENDF (end float)                                     | 3-97          |

|         | Character Move Operators                             | 3-97          |

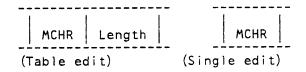

|         | MCHR (move characters)                               | 3-97          |

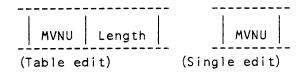

|         | MVNU (move numeric)                                  | 3-97          |

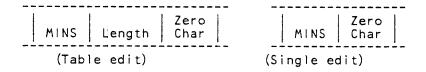

|         | MINS (move with insert)                              | 3-98          |

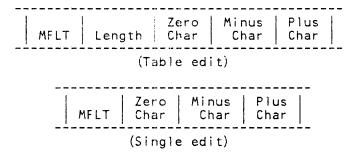

|         | MFLT (move with float)                               | 3-98          |

|         | Miscellaneous Edit Operators                         | 3-99          |

|         | RSTF (reset float flip-flop)                         | 3-99          |

|         | ENDE (end edit)                                      | 3-99          |

|         | External Communication Operators                     | 3-99          |

|         | CUIO (communicate with Universal I/O)                | 3-99          |

|         | SCNI/ SCNO (scan in/out) IDLE (idle until interrupt) | 3-99          |

|         | PAUS (pause until interrupt)                         | 3-99          |

|         | REMC (read external memory control)                  | 3 <b>-</b> 99 |

|         | WEMC (write external memory control)                 | 3-100         |

|         | Miscellaneous Operators                              | 3-100         |

|         | NOOP (no operation)                                  | 3-100         |

|         | DLAY (delay)                                         | 3-100         |

|         | PUSH (push working stack onto activation record)     | 3-100         |

|         | STOP (unconditional processor halt)                  | 3-101         |

|         | HALT (conditional processor halt)                    | 3-101         |

|         | NVLD (invalid operator)                              | 3-101         |

|         | ASRT (assert)                                        | 3-101         |

|         |                                                      |               |

| Section  |                                  | Titl | e |  |       |   |  |  |  |   | Page  |

|----------|----------------------------------|------|---|--|-------|---|--|--|--|---|-------|

| 3 (Cont) | VARI (introduce variant operator | r)   |   |  |       |   |  |  |  |   | 3-101 |

| 4        | INTERRUPTS                       |      |   |  |       |   |  |  |  |   | 4-1   |

|          | General Information              |      |   |  |       |   |  |  |  | • | 4-1   |

|          | Interrupt Parameters             |      |   |  | <br>۰ |   |  |  |  | • | 4-1   |

|          | Interrupt ID Parameter           |      |   |  |       |   |  |  |  | • | 4-1   |

|          | Resumption Conditions            |      |   |  |       |   |  |  |  |   | 4-6   |

|          | P2 parameter                     |      |   |  |       |   |  |  |  |   | 4-7   |

|          | Superhalt                        |      |   |  |       |   |  |  |  |   | 4-7   |

|          | Interrupt Definition             |      |   |  |       |   |  |  |  |   | 4-8   |

|          | Operator Dependent Interrupts    |      |   |  |       |   |  |  |  |   | 4-8   |

|          | MCP Service                      |      |   |  |       |   |  |  |  |   | 4-10  |

|          | Presence Bit                     |      |   |  |       |   |  |  |  |   | 4-10  |

|          | Paged Array                      |      |   |  |       |   |  |  |  |   | 4-10  |

|          | Binding Request                  |      |   |  |       |   |  |  |  |   | 4-11  |

|          | Stack Overflow                   |      |   |  |       |   |  |  |  |   | 4-12  |

|          | Block Exit                       |      |   |  |       |   |  |  |  |   | 4-12  |

|          | Locking and Unlocking            |      |   |  |       |   |  |  |  |   | 4-12  |

|          | Error Reporting                  |      |   |  |       |   |  |  |  |   | 4-12  |

|          | Invalid Operator                 |      |   |  |       |   |  |  |  |   | 4-13  |

|          | Undefined Operator               |      |   |  |       |   |  |  |  |   | 4-13  |

|          | Invalid Stack Argument           |      |   |  |       |   |  |  |  |   | 4-13  |

|          | Invalid Argument Value           |      |   |  |       |   |  |  |  |   | 4-14  |

|          | Invalid Code Parameter           |      |   |  |       |   |  |  |  |   | 4-14  |

|          | Invalid Reference                |      |   |  |       |   |  |  |  |   | 4-14  |

|          | Invalid Reference Chain          |      |   |  |       |   |  |  |  |   | 4-14  |

|          | Invalid Object                   |      |   |  |       |   |  |  |  |   | 4-16  |

|          | Invalid Index                    |      |   |  |       |   |  |  |  |   | 4-16  |

|          | Memory Protect                   |      |   |  |       |   |  |  |  |   | 4-17  |

|          | Divide by Zero                   |      |   |  |       | • |  |  |  |   | 4-17  |

|          | Exponent-Overflow                |      |   |  |       |   |  |  |  |   |       |

|          | Exponent-Underflow               |      |   |  |       |   |  |  |  |   | 4-18  |

|          | Precision Loss                   |      |   |  |       |   |  |  |  |   |       |

|          | Integer-Overflow                 |      |   |  |       |   |  |  |  |   |       |

|          | Stack-Underflow                  |      |   |  |       |   |  |  |  |   | 4-19  |

|          | Stack Structure Error            |      |   |  |       |   |  |  |  |   | 4-19  |

|          | Code Segment Error               |      |   |  |       |   |  |  |  |   | 4-20  |

|          | Invalid Program Word             |      |   |  |       |   |  |  |  |   | 4-20  |

|          | Page Structure Error             |      |   |  |       |   |  |  |  |   | 4-20  |

|          | False Assertion                  |      |   |  |       |   |  |  |  |   | 4-21  |

|          | Alarm Interrupts                 |      |   |  |       |   |  |  |  |   | 4-21  |

|          | Invalid Address                  |      |   |  |       |   |  |  |  |   | 4-21  |

|          | Uncorrectable Memory Error       |      |   |  |       |   |  |  |  |   | 4-21  |

|          | Loop Timer                       |      |   |  | <br>• | • |  |  |  |   | 4-22  |

|          | Hardware Error                   |      |   |  |       |   |  |  |  |   | 4-22  |

|          | External Interrupts              |      |   |  |       |   |  |  |  |   | 4-22  |

| Α        | OPERATOR SET                     |      |   |  |       |   |  |  |  |   | A-1   |

|          | General Information              |      |   |  |       |   |  |  |  |   | A-1   |

| Section | Title                                    | Page                           |

|---------|------------------------------------------|--------------------------------|

| В       | OPERATOR REFERENCE SUMMARIES             | . B-1                          |

| _       | General Information                      | . B-1                          |

|         | The Code-Stream Encoding Of The Operator | . B-1                          |

|         | Clients                                  | . B-1                          |

|         | Stack State Transformation               | . B-1                          |

|         | Interrupts That May Be Generated         | . B-1                          |

|         | Symbols Used In This Appendix            | . B-2                          |

|         | Operator and Common Action Listing       | . B-2<br>. B-3                 |

|         | aACCE                                    | . В-3                          |

|         | aCPY                                     | . В-3                          |

|         | aFOP                                     | . B-3                          |

|         | aINTE                                    | . В-4                          |

|         | aISX                                     | B-5                            |

|         | aLXCH                                    | B-5                            |

|         | aLXLK                                    | . В-5<br>В-6                   |

|         | aPRCW                                    | B-6                            |

|         | ADD                                      | . В-0<br>. В-7                 |

|         | AMAX                                     | . В-7<br>В-7                   |

|         | AMIN                                     | . В-7<br>. В-7                 |

|         | ASRT                                     | . В-7<br>. В-8                 |

|         | BCD                                      | . В-о<br>В-8                   |

|         | BRFL                                     | . В-о<br>. В-8                 |

|         | BRTR                                     | . <b>в-</b> о<br>. <b>В-</b> 9 |

|         | BRST                                     | . <b>в-</b> 9<br>. <b>В-</b> 9 |

|         | BRUN                                     | . <b>В-</b> 9<br>. <b>В-</b> 9 |

|         | BSET                                     | . <b>в-</b> 9<br>. <b>В-</b> 9 |

|         | CBON                                     | -                              |

|         | CEQD                                     | . В-9<br>. В-10                |

|         |                                          |                                |

|         | CEQU                                     | B-10                           |

|         | CGEU                                     | B-10                           |

|         |                                          | B-11                           |

|         | COTLI                                    | B-11                           |

|         | CHEN                                     | B-11                           |

|         | CLED                                     | B-11                           |

|         | CLEU                                     | B-11                           |

|         | CLEO                                     | B-11                           |

|         | CLSU                                     | B-12                           |

|         |                                          | B-12                           |

|         | CNED                                     | B-12                           |

|         | CUIO                                     | B-12                           |

|         |                                          | B-12                           |

|         | DBCD                                     | B-13                           |

|         | DBFL                                     | B-13                           |

|         | DBRS                                     | B-13                           |

|         | DBST                                     | B-14                           |

|         | DBTR                                     | B-14                           |

|         | DBUN                                     | B-14                           |

| Section  |        | Title |           | Page         |

|----------|--------|-------|-----------|--------------|

| B (Cont) | DEXI   |       |           | B-14         |

| _ ( ,    | DFTR   |       |           | B-15         |

|          | DINS . |       |           | B-15         |

|          | DISO . |       |           | B-16         |

|          | DIVD   |       |           | B-16         |

|          | DLAY   |       |           | B-16         |

|          | DLET   |       |           | B-17         |

|          | DRNT   |       |           | B-17         |

|          | DSLF   |       |           | B-17         |

|          | DSRF   |       |           | B-18         |

|          | DSRR   |       |           | B-18         |

|          | DSRS   |       |           | B-18         |

|          | DSRT   |       |           | B-19         |

|          | DUPL   |       |           | B-19         |

|          | EEXI . |       |           | B-19         |

|          | ENDE   |       |           | B-19         |

|          |        |       |           | B-20         |

|          | ENDF   |       |           | B-21         |

|          | ENTR   |       |           | B-21<br>B-22 |

|          | EQUL   |       |           | B-22         |

|          | EVAL   |       |           |              |

|          | EXCH   |       |           | B-22         |

|          | EXIT.  |       |           | B-23         |

|          | EXPU   |       |           | B-24         |

|          | EXSD   |       |           | B-24         |

|          | EXSU   |       |           | B-25         |

|          | FLTR   |       |           | B-25         |

|          | GREQ   |       |           | B-25         |

|          | GRTR   |       |           | B-25         |

|          | HALT   |       |           | B-26         |

|          | ICLD . |       |           | B-26         |

|          | ICRD   |       | ·         | B-26         |

|          | ICUD   |       |           | B-26         |

|          | ICVD   |       |           | B-27         |

|          | ICVU   |       |           | B-27         |

|          | IDIV . |       |           | B-27         |

|          | IDLE . |       |           | B-27         |

|          | IMKS   |       |           |              |

|          | INDX   |       |           |              |

|          | INOP   |       |           |              |

|          | INSC . |       |           |              |

|          | INSG . |       |           |              |

|          | INSR . |       |           |              |

|          | INSU . |       |           | B-31         |

|          | INXA   |       |           | B-32         |

|          | ISOL . |       | . <b></b> | B-32         |

|          | JOIN . |       | . <b></b> | B-33         |

|          | LAND   |       |           | B-33         |

| Section  |               |     |     |   |   |     |   | 7 | fitle | e |   |     |   |   |   |   |   |   |    |     |   |   |   | Page                     |

|----------|---------------|-----|-----|---|---|-----|---|---|-------|---|---|-----|---|---|---|---|---|---|----|-----|---|---|---|--------------------------|

| B (Cont) | LEQV          |     |     |   |   |     |   |   |       |   |   |     |   |   |   |   |   |   |    |     |   |   |   | . В-33                   |

|          | LESS .        |     |     | · | · | •   | • | • | •     | • | • | • • | • | • | • | • | • | • | ٠. | •   | • | • | • | . B-33                   |

|          | LKID .        |     |     | • | • |     | • | • | •     | • | • | • • | • | • | • | • | • | • | •• | •   | • | • | • | . B-34                   |

|          | LLLU          |     |     | • | • | • • | • | • | •     | • | • |     | • | • | ٠ | • | • | • | •  | •   | • | • | • | . B-34                   |

|          | LNMC          |     | • • | • | • | •   | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . B-35                   |

|          | LNOT          |     |     | • | • | •   | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-35                   |

|          | LOAD          | •   | • • | • | • | •   | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . B-35                   |

|          | LODT          |     |     | • | • | •   | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-36                   |

|          | LOG2          |     |     | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . В-36                   |

|          | LOK .         |     | •   | • | • | •   | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-36                   |

|          | LOKC          |     |     | · | • | •   | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | B-37                     |

|          | LOR .         | • • | • • | • | • | • • | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . В-37                   |

|          | LSEQ .        | • • | • • | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | B-37                     |

|          | LT8 .         | • • | • • | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | B-37                     |

|          | LT16 .        | • • |     | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | • . | • | ٠ | • | . B-37                   |

|          | LT48 .        |     |     | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | B-38                     |

|          | LVLC .        | • • | • • | • | • | • • | • | • | ٠     | • | • |     | • | • | ٠ | • | • | • | •  | •   | • | • | • | . В-38<br>. В-38         |

|          | MCHR          | • • | • • | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-38                   |

|          | MFLT          | • • |     | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-38                   |

|          | MINS          | • • | • • | • | • | • • | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . В-36<br>. В-39         |

|          | MKSN          | • • | • • | • | • |     | • | • | •     | • | • |     | • | ٠ | • | • | • | • | •  | •   | • | • | ٠ | . B-39                   |

|          | MKST          | • • | • • | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . В-39<br>. В-39         |

|          | MPCW          |     | • • | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | ٠ | . В-39<br>. В-40         |

|          | MULT          |     | • • | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-40                   |

|          | MULX          |     | • • | • | • | • • | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . В-40<br>. В-40         |

|          | MVNU          | • • | • • | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . В-40<br>. В-41         |

|          | MVST          |     |     | • | • |     | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . B-41<br>. B-42         |

|          | NAMC          | • • |     | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-42                   |

|          | NEQL          |     |     | • | • |     | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . В-43<br>. В-43         |

|          | NOOP          | • • | • • | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . В-43<br>. В-43         |

|          | NORM          | • • |     | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . В-43<br>. В-43         |

|          | NTGD          | • • |     | • | • |     | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | ٠ | • | • |                          |

|          | NTGR          |     | • • | • | • |     | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • | • | . B-44<br>. B-44         |

|          | NTIA          | • • | • • | • | • | • • | • | ٠ | •     | • | • |     | • | • | • | • | • | • | •  | •   | ٠ | • | • | . B-44                   |

|          | NTTD          | • • |     | • | • |     | • | • | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . B-44<br>. B-44         |

|          | NVLD          | • • | • • | • | • |     | • | ٠ | •     | • | • |     | • | ٠ | • | • | • | • | •  | •   | • | ٠ | • | . В-44<br>. В-45         |

|          | NXLN          |     | • • | • | • | • • | • | ٠ | •     | • | • | • • | • | • | • | • | • | • | •  | •   | • | • | • | . В-45<br>. В-45         |

|          | NXLV          | • • | • • | • | • | • • | • | • | •     | • | • |     | • | • | • | • | • | • | •  | •   | • | • |   | . <b>В-4</b> 3           |

|          | NXVA          | • • | • • | • | • | • • | • | • | ٠     | • | • |     | • | • | • | • | • | • | •  | •   | ٠ | • | • | . <b>В-4</b> 0<br>. В-47 |

|          | OCRX          | • • | • • | • | • |     | • | • | ٠     | • | • |     | • | • | • | • | • | • | •  | •   | ٠ | • | • | . B-47                   |

|          | OCKA<br>ONE . | • • | • • | ٠ | • |     | • | • | •     | • | • |     | • | • | ٠ | • | ٠ | • | •  | •   | • | • | • | . <b>В-4</b> /           |

|          |               | • • |     | • | • |     | • | • | •     | • | • | •   | • | • | • | • | • | • | ٠  | •   | • | • | • | . В-48                   |

|          | OVRD<br>OVRN  | • • | • • | • | • |     | • | • | •     | • | • | •   | • | • | • | • | • | • | •  | •   | • | • | • | . B-48<br>. B-48         |

|          | PACD          | • • | • • | ٠ | • | • • | ٠ | • | •     | • | • | • • | • | • | • | • | • | ٠ | •  | •   | • | • | • | . B-48<br>В-48           |

|          | PACU          | • • | • • | ٠ | • |     | • | • | •     | • | • | •   | • | • | • | • | • | • | •  | •   | • | • | • | B-48<br>B-49             |

|          | PACU          | • • | • • | ٠ | • |     | • | • | •     | • | • | •   | • | • | • | • | • | • | •  | •   | • | • | • | B-49                     |

|          |               | • • | • • | ٠ | • | • • | • | • | •     | • |   | •   | • | ٠ | ٠ | ٠ | • | • | •  | •   | • | • | ٠ |                          |

|          | PKLD          |     |     |   |   |     |   |   |       |   |   |     |   |   |   |   |   |   |    |     |   |   |   | . B-49                   |

| Section  | <b>V</b> |   |   |   |   |   |   |   |   |   | 1 | [itl | e  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Page         |

|----------|----------|---|---|---|---|---|---|---|---|---|---|------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--------------|

| B (Cont) | PKRD     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-49         |

| _ (/     | PKUD     | • | • | • | • |   | • |   |   | _ | _ |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-50         |

|          | PUSH     | • | • | • | • | • | • | • | • | • | • | Ĭ.   | Ĭ. |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-50         |

|          | RDIV     | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • |   | _ |   |   |   |   |   |   |   | B-50         |

|          |          | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | Ī | i | B-51         |

|          | RDLK     | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-51         |

|          | REMC     | • | • | • | • | • | • | • | • | • | ٠ | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-52         |

|          | RETN     | • | • | • | • | • | • | • | ٠ | • | ٠ | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-52         |

|          | RIPS .   | • | • | • | • | • | • | • | • | • | • | •    | •  | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | • | B-52<br>B-53 |

|          | RNGT     | • |   | • | • | • | ٠ | • | • | • | • | •    | •  | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-53         |

|          | ROFF     |   |   |   |   | • |   | • |   | • | • | •    | •  | • | ٠ | • | • | • | ٠ | • | • | • | • | • | ٠ | • | • | • |              |

|          | RPRR     |   |   |   |   |   |   |   |   |   |   |      | ٠  |   |   | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | B-53         |

|          | RSDN     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   | • | • | • | • | • | • | • | B-54         |

|          | RSNR     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   | • |   |   | • | • |   | • | B-54         |

|          | RSTF .   |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-54         |

|          | RSUP     | _ |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-54         |

|          | RTAG     | · |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-55         |

|          | RTFF     | • | • | • |   | • |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-55         |

|          | RTOD     | • | • | • | • | • | • | • | • | • | • | ·    | •  | · |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-55         |

|          | RUNI     | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | į |   |   |   |   |   |   |   |   |   |   |   | B-55         |

|          |          | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • |   | • |   |   |   |   | B-56         |

|          | SAME     | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • |   | • | • | • | • | • | B-56         |

|          | SCLF.    | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | ۰ | • | • | • | • | • | B-56         |

|          | SCRF     | • | • | • | • | • | • | • | • | ٠ | ٠ | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-50<br>B-57 |

|          | SCRR     | • | • | ٠ | • | • | • | • | • | • | ٠ | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-57         |

|          | SCRS .   |   |   |   | • |   | • | • | • | • | ٠ | •    | •  | • | • | • | ٠ | • | ٠ | • | ٠ | • | • | • | • | • | • | • |              |

|          | SCRT     |   |   |   |   |   |   |   | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-57         |

|          | SEQD     |   |   |   |   |   |   |   |   | • | • | •    |    |   | • |   | • | • | • | • | • | • | • | • | • | ٠ | • | • | B-58         |

|          | SEQU     |   |   | • |   |   |   |   |   |   |   |      |    |   | • |   | • |   | • | • |   | • | • | • | • | • | • | • | B-58         |

|          | SFDC     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   | • |   | • | • |   | • | • | B-58         |

|          | SFSC .   |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-59         |

|          | SGED     | _ |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-59         |

|          | SGEU     | Ī |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-59         |

|          | SGTD     | • | • | • | • | • | • | · | Ī | Ī |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-59         |

|          | SGTU     | • | • | • | • | • | • | • | • | • | • | ·    | ·  | • | · |   |   |   |   |   |   |   |   |   |   |   |   |   | B-59         |

|          | SHOW     | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | · |   |   |   |   |   |   |   |   |   |   | B-60         |

|          |          | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | · | · | · |   |   | B-60         |

|          | SINT .   | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-61         |

|          | SISO .   | • | • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • |   | D (1         |

|          | SLED     | • | • | • | • | ٠ | • | • | ٠ | • | • | •    | ٠  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-61         |

|          | SLEU     | • | • | • | ٠ | • | • | • | • | • | • | •    | •  | • | • | ٠ | ٠ | • | • | • | • | • | • | • | • | • | • | • | D (2         |

|          | SLSD .   |   | • | ٠ | • | • | • | • | • | ٠ | • | •    | •  | • | • | • | • | • | ٠ | • | ٠ | • | ٠ | • | ٠ | • | • | • | B-62         |

|          | SLSU .   |   |   |   |   | • |   | • | • | • |   | •    | •  | • | • | ٠ | • | • | • | • | ٠ | • | • | • | • | • | • | • |              |

|          | SNED     |   |   |   |   |   |   |   |   |   |   |      |    |   | • |   | • | • | • | • | • | • | • | ٠ | • | • | • | • | B-62         |

|          | SNEU     |   |   |   |   |   |   |   |   |   |   |      |    |   | • |   |   |   |   | • | • | • | • | • | • | • | • | • | B-62         |

|          | SNGL     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   | ٠ |   | • | • | • |   |   |   | B-62         |

|          | SNGT     |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-63         |

|          | SPLT .   |   |   |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-63         |

|          | SPRR     |   |   |   |   |   |   |   |   | 4 |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-64         |

|          | SRCH     | • |   | - | - |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-64         |

|          | SRDC     | • | • | • | • | • | • |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-64         |

|          | DILLO    | • | • | • | • | • | • | • | • | • | • | •    |    | • | - | - | - | - |   |   |   |   |   |   |   |   |   |   |              |

| Section  |             |     |   |   |   |   |   |   |   | 7 | Γitl | le |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | Page |

|----------|-------------|-----|---|---|---|---|---|---|---|---|------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| B (Cont) | SRSC .      |     |   |   |   |   |   |   | • |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-65 |

|          | STAD        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-65 |

|          | STAG        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-66 |

|          | STAN        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-66 |

|          | STFF.       |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-66 |

|          | STOD        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-67 |

|          | STON        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-68 |

|          | STOP        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-68 |

|          | SUBT        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-68 |

|          | SWFD        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-69 |

|          | SWFU        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-69 |

|          | SWTD        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-69 |

|          | <b>SWTU</b> |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | B-70 |

|          | SXSN        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   | į | B-70 |

|          | TEED        |     |   |   |   |   |   |   |   |   |      |    |   |   |   |   |   |   |   |   |   |   |   | - | · |   | • | B-70 |

|          | TEEU        |     |   |   |   |   |   |   |   |   |      |    |   | · |   |   | • |   |   |   |   | • | • | • | • |   | · | B-71 |

|          | TEQD        |     |   |   |   |   | · |   |   |   | •    | ·  | · | · | • | · | Ċ | · | • | Ī | • | • | • | • | • | • | • | B-71 |

|          | TEQU        |     |   |   |   |   |   | • |   | · | •    | •  | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | B-72 |

|          | TGED        |     | • | i | • | • | • | • | • | · | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-72 |

|          | TGEU        |     |   |   |   |   |   |   |   | i | •    | •  | Ī | • | · | · | Ċ | • | • | • | • | • | • | • | • | • | • | B-72 |

|          | TGTD        |     |   |   | • | • |   | • | · | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-72 |

|          | TGTU        |     | • |   | • | • | • | • | · | • | •    | •  | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | B-72 |

|          | TLED        |     | • |   |   |   |   | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | B-72 |

|          | TLEU        |     |   |   |   |   |   |   |   |   |      |    |   | · | Ċ |   | • | • | • | • | • | • | • | • | • |   | Ċ | B-73 |

|          | TLSD        |     |   |   |   |   |   | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-73 |

|          | TLSU        |     |   |   |   |   |   |   |   |   | •    |    | • | · | Ċ | · | • | · | • | · | · | · | · | • | · | · | • | B-73 |

|          | TNED        |     | • | • | • |   |   | • | • | • | •    | ·  | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | B-73 |

|          | TNEU        |     |   |   |   |   |   |   |   | • |      |    |   |   | • | Ċ | • | • | • | • | • | • | · | · | • | • | • | B-73 |

|          | TRNS        |     | • |   | • |   | • |   | Ċ |   | ·    | •  | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | B-74 |

|          | TUND        |     | • | • |   |   | • | • | • | • | •    | •  | • | • | • | • |   | • |   | • | • | • | • | • | • | • | • | B-75 |

|          | TUNU        |     | • | • | • | • | • | • | • | • | •    |    |   |   | • | • | • | • | • | • | • | • | • | • | • | • | • | B-75 |

|          | TWFD        |     | • |   | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-76 |

|          | TWFU        |     | • |   | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-76 |

|          | TWOD        |     | • | • | • | • | • | • | • | • | •    |    | • | • |   | • |   |   | • |   | • | • | • | • | • | • | • | B-77 |

|          | TWOU        |     | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-77 |

|          | TWSD        |     | į | • | • | • | • | • | • |   | •    | •  | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | B-78 |

|          | TWSU        |     | · | • | • | • | • | • | • | • | •    | :  |   | • | • | • | • | • | • | ٠ | • | • | • | • | • | • | • | B-78 |

|          | TWTD        | •   | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • |   | • | B-79 |

|          | TWTU        | • • | • | • | • | • | • | • | • | • | •    | •  | • | : | • | • | • | • | • | • | • | • | • | • |   |   | • | B-79 |

|          | UNLK        | • • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | ٠ | • | • | • | • | • | • | • |   |   | B-79 |

|          | UPLD        | • • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-79 |

|          | UPLU        | • • | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-79 |

|          | UPRD        |     | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | B-79 |

|          | UPRU        |     | • | • | • | • |   | • | • | • | •    | •  | • | • | • | • | • | • |   | • | • | • | • | • | • | • | • | B-80 |

|          | UPUD        |     | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-80 |

|          | UPUU        |     | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-80 |

|          | USND        |     | • | • | • | • | • | • | • | • | •    | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | B-81 |

|          | USNU        |     |   |   |   |   |   |   | • |   |      | •  |   |   |   |   |   |   | : | • |   |   |   |   |   | • |   | B-81 |

| Section  | Title                                              | Page |

|----------|----------------------------------------------------|------|

| B (Cont) | VALC                                               | B-81 |

|          | VARI                                               | B-81 |

|          | WATI                                               | B-82 |

|          | WEMC                                               | B-82 |

|          | WHOI                                               | B-82 |

|          | WIPS                                               | B-82 |

|          | WTOD                                               | B-83 |

|          | XTND                                               | B-83 |

|          | ZERO                                               | B-83 |

|          | ZIC                                                | B-83 |

| C        | OPERATOR DEPENDENT INTERRUPT REFERENCE SUMMARIES . | C-1  |

|          | General Information                                | C-1  |

|          | Binding Request                                    | C-2  |

|          | Block Exit                                         | C-2  |

|          | Code Segment Error                                 | C-2  |

|          | Divide by Zero                                     | C-2  |

|          | Exponent Overflow                                  | C-2  |

|          | Exponent Underflow                                 | C-3  |

|          | False Assertion                                    | C-3  |

|          | Integer Overflow                                   | C-3  |

|          | Invalid Argument Value                             | C-5  |

|          | Invalid Code Parameter                             | C-6  |

|          | Invalid Index                                      | C-6  |

|          | Invalid Object                                     | C-8  |

|          | Invalid Operator                                   | C-9  |

|          | Invalid Reference                                  | C-9  |

|          | Invalid Reference Chain                            | C-10 |

|          | Invalid Stack Argument                             | C-10 |

|          | Locking                                            | C-13 |

|          | Memory Protect                                     | C-13 |

|          | Paged Array                                        | C-14 |

|          | Page Structure Error                               | C-15 |

|          | Precision Loss                                     | C-16 |

|          | Presence Bit                                       | C-16 |

|          | Stack Overflow                                     | C-17 |

|          | Stack Structure Error                              | C-18 |

|          | Stack Underflow                                    | C-18 |

|          | Undefined Operator                                 | C-19 |

|          | Unlocking                                          | C-19 |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                      | Page        |

|--------|------------------------------------------------------------|-------------|

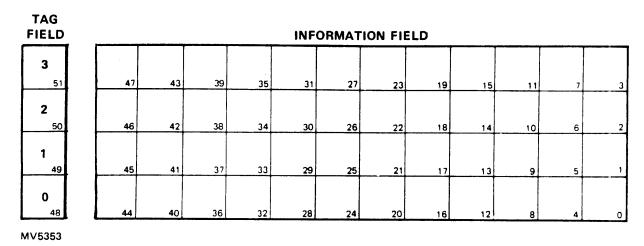

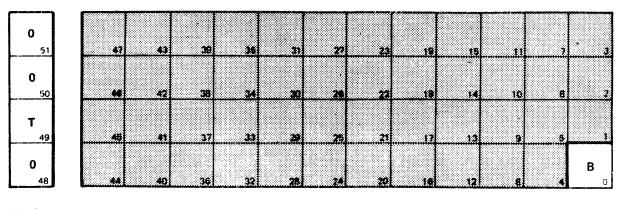

| 1-1    | Word Format                                                | . 1-1       |

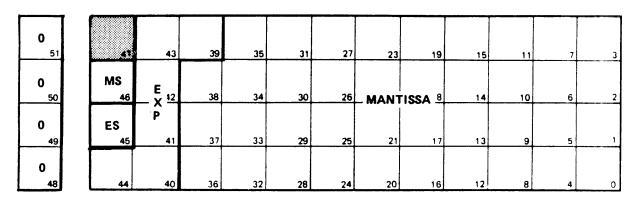

| 1-2    | Single Precision Operand Format                            | . 1-3       |

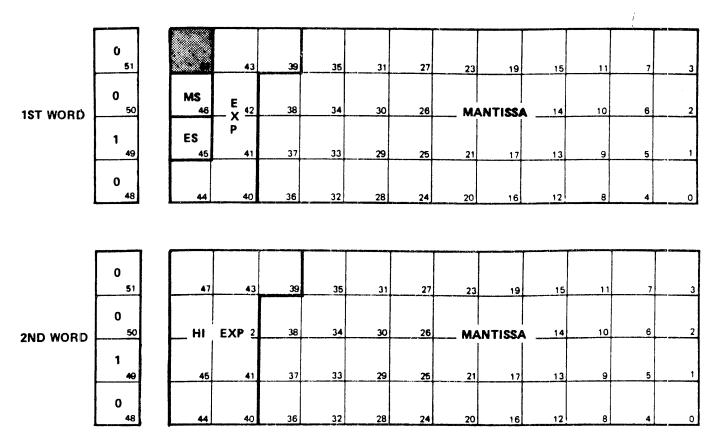

| 1-3    | Double Precision Operand Format                            |             |

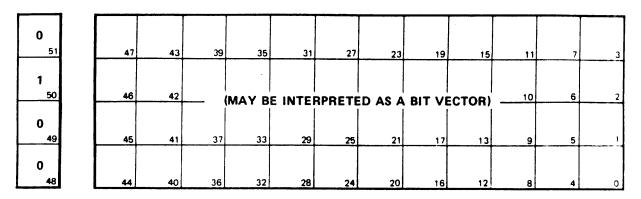

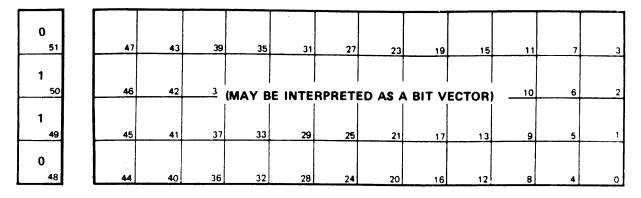

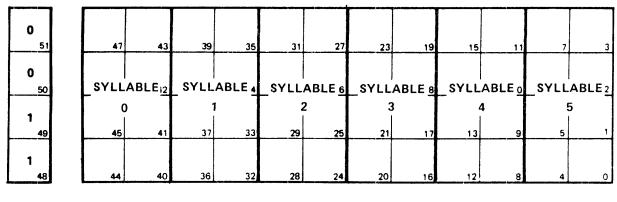

| 1-4    | Boolean Operand Format                                     | 1-6         |

| 1-5    | Tag-4 Word Format                                          | . 1-7       |

| 1-6    | Tag-6 Word Format                                          | 1-7         |

| 1-7    | Program Code Word Format                                   | 1-8         |

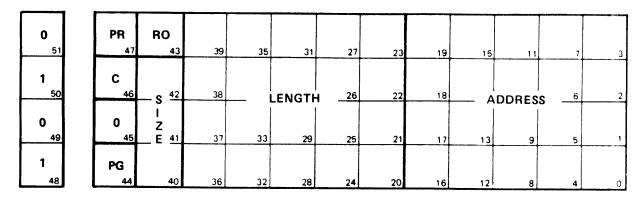

| 1-8    | Data Descriptor Format                                     | 1-9         |

| 1-9    | Code Segment Descriptor Format                             | . 1-11      |

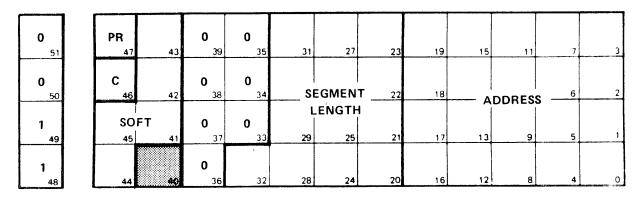

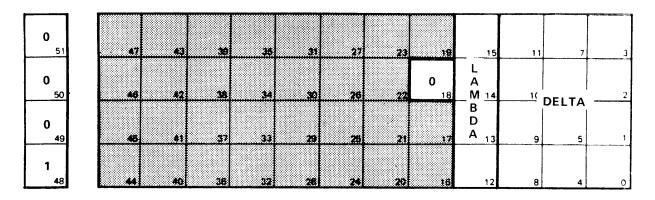

| 1-10   | Normal Indirect Reference Word Format                      |             |

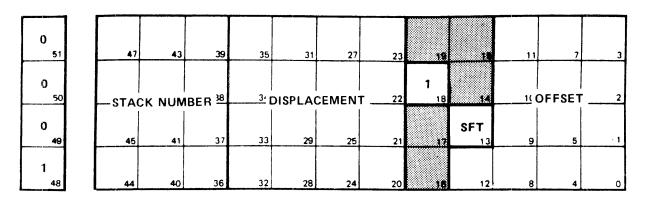

| 1-11   | SIRW Word Format                                           |             |

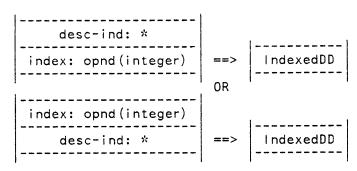

| 1-12   | Indexed Word Data Descriptor Format                        |             |

| 1-13   | Indexed Character Data Descriptor (Pointer) Format         |             |

| 1-14   | Program Control Word Format                                |             |

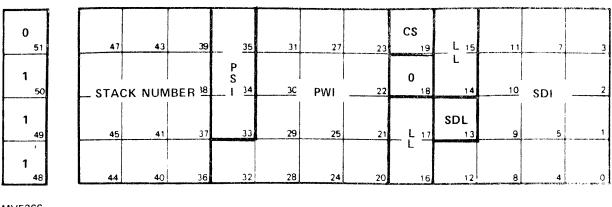

| 1-15   | Mark Stack Control Word (MSCW) Format                      | . 1-18      |

| 1-16   | Return Control word (RCW) Format                           | . 1-19      |

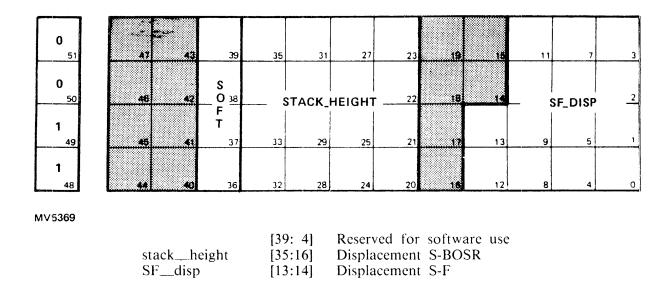

| 1-17   | Top Of Stack Control Word (TSCW) Format                    | . 1-20      |

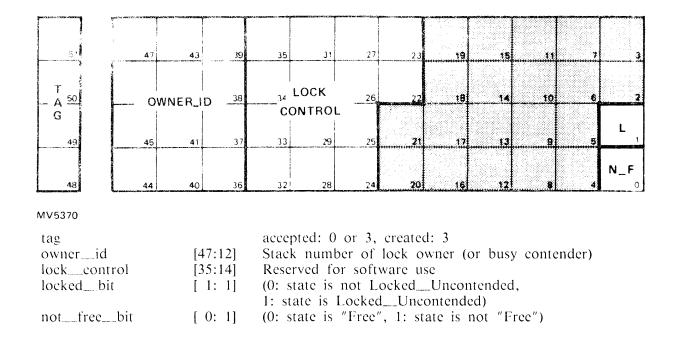

| 1-18   | Interlock Control word Format                              | . 1-21      |

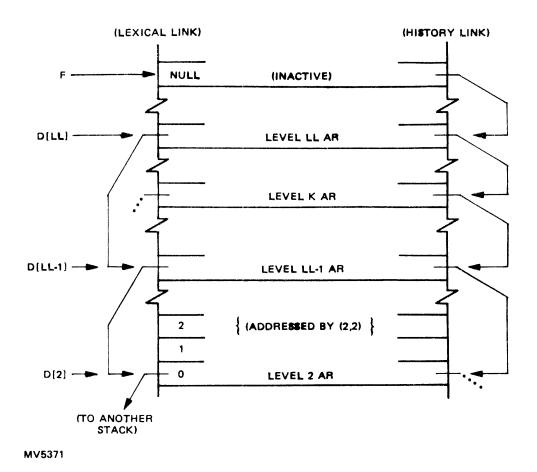

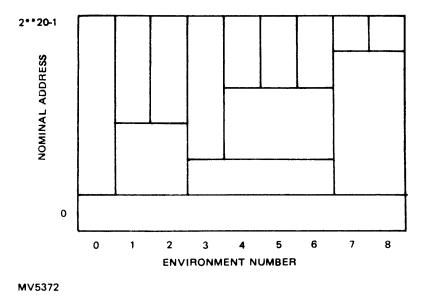

| 2-1    | Addressing environment example                             | 2-4         |

| 2-2    | Memory Environment Mapping                                 | 2-5         |

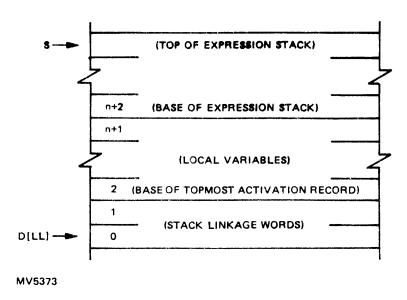

| 2-3    | Topmost Activation Record Example                          |             |

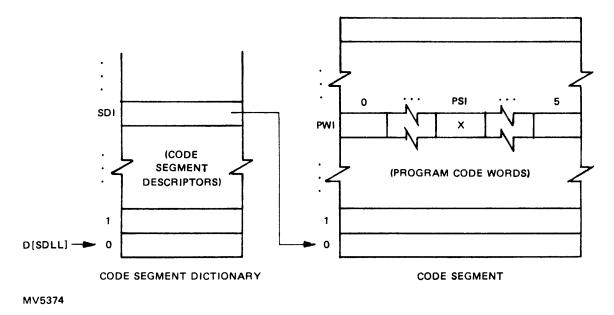

| 2-4    | Processor Code Stream Pointer                              |             |

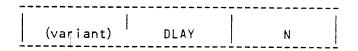

| 4-1    | P-1 Operator Dependent Interrupt (ODI) ID Parameter Format | 4-2         |

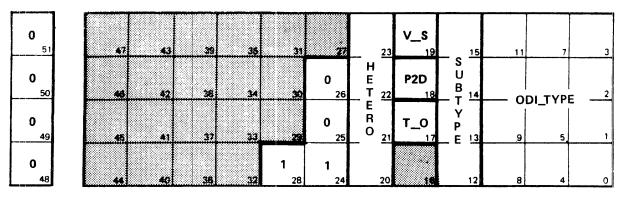

| 4-2    | P-1 Alarm Interrupt ID Parameter Format                    | 4-3         |

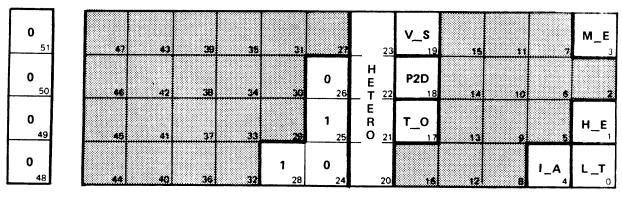

| 4-3    | P-1 External Interrupt ID Parameter Format                 |             |

|        | LIST OF TABLES                                             |             |

| Гable  | Title                                                      | Page        |

| 1 1    | Adduses Counts Force Deceding                              |             |

| 1-1    | Address Couple Fence Decoding                              | 1-12        |

| A-1    | Operators, Alphabetical List                               | A-1         |

| A-2    | Operators, Numerical List                                  | <b>A-</b> 6 |

5014954 xix

### INTRODUCTION

This manual describes and defines an architecture used in Burroughs Corporation data processing system products. Products that include architecture described in this manual are essentially compatible with each other, including four generations of prior system products. It is intended that this tradition extend to systems developed in the future.

"Essentially compatible", as used in this manual, means that programs written to process on one system also process on other systems sharing the same architectural design. Any reprogramming or adaptation to process a program on a similar system architecture will be of a minor nature. Programs originally written for execution on a prior generation system may require adaptation to account for present-day peripheral devices, which did not exist when the prior system architecture was designed. This is also true when adapting a present-day program to execute on a prior system design architecture.