# Burroughs

B 5281

PROCESSOR

TRAINING MANUAL

PROPERTY OF AND TO BE RETURNED TO

Burroughs

#### TABLE OF CONTENTS

| SECTION                                            | TITLE                                                                                                                                                                                                                                   |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1.1<br>1.2                                    | INTRODUCTION  General  Physical Orientation                                                                                                                                                                                             |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | LOGICAL IMPLEMENTATION Operator Control Level Coding Memory Access B Register Alignment Parallel Adder Serial Decimal Adder Input Convert: B29T Output Convert: B30T                                                                    |

| 3<br>3.1<br>3.2<br>3.3<br>3.4                      | WORD MODE OPERATIONAL FLOWS Logical AND Logical OR Logical EQUIVALENCE Logical NEGATE Relational Operators Compare: B Greater than A B Greater than or Equal to A B Equal to A B Less than or Equal to A B Less than A B Not Equal to A |

| 3.5                                                | Branch Forward/Backward Unconditional                                                                                                                                                                                                   |

| 3.6                                                | Branch Forward/Backward Conditional<br>Branch Return Operator                                                                                                                                                                           |

| 3.7<br>3.8                                         | Store Destructive/Non-Destructive                                                                                                                                                                                                       |

|                                                    | Integer Store Destructive/Non-Destructive:                                                                                                                                                                                              |

| 3.9                                                | Unconditional - Conditional                                                                                                                                                                                                             |

| 3.10                                               | Dial A - Dial B                                                                                                                                                                                                                         |

| 3.11                                               | Transfer Bits                                                                                                                                                                                                                           |

| 3.12                                               | Compare Field Equal                                                                                                                                                                                                                     |

| 3.13                                               | Compare Field Low                                                                                                                                                                                                                       |

| 3.14                                               | Set Flag Bit/Reset Flag Bit                                                                                                                                                                                                             |

| 3.15                                               | Test Flag Bit/Interrogate Peripheral Status/Interrogate I/O Channel                                                                                                                                                                     |

| 3.16                                               | Reset Sign Bit/Set Sign Bit/Change Sign Bit/Stack Search for Flag                                                                                                                                                                       |

| 3.17                                               | Single Precision Add/Subtract                                                                                                                                                                                                           |

| 3 <b>.1</b> 8                                      | Single Precision Multiply                                                                                                                                                                                                               |

| 3 <b>.1</b> 9                                      | Single Precision Divide                                                                                                                                                                                                                 |

| 3.20                                               | Integer Divide                                                                                                                                                                                                                          |

| 3.21                                               | Remainder Divide                                                                                                                                                                                                                        |

| 3.22                                               | Double Precision Add/Subtract                                                                                                                                                                                                           |

| 3.23                                               | Double Precision Multiply                                                                                                                                                                                                               |

| 3.24                                               | Double Precision Divide                                                                                                                                                                                                                 |

| 3.25                                               | Exponential Arithmetic                                                                                                                                                                                                                  |

| 3.26                                               | Mark Stack, Enter Character Mode EXIT                                                                                                                                                                                                   |

| 3 <b>.2</b> 7                                      | EVII                                                                                                                                                                                                                                    |

## TABLE OF CONTENTS (Continued)

| SECTION                                                                                                                              | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.28<br>3.29<br>3.30<br>3.31<br>3.32<br>3.33<br>3.34<br>3.35                                                                         | Return Normal/Return Special Exchange Duplicate Load Index Construct Operand/Descriptor Call Branch Forward/Backward/Non-destructive/Destructive/Delete Variable Field Isolate                                                                                                                                                                                                                                                   |

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                          | CHARACTER MODE OPERATIONAL FLOWS  Transfer Source Characters Transfer Source Zone Transfer Source Numerics Transfer Program Characters/Transfer Blanks for Non-numerics Transfer Words Test Operators Test for: Equal  Greater than or Equal to Less than or Equal to Greater Less Not Equal                                                                                                                                     |

| 4.7<br>4.8<br>4.9                                                                                                                    | Not Equal Test for Alphanumeric Test Bit Comparison Operators Compare for: Equal Not Equal Greater or Equal Greater Equal or Less                                                                                                                                                                                                                                                                                                |

| 4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17<br>4.18<br>4.19<br>4.20<br>4.21<br>4.22<br>4.22<br>4.22<br>4.25<br>4.26 | Less Field Add/Subtract Jump Forward Unconditional/Conditional Jump Reverse Unconditional/Conditional Begin Loop End Loop Jump Out of Loop Unconditional/Conditional Skip Forward/Reverse Source Skip Forward Destination Skip Reverse Destination Skip Bit Source Skip Bit Destination Store Source Address Store Destination Address Store Control Address Recall Source Address Recall Control Address Recall Control Address |

## TABLE OF CONTENTS (Continued)

| TITLE                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Source Address Set Destination Address Transfer Source Address Transfer Destination Address Input Convert Output Convert Set Tally/Increase Tally/Character Mode No-Op Store Tally Reset Bit Set Bit                                                                                                                           |

| Call Repeat Field Exit Character Mode/In-Line Exit Character Mode                                                                                                                                                                                                                                                                  |

| CONTROL STATE AND MISCELLANEOUS OPERATORS Communicate Program Release - I/O Release Interrogate Interrupt Store for Interrupt - Store for Test Initiate Pl - Initiate Test Initiate P2 - Initiate I/O Halt P2 Syllable Read Timer Literal Syllable Operand/Descriptor Call Syllable Conditional Stop Syllable Interface SECL/Fetch |

|                                                                                                                                                                                                                                                                                                                                    |

### LIST OF ILLUSTRATIONS

| FIGURE          | TITLE                                                          | PAGE           |

|-----------------|----------------------------------------------------------------|----------------|

| 1.2-1           | DP-A and DP-B Main Frame Location                              | 1.2-1          |

| 1.2-2           | Main Frame with Processor Opened                               | 1.2-2          |

| 1.2-3           | Processor Rack Layout                                          | 1.2-3          |

| 1.2-4           | Panel Layout Wiring Side                                       | 1.2-4          |

| 1.2-5           | Processor Display Panel                                        | 1.2-6          |

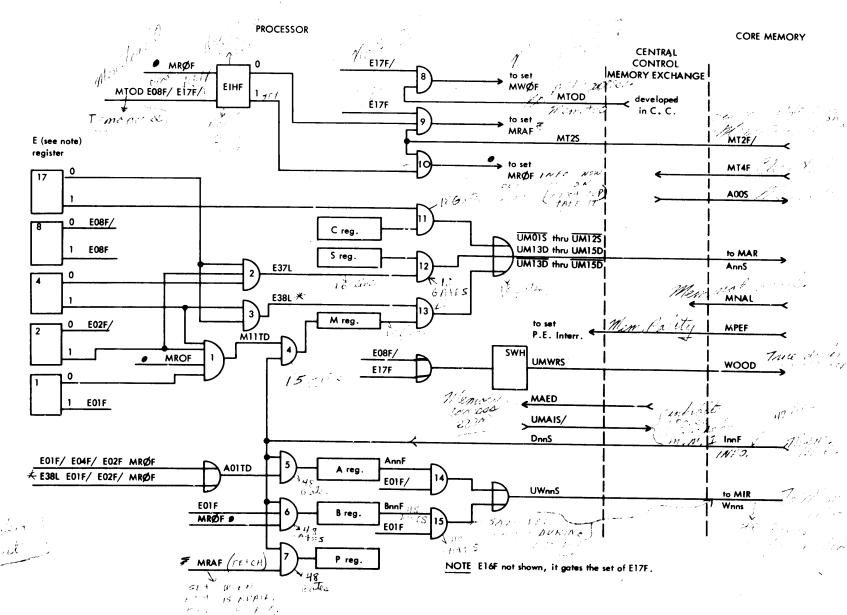

| 2.2-1           | "E" Register Gating                                            | 2.2-4          |

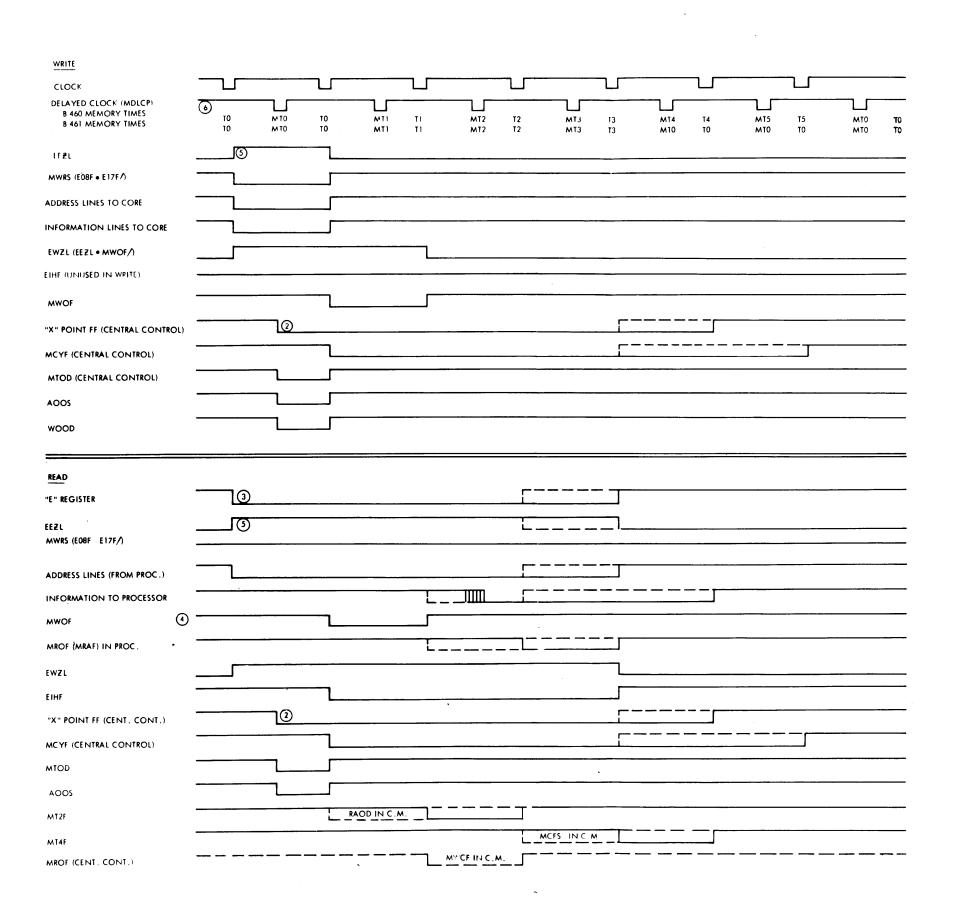

| 2.2-2           | Processor Access Timing                                        | 2.2-7          |

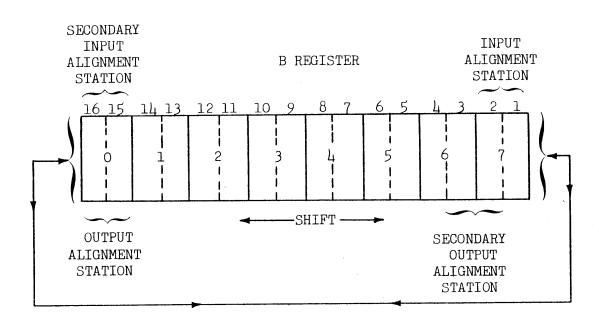

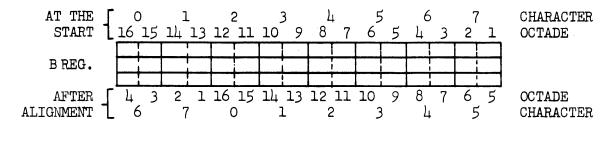

| 2.3-1           | B Register Alignment Stations                                  | 2.3-2          |

| 2.3-2           | Character Alignment                                            | 2.3-3          |

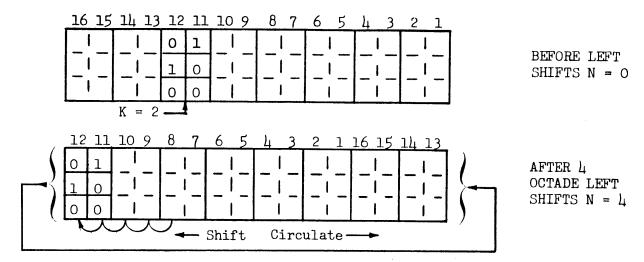

| 2.3-3           | Left Shift Alignment                                           | 2.3-4          |

| 2.3-4           | Right Shift Alignment                                          | 2.3-5          |

| 2.4-1           | ,42 Bit Mantissa - 10 Bit Address Adder                        | 2.4-2          |

| 2.4-2           | B Bit Complement                                               | 2.4-3          |

| 2.4-3           | Complement Even Bit Position                                   | 2.4-4          |

| 2.4-4           | Bit Combination for WnnR                                       | 2.4-4          |

| 2.4-5           | Marginal Carry from Position mn                                | 2.4-4          |

| 2.4-6           | 42 Bit Mantissa Adder Registers                                | 2.4-5          |

| 2.4-7           | 10 Bit Address Adder Registers                                 | 2.4-0          |

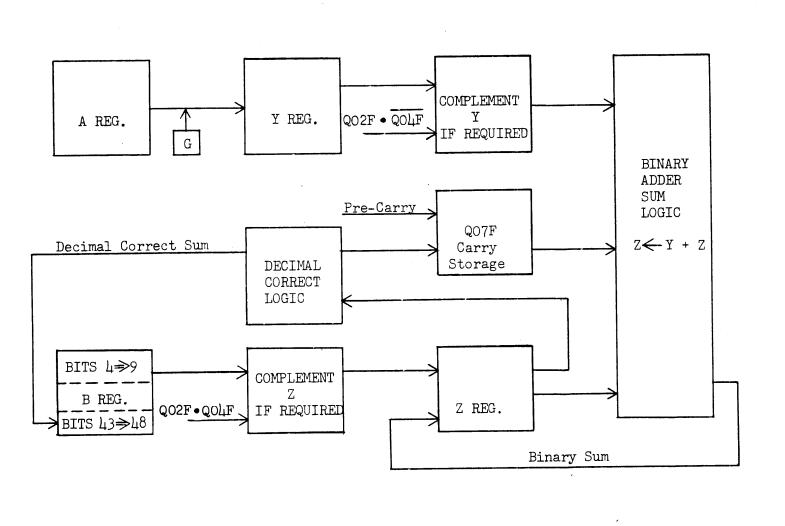

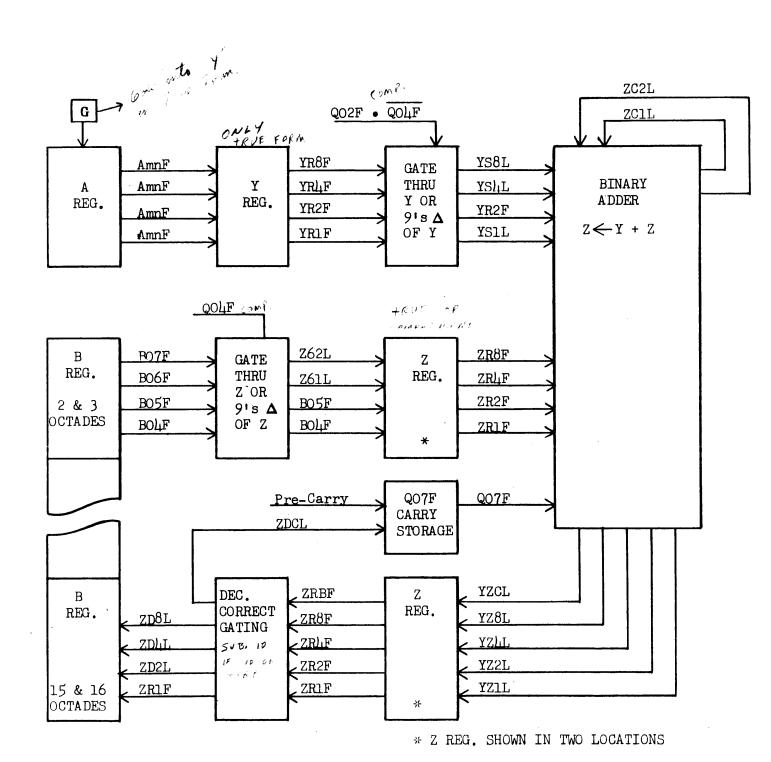

| 2.5-1           | Serial Decimal Adder                                           | 2.5-2          |

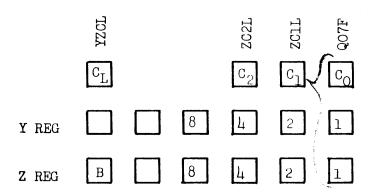

| 2.5-2           | Adder Levels                                                   | 2.5-2          |

| 2.5-3           | Nines Complement                                               |                |

| 2.5-4           | Carry Levels                                                   | 2.5-4          |

| 2.5-5           | Decimal Correction Truth Table                                 | 2.5-6          |

| 2.6-1           | Decimal 151 to Binary                                          | 2.5-7          |

| 2.6-2           | BCD Conversion Via Shifting                                    | 2.6-1          |

| 2.6-3           | Setting Flip-flops of nth Decade                               | 2.6-2          |

| 2.7-1           | Decade Bit Shift                                               | 2.6-3          |

| 2.7-2           | Binary to Decimal Conversion                                   | 2.7-3<br>2.7-4 |

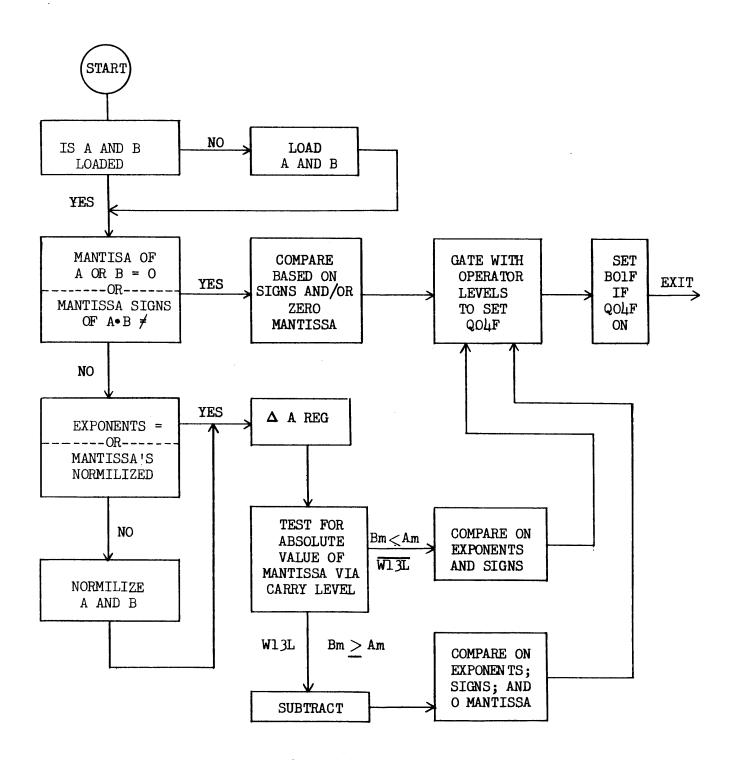

| 3.4-1           | Compare Operator Logic                                         | 3.4-2          |

| 3.4-2           | Mantissa Comparison                                            | 3.4-2          |

| 3.5-1           | Branch 4 Syllables                                             | 3.5-2          |

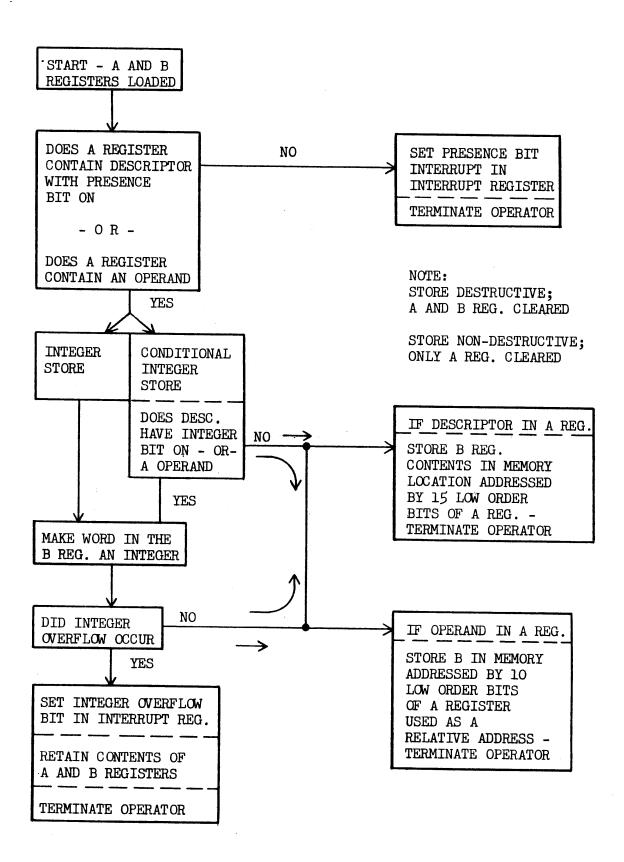

| 3.9-1           | Integer/Conditional Integer Store  Destructive/Non-Destructive | -              |

| 3.11-1          |                                                                | 3.9-2          |

| 3.15 <b>-</b> 1 | B Register Alignment                                           |                |

| 3.15 <b>-</b> 2 | Peripheral to a Register                                       | 3.15-2         |

| 3.18 <b>-</b> 1 | I/O Channel Interrogation                                      | 3.15-1         |

| 3.18 <b>-</b> 2 | Multiplicand Adjustment Table                                  | 3.18-7         |

| 3.18-3          | Adjust Multiplicand Values                                     | 3.18-8         |

| 3.19 <b>-</b> 1 | Algorithm for Adding or Subtracting                            | 3.18-8         |

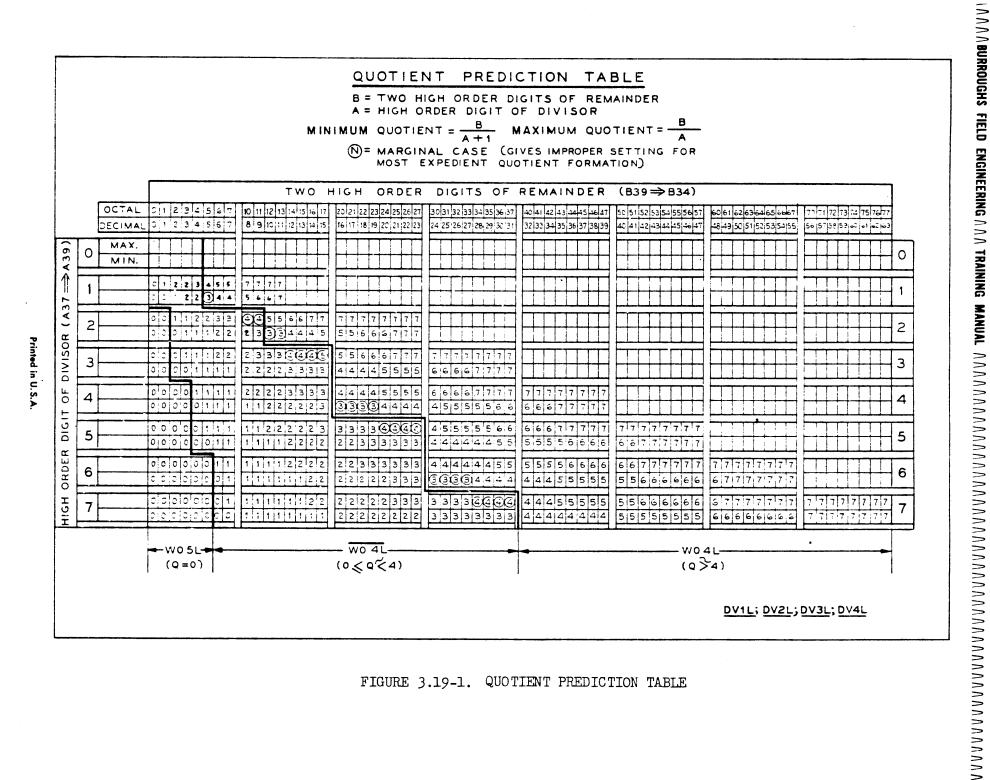

|                 | Quotient Prediction Table                                      | 3.19-L         |

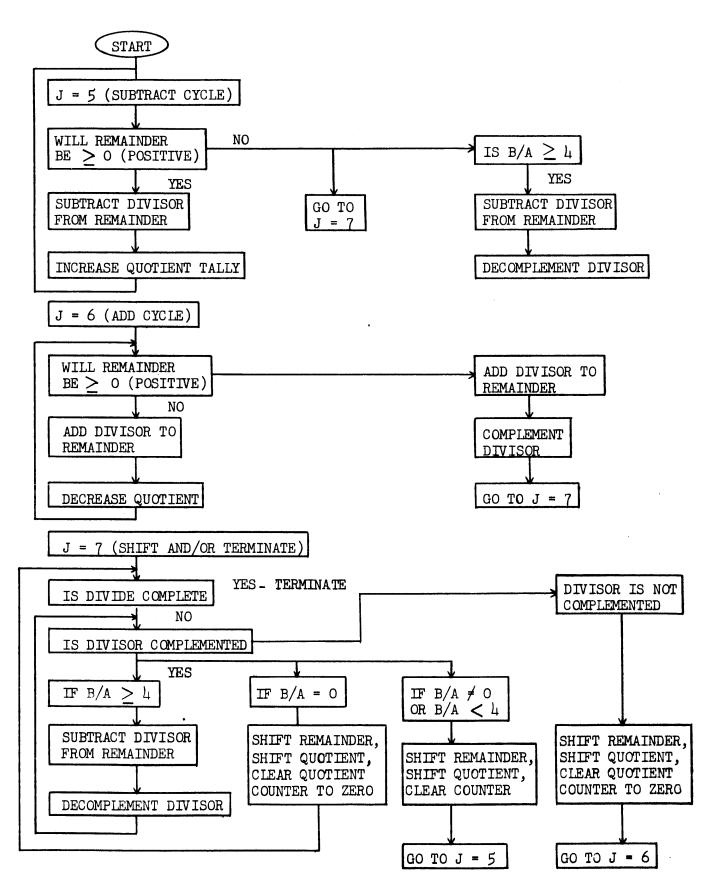

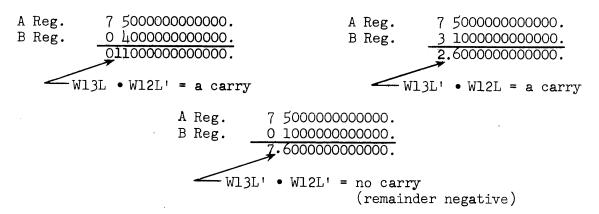

| 3.19-2          | Divide Cycle Block Diagram                                     | 3.19-5         |

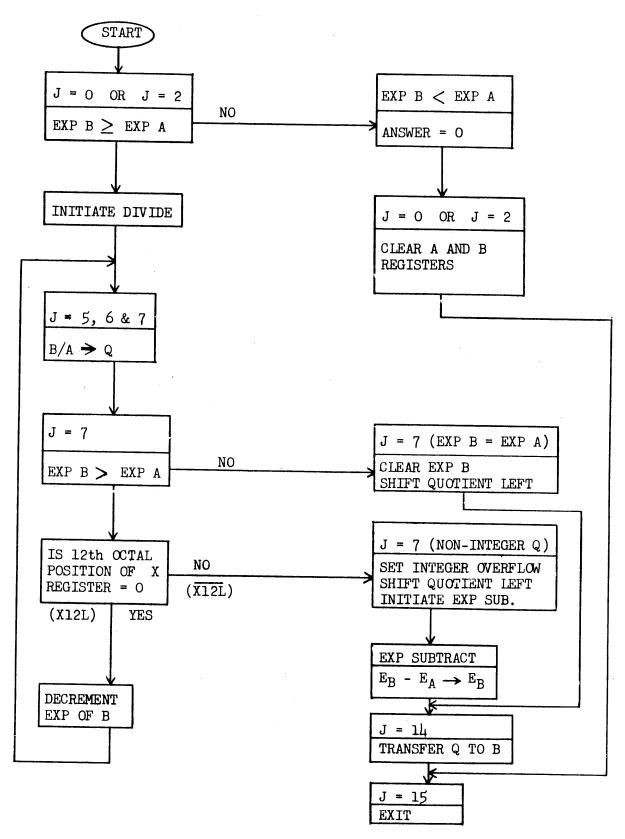

| 3.20-1          | Simplified Flow Chart - Integer Divide                         | 3.20-2         |

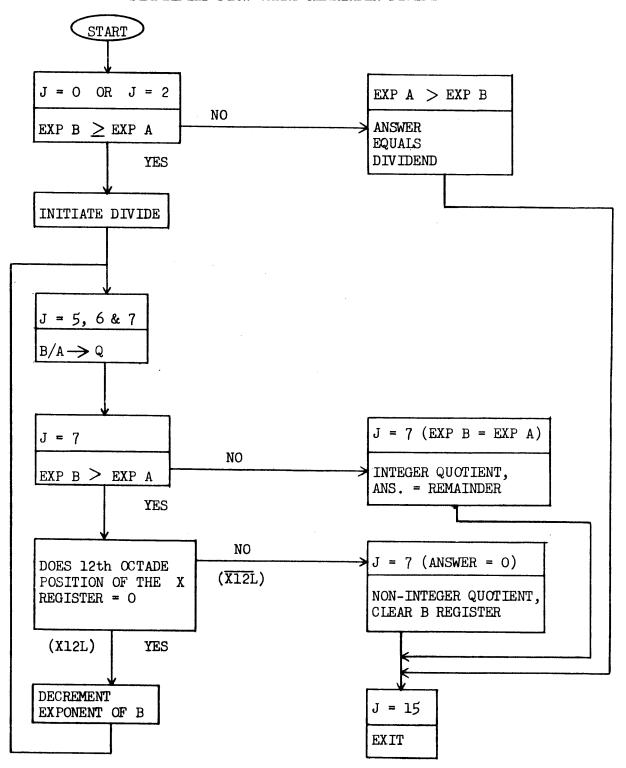

| 3.21-1          | Simplified Flow Chart - Remainder Divide                       | 3.21-2         |

| 3.23-1          | Multiply Flow Diagram                                          | 3.23-3         |

| 3.24-1          | Simplified Actions of Double Precision Divide                  | 3.24-6         |

| 3.24-2          | Detailed Actions of Double Precision Divide                    | 3.24-7         |

## LIST OF ILLUSTRATIONS (Continued)

| FIGURE                                                                                                             | TITLE                                                                                                                                                                                                                                                                                                                              | PAGE                                                                                            |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

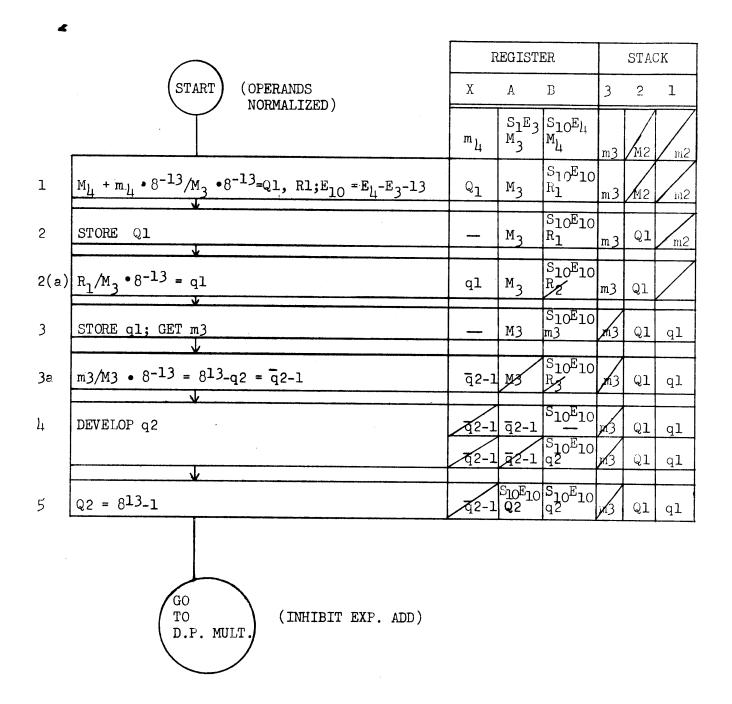

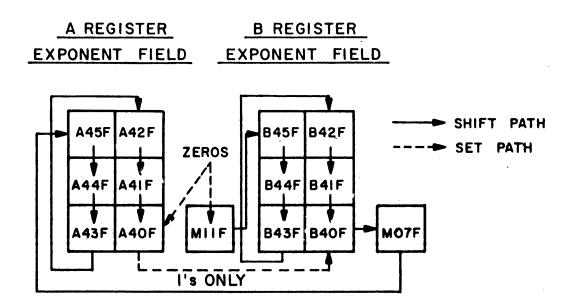

| 3.25-1<br>3.31-1<br>3.32-1<br>3.35-1<br>3.35-2                                                                     | Exponent Arithmetic Registers———————————————————————————————————                                                                                                                                                                                                                                                                   | 3.25-1<br>3.31-2<br>3.32-2<br>3.35-2<br>3.35-3                                                  |

| 4.10-1                                                                                                             | Truth Table for Result Sign                                                                                                                                                                                                                                                                                                        | 4.10-7                                                                                          |

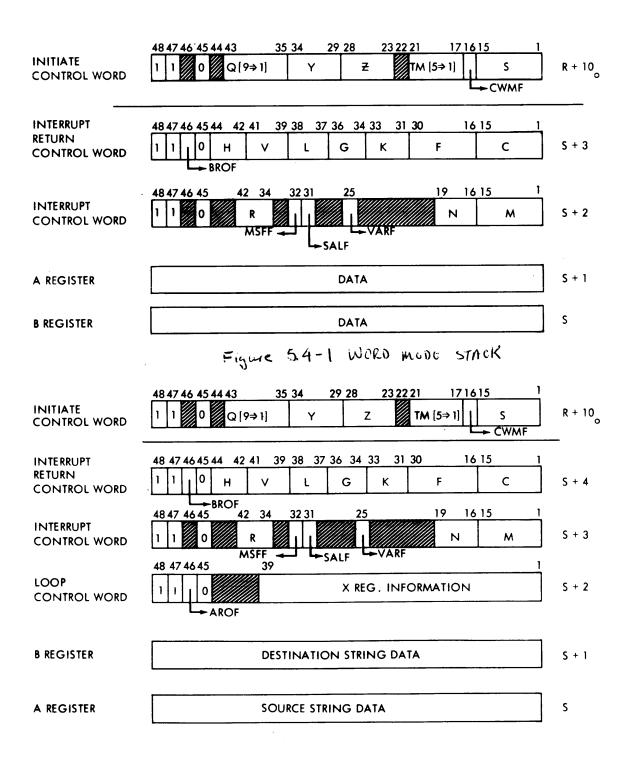

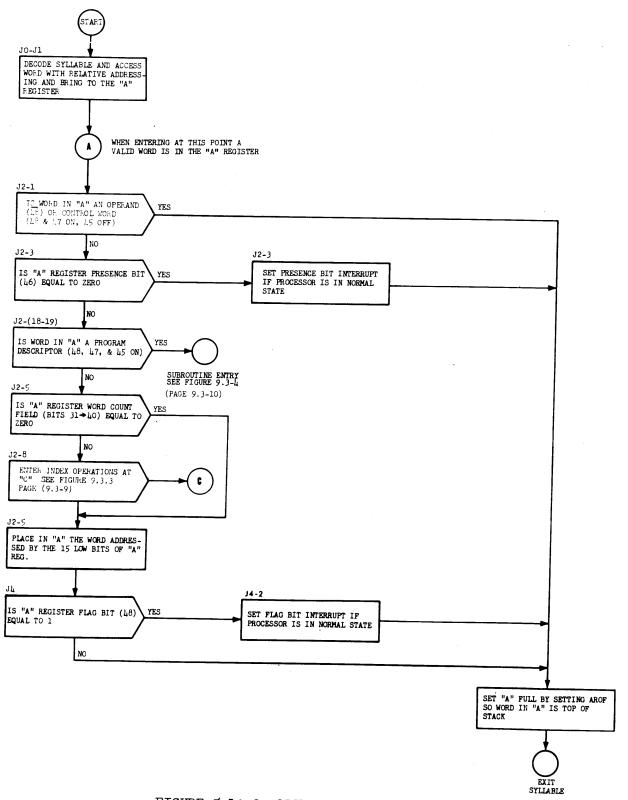

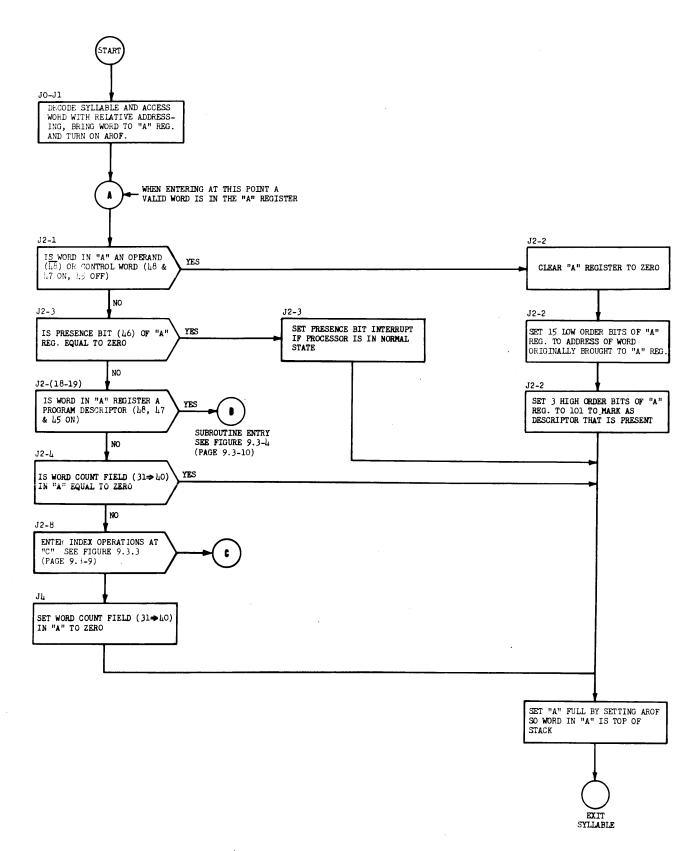

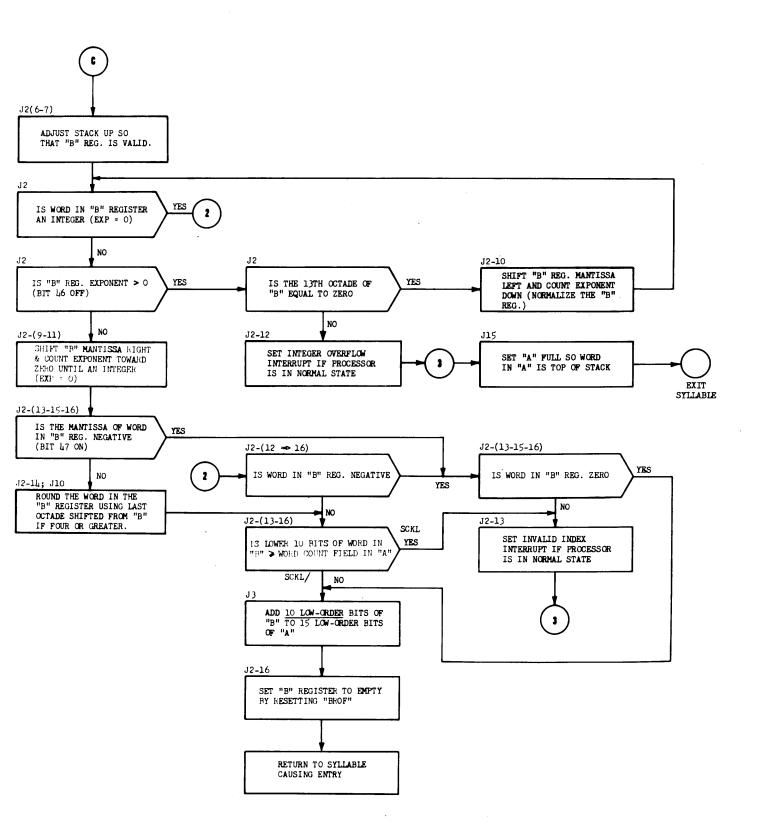

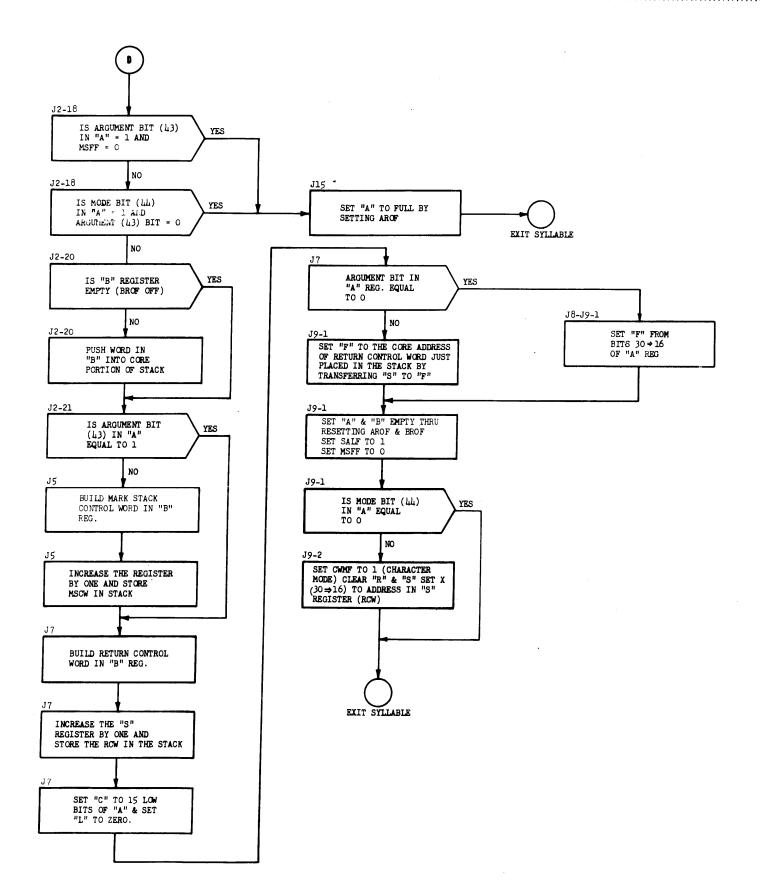

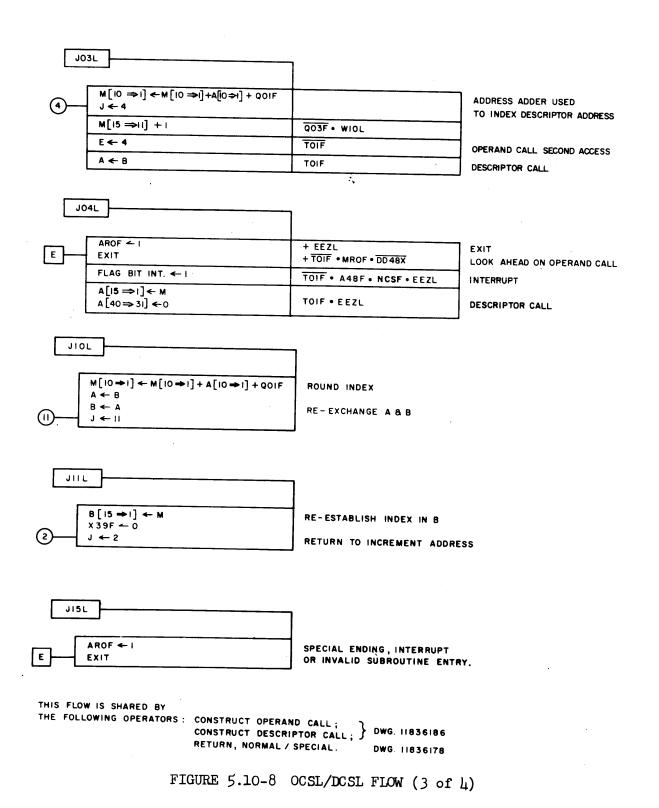

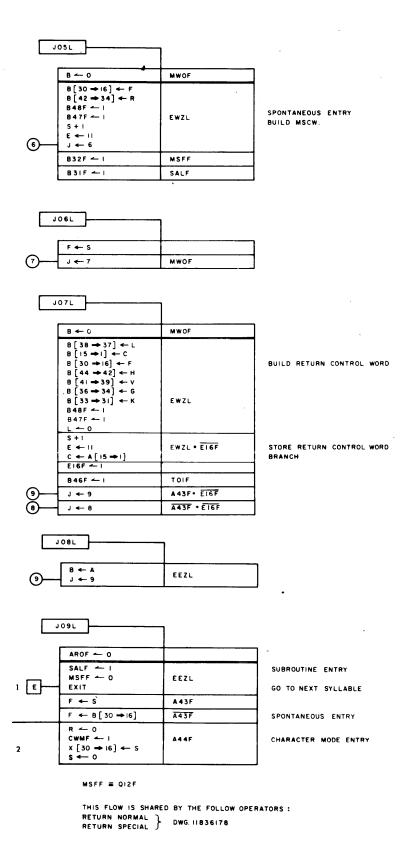

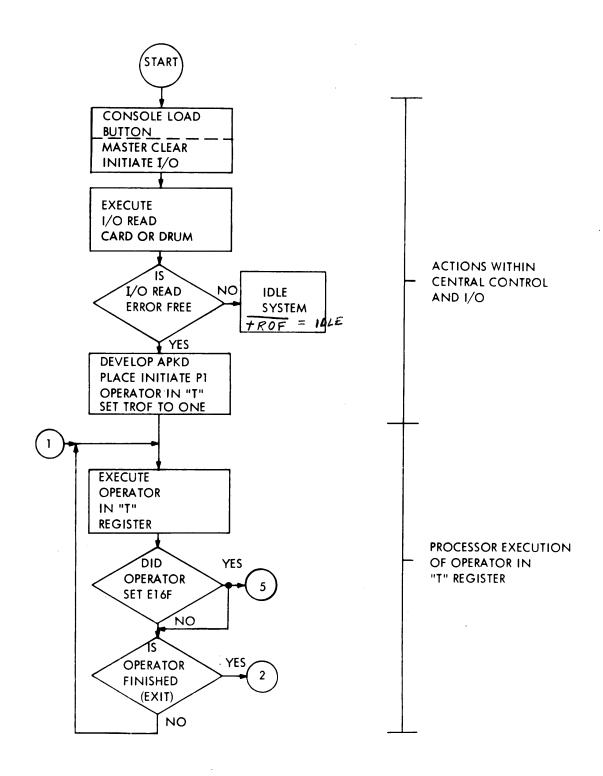

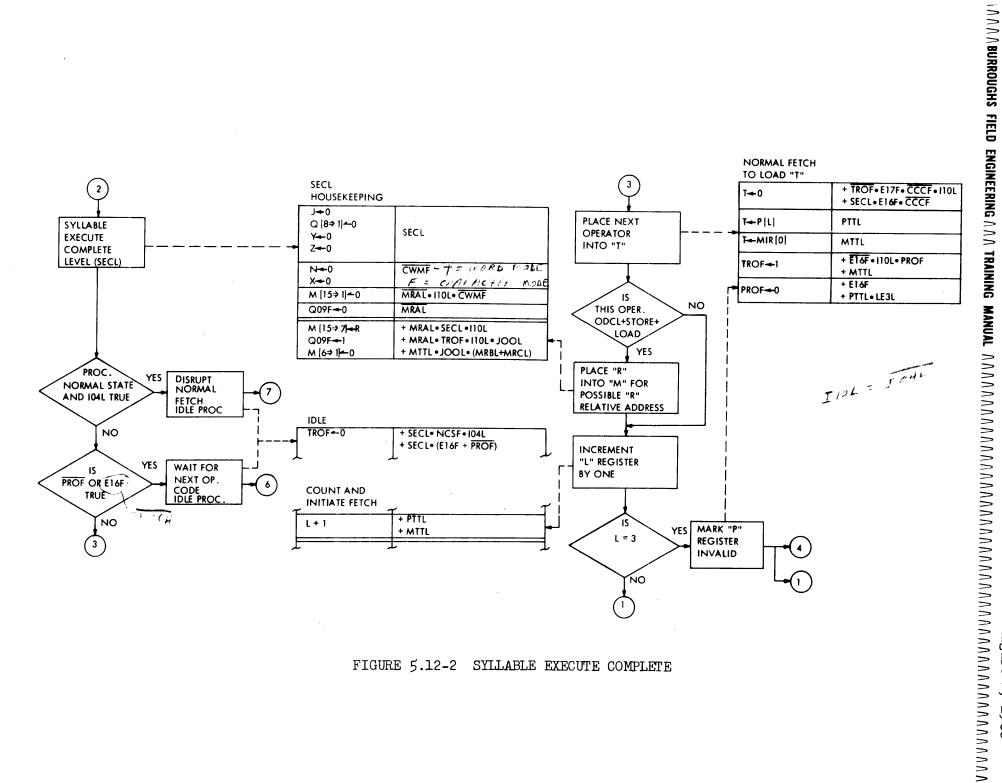

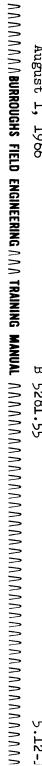

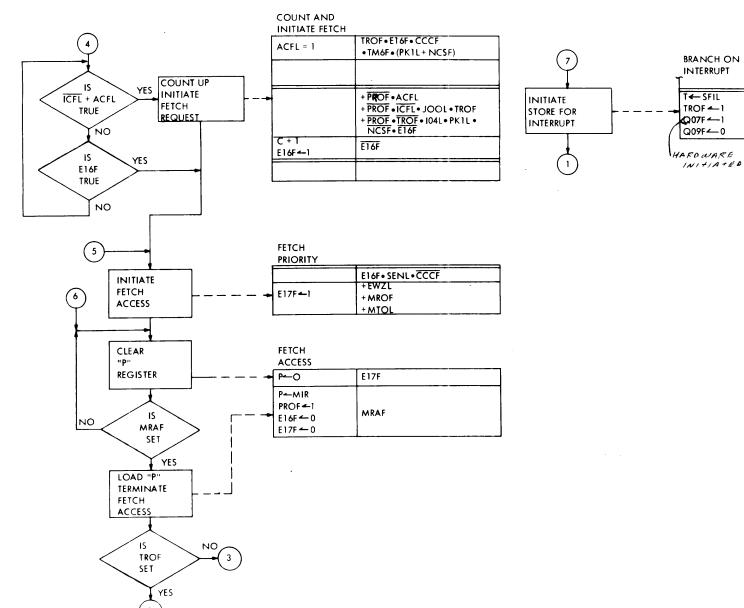

| 5.4-1<br>5.4-2<br>5.10-1<br>5.10-2<br>5.10-3<br>5.10-4<br>5.10-5<br>5.10-6<br>5.10-7<br>5.10-8<br>5.10-9<br>5.12-1 | Word Mode Stack Character Mode Stack Relative Addressing Table Operand Call Block Diagram Index Operations - Operand and Descriptor Call Subroutine Entry - Operand or Descriptor Call OCSL/DCSL Flow (1 of 4) OCSL/DCSL Flow (2 of 4) OCSL/DCSL Flow (3 of 4) OCSL/DCSL Flow (4 of 4) Processor Initiation and Syllable Execution | 5.4-2<br>5.4-2<br>5.10-3<br>5.10-4<br>5.10-5<br>5.10-6<br>5.10-7<br>5.10-8<br>5.10-9<br>5.10-10 |

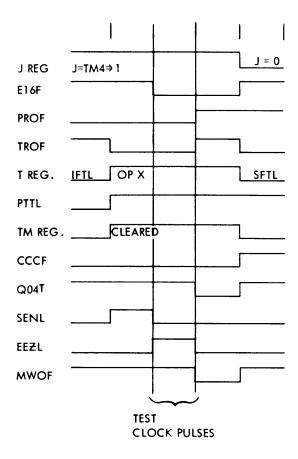

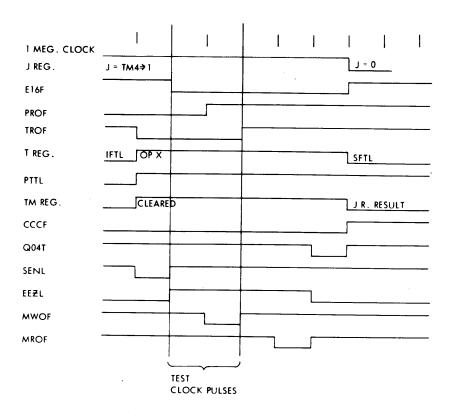

| 5.12-2<br>5.12-3<br>5.13-1<br>5.13-2                                                                               | Syllable Execute Complete Fetch Access Test - No Memory Access                                                                                                                                                                                                                                                                     | 5.12-9<br>5.12-10<br>5.12-11<br>5.13-3                                                          |

| 5.13-3                                                                                                             | Test and Memory Write Test and Memory Read                                                                                                                                                                                                                                                                                         | 5.13-4<br>5.13-5                                                                                |

#### INTRODUCTION

#### 1.1 GENERAL

The purpose of this manual is to provide a detailed description of the internal functioning of the B 5281 Data Processor. It is written with the assumption that a knowledge of the B 5500 System Concept has been attained, prior to reading this manual. Its intention is, therefore, not to duplicate the System Concept material previously covered, but to complement existing material. For these reasons the system operating characteristics relative to the Processor are not described. Instead, the specific operation of the Processor is detailed.

To accomplish its purpose, it is intended that this manual be utilized in conjunction with the B 5500 Processor Flow Charts, which are contained in a separate binder. As each operator, that the Processor is mechanized to execute, is detailed in a logical form on the Flow Charts, a description of the operator flow charts will suffice to explain the operator complement which is available within the Processor. To facilitate the description of the operators, the major logical elements provided as part of the Processor logic are described. These include:

- 1. The Parallel Adder

- 2. The Serial Decimal Adder

- 3. The Input/Output Conversion

- 4. B Register manipulation

- 5. The Processor to Memory Timing relationship

- 5. The Operator Control Level Coding

- 7. Maintenance Test Logic

To facilitate and complement the use of this manual, the separate binder containing the Operator Flow Charts also contains the Glossary of terms which are utilized, a Cross Index to the D.A. Logical Schematics, and a Cross Index to the Logic Book.

### 1.2 PHYSICAL ORIENTATION

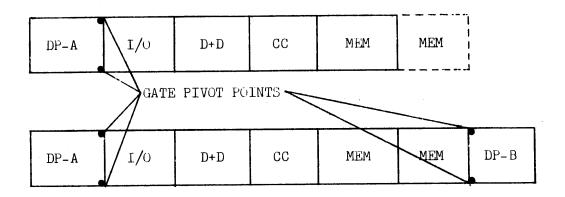

The physical location of the B 5281 Data Processor within the B 5120 Main Frame is illustrated in Figure 1.2-1. When a single data processor is utilized, its location is at the left end of the main frame and is designated as DP-A. When two data processors are utilized, DP-A is at the left and DP-B is at the right. Also illustrated in Figure 1.2-1 are the Gate (Rack) pivot points. The gate pivot point arrangement facilitates the cabling connections to the other units of the Main Frame.

FIGURE 1.2-1. DP-A AND DP-B MAIN FRAME LOCATION

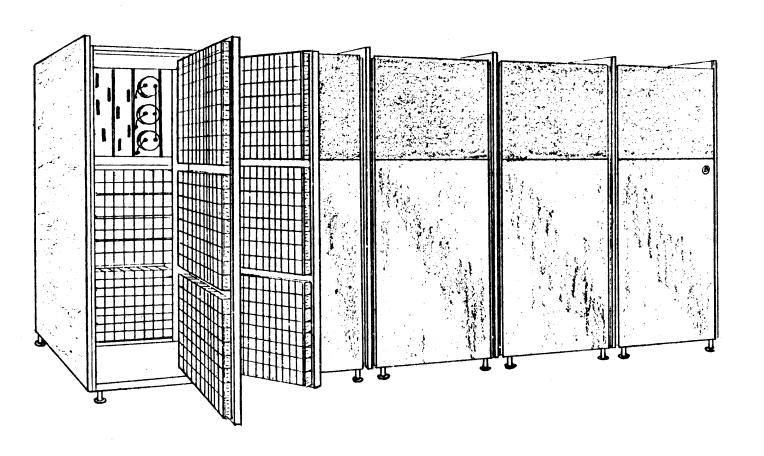

Figure 1.2-2 shows a general view of the Main Frame (front view) with the gates of the **Processor** opened. The Power Pack and Rack J can be observed within the Processor. The Power Pack is described in the B 5370 Power Supply Manual.

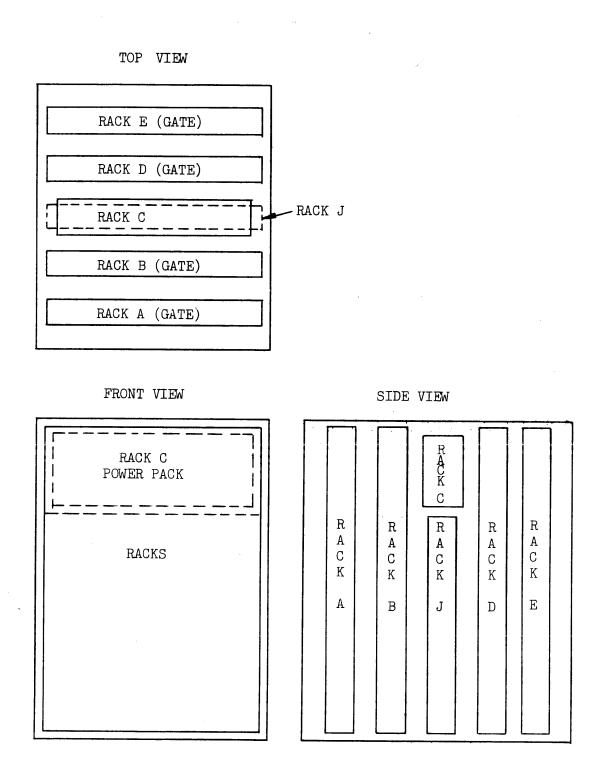

The physical construction of the two Processors (DP-A and DP-B) is the same. The rack layout as illustrated in Figure 1.2-3 is therefore applicable to either Processor The layout of DP-B is rotated relative to DP-A due to the physical location of the two Processors. When a single Processor is utilized, the Rack layout as illustrated in Figure 1.2-3 is valid for DP-A when viewed from the front. It is noted that Rack J is stationary as opposed to Racks A, B, D, and E which are swing-out gates.

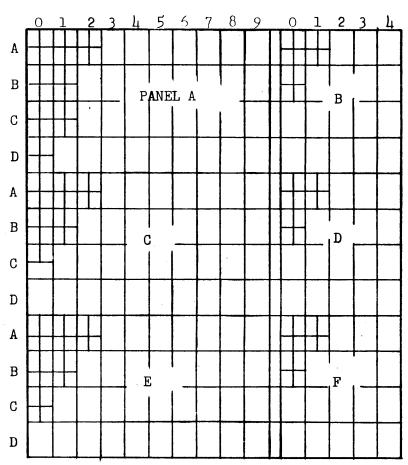

Figure 1.2-4 illustrates the panel layout for the various racks within the Processor. The numbering layout (0 through 9) as illustrated implies that the racks are viewed from the wiring side of the rack. The numbering is reversed when viewed from the package insertion side. The panel layout is the same for Racks A, B, D, and E. Rack J is merely a smaller version of the swing out gates. Note that the cabling, to and from the Processor racks, plugs into column 4 of Panels B, D and F.

1.2-2

FIGURE 1.2-2. MAIN FRAME WITH PROCESSOR OPENED

FIGURE 1.2-3. PROCESSOR RACK LAYOUT

RACKS A, B, D & E

RACK J 6 8 0 2 0 1 2 A В PANEL C C D A В E C D

FIGURE 1.2-4. PANEL LAYOUT WIRING SIDE

#### RACK CONTENT

The rack content in terms of the various registers and logical flip-flops of the **Processor** are listed below; the Q flip-flops appear on various racks:

|                                  | A RACK                                                                 |                                  | D RACK                                                            |

|----------------------------------|------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------|

| 1.<br>2.<br>3.<br>4.<br>5.       | A Register<br>X Register<br>AROF<br>BROF<br>SALF                       | 1.<br>2.<br>3.<br>4.<br>5.<br>6. | K Register V Register N Register L Register G Register H Register |

|                                  | B RACK                                                                 | 8.<br>9.                         | E Register<br>Y Register<br>Z Register                            |

| 1. 2.                            | B Register "W" Drivers (Adder Logic)                                   | 10.<br>11.<br>12.                | I Register<br>NCSF                                                |

|                                  | E RACK                                                                 |                                  | J RACK                                                            |

| 1.<br>2.<br>3.<br>4.<br>5.<br>6. | P Register<br>T Register<br>J Register<br>CWMF<br>PROF<br>TROF<br>MRAF | 1.<br>2.<br>3.<br>4.<br>5.       | F Register S Register C Register M Register R Register            |

| 8.<br>9.<br>10.                  | MROF<br>MWOF<br>HLTF                                                   | 1.                               | C RACK                                                            |

| 11.<br>12.                       | TM Register<br>CCCF                                                    |                                  | <del></del>                                                       |

#### SCHEMATIC PAGE NUMBER

The various registers and their associated drivers and switches are contained on the D.A. Logic Schematics in a grouped numbered sequence. The D.A. Logic Schematics are grouped together according to rack content; that is, all logic contained on a specific rack is grouped together to form a set of schematics for that rack. The list which follows indicates the D.A. Logic Schematic numbering groups according to the indicated circuitry. Because the page numbers, as indicated on the following list, refer to common circuitry which may be contained on more than one rack, the same page number group may be found within the schematics for more than one specific rack. The indicated page number groups with an (nn), imply a series of pages relative to that logic.

| X REQ                                                                                                     |                                                                 | Q REG                                 | R REG           | REG CLEAR |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|-----------------|-----------|

| 000000000000000000000000000000000000000                                                                   | O O O O O O O O O O O O O O O O O O O                           |                                       | 0 0 0'<br>0 0 0 |           |

|                                                                                                           | 3 2 1 1 NGSF HLTF                                               | 12 7 4 1                              | W 850           | i         |

|                                                                                                           | 00000                                                           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0 0 0 0 0       |           |

|                                                                                                           |                                                                 |                                       |                 |           |

|                                                                                                           |                                                                 |                                       |                 |           |

| INT BESET  INHIBIT COUNT  BEPTAT RELD SAM M EAVEN AROF BROF T-P(L)  O O O O O O O O O O O O O O O O O O O | MEMORY LOAD  MEMORY SIMPLE WRITE PULSE  STORE IN/OUT  LOCK UP 8 | E REG  OF STOP  OF OF OF OF           |                 |           |

|                                                                                                           | 617 ADD • • • • • • • • • • • • • • • • • •                     | 1 INTERRUPT NORMALIZED J COUNT        |                 |           |

| * * * * * * * * * * * * * * * * * * *                                                                     | UMIT CLEAR                                                      | <u> </u>                              |                 |           |

FIGURE 1.2-5 PROCESSOR DISPLAY PANEL

#### PROCESSOR DISPLAY PANEL

The Processor display panel is located in Display and Distribution as illustrated in Figure 1.2-5. If the system consists of two Processors, then there will be two such display panels. The display panel for Processor A will be located on Gate A (outer gate) of Display and Distribution and display panel for Processor B will be located on Gate B (inner gate).

The display panels for either Processors A or B are identical and are as illustrated in Figure 1.2-5. Mounted on the display panel are the neon indicators for each flip-flop in the Processor. Each of these indicators contains the capability of manually setting or resetting its respective flip-flop. Also contained on the display panel are all of the Processor maintenance switches. The following description will give a basic description of each of the registers (and flip-flops) and maintenance switches on the Processor maintenance panel.

#### Registers and Flip-Flops

A REGISTER. The A register is a 48 bit register which is used to contain the top word of the stack for word mode or a word of the source string in character mode. The bits are numbered 1 thru 48 (bottom to top, right to left). These 48 bits can be subdivided into 16 octal digits or 8 six bit characters. The octal digits (octades) are numbered right to left as indicated at the bottom of the A register neons with octade 1 consisting of bits 1, 2 and 3 of the A register. The six bit characters are numbered, as indicated above the A register, 0 thru 7 from left to right, with character 0 (zero) containing the six high order bits of the A register  $(48 \implies 43)$ .

AROF. This is the "A" Register Occupied Flip-flop. When it is set it indicates that the contents of the A register is valid; when reset, it indicates that the A register contents are invalid.

B REGISTER. Is of the same construct as the A register. The B register will contain (in word mode) the top word of the stack if the A register is empty (indicated by AROF) or the second word of the stack if the A register is occupied (AROF). In Character Mode the B register will contain one word of the destination string.

BROF. This is the B Register Occupied Flip-flop. When it is ON, it indicates that the contents of the B register are valid. When it is OFF, it indicates that the contents of the B register are invalid.

C REG. This register contains 15 neons which indicate the status of the flip-flops in the C register. In either the Word Mode or Character Mode, this register holds the core address of the program word which is in the P register.

- CCCF. Logical flip-flop for the maintenance Test Routines. Controls the Processor clock.

- E REG. There are six neons in this register which are used to indicate the type of memory access needed by the Processor.

- F REG. There are 15 indicators in this register. In Word Mode, this register holds the address of the top Return Control Word or top Mark Stack Control Word in the stack. In Character Mode, this register holds the address of the top Return Control Word in the stack.

- G REG. There are three flip-flops in this register. In Word Mode or Character Mode, this register points to a character within the A register.

- H REG. There are three flip-flops in this register. In either Word Mode or Character Mode, this register points to the bit of the character in the A register pointed to by the G register.

- I REG. There are seven flip-flops in this register. Bits 1, 2 and 3 are for the Non-Syllable Interrupts, bits 5, 6, 7 and 8 are used to develop binary values for syllable interrupts.

- J REG. There are four neons in this register. This register contains the primary control setting used during the execution of a syllable.

- K REG. There are three neons in this register. In either the Word Mode or Character Mode, this register points to a character within the B register.

- L REG. (Located between the P and T registers) There are two neons in this register. In either the Word Mode or Character Mode, this register points to the next operator (to be executed) within the P register.

- M REG. There are 15 neons within this register. In Word Mode, this register holds the memory address of the word placed in the A register other than by stack adjustment. In Character Mode, this register holds the address of the current word in the source string.

- N REG. There are four neons in this register. In either the Word Mode or Character Mode this register is used as a special counter. The flow chart should be used to obtain its specific use.

- P REG. There are 48 indicators in this register. They are divided into four groups of 12, with each group representing one operator. The operators are selected by the L registers.

- PROF. This is the P Register Occupied Flip-flop which indicates whether or not the information in the P register is valid. When True (indicator On) the information in the P register is valid, when False the information in the P register is invalid.

- Q REG. There are 18 flip-flops in this register. The Q register flip-flops are distributed throughout the Processor unit and they are used as logical flip-flops as needed by the operators. Bits 1 through 9 are not specified as to particular use. Bits 12 through 18 are used as follows:

- Q12F In Character Mode it is used as the True-False indicator. In Word Mode it is the Mark Stack Flip-flop (MSFF).

- MRAF This flip-flop is on when the memory operation is completed for a memory fetch access.

- MROF This flip-flop is on when the memory operation is completed for a memory read access.

- HLTF This bit is used to provide special stops during maintenance operations.

- EIHF Control flip-flops for a memory read access.

- MWOF This bit is on when the memory operation is completed for a memory write access.

- SALF Control flip-flop used to indicate if a program is in sublevel or program level. When this bit is on it indicates sublevel.

- CWMF Character Word Mode Flip-flop, when on indicates program is in character mode.

- R REG. There are nine bits in this register. In word mode, this register contains the base address (three high order digits only) of the Program Reference Table (PRT). In Character Mode the six-bits are used as a tally register.

- S REG. There are 15 bits within this register. In Word Mode, this register contains the address of the top word in the stack in core memory. In Character Mode, this register holds the address of the current word in the destination string.

T REG. There are 12 bits in this register. This register contains the syllable currently being executed by the Processor.

TM REG. Eight bit register used for Temporary storage for the Maintenance Test Routines.

V REG. There are three bits within this register. In either the Word Mode or Character Mode, this register points to the bit of the character in the B register pointed to by the K register.

VARF. When set will allow the Processor to access the entire PRT when in sublevel.

X REG. There are 39 bits in this register. In Word Mode, this register is used as an extension of the B register during mathematical computations. In Character Mode, this register is used as storage for Loop Control Words.

Y REG. There are six bits in this register. In either the Word Mode or Character Mode, the register is used for temporary storage of a character from the A register.

Z REG. There are six bits in this register. In either the Word Mode or Character Mode, the register is used for temporary storage of a character from the B register.

## PUSH BUTTON SWITCHES

This is a description of the push button switches (non-indicating) located on the Processor Display Panel.

These switches are the push type and maintain contact during the duration that the switch is held in.

BIT RESET. When this switch is held in, it switches the input voltage to the neon switches from +100V to -100V. This causes the neon switch to apply a reset voltage to the flip-flop when the neon switch button is pressed. The BIT RESET switch is common to all of the neon switches on the Processor Panel.

MEMORY WRITE (US25%). To use this switch the MEMORY LOAD switch must be in the TEST position (up) and TROF must be Off.

When depressed, this switch causes the contents of the B register to be written into memory under the control of the S register. The S register is incremented by one.

REG CLEAR. There are 16 buttons in this group. When a button is depressed its associated register is completely cleared (all bits reset).

SINGLE PULSE (US2LX). This button is used to generate one clock pulse to the Processor. It is normally used in conjunction with one of the Processor stop switches.

UNIT CLEAR. Pressing this button resets all of the flip-flops in the Processor. This is the general Clear button for the Processor only.

#### INHIBIT TOGGLE SWITCHES

This is a description of the toggle switches located on the Processor Display Panel. Listed below is a table of all toggle switches on the Processor Display Panel. This table is a listing by switch number sequence. The following write up is in alphabetical sequence and describes the use of the switches.

#### B 5000 PROCESSOR - MAINTENANCE PANEL SWITCHES

| SWITCH NUMBER | ACTION                             |

|---------------|------------------------------------|

| USOlX         | INHIBIT COUNT REPEAT FIELD         |

| USO2X         | INHIBIT COUNT G AND H              |

| USO3X         | INHIBIT COUNT M                    |

| USOЦХ         | INHIBIT COUNT K AND V AND N        |

| US05X         | INHIBIT COUNT S                    |

| USO6X         | INHIBIT COUNT C                    |

| US07X         | INHIBIT COUNT L                    |

| USO8X         | INHIBIT RESET AROF                 |

| US09X         | INHIBIT RESET BROF                 |

| USlox         | INHIBIT $T \leftarrow P[L]$        |

| USllX         | INHIBIT STORE                      |

| US12X         | INHIBIT IN/OUT                     |

| US13X         | INHIBIT INTERRUPT                  |

| ∙uslկx        | STOP OPERATOR                      |

| US15X         | STOP CLOCK                         |

| US16X         | STOP ON EXIT                       |

| US17X         | STOP ON INTERRUPT (PROCESSOR TYPE) |

| US18X         | STOP WHEN NORMALIZED               |

| US19X         | STOP ON J COUNT                    |

| US2OX ⇒ US23X | J-CODE SWITCHES (1, 2, 4 and 8)    |

| US26X         | INHIBIT RESET A REGISTER           |

| US27X         | INHIBIT 42 BIT ADD                 |

| US28X         | LOCK-UP ON J CODE                  |

| US29X         | MEMORY LOAD                        |

Inhibit 42 Bit Add (US27X). This switch in the TEST position inhibits the level from the outputs of the adder circuit. This prevents the sum of the addition from being fed into the B register.

Inhibit In/Out (US12X). This switch in TEST position forces the Initiate Input/Output operators to become NO OPS, thus eliminating any I/O operations.

Inhibit Interrupt (US13X). In TEST position, this switch inhibits the set of any interrupt in the Processor, by inhibiting the setting of any bits in the I register.

Inhibit Store (US11X). When this switch is in TEST position, any memory write access by the Processor is inhibited.

Inhibit  $T \le P(L)$  (US10X). When this switch is in the TEST position it inhibits the transfer of the operators from the P register to the T register. This switch will not inhibit the character transfer from the P register to the T register when called for by the CALL REPEAT FIELD operator.

Inhibit Count C (USO6X). When this switch is in the TEST position, it inhibits incrementing the C register. This prevents the fetch of a new program word, allowing the Processor to recycle on the instruction word addressed by the C register.

Inhibit Count G & H (USO2X). When this switch is in the TEST position it inhibits the incrementing or decrementing of the G and H registers.

Inhibit Count K, V & N (USOLX). When this switch is in the TEST position, it inhibits the incrementing or decrementing of the K, V and N registers. These registers may be either set or reset.

Inhibit Count L (USO7X). When this switch is in the TEST position, it inhibits the incrementing or decrementing of the L register. This locks the Processor on a single operator unless an interrupt is encountered.

Inhibit Count M (USO3X). When this switch is in the TEST position, it inhibits the incrementing or decrementing of the M register.

Inhibit Count Repeat Field (USOIX). When this switch is in the TEST position, it inhibits the decrementing of the REPEAT COUNT FIELD in the T register.

Inhibit Count S (USO5X). When this switch is in the TEST position, it inhibits the incrementing or decrementing of the S register.

Inhibit Reset of AROF (USO8X). When this switch is in the TEST position, it inhibits the logical resetting of the AROF Flip-flop.

Inhibit Reset of BROF (USO9X). When this switch is in the TEST position, it inhibits the logical resetting of the BROF Flip-flop.

Inhibit Reset of A Reg (US26X). When this switch is in the TEST position, it inhibits the logical resetting of the Mantissa in the A register for all operators.

J-Code Switches 1, 2,  $\mu$  and 8 (US20X  $\Rightarrow$  US23X). These switches are used in conjunction with the STOP ON COUNT and the J CODE LOCK UP switches. These four switches (1, 2,  $\mu$  and 8) are set to indicate the desired J register setting to stop or lock up on.

Lock-Up on J (US28X). This switch is used in conjunction with the J-CODE SWITCHES. When this switch is in TEST position, it inhibits further changes to the J REG once it has attained a setting equal to the value set in the J-CODE SWITCHES.

Stop Clock (US15X). When this switch is turned on, it inhibits the clock pulses to this Processor from Central Control when a memory cycle is not in progress. This allows for single pulsing the Processor while the remainder of the system is running with the clock normal.

Stop Exit (US16X). When this switch is in TEST position, it will inhibit the clock pulses at SECL time, which is at the end of the operator that is presently being executed.

Stop on Interrupts (US17X). When this switch is in TEST position, it will inhibit the clock when any Processor Interrupt appears in the Processor Interrupt Register.

Stop on J Count (US19X). When this switch is in TEST position, it will inhibit the clock pulses to the Processor when the value of the J register equals the value encoded by the J-CODE switches.

Stop Normalized (US18X). When this switch is in the TEST position, it will stop the Processor clock pulses when both operands in the A and B register are aligned (exponents are equal).

Stop Operator (USILX). When this switch is in TEST position, it provides a level which, in conjunction with the Conditional Halt Operator and the J register equal to zero, will stop all Processor action. Processor operation will be resumed when the CLOCK START button is pushed. When this switch is in NORMAL position the Conditional Halt Operator is treated as a No Op.

#### B 5000 PROCESSOR SCHEMATIC PAGE NUMBERS

```

65 • 10 • nn • 0

A Register FF's, drivers and switches

65 • 14 • nn • 0

F Register FF's, drivers and switches

65 • 18 • nn • 0

X Register FF's, drivers and switches

K Register FF's, drivers and switches

65 • 22 • nn • 0

65 • 26 • nn • 0

V Register FF's, drivers and switches

65 • 30 • nn • 0

N Register FF's, drivers and switches

65 • 34 • nn • 0

S Register FF's, drivers and switches

65 • 38 • nn • 0

C Register FF's, drivers and switches

65 • 38 • 50

D Drivers

• 42 • nn • 0

L Register FF's, drivers and switches

65 • 46 • nn • 0

P Register FF's, drivers and switches

65 • 50 • nn • 0

T Register FF's, drivers and switches

65 • 54 • nn • 0

G Register FF's, drivers and switches

65 • 58 • nn • 0

H Register FF's, drivers and switches

65 • 62 • nn • 0

M Register FF's, drivers and switches

65 • 66 • nn • 0

B Register FF's, drivers and switches

65 • 68 • nn • 0

"W" Drivers and Switches

65 • 70 • nn • 0

E Register FF's, drivers and switches

65 • 72 • nn • 0

"U" Drivers and Switches

65 • 74 • nn • 0

R Register FF's, drivers and switches

65 • 78 • nn • 0

J Register FF's, drivers and switches, TM Register, CCCF

65 • 82 • nn • 0

Y Register FF's, drivers and switches

65 • 86 • nn • 0

Z Register FF's, drivers and switches

65 • 88 • nn • 0

I Register FF's, drivers and switches

65 • 90 • nn • 0

Q Register FF's, drivers and switches, VARF

65 • 92 • nn • 0

Common AND Gates

65 • 94 • nn • 0

Misc. "L" Levels

65 • 95 • nn • 0

Intergate Cables

65 • 96 • nn • 0

Interunit Cables

65 • 97 • nn • 0

Filters (Power Distribution)

65 • 97 • 60 • 0

65 • 97 • 61 • 0

E Rack Ground

65 • 97 • 62 • 0

65 • 97 • 62 • 5

Inter-Lace Ground

65 • 97 • 63 • 0

65 • 97 • 64 •

0

J Rack Ground

65 • 97 • 65 • 0

65 •

97 • 66 • 0

65 •

97 • 67 • 0

B Rack Ground

65 •

97 • 68 • 0

97 • 68 • 5

Inter-Lace Ground

65 •

97 • 69 •

0

65 •

97 •

70 •

A Rack Ground

0

65 •

97 • 71 •

97 •

71 •

Inter-Lace Ground

65 •

97 •

72.

0

65 •

97 •

73 •

D Rack Ground

0

65 • 97 • 74 •

65 •

97 •

Inter-Lace Ground

74 •

65 •

98 • nn •

0

Terminations

65 •

99 • nn • 0

Inter Frame Jumpers

```

#### **SECTION 2**

#### LOGICAL IMPLEMENTATION

#### 2.1 OPERATOR CONTROL LEVEL CODING

The operator code for a specific operator, when in the T register, is decoded to provide a level or levels to enable the logic relative to that specific operator. In some cases the level developed has the same mnemonic designation as the operator itself. In other cases, the level developed is not readily identifiable to the specific operator. In addition, certain operators are decoded such that more than one level is developed; in this case, the levels developed are common to more than one specific operator.

The information which follows indicates the mnemonic name of the operator and the associated bit configuration decoded in the T register. Not all bit positions of the T register are decoded in order to develop the various operator control levels. Only those bits necessary to accomplish the required decoding are actually decoded. For those bit combinations which do not decode to a valid operator, the bit configuration is decoded as Syllable Execute Complete Level and, therefore, act as a NO-OP if placed in the T register.

#### WORD MODE OPERATORS

Refer to the B 5500 Handbook, Section 2, for a listing of the word mode operators with their associated mnemonic code and octal code. Section 9 of the handbook contains a listing of the T register setting assigned to each word mode operator, including Operand Call, Descriptor Call, Literal Syllables and Control operators.

The common levels developed from these operators are indicated in the margins and footnotes. For those states which are assigned, all blanks are zero, although only those flip-flops whose state is designated are tested by the decoding gates. Where a flip-flop is indicated as "X", a "don't care" condition exists.

#### CHARACTER MODE OPERATORS

Refer to the B 5500 Handbook, Section 2, for a listing of the Character Mode Operators with their associated mnemonic code and octal code. Section 9 of the handbook contains the Character Mode listing the T register states assigned to each character mode operator, including reserved and "not assigned" states.

In all assigned cases, the literal portion of the syllable is represented as a "don't care" condition. The common levels developed from these operators are indicated in the margins.

#### 2.2 MEMORY ACCESS

Any time the Processor requires a memory access it must provide Central Control with the necessary data to allow the memory exchange portion of Central Control to select the correct Memory Module (0 thru 7) and to subsequently enable the address, control, and information lines between the Processor and the Memory Module. The addressing data provided by the Processor consists of 15 bits of addressing data to Central Control. The information lines between the Processor and Core Memory consist of 48 write information lines and 48 read information lines. Control data to Central Control is a memory write level to indicate a memory write operation and an inhibit level to prevent crosspoint selection when necessary.

The following is a glossary of the levels between Processor and Central Control that are pertinent to a memory access.

#### PROCESSOR TO CENTRAL CONTROL

UMAIS/. Memory Request Not, when false inhibits the setting of the crosspoint flip-flop in Central Control. This level is primarily used in case of an address error, an address less than 01000 when in Normal State.

UMWRS. Memory Write Level, when true indicates that the subsequent memory access is a memory write access.

UWnnS. h8 write information lines from the Processor.

UMOLS/ thru UM12S/ Address lines from the 12 low order bits of the addressing register. These lines are routed thru memory exchange to the Memory Module.

UM13D thru UM15D and UM13D/ thru UM15D/. Six lines indicating the status of the 3 high order bits of the addressing register. These bits are used in Central Control to select a crosspoint flip-flop.

#### CENTRAL CONTROL TO PROCESSOR

DnnS. 48 read information lines from Core Memory to Processor via memory exchange.

MAED. Memory Address Error indicates an attempt to access either a non-existant Memory Module or a Memory Module that is in local.

MPEX. Memory Parity Error, used during a memory read operation to indicate that a memory parity exists. This level is used to set the Memory Parity Error Interrupt in the Processor.

MTOD. Memory Time Zero Driver, originates in Central Control, indicates the memory cycle is at memory time zero. This level is used to set MWOF (Memory Write Obtained Flip-flop) in the Processor.

MT2S. Memory Time Two, originates in the Memory Module, indicates when the memory cycle is at memory time two. This level is only used during a read access to signify when the Processor can sample the read information lines.

No detailed explanation will be given in this manual of the operation of memory exchange. For this description refer to the Central Control Technical Manual, Subject 7.6.

#### ADDRESS REGISTERS

With each memory access the Processor uses one of three 15 bit registers for addressing memory; the S register, M register, or C register. Of the 15 bits, the three high order bits are decoded in Central Control and used to select the correct Memory Module. The 12 low order bits are routed thru memory exchange to the Memory Address Register in the Memory Module. For the usage of the three addressing registers refer to the Processor Flow Charts, page 4.02.0.

#### INFORMATION REGISTERS

For each memory access the Processor uses one of four registers to contain the information to be written into or read from memory. These registers are the A register, B register, M register, and the P register. The A and B registers are 48 bit registers used to contain the information being acted upon by the Processor. Any information to be written into memory must be in one of these two registers.

The P register is a 48 bit register used to contain the program word presently being executed. Use of the P register as an information register is only during a fetch access, the addressing register will be the C register.

The M register is normally considered to be an addressing register but can be used as an information register. This register, being only 15 bits long, will only receive bits 16 thru 30 of the word read from core memory.

#### CONTROL FLIP-FLOPS

The Processor uses several flip-flops to control its memory access. A description of these flip-flops and their functions follows.

MWOF. Memory Write Obtained Flip-flop, is set by MTOD and reset by the next clock pulse. Its function during a write access is to indicate the termination of the write access, during a read access it serves to clear the information register in the Processor.

MROF. Memory Read Obtained Flip-flop, set by MT2S, it is on for l  $\mu$ s. This flip-flop is not used during a write access. During a read access it indicates the termination of the read access. MROF serves also to enable the read information lines into the appropriate information register.

MRAF. Memory Read Access Flip-flop, its use is the same as MROF except that it is only used during a fetch access. It is used to gate the information into the P register and to indicate the termination of a fetch access.

EIHF. Inhibit Address Flip-flop is set during a memory read, other than a fetch access, to prevent erroneously selecting more than one Memory Module during one read access. Its use will take affect in such a case as the addressing register being counted up or down to address the next Memory Module in sequence prior to completion of a memory cycle.

#### E REGISTER

The E register is set by the Processor when initiating a memory access. This register is a six bit register that is used to select the desired address register, information register, and to indicate a read or write access. A description of the E register bit usage follows.

EOIF. When ON indicates that the B register is the information register, when OFF, the A register is the information register.

EO2F. When ON indicates that the S register will be the addressing register.

EOLF. When ON indicates that the M register will be the addressing register.

EO8F. When ON indicates a memory write access, when OFF, a memory read access.

$E02F \bullet E0\$  When the E register is equal to six, the access will be a read, the M register is the addressing register and also the information register.

El6F • El7F. Used to initiate a fetch access in the Processor. El6F is set by the Processor to request a fetch access, El7F is then set to execute the fetch access.

Figure 2.2-1 is a simplified diagram of the E register gating for selection of the various address and information registers. The selection of any of these registers is possible with any value in the E register. For example, if the E register was equal to 3, then the S register will be the addressing register, selected via gates 2 and 12. The B register will be selected as the information register via gate 6 when MROF is true.

MROF is set, via gate 10, at memory time two (MT2S) with EIHF. EIHF will be set if the memory access is a read access, but not a fetch access.

2.2-5

If the E register is equal to eleven (EOIF • EO2F • EO8F) then the memory access is a write. The S register is still the addressing register, via gates 2 and 12, and the B register is still the information register, now selected by gate 15, to the write information lines (UWnnS).

Gate 15 will be active during both a read and write access by the Processor, but only during a write access will the Memory Module sample the status of the write lines. The write level from the Processor, UMWRS, will be true with EO8F • E17F/, enabling the Memory Write Level (WOOD) to the memory module.

Coming into the Processor during a memory write access is the timing level MTOD. With El7F/, indicating that this is not a fetch access, the output of gate 8 will set MWOF. MWOF in turn indicates to the Processor the termination of the write access in the Processor.

Two levels are produced as a result of a memory access by the Processor. These two levels, E Register Equal Zero (EEZL) and E Register Equal Zero and MWOF/ (EWZL), are for use only within the Processor to indicate when a Processor memory access is in progress, other than a fetch access. EEZL is true when the E register equals zero; any access will set the E register bits 1, 2, or 4 making EEZL False. EWZL, also normally True, will go False if EEZL is False or MWOF (Memory Write Obtained Flip-flop) is set. These two levels are primarily used to gate logical functions within the Processor.

A fetch access, using El6F and El7F, can be attempted simultaneous with a read or write access. Normally the fetch access will wait for the data access to take place. For a description of the type of access and priority of accesses, refer to the Processor Flow Charts, 4.01.0.

#### PROCESSOR ACCESS TIMING

The timing diagram in Figure 2.2-2 is for the Processor accessing Core Memory, write and read. The timing diagram will accommodate both the B  $\mu$ 60 (6  $\mu$ 8 memory) and the B  $\mu$ 61 ( $\mu$ 9 memory) timing. The differences in timing which are pertinent to the B  $\mu$ 61 Memory Module are indicated by the dashed lines.

FIGURE 2.2-1 "E" REGISTER GATING

August 1, 1966

##

NOTES: 1. DASHED LINES INDICATE TIMINGS UNIQUE TO B 461 (4 PS CORE).

- "X" POINT SET IS UNCLOCKED SET, GATED BY MDCLP. "X" POINT FF ARE FFN7 TYPES, NO DELAY.

- 3. COULD BE E17F IF PROCESSOR DOING A FETCH ACCESS.

- 4. MRAF INSTEAD OF MROF FOR FETCH ACCESS.

- 5. EEZL = E04F/ E02F/ E01F/

- 6. DELAYED CLOCK IN CENTRAL CONTROL

### 2.3 B REGISTER ALIGNMENT

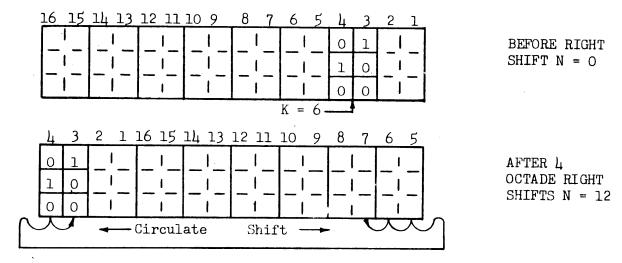

The B register, when handling character type information, can only transfer characters to or from the B register via specified register locations. In this respect, the B register differs from the A register in that any specified character position of the register cannot be directly accessed. In the B register any specified character that must be accessed requires that the specified character position be shifted to the proper register location. When a specified character position is in the proper register location to be accessed, the character position is said to be "aligned" in the alignment station. Figure 2.3-1 illustrates the B register with the alignment stations indicated. If it is desired that a character be transferred from the B register, the Normal output register location is the 16th and 15th octade positions of the B register; that is, the most significant character position (0) of the B register. If it is desired that a character be transferred to the B register, the Normal input register location is the 1st and 2nd octade positions of the B register; that is, the least significant character position (7) of the B register. These two alignment stations are utilized whenever characters are to be transferred or compared. In addition to the normal input and output alignment stations, the Field Add/Subtract operator utilizes two additional alignment stations. During Field Add/Subtract, the output alignment station is the 2nd and 3rd octade positions of the B register; the input alignment station is the 16th and 15th octade positions of the B register. In this case, the input alignment station during Field Add/Subtract occupies the same register location as the normal output alignment station.

When character type information is accessed from core memory and placed in the B register, the characters of the word just accessed may or not be in their normal configuration. In this sense, normal configuration implies that the most significant character position of the word occupies the most significant character position of the B register and the least significant character position of the word occupied the least significant character position of the B register. The N register is utilized to determine whether the characters of the word currently occupy their normal character positions within the word. If the N register equals zero, the word currently occupying the B register is said to be "restored" to its normal configuration. Thus, if the N register is not equal to zero, the B register contents are not in their normal configuration; that is, the characters of the word in the B register have been shifted.

FIGURE 2.3-1. B REGISTER ALIGNMENT STATIONS

#### CHARACTER ALIGNMENT

When it is desired to either transfer a character to or from the B register, the specified character position must first be placed in the proper alignment station. The K register performs the function of specifying the specific character position to be placed in the proper alignment station. Normally the K register points to the character position that is to be aligned to the output alignment station. In the process of aligning a particular character into the output alignment station, the B register contents are either shifted right or left by octades (one-half character shifts) until the specified character position is in the output alignment station. During the shifting of the B register contents, the octade that is shifted out of either end of the register is circulated to the other end of the B register. In conjunction with the octade shifts of the B register, the N register tallies the octade shifts; minus one for each right shift and plus one for each left shift.

Assume that it is desired to transfer a character out of the B register. The desired character must be shifted to the output alignment station if not currently there. Output alignment stations, as referred to here, imply the normal alignment station (16th and 15th octade positions). The output alignment station utilized during Field Add/Subtract is referred to as the secondary output alignment station. Figure 2.3-2 illustrates two cases, where initially the B register contents are in their normal configuration (N = 0) and thereafter the specified character is shifted to the output alignment station. In case 1, the desired character is the 2nd character position of the B register and is subsequently shifted left by octades until it occupies the 16th and 15th octade positions of the B register; note that the N register is incremented to a value of four. In case 2, the desired character is in the 6th character position of the B register, and is subsequently shifted right by octades until it occupies the 16th and 15th octade positions of the B register; note that the N register is decremented to a value of 12.

CASE 1. DESIRED CHARACTER IN 12 AND 11 OCTADE POSITIONS

CASE 2. DESIRED CHARACTER IN 4 AND 3 OCTADE POSITIONS

FIGURE 2.3-2. CHARACTER ALIGNMENT

#### ALIGNMENT SHIFT CONTROL

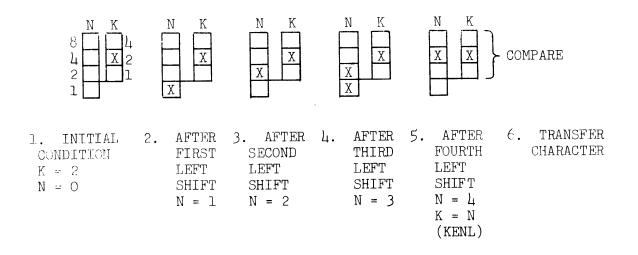

In order to determine the proper direction for shifting the B register contents to align the specified character in the output alignment station, the 4's bit of the K register is interrogated. If the K register equals four or more (4's bit on), the B register is shifted to the right until alignment is attained. If the K register equals less than four (4's bit is off), the B register is shifted left until alignment is attained.

To recognize that a specified character is in the output alignment station, the logical condition (K = N) is interrogated. In case 1 of Figure 2.3-2, the character pointer K is specifying the 2nd character position of the B register. Also, it is illustrated that the word in the B register is initially in its original configuration as indicated by the N register being equal to zero. Examining the K and N registers for equality, and thus alignment, is accomplished through the comparison of the 3 most significant bits (2, 4 and 8) of the N register with the 3 bits of the K register (1, 2 and 4). Effectively, the comparison is recognizing double counts of the N register and thereby recognizing whole character shifts of the B register.

For example: If initially K=2 and N=0 (Case 1), the illustration of Figure 2.3-3 shows the conditions existing during the shifting of the specified character into the output alignment station. When the condition K=N is recognized (the logical level KENL goes true), as indicated in step 5, the following clock pulse transfers the specified character out of the output alignment station. Simultaneously, if additional characters require transfer, the K register is incremented, the B register is shifted another octade position and the N register is incremented to tally the shift. Thereafter, with an additional shift of the B register, K will again equal N and the process is repeated until all required characters are transferred.

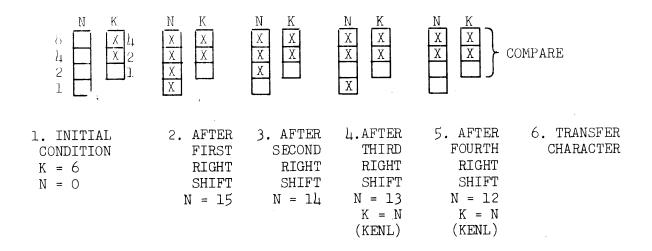

FIGURE 2.3-3. LEFT SHIFT ALIGNMENT

Similarly, if a right shift is indicated, as in Case 2 of Figure 2.3-2, the N register will be decremented during the alignment procedure as shown in Figure 2.3-4. Note that in this case, when the logical condition of K = N is first recognized (KENL is true), only one-half of the desired character is in the output alignment station. This condition is recognized by the 1's bit of the N register being in the set state. Therefore, even though the logical condition of KENL is true, one additional shift of the B register is required to place the complete character in the output alignment station. When shifting to the right, the logical condition of (KENL • NOIF') indicates the alignment of the specified character is completed.

FIGURE 2.3-4. RIGHT SHIFT ALIGNMENT

#### INPUT ALIGNMENT STATION

From the preceding discussion, it is observed that the logical condition of KENL indicates the specified character is in the output alignment station. Therefore, in order to place the specified character position into the input alignment station, two left shifts and a corresponding circulate of the B register contents will place the specified character in the input alignment station. This is the normal procedure utilized.

#### RESTORATION OF THE B REGISTER

During the execution of certain operators the contents of the B register must be restored to their original configuration. In this case, the status of the 8's bit of the N register is interrogated to determine the most expedient method to restore the word. If the 8's bit is set (NO8F), the B register contents are shifted left by octades, with a corresponding increment of the N register, until the N register equals zero. If the 8's bit is reset (NO8F'), the B register contents are shifted to the right, with a corresponding decrement of the N register, until the N register equals zero. When NEZL is true (N equals zero), the contents of the B register are in their original configuration.

### ALIGNMENT DURING FIELD ADD/SUBTRACT

During the field Add/Subtract Operation, the same logic is utilized to place the specified character in the secondary alignment station as is utilized to align to the normal alignment station. If, when the B register contents are in their normal configuration (N equals zero), the N register is preset to the value of 13, the alignment procedure, when executed, will place the desired character in the secondary output alignment station. During the restoration process in this case, the B register is shifted and the N register counted until the N register equals 13.

#### 2.4 PARALLEL ADDER

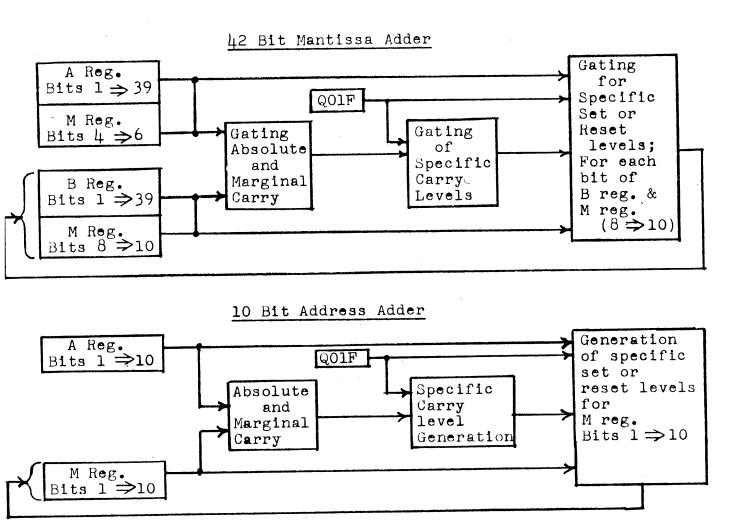

The parallel adder is a straight binary D.C. level adder. The parallel adder is mechanized in two configurations:

- 1. The 42 Bit Mantissa Adder

- 2. The 10 Bit Address Adder

The 42 bit mantissa adder may also function as a 39 bit adder. The basic add logic of both the mantissa and address adder is the same, with the primary difference in the number of bits which are added and the specific registers which are utilized.

The parallel adder is capable of addition in only one clock pulse time. To facilitate the single pulse addition, logic is provided to determine the presence of a carry prior to the actual addition. Because the parallel adder is only capable of addition, subtraction is a function of complement addition.

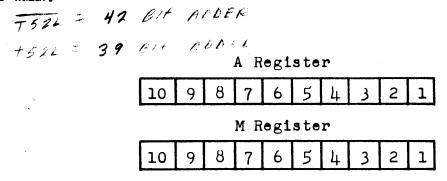

Figure 2.4-1 shows the 42 Bit Mantissa Adder and the 10 Bit Address Adder in block diagram form. The 42 bits of the mantissa adder are made up from the 39 bits of the A and B registers, respectively, plus their respective 3 bit extension which is contained within the M register. The following two equations state the action performed by the parallel mantissa and address adder, respectively.

Logic for the Mantissa Adder

$$B \leftarrow B + A \equiv M [10 \Rightarrow 8] B [39 \Rightarrow 1] \leftarrow M [10 \Rightarrow 8] B [39 \Rightarrow 1] + M [6 \Rightarrow 4] A [39 \Rightarrow 1] + QO1F$$

Logic for the Address Adder

$$M \leftarrow M+A \equiv M [10 \Rightarrow 1] \leftarrow M [10 \Rightarrow 1] + A [10 \Rightarrow 1] + QO1F$$

FIGURE 2.4-1. 42 BIT MANTISSA/10 BIT ADDRESS ADDER

#### BASIC ADDER LOGIC

Due to the binary nature of the parallel adder, it is sufficient to explain the addition of only two binary bits. Each succeeding binary bit position has a similar bit configuration.

Consider the addition of two binary bits, which we will call A and B, plus a possible carry input. The only possible bit configurations that can occur are:

- 1. A and B zero, with or without a carry

- 2. A and B one, with or without a carry

- 3. A zero and B one, with or without a carry

- 4. A one and B zero, with or without a carry

With these the only possible bit configurations, the logic necessary to sum the A and B bits (with or without a carry) and then place the sum in the B bit position, can be stated simply as:

$$\Delta B = (A \bullet CARRY') + (A' \bullet CARRY)$$

Note that the logic is only written in the form to complement the B bit if required. If the B bit is already in the correct state, no further action is necessary. Figure 2.4-2 shows the possible bit configurations previously stated. Note that the equation for  $\Delta$ B is valid.

| Common Bit Positions Indicated |   |   |   |    |     |    |   |   |

|--------------------------------|---|---|---|----|-----|----|---|---|

| С                              | 1 | 1 | 0 | 0  | 0   | 0  | 1 | 1 |

| A                              | 0 | 0 | 1 | 1  | 0   | 0  | 1 | 1 |

| В                              | 0 | 1 | 0 | 1  | 0   | 1  | 0 | 1 |

|                                |   |   |   | Do | Not | ΔB |   |   |

FIGURE 2.4-2. B BIT COMPLEMENT

To mechanize an adder to sum a series of bit positions in parallel requires a knowledge of a carry from the previous bit position. An equation for the add logic of the second bit of a two bit configuration follows. Note that this equation is similar to the equation for \$\textit{A}\$B with the carry portion of the equation expanded to include the specific terms of the preceeding bit position.

```

ΔBmnF = AmnF • (Amn-1F' • Bmn-1F'

+ Amn-1F' • Wmn-2C'

+ Bmn-1F' • Wmn-2C')

+ AmnF' • (Amn-1F • Bmn-1F

+ Amn-1F • Wmn-2C

+ Bmn-1F • Wmn-2C)

```

### NOTE

In order to facilitate writing the equation for a number of bit positions, the notation of mn is utilized:

mn = EVEN bit position, ex. 02, 04, 06, etc.

mn-l = ODD bit position, ex. 01, 03, 05, etc.

W = Adder Logic

In Figure 2.4-3, an example of two bit positions of the A and B register illustrate the usage of the equation for  $\triangle BmnF$ . Note the equation is valid for all possible bit combinations that will complement the B bit.

| Bit | mn | mn-l |

|-----|----|------|----|------|----|------|----|------|----|------|----|------|

| С   |    |      |    | 0    |    | 0    |    |      |    | 1    |    | 1    |

| A   | 1  | 0    | 1  | 0    | 1  |      | 0  | 1    | 0  | 1    | 0  | `    |

| В   | Δ  | 0    | Δ  |      | Δ  | 0    | Δ  | 1    | Δ  |      | Δ  | 1    |

FIGURE 2.4-3. COMPLEMENT EVEN BIT POSITION

### · CARRY LOGIC

From the two previously stated equations to set the sum in the B register (  $\Delta$ Bmn-lF and  $\Delta$ BmnF), knowledge of a carry from a previous bit position is required. In order to add all bit positions at one clock pulse time, knowledge of the existance of a carry into ALL bit positions is required prior to the actual summing process.

### Absolute Carry

It is not always necessary to know if a <u>carry</u> exists from a previous bit position in order to determine if a subsequent carry will result from a given bit position. For those carries which do not require information relative to a prior carry, the carry logic can be written directly. All that is necessary is to know the status of the preceding bit position. The following equation for WmnR states the logic for an Absolute Carry. The letter W indicates adder logics while the letter R indicates absolute carry.

WmnR = AmnF • BmnF

- + AmnF Amn-lF Bmn-lF

- + BmnF Bmn-lF Amn-lF

Figure 2.4-4 illustrates three examples of an absolute carry, corresponding to each of the OR terms of the equation for an absolute carry.

| Bit | mn mn-l | mn | mn-l | mn | mn-l |

|-----|---------|----|------|----|------|

| A   | 1       | 1  | 1    |    | ı    |

| В   | 1       |    | 1    | 1  | ı    |

FIGURE 2.4-4. BIT COMBINATION FOR WmnR

# Marginal Carry

For those bit positions which do require a carry from a prior bit position to develop a carry from their own bit position, an equation is written to indicate that the specific bit position in question has a marginal carry. The interpretation of a marginal carry is as follows: There is a carry from the bit position in question if there is a marginal carry preceded by an absolute carry or a series of marginal carries preceded by an absolute carry. The equation for a marginal carry, WmnM, is as follows; M indicates a marginal carry.

WmnM = AmnF • Amn-lF + AmnF • Bmn-lF • BmnF • Amn-lF + BmnF • Bmn-lF

Figure 2.4-5 illustrates four examples of a marginal carry corresponding to each of the OR terms of the equation for a marginal carry.

| Bit | mn | mn-l | mn | mn-l | mn | mn-l | mn | mn-l |

|-----|----|------|----|------|----|------|----|------|

| A   | 1  | 1    | 1  |      |    | 1    |    |      |

| В   |    |      |    | 1    | 1  |      | 1  | 1    |

FIGURE 2.4-5. MARGINAL CARRY FROM POSTTION mn

### Carry

With the knowledge of an absolute or marginal carry for each even bit position, it can then be determined if a carry from any even bit position does indeed exist. An example of the logical equation stating the existence of an actual carry for bit position 6 is as follows: C indicates a carry level. The term WOOC indicates a carry into the low order end of the register.

W06C = W06R + W06M • W04R + W06M • W04M • W02R + W06M • W04M • W02M • W00C

The existence of an actual carry is seen to result from:

- 1. An absolute carry