PDP-15 SYSTEMS

FP15

FLOATING POINT PROCESSOR

MAINTENANCE MANUAL

VOLUME 1

1st Edition June 1971

Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

# CONTENTS

|         |                                               | Page |         |                                                           | Pag  |

|---------|-----------------------------------------------|------|---------|-----------------------------------------------------------|------|

| CHAPTE  | R 1 INTRODUCTION                              |      | 3.7.4   | Extended Integer                                          | 3-1  |

| 1.1     | General                                       | 1-1  | 3.7.5   | Single-Precision Integer                                  | 3-1: |

| 1.2     | Floating-Point Processor Physical Description | 1-1  | 3.8     | Interrupt Cycle Interface                                 | 3-14 |

| 1.3     | Functional Description                        | 1-2  | 3.8.1   | INT 1 Cycle                                               | 3-1- |

| 1.3.1   | Operating Cycles                              | 1-2  | 3.8.2   | INT 2 Cycle                                               | 3-1- |

| 1.3.2   | Major Register Functional Descriptions        | 1-3  | 3.9     | Interrupt Cycle                                           | 3-1: |

|         | Major Register Folierioliai Descriptions      |      | 3.10    | FP15/CPU Control                                          | 3-1  |

| CHAPTER | R 2 MODULE DESCRIPTIONS                       |      | CHAPTER | 4 INSTRUCTION SET                                         |      |

| 2.1     | General                                       | 2-1  | 4.1     | Introduction                                              | 4-1  |

| 2.1.1   | M238 Synchronous Up/Down Counter              | 2-1  | 4.2     | Converting Negative Integers To Sign and Magnitude Format | 4-1  |

| 2.1.2   | M159 Arithmetic Logic Unit                    | 2-1  | 4.3     | Normalize                                                 | 4-1  |

| 2.1.3   | M191 Carry Look-Ahead Generator               | 2-2  | 4.3.1   | Normalization (Except Store, Divide, or Reverse Divide)   | 4-2  |

| 2.1.4   | M248 Right-Shift Parallel Load Register       | 2-3  | 4.3.2   | Store, Divide, or Reverse Divide                          | 4-2  |

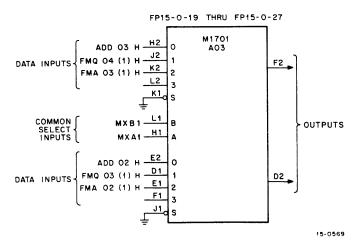

| 2.1.5   | M1701 Data Selector                           | 2-3  | 4.4     | Rounding                                                  | 4-2  |

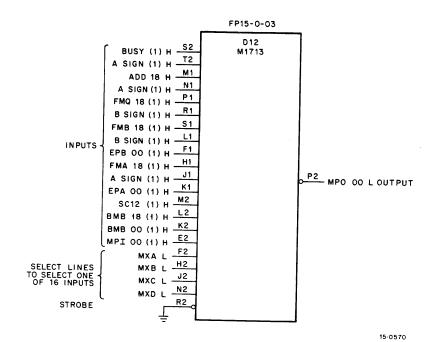

| 2.1.6   | M1713 16-To-1 Data Selector                   | 2-4  | 4.5     | Guard Bit                                                 | 4-6  |

|         |                                               |      | 4.6     | Floating-Point Addition and Subtraction                   | 4-6  |

| CHAPTER | R 3 FP15/PDP-15 INTERFACE                     |      | 4.6.1   | EXP Cycle                                                 | 4-6  |

|         |                                               |      | 4.6.2   | FUN Cycle                                                 | 4-8  |

| 3.1     | Introduction                                  | 3–1  | 4.6.3   | Processing of Subtracted Quantities                       | 4-10 |

| 3.2     | FETCH Cycle Interface                         | 3-1  | 4.6.3.1 | Overflow                                                  | 4-10 |

| 3.3     | FETCH (Indirect) Cycle Interface              | 3-3  | 4.6.4   | Processing of Added Quantities                            | 4-10 |

| 3.4     | FETCH Cycle Description                       | 3-3  | 4.6.4.1 | Overflow Interrupt Due to Addition or Subtraction         | 4-10 |

| 3.5     | OPAND Cycle Interface                         | 3-7  | 4.6.4.2 | Overflow Interrupt Due to Rounding                        | 4-10 |

| 3.6     | OPAND Cycle Description                       | 3-8  | 4.6.4.3 | Underflow Interrupt Due to Normalizing                    | 4-11 |

| 3.6.1   | Double-Precision Floating-Point Format        | 3-8  | 4.7     | Integer Add and Subtract                                  | 4-12 |

| 3.6.2   | Single-Precision Floating-Point Format        | 3-8  | 4.7.1   | EXP Cycle                                                 | 4-12 |

| 3.6.3   | Extended Integer Format                       | 3-8  | 4.7.2   | FUN Cycle                                                 | 4-12 |

| 3.6.4   | Single-Precision Integer Format               | 3-12 | 4.7.3   | Overflow                                                  | 4-13 |

| 3.7     | WRITE Cycle                                   | 3-12 | 4.7.4   | Integer Reverse Subtraction                               | 4-13 |

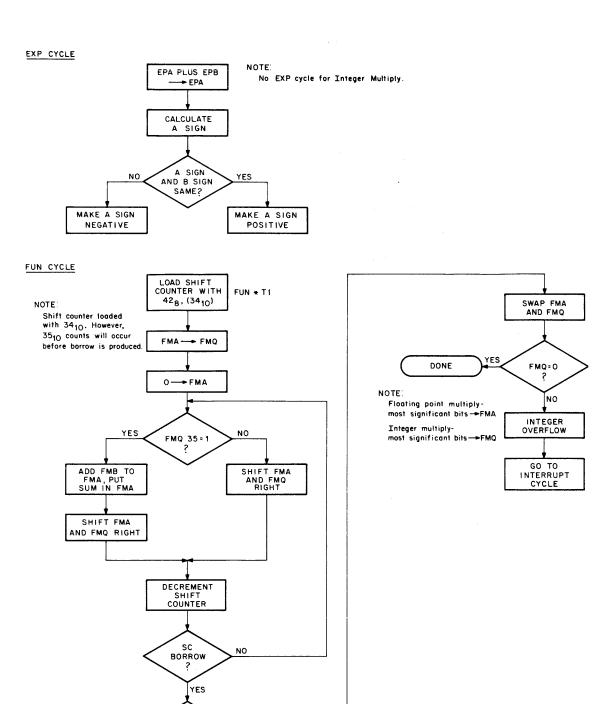

| 3.7.1   | Store JEA                                     | 3–12 | 4.8     | Floating-Point and Integer Multiply                       | 4-13 |

| 3.7.2   | Double—Precision Floating Point               | 3–12 | 4.8.1   | Calculation of Exponents                                  | 4-13 |

| 3.7.3   | Single-Precision Floating Point               | 3-12 | 4.8.2   | Determining Sign of Product                               | 4-13 |

# **CONTENTS** (cont)

|          |                                 | Page |                                                 | Page |

|----------|---------------------------------|------|-------------------------------------------------|------|

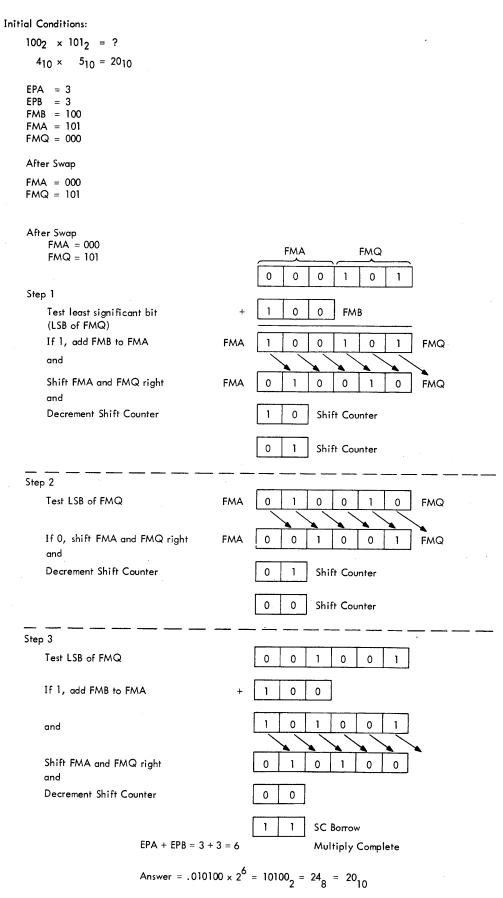

| 4.8.3    | Multiplication of the Mantissas | 4-13 | 4.15 Swap, Load and Swap                        | 4-26 |

| 4.8.4    | Multiply Algorithm              | 4-14 | 4.15.1 Underflow Interrupt                      | 4-26 |

| 4.8.5    | Floating-Point Overflow         | 4-16 | 4.16 Float, Load and Float FMA                  | 4-26 |

| 4.8.5.1  | Overflow Interrupt - EXP Cycle  | 4-16 | 4.17 Fix, Load and Fix                          | 4-28 |

| 4.8.5.2  | Underflow Interrupt - EXP Cycle | 4-16 | 4.18 Load JEA and Store JEA                     | 4-28 |

| 4.8.5.3  | Overflow Interrupt - NOR Cycle  | 4-16 | 4.19 Branch                                     | 4-28 |

| 4.8.5.4  | Underflow Interrupt - NOR Cycle | 4-16 | 4.20 Modify FMA                                 | 4-30 |

| 4.8.5.5  | Integer Overflow                | 4-19 | 4.20.1 Underflow Interrupt Due to Normalization | 4-30 |

| 4.9      | Floating–Point Division         | 4-19 | 4.21 Diagnostic Instructions                    | 4-30 |

| 4.9.1    | Calculation of Exponents        | 4-19 | 4.21.1 Diagnostic Read                          | 4-31 |

| 4.9.2    | Determining Sign of Quotient    | 4-19 | 4.21.2 Diagnostic Step and Read                 | 4-34 |

| 4.9.3    | Division of the Mantissas       | 4-19 | ğ ı                                             |      |

| 4.9.4    | Divide Algorithm                | 4-20 |                                                 |      |

| 4.9.5    | Interrupts                      | 4-21 |                                                 |      |

| 4 9_5,1_ | . Our-flow Intermed EVD Cools   | 4 01 | CHAPTER 5 INSTALLATION AND MAINTENANCE          |      |

| 4.9.5.4 | Underflow Interrupt - FUN Cycle       | 4-21 | 5.1.2 | Indicator Panel/Power Supply Wiring | 5–2 |

|---------|---------------------------------------|------|-------|-------------------------------------|-----|

| 4.9.5.5 | Abnormal Divide - FUN Cycle           | 4–21 | 5.1.3 | H721 Power Supply Wiring            | 5-2 |

| 4.10    | Floating-Point Reverse Divide         | 4–21 | 5.1.4 | Signal Cable Connections            | 5-2 |

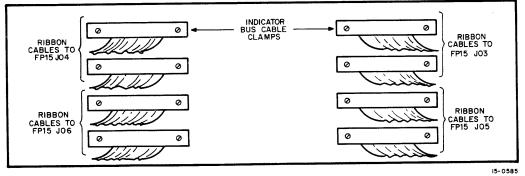

| 4.11    | Integer Division                      | 4-22 | 5.1.5 | Indicator Bus Cable Connections     | 5-2 |

| 4.11.1  | EXP Cycle                             | 4–22 | 5.1.6 | Handwire List                       | 5-2 |

| 4.11.2  | FUN Cycle                             | 4-22 | 5.1.7 | Postinstallation Checks and Tests   | 5-3 |

| 4.11.3  | Divide Algorithm                      | 4-22 | 5.2   | Maintenance                         | 5-3 |

| 4.11.4  | Interrupt Exception - Abnormal Divide | 4-25 | 5.2.1 | FP15 Indicator Panel                | 5-3 |

| 4.12    | Integer Reverse Division              | 4–25 | 5.2.2 | Diagnostic Programs                 | 5-4 |

| 4.13    | Integer Store                         | 4–25 | 5.2.3 | Instruction Tests                   | 5-4 |

| 4.13.1  | Overflow Interrupt                    | 4-25 | 5.2.4 | Random Exerciser                    | 5-4 |

| 4.14    | Floating-Point Store                  | 4-25 | 5.3   | Engineering Drawings                | 5-5 |

| 4.14.1  | EPA Underflow or Overflow Interrupt   | 4-26 |       |                                     |     |

| 4.14.2  | Underflow Interrupt Due to Normalize  | 4-26 |       |                                     |     |

# **ILLUSTRATIONS**

| Figure No. | Title                                                           | Art No. | Page |

|------------|-----------------------------------------------------------------|---------|------|

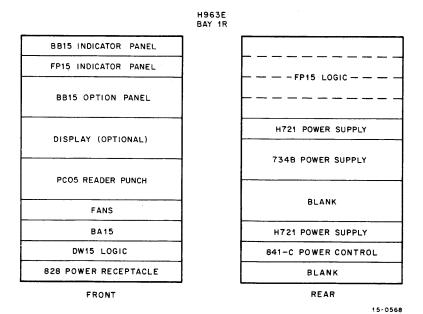

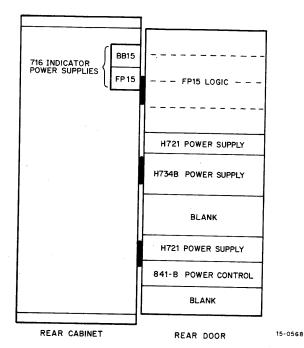

| 1-1        | Cabinet Housing FP15 Logic                                      | 15-0568 | 1-1  |

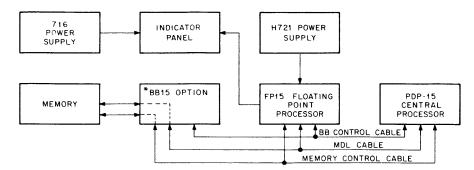

| 1-2        | System Interconnecting Cabling                                  | 15-0575 | 1-2  |

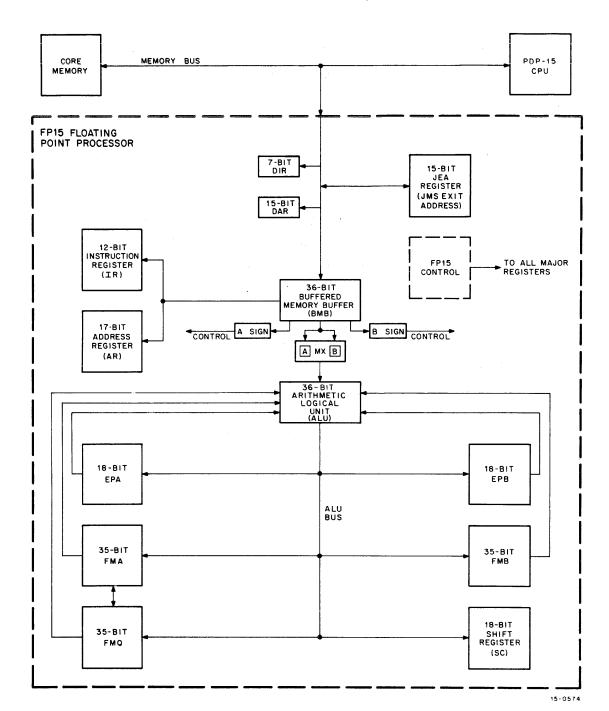

| 1-3        | FP15 Functional Block Diagram                                   | 15-0574 | 1-3  |

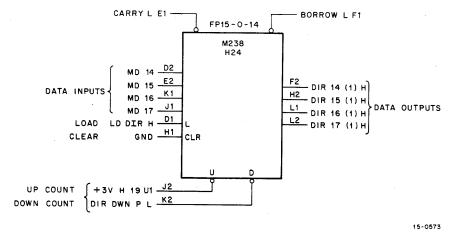

| 2-1        | M238 Synchronous Up/Down Counter                                | 15-0573 | 2-1  |

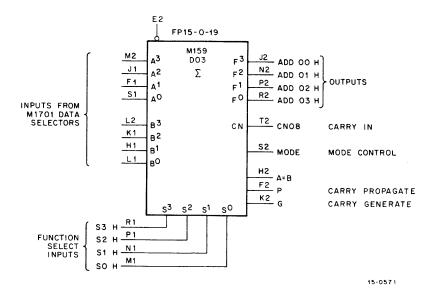

| 2-2        | M159 Arithmetic Logic Unit                                      | 15-0571 | 2-2  |

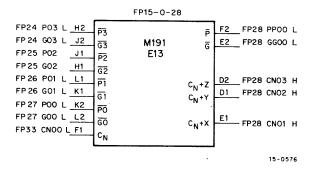

| 2-3        | M191 Carry Look-Ahead Generator                                 | 15-0576 | 2-2  |

| 2-4        | 36-Bit ALU, Full-Carry Look-Ahead in Three<br>Levels            | 15-0577 | 2-2  |

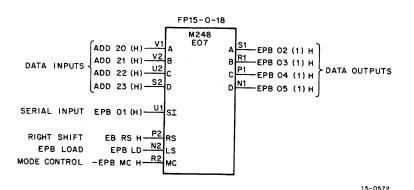

| 2-5        | M248 Right-Shift Parallel Load Register                         | 15-0572 | 2-3  |

| 2-6        | M1701 Data Selector                                             | 15-0569 | 2-4  |

| 2-7        | M1713 16-To-1 Data Selector                                     | 15-0570 | 2-5  |

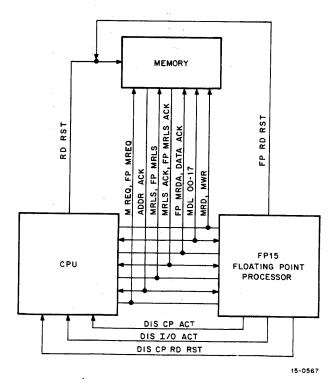

| 3–1        | Major Signal Interface Diagram                                  | 15-0567 | 3-1  |

| 3-2        | Memory InterfaceFETCH Cycle                                     |         | 3-2  |

| 3–3        | Memory InterfaceFETCH Cycle (Indirect)                          |         | 3-3  |

| 3-4        | Memory InterfaceOPAND Cycle                                     |         | 3-7  |

| 3–5        | INT 1 Cycle Interface Diagram                                   |         | 3-14 |

| 3–6        | INT 2 Cycle Interface Diagram                                   |         | 3-15 |

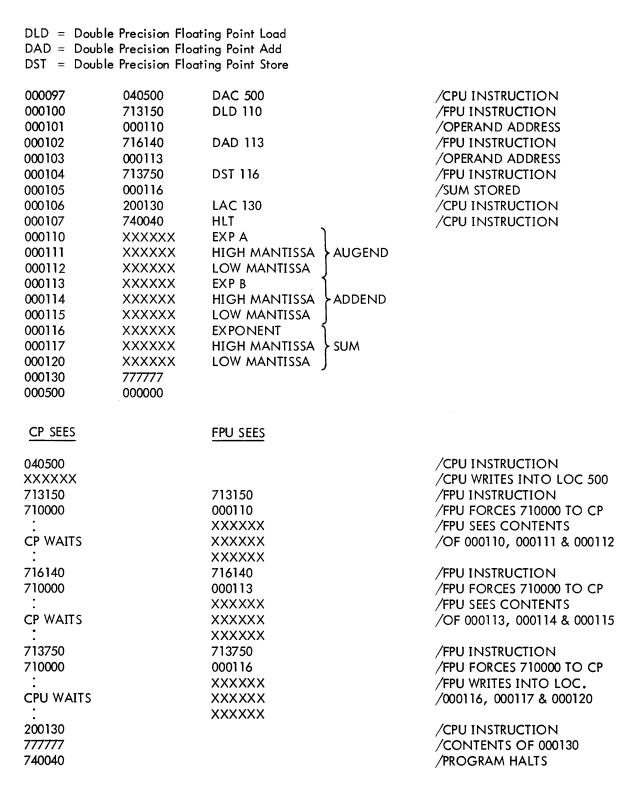

| 3-7        | CPU/FP15 Sample Program                                         |         | 3-17 |

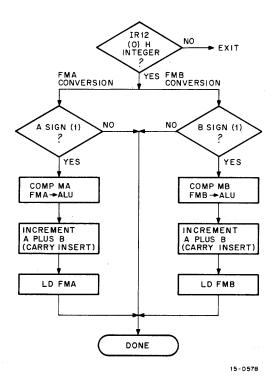

| 4–1        | Converting Negative Integers to Sign and Magnitude              | 15-0578 | 4-1  |

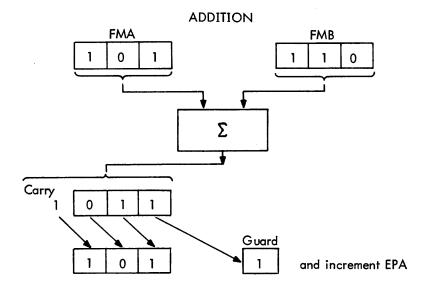

| 4-2        | Guard Bit and Rounding                                          |         | 4-2  |

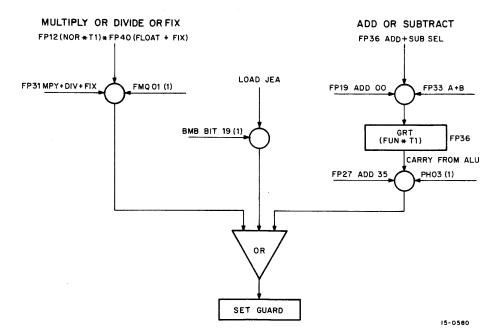

| 4–3        | Flow Diagram for Setting Guard                                  | 15-0580 | 4-6  |

| 4–4        | Multiply Simplified Flow Diagram                                | 15-0581 | 4-14 |

| 4–5        | Multiply Algorithm                                              |         | 4-15 |

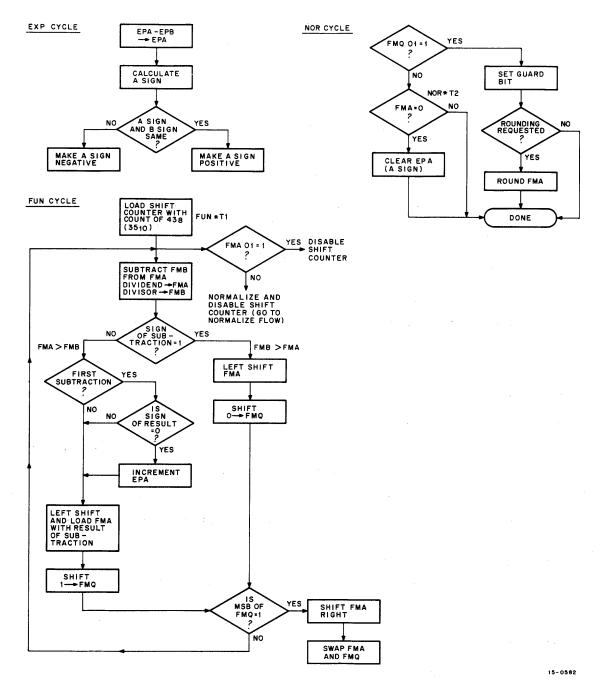

| 4-6        | Floating-Point Divide Simplified Flow Diagram                   | 15-0582 | 4-19 |

| 4-7        | Floating Point Divide Algorithm                                 |         | 4-20 |

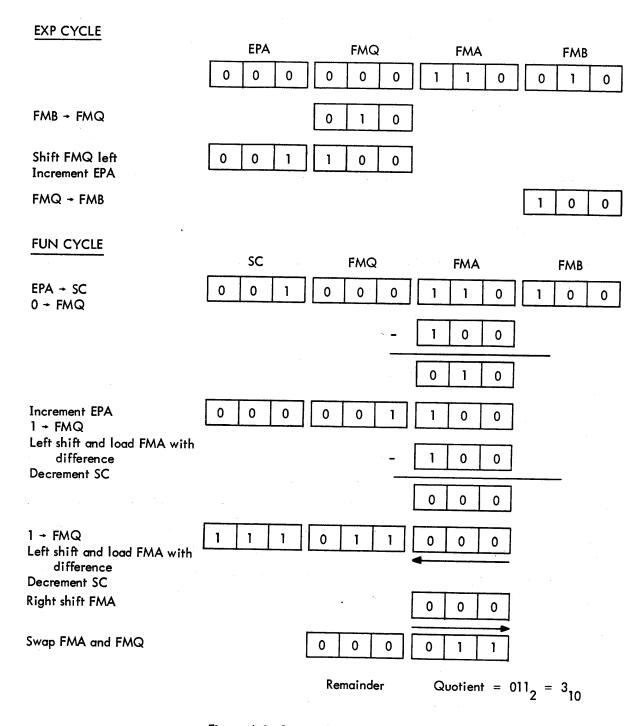

| 4-8        | Integer Divide Algorithm                                        |         | 4-25 |

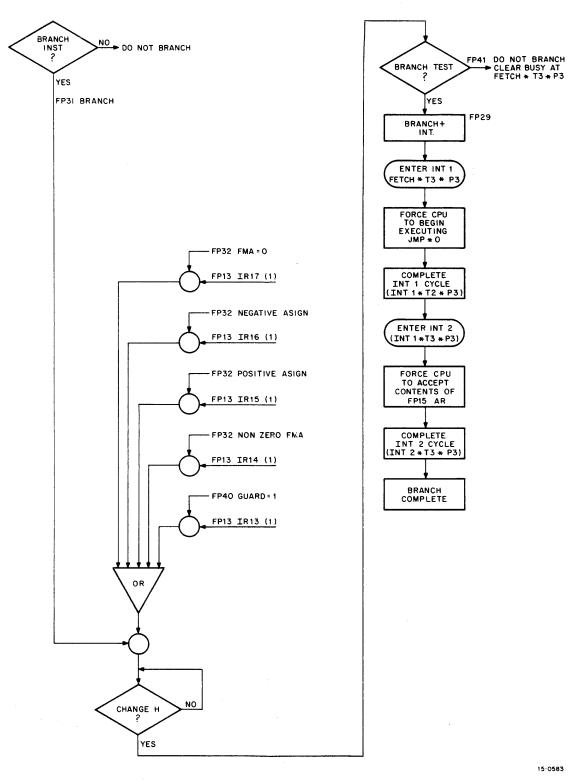

| 4-9        | Branch Instruction Flow Diagram                                 | 15-0583 | 4-30 |

| 5-1        | H963E Cabinet (Bay 1R), Rear View with Mounting Panel Door Open | 15-0568 | 5-1  |

| 5-2        | FP15 Indicator Bus Connections                                  | 15-0585 | 5-2  |

# **ENGINEERING DRAWINGS**

|     | Drawing No. |               | Title                         | Page |

|-----|-------------|---------------|-------------------------------|------|

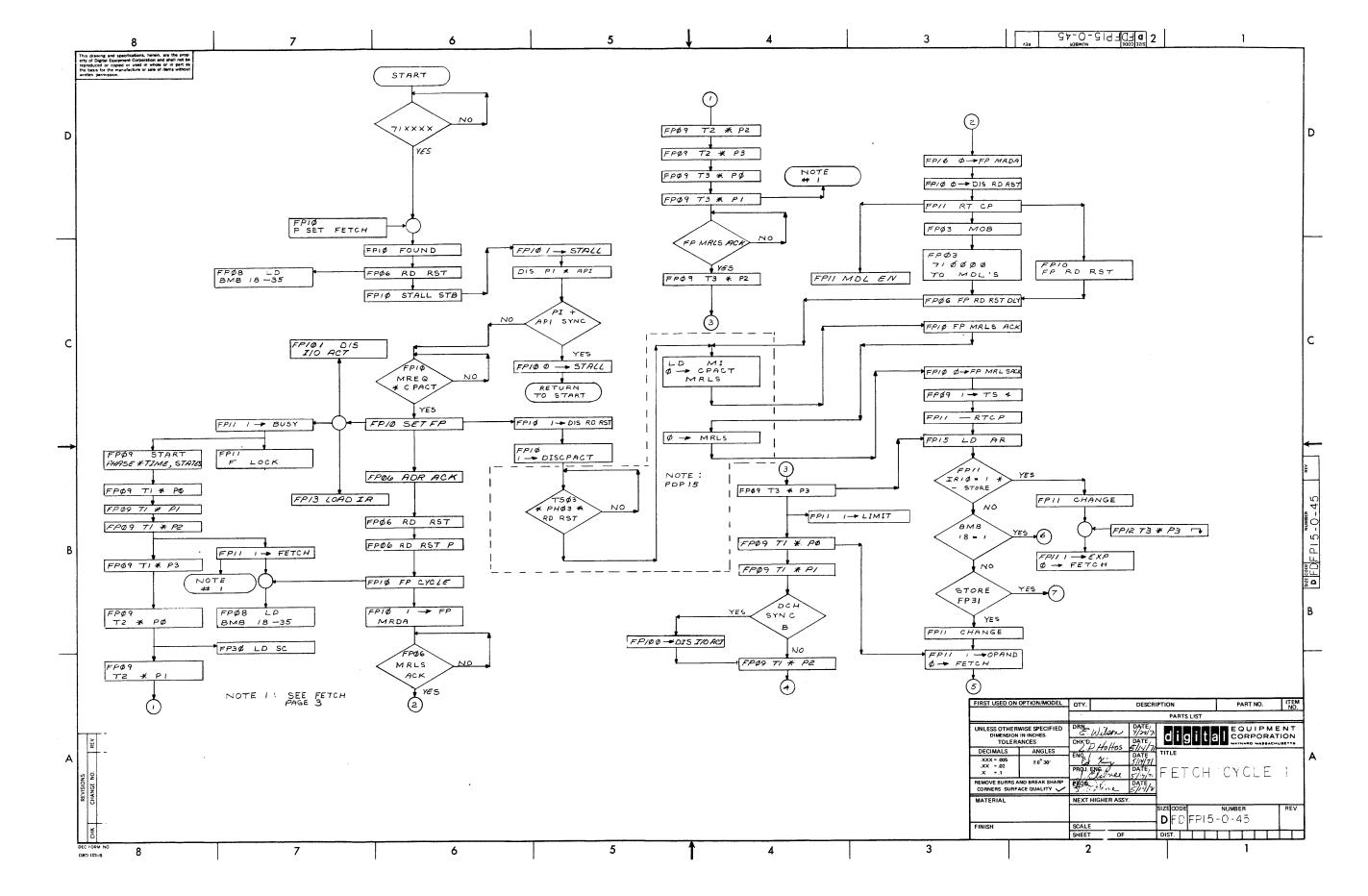

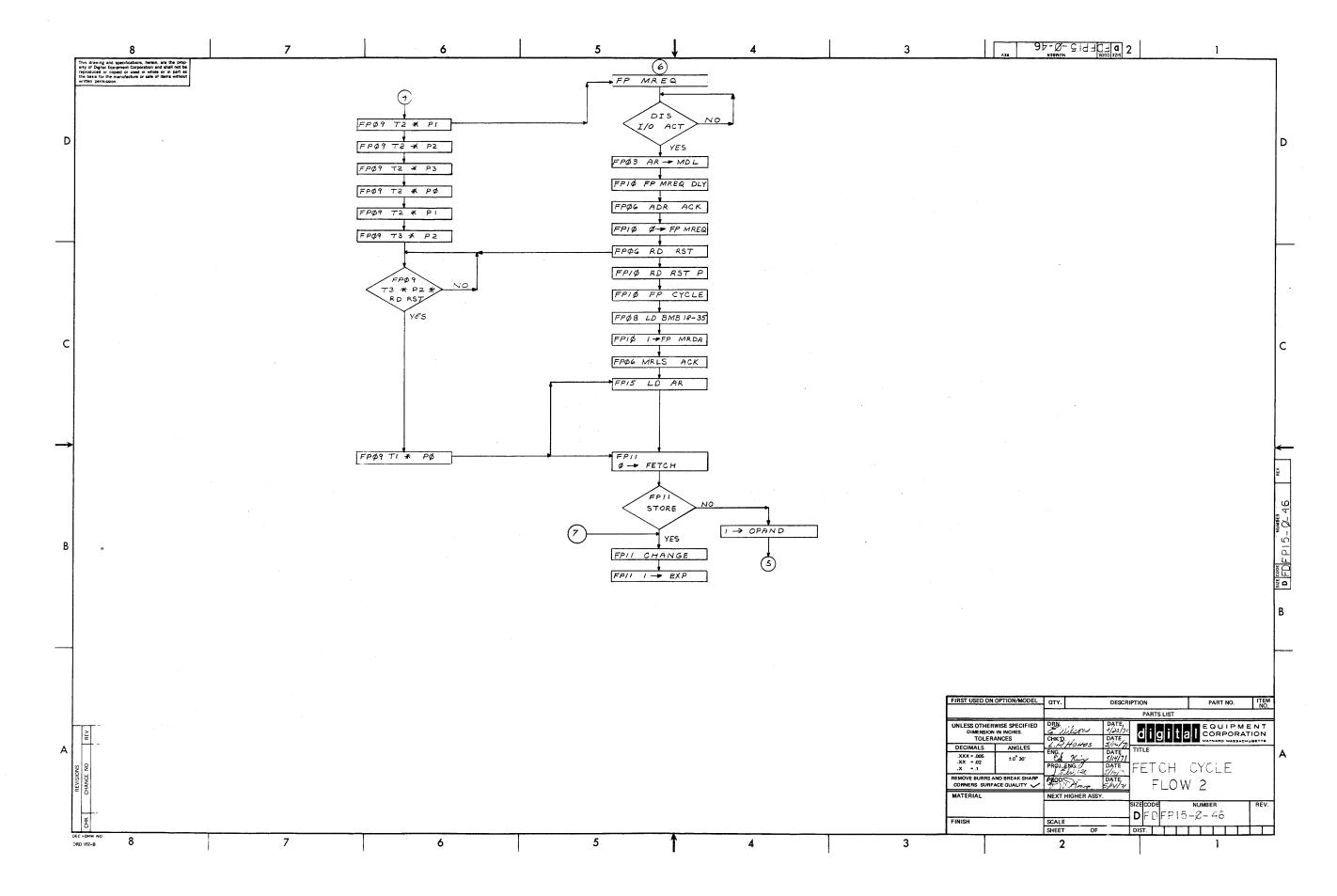

|     | D-FD-FP15-  | 0-45          | Fetch Cycle Flow 1            | 3-4  |

|     | D-FD-FP15-  | 0-46          | Fetch Cycle Flow 2            | 3-5  |

|     | D-FD-FP15-  | 0 <b>-4</b> 7 | Fetch Cycle Flow 3            | 3-6  |

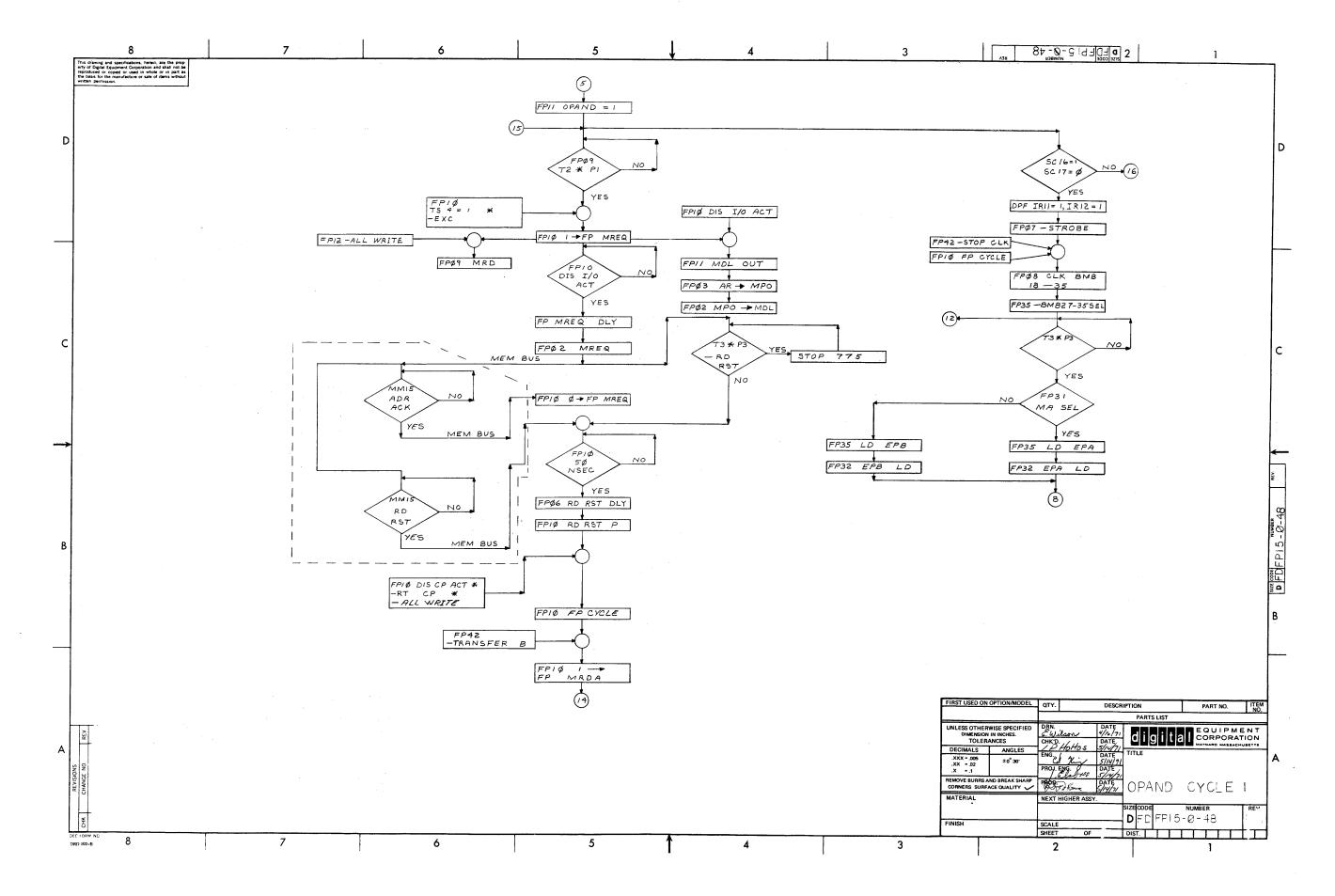

|     | D-FD-FP15-  | 0–48          | Opand Cycle Flow 1            | 3-9  |

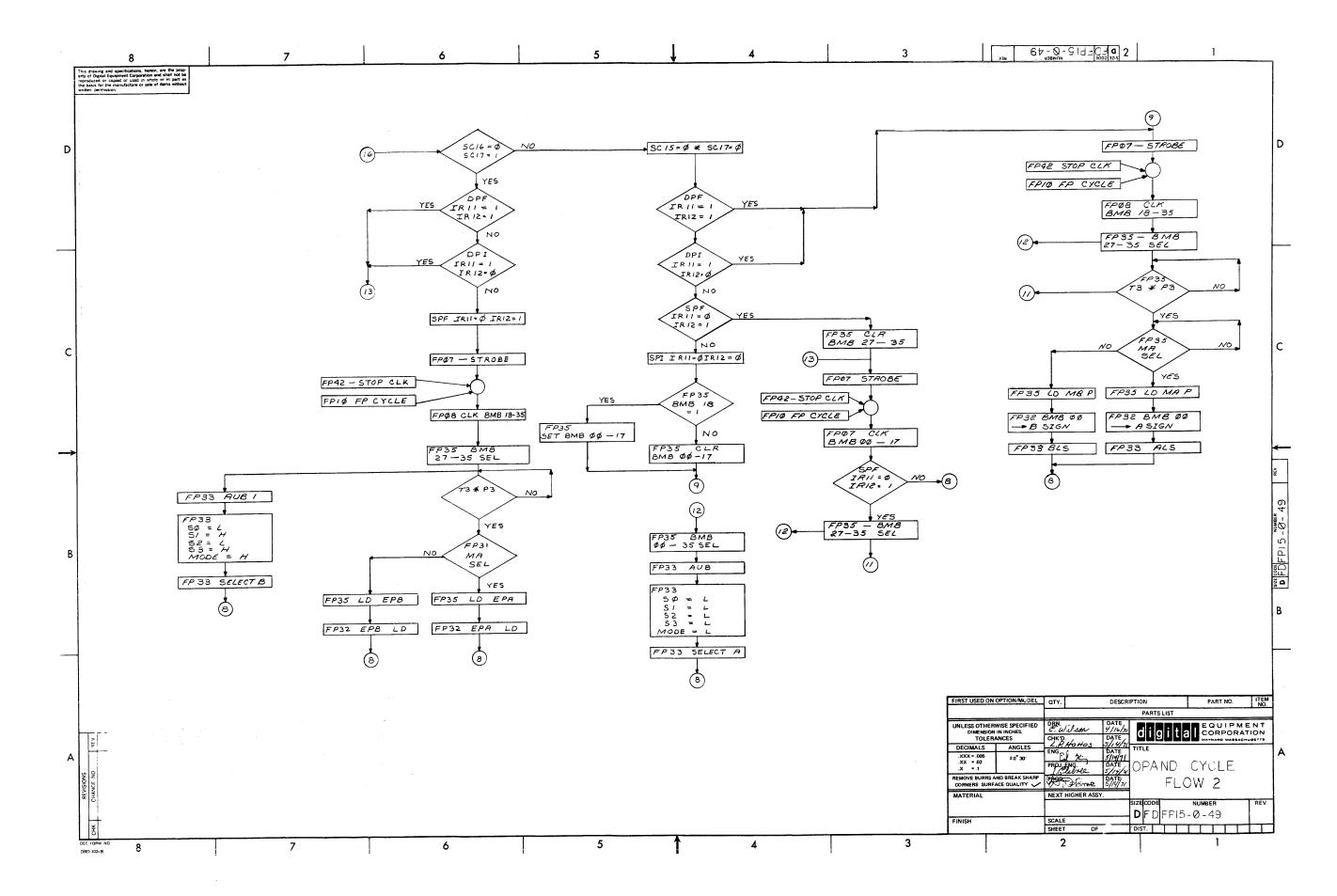

|     | D-FD-FP15-0 | 0-49          | Opand Cycle Flow 2            | 3–10 |

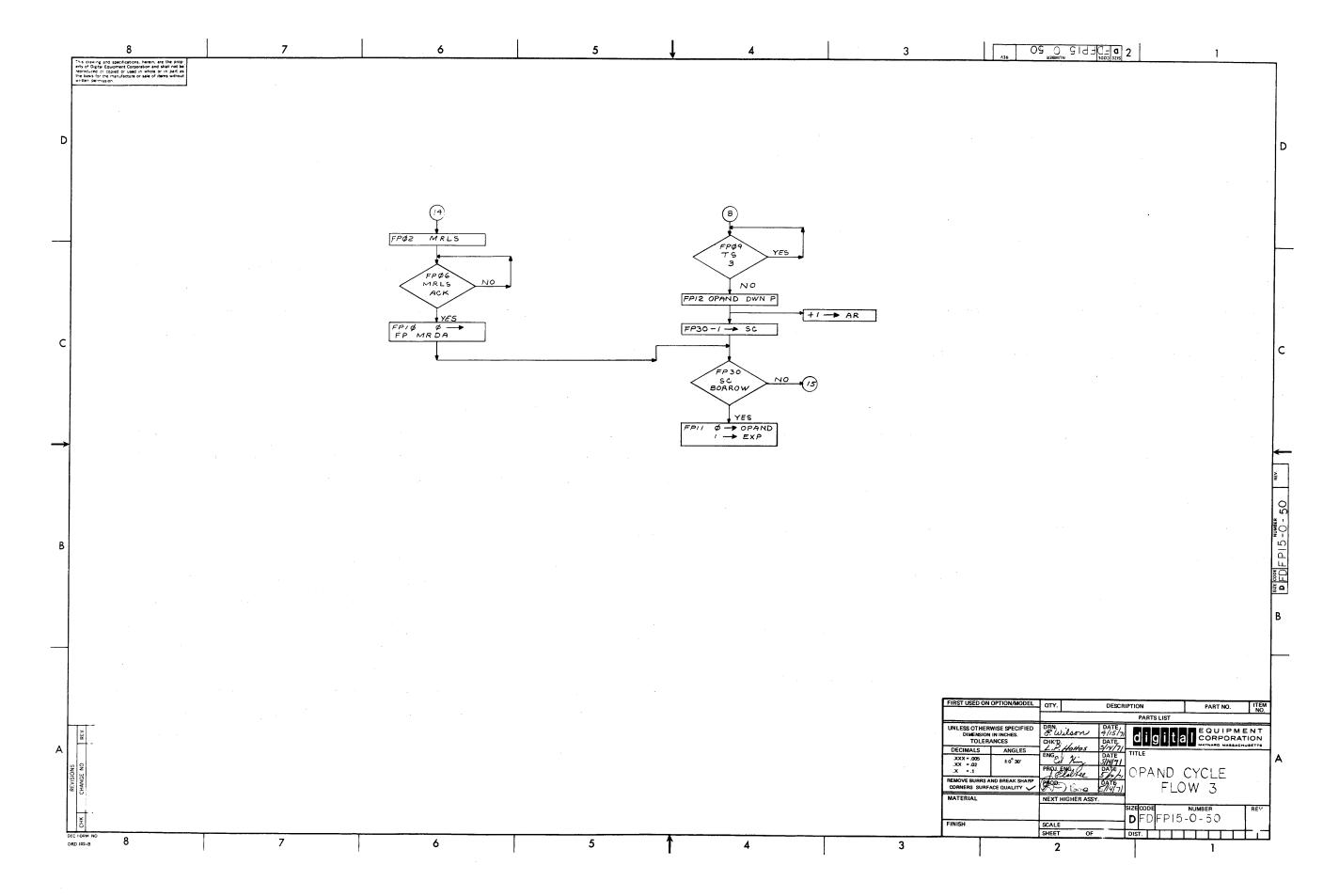

|     | D-FD-FP15-0 | 0-50          | Opand Cycle Flow 3            | 3-11 |

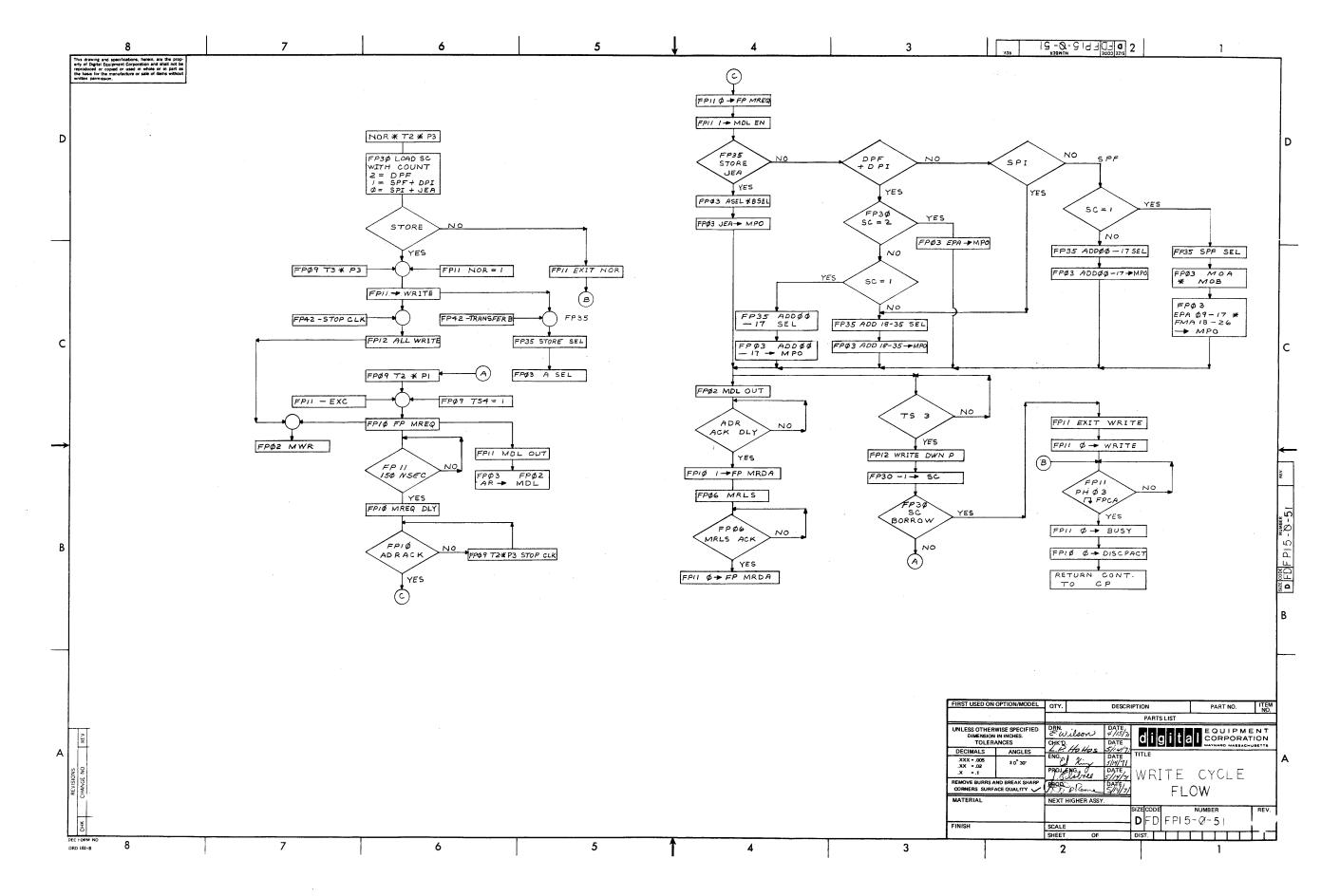

|     | D-FD-FP15-0 | 0-51          | Write Cycle Flow              | 3-13 |

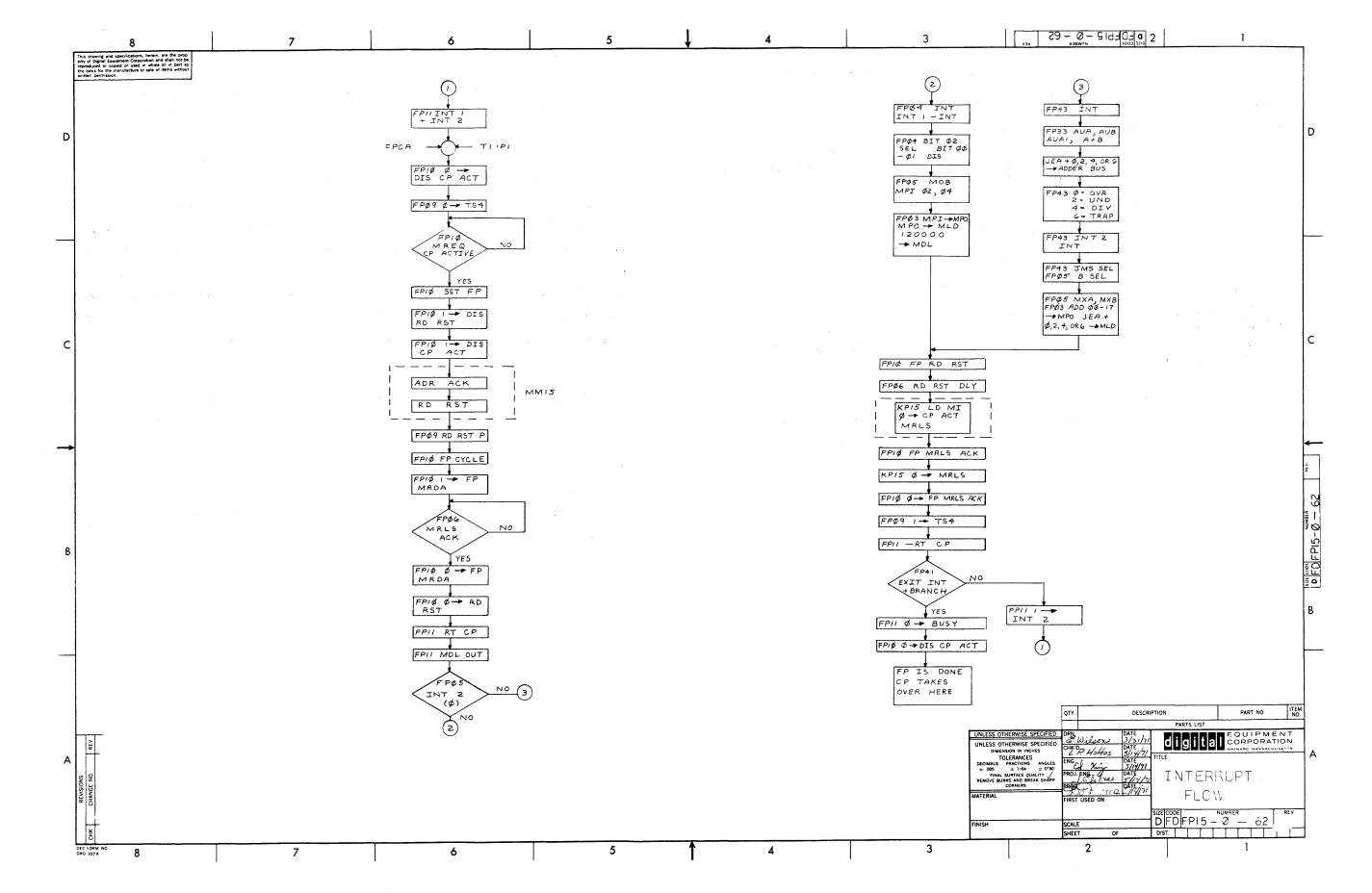

|     | D-FD-FP15-0 | 0-62          | Interrupt Flow                | 3-16 |

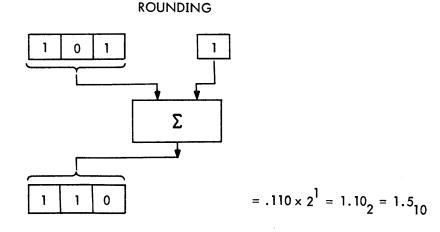

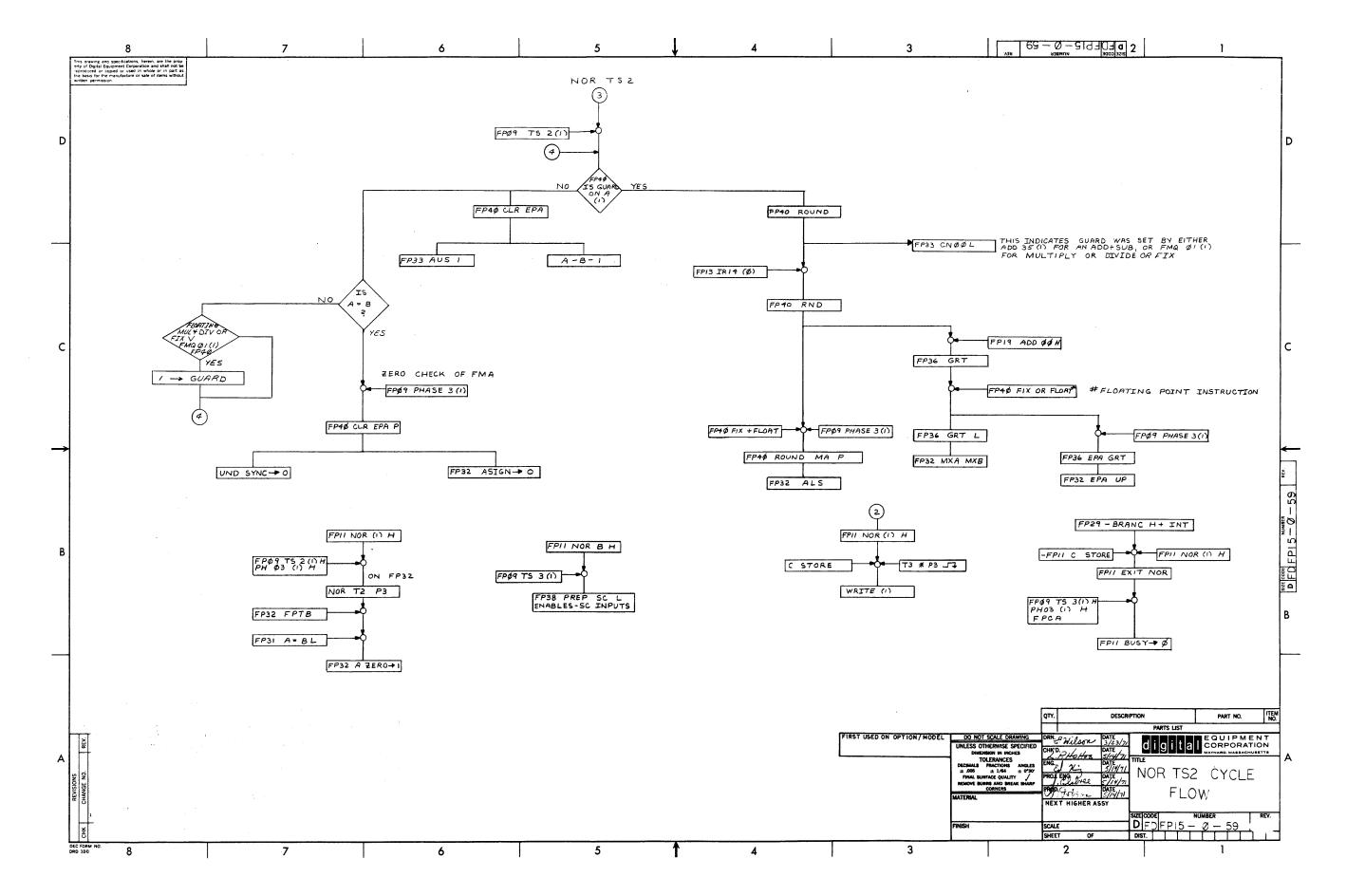

|     | D-FD-FP15-0 | D <b>-</b> 58 | NOR TS1 Cycle Flow            | 4-3  |

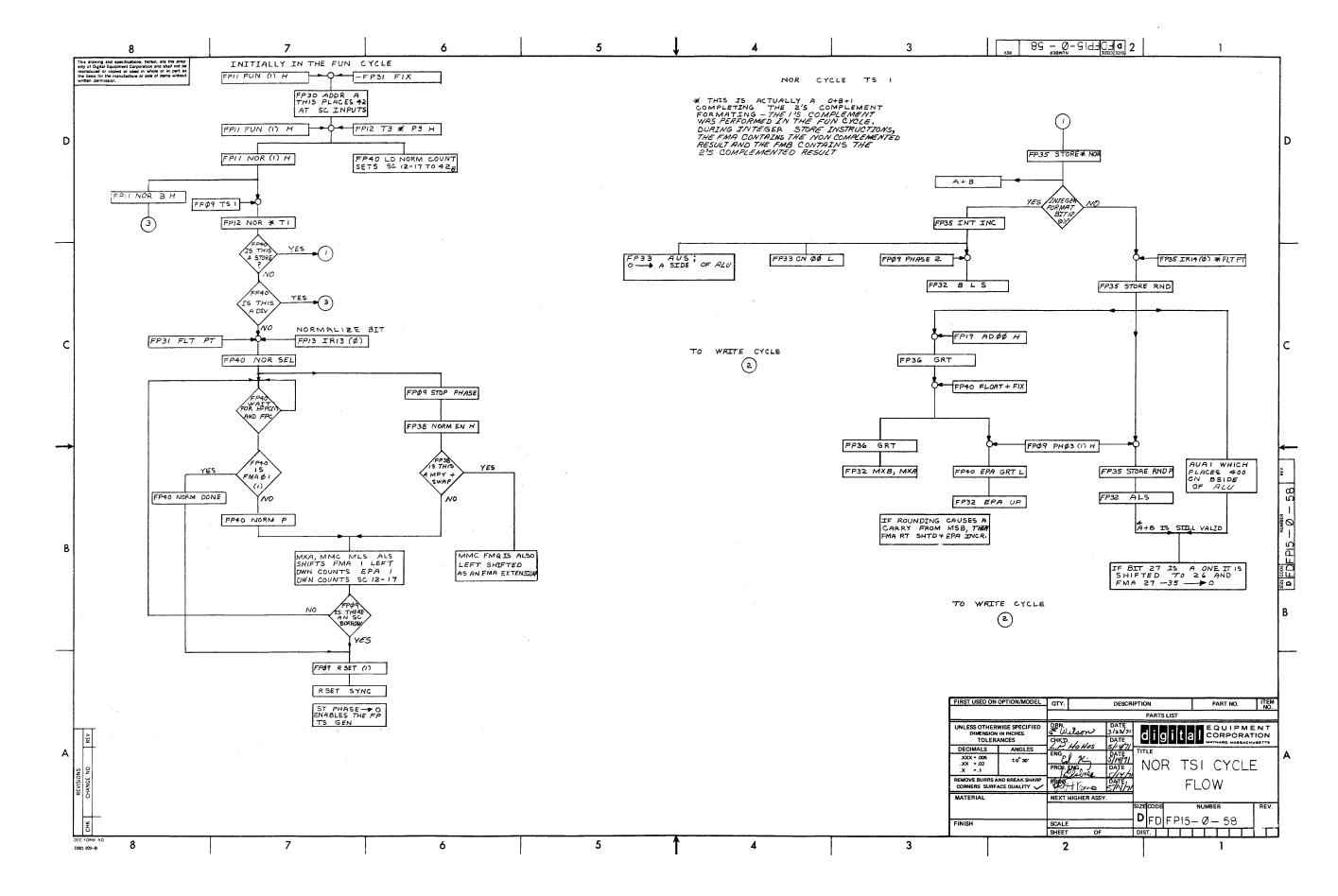

|     | D-FD-FP15-0 | 0-59          | NOR TS2 Cycle Flow            | 4-4  |

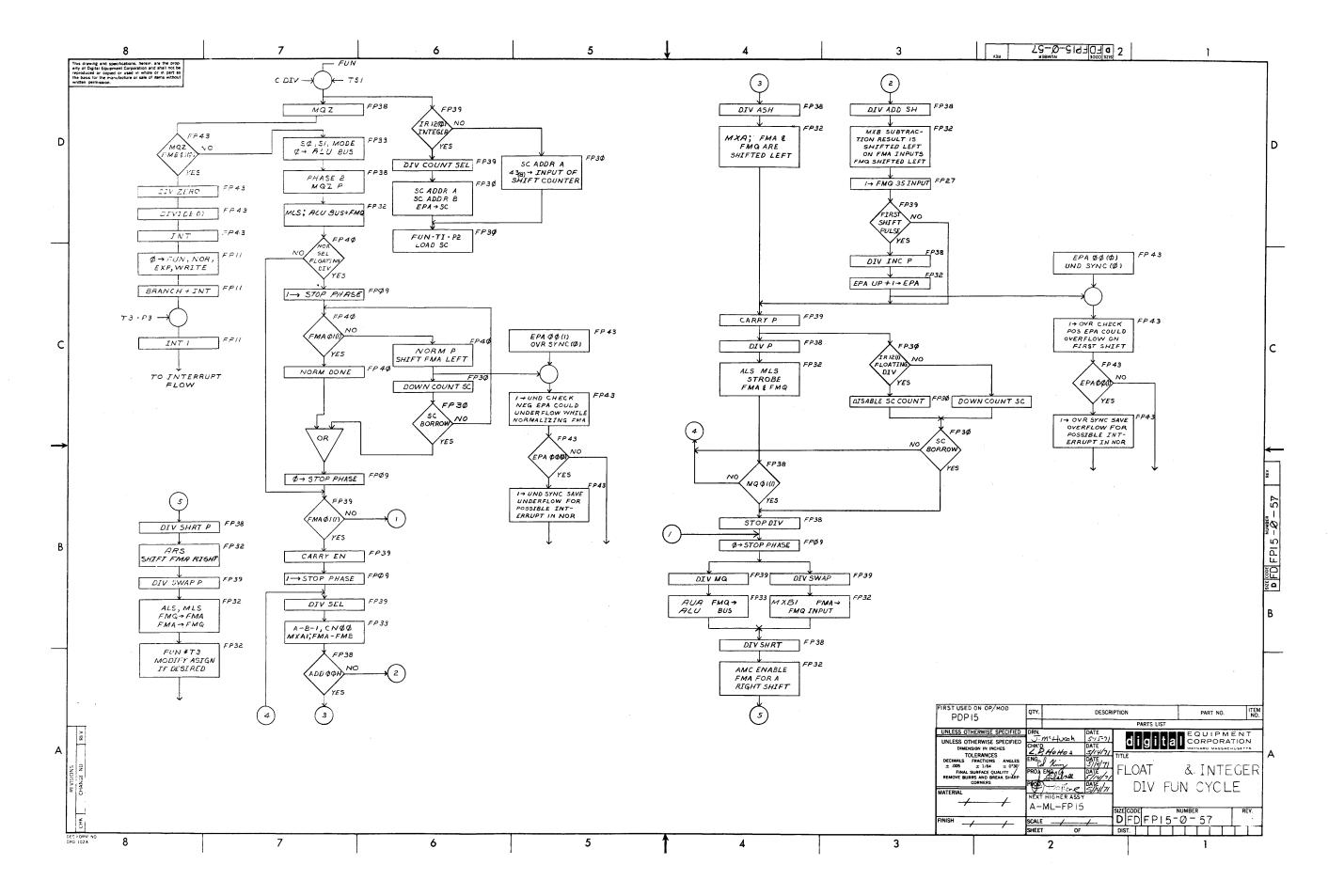

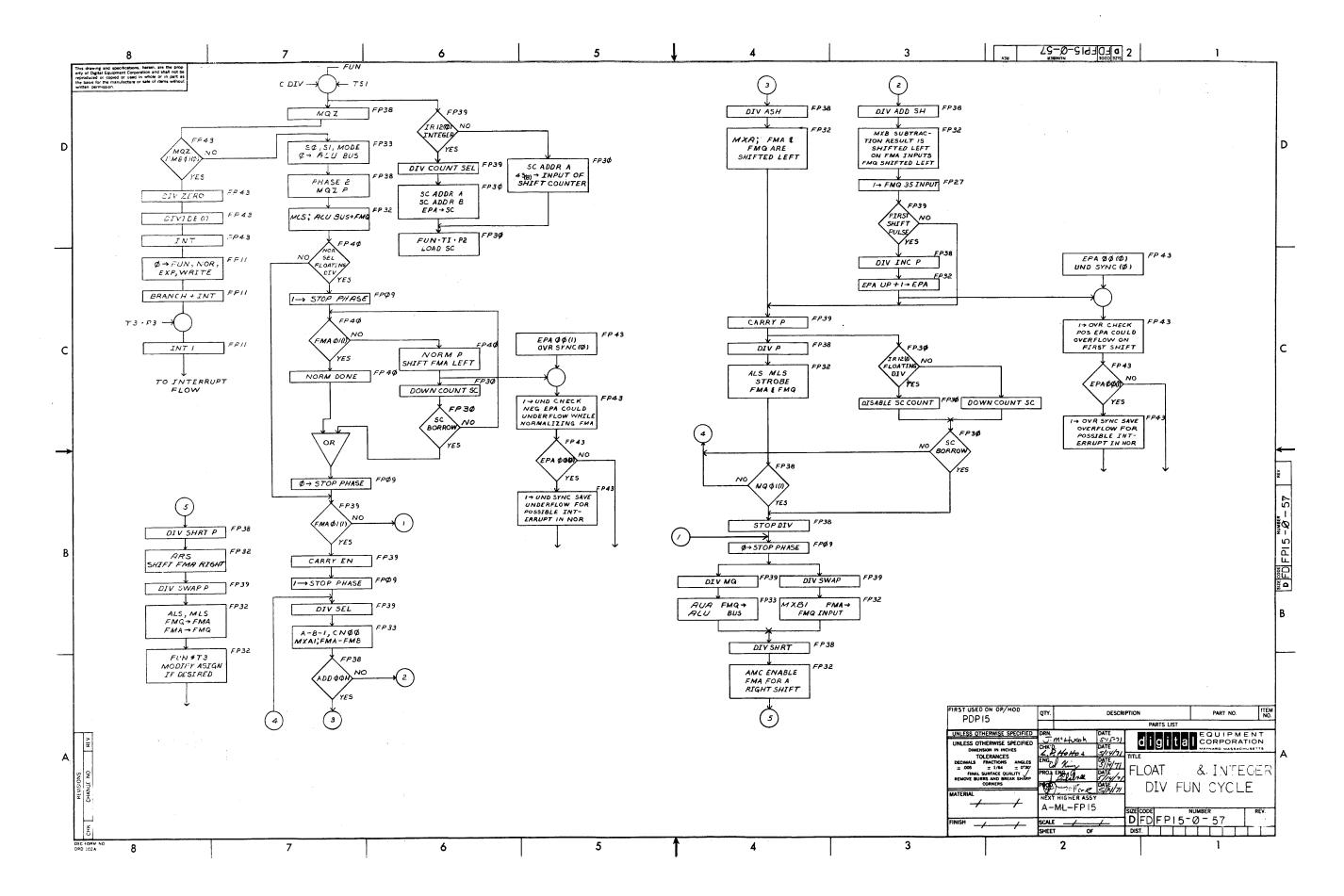

|     | D-FD-FP15-0 | D <b>-</b> 57 | Float & Integer Div Fun Cycle | 4-5  |

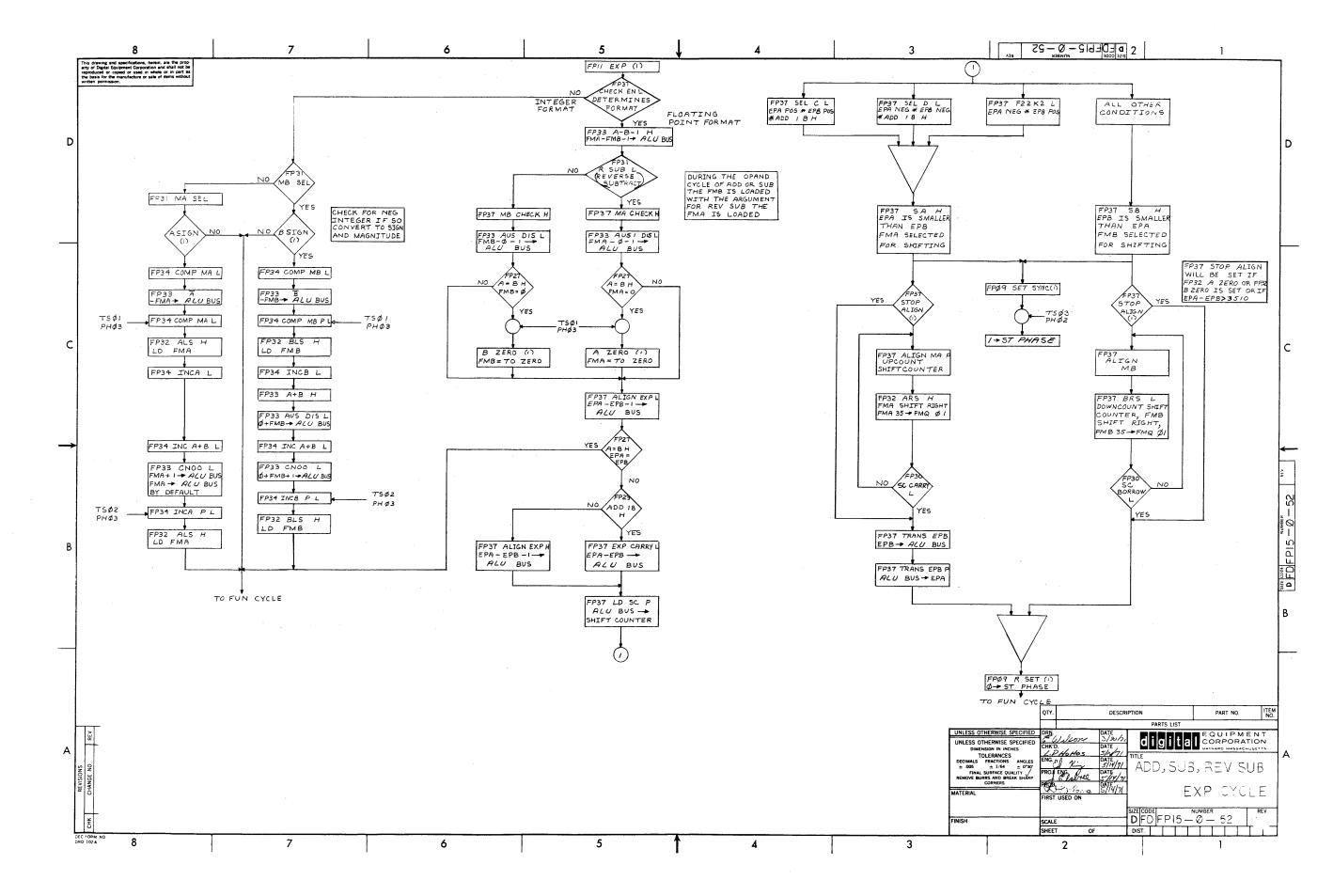

|     | D-FD-FP15-0 | ) <b>-</b> 52 | Add, Sub, Rev Sub, Exp Cycle  | 4-7  |

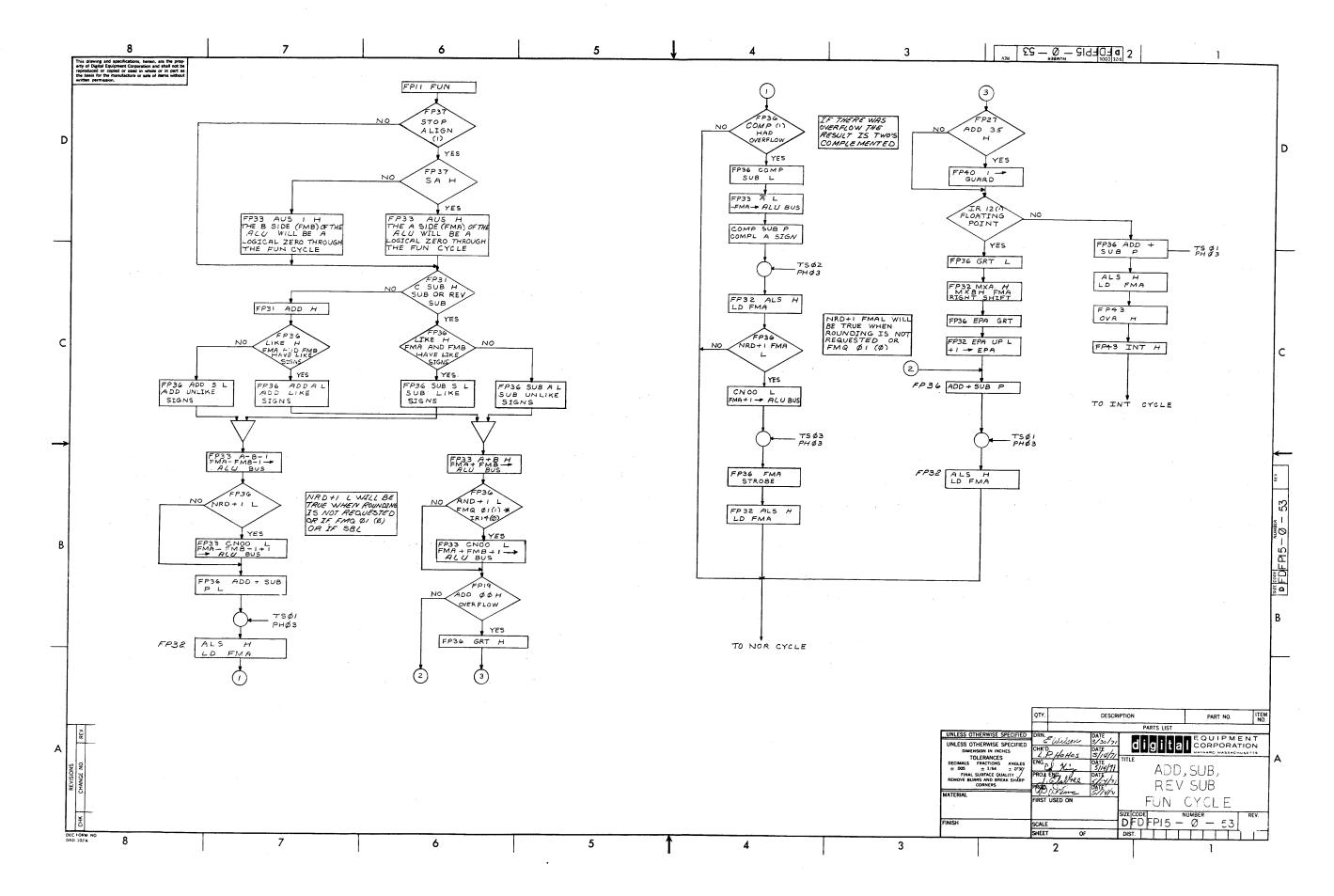

|     | D-FD-FP15-0 | ) <b>-</b> 53 | Add, Sub, Rev Sub, Sub Cycle  | 4-9  |

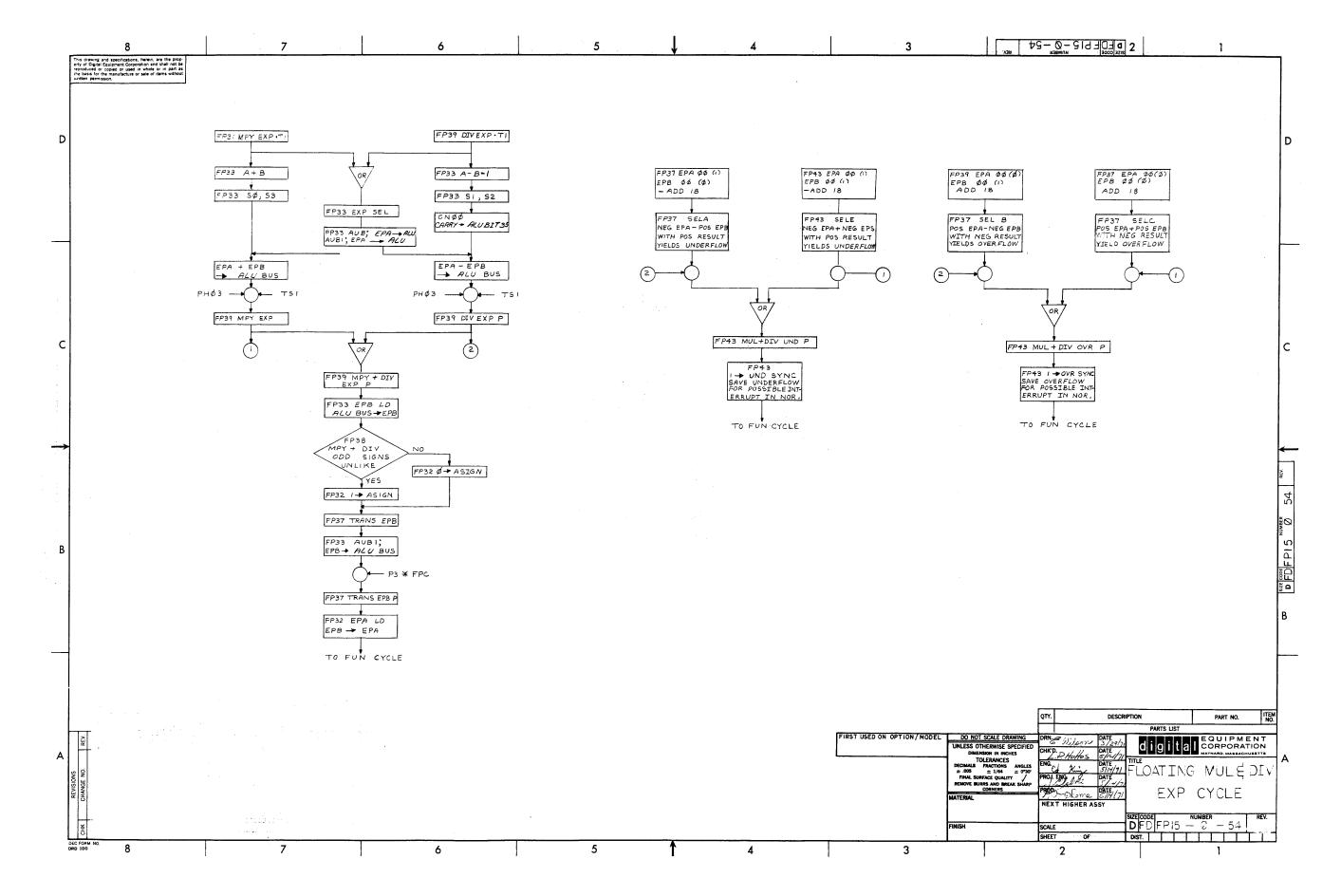

|     | D-FD-FP15-0 | )-54          | Floating Mul & Div Exp Cycle  | 4-17 |

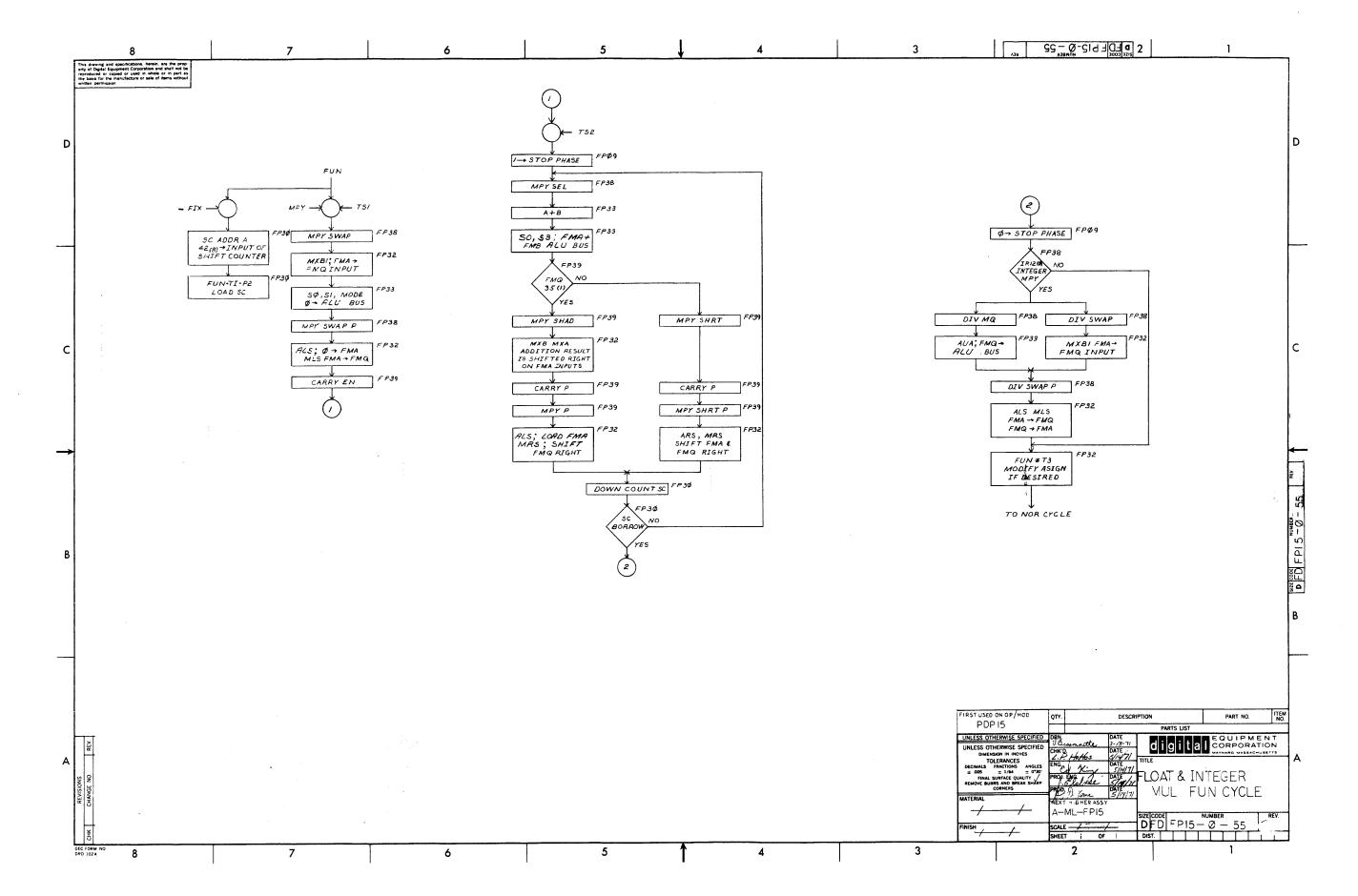

|     | D-FD-FP15-0 | ) <b>-</b> 55 | Float & Integer Mul Fun Cycle | 4-18 |

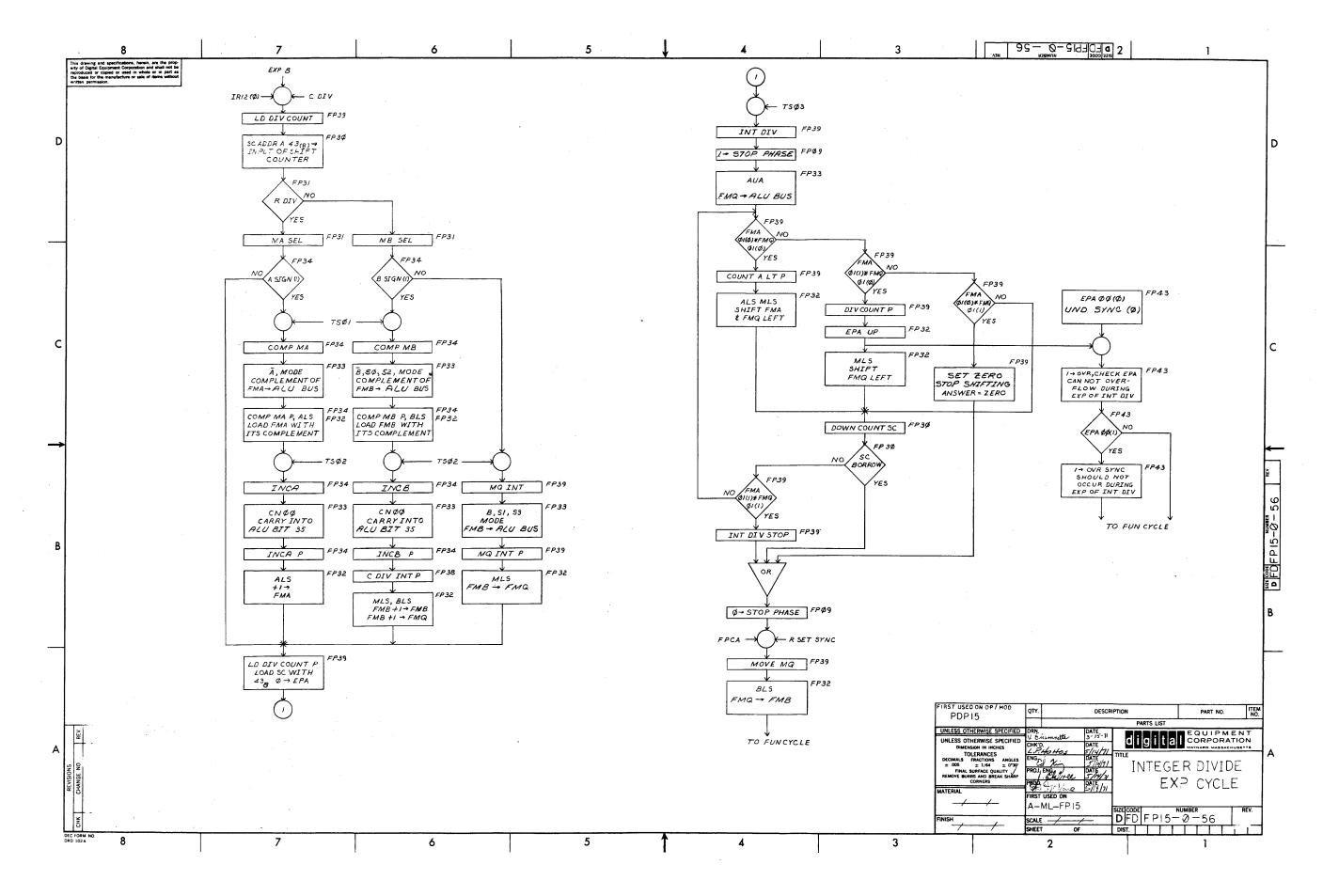

|     | D-FD-FP15-0 | )-56          | Integer Divide Exp Cycle      | 4-23 |

|     | D-FD-FP15-0 | )-57          | Float & Integer Div Fun Cycle | 4-24 |

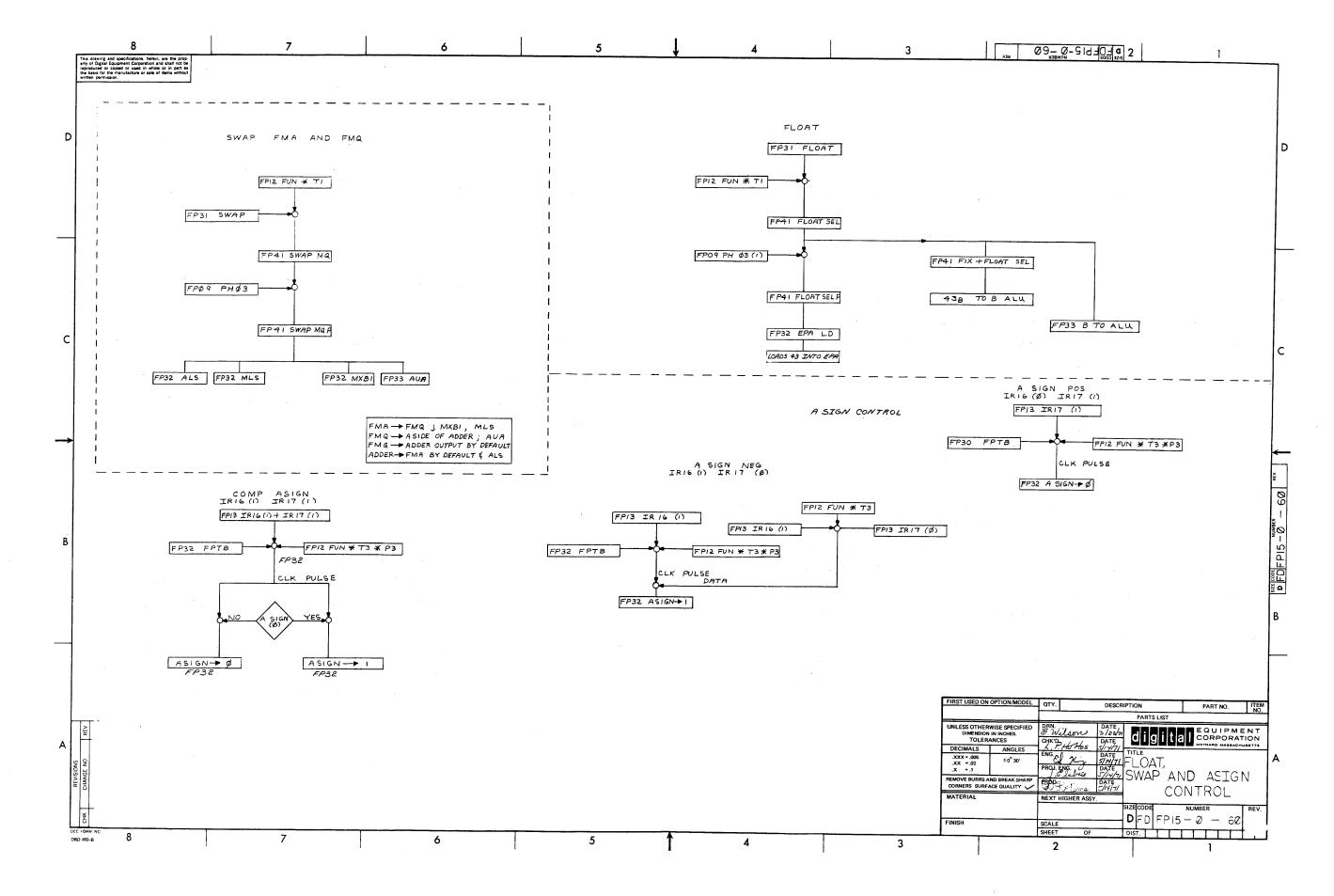

|     | D-FD-FP15-0 | <b>)-60</b>   | ASIGN Swap & Float Control    | 4-27 |

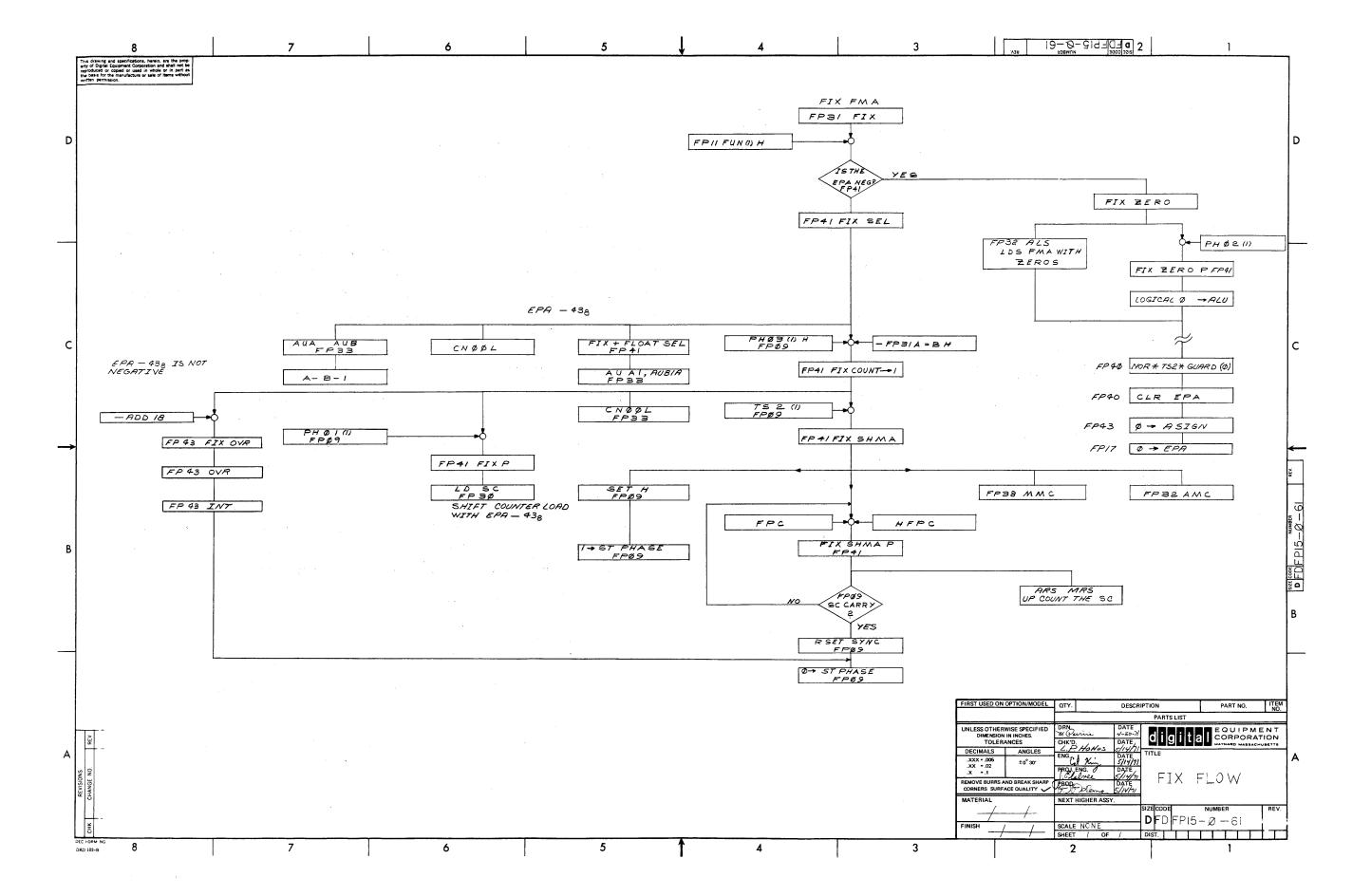

|     | D-FD-FP15-0 | -61           | Fix Flow                      | 4-29 |

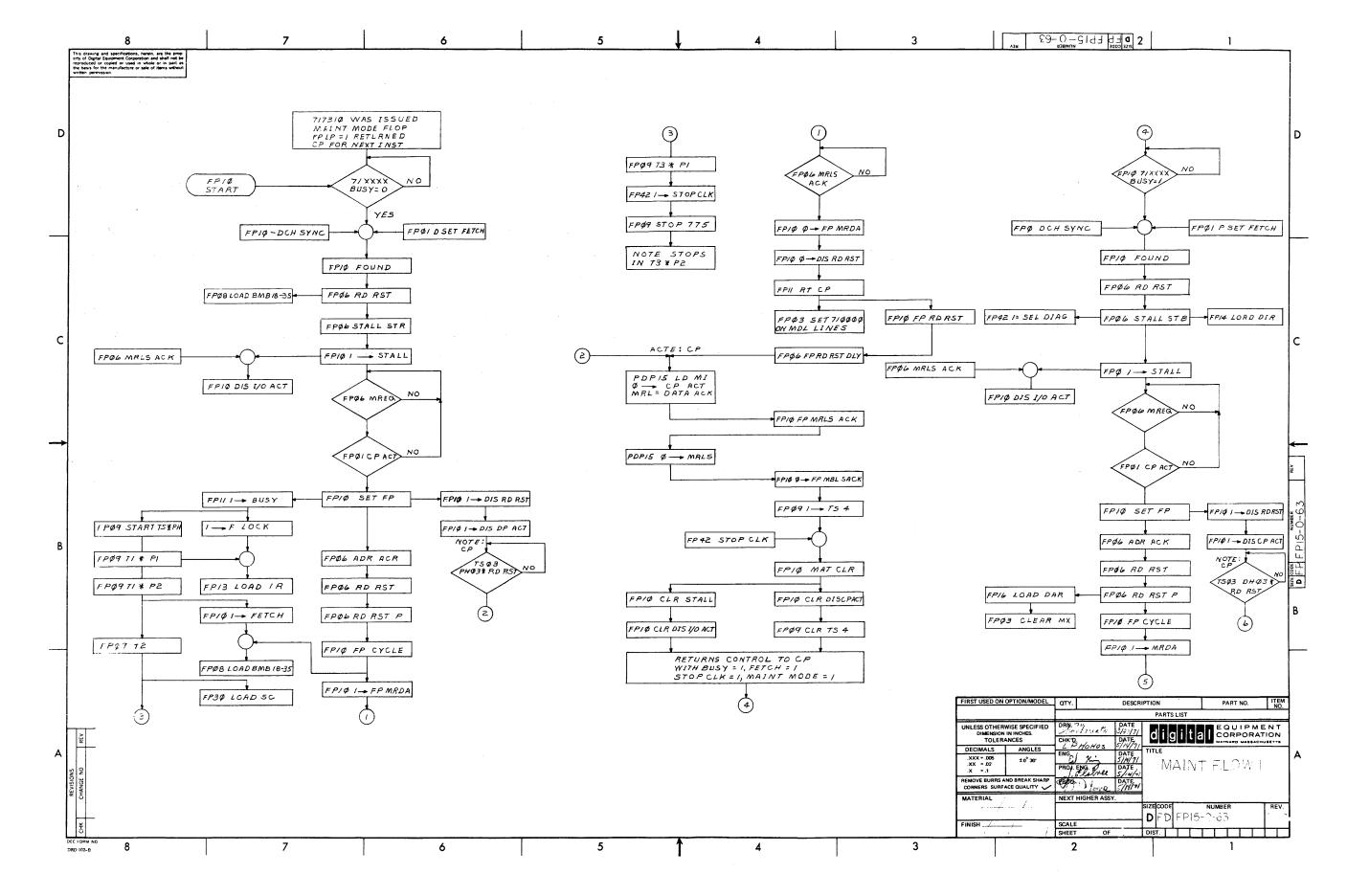

|     | D-FD-FP15-0 | -63           | Maint Flow 1                  | 4-32 |

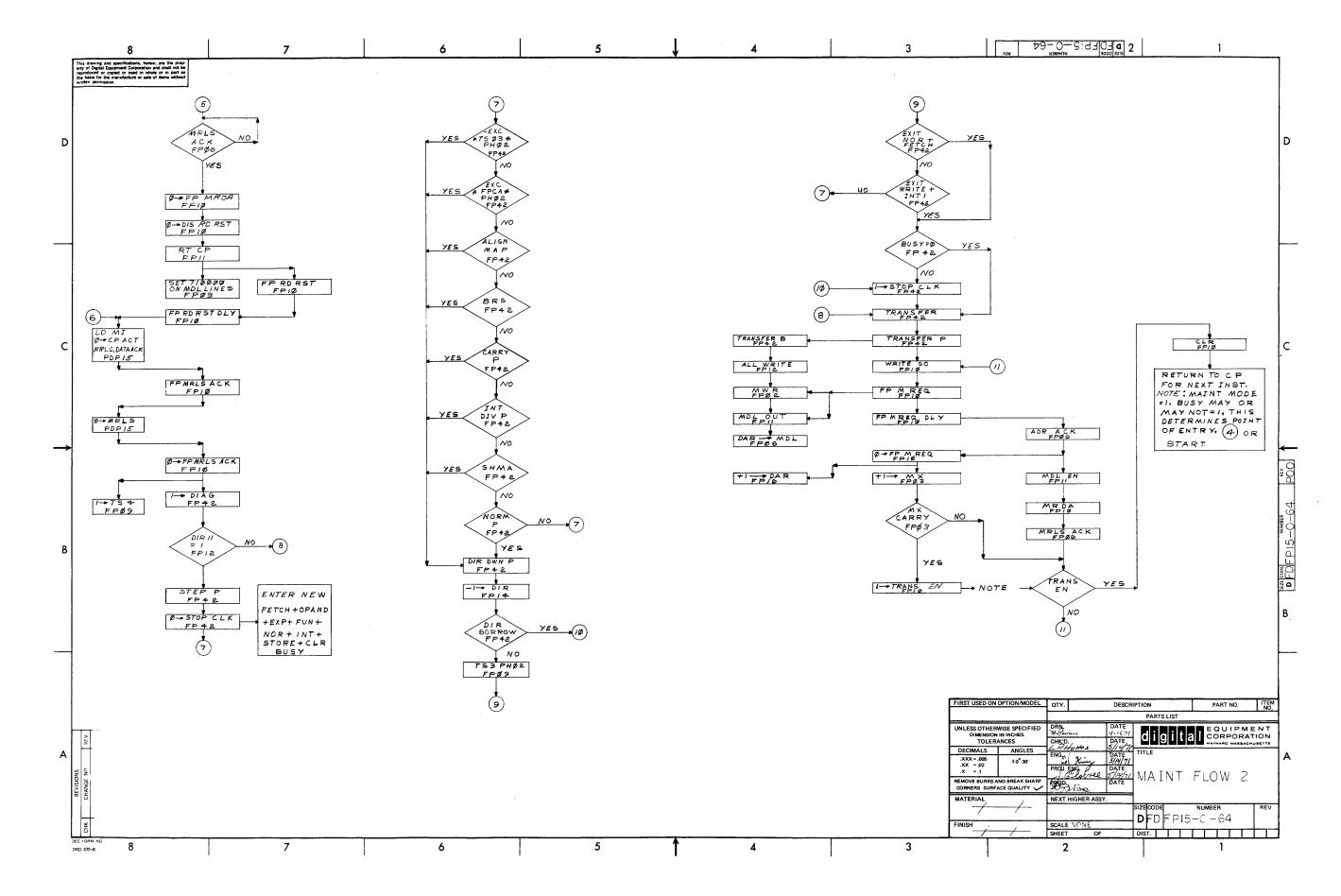

|     | D-FD-FP15-0 | -64           | Maint Flow 2                  | 4-33 |

| TAB | LES         |               |                               |      |

|     | Table No.   |               | Title                         | Page |

|     | 1-1         | FP15 Syst     | em Characteristics            | 1-1  |

|     | 1-2         | FP15 Syst     | em Features                   | 1-2  |

|     | 1-3         | Operand       | Transfer and Cycle Time       | 1-2  |

|     |             |               |                               |      |

Signal Cable Connections

FP15 Floating-Point Processor Major Components

FP15 Floating-Point Processor Engineering Drawings

5-1

5-2

5-3

5-1

5-2

# CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL

This chapter provides a physical and functional description of the FP15 Floating-Point Processor. The physical description includes lists of FP15 system parameters and special features.

# 1.2 FLOATING-POINT PROCESSOR PHYSICAL DESCRIPTION

The FP15 Floating-Point Processor consists of four racks of Medium Scale Integrated logic (MSI) and TTL logic located as shown in Figure 1-1. The interconnecting cabling associated with the FP15 is shown in Figure 1-2. The floating-point processor logic uses an operating voltage of +5 Vdc that is supplied from an H721 Power Supply, with 115V or 220V input and +5 Vdc output fused at 20A. A 716 Power Supply provides the power for the indicator panel. The operating characteristics of the FP15 are listed in Table 1-1; Table 1-2 includes some of the more significant features of the FP15.

Table 1-1 FP15 System Characteristics

| Operating Characteristics |                                                             |

|---------------------------|-------------------------------------------------------------|

| Power Requirements        | 115V, ±15%<br>12A<br>50 ± 1 Hz, 60 ± 1.2 Hz<br>Single Phase |

|                           | 230V, ±15%<br>6A<br>50 ± 1 Hz, 60 ± 1.2 Hz<br>Single Phase  |

| Power Consumption         | 1.4 kW max                                                  |

| Temperature Range         | 50° - 120°F                                                 |

| Relative Humidity         | 10 - 95%                                                    |

| Heat Dissipation          | 4800 btu/hr                                                 |

Table 1–1 (Cont)

FP15 System Characteristics

| Physical Characteristics |                            |

|--------------------------|----------------------------|

| Size                     | 19-in. wide by 21-in. high |

| Weight                   | 50 lb                      |

| No. of Racks             | 4                          |

| Type of Logic            | TTL and MSI                |

Figure 1-1 Cabinet Housing FP15 Logic

\*If BB option is not installed, cables are directly routed to memory

15-0579

Figure 1-2 System Interconnecting Cabling

### Table 1-2 FP15 System Features

- o Directly or indirectly addressable up to 128K of core.

- o Performs arithmetic operations on 18- or 36-bit integers and 36- or 54-bit floating-point numbers.

- o Allows execution of in-line code--CPU instructions and floating-point instructions may be interspersed as desired.

- o I/O Processor can access memory on a shared basis with the floating-point processor; however, the I/O Processor takes priority over the FP15.

- o When an undesired condition (Underflow, Overflow, Abnormal Division, or Memory Protect Violation) occurs, the FP15 interrupts the CP stored program and automatically identifies the source of the interrupt.

- o Worst-case multiplication and division times on normalized operands do not exceed  $24\,\mu s$ .

- o Possesses ability to convert floating-point numbers to integers and integers to floating-point numbers.

- o Remainder, product, and align bits in FMQ are accessible by appropriate software.

- o Unnormalized and unrounded arithmetic may be specified.

- o A class of non-memory reference instructions is available. These instructions use existing contents of FMA and FMB and require no memory reference.

- Built-in maintenance logic (maintenance mode) allows single or multiple substeps of an instruction. All major registers and control can be examined at the end of each step.

- Designed to operate with existing PDP-15 options (Memory Protect, Memory Relocate, etc.) with no increase in cycle time.

1-2

#### 1.3 FUNCTIONAL DESCRIPTION

The FP15 Floating-Point Processor functional block diagram is shown in Figure 1-3. Before describing each of the major elements in the diagram, it is necessary to introduce the various operating cycles in the FP15; they are:

- a. FETCH

- b. OPAND

- c. EXP

- d. FUN

- . NOR

- f. WRITE

- g. INTERRUPT

# 1.3.1 Operating Cycles

During a floating-point instruction, the FP15 is in one of the operating cycles. Each cycle is approximately 900 ns and is divided into three time states (300 ns per time state). The cycles can be extended in time due to shifting and aligning. In turn, each time state is subdivided into four phases (75 ns per phase). The following paragraphs provide a brief description of the major events that occur during each cycle.

FETCH - In the FETCH cycle the instruction word (first word) is loaded into the FP15 Instruction Register (IR) and the address of the operand is loaded into the FP15 Address Register (AR). If indirection (indirect addressing) is requested, the FP15 remains in the FETCH cycle to obtain the effective address.

OPAND - In the OPAND cycle the operand(s) is transferred from memory to the FP15. The number of operands transferred depends on the format in Table 1-3.

Table 1-3

Operand Transfer and Cycle Time

| Format                                                       | No. of Operands | Cycle Time |

|--------------------------------------------------------------|-----------------|------------|

| Single-precision integer                                     | One operand     | (1) 1.2 μs |

| Double-precision integer and Single-precision floating-point | Two operands    | (2) 2.4 μs |

| Double-precision floating-point                              | Three operands  | (3) 3.6 μs |

If non-memory reference instructions are specified, the OPAND cycle is bypassed and no operands are transferred from memory to the FP15.

Figure 1-3 FP15 Functional Block Diagram

EXP - In the EXP cycle, during floating-point addition and subtraction, the mantissa with the smaller exponent is aligned with the mantissa having the larger exponent. Alignment occurs by right-shifting the smaller mantissa.

In the EXP cycle, during floating-point multiplication and division, the exponent is calculated. In integer format, negative integers in 2's complement format are converted to sign and magnitude numbers during the EXP cycle.

FUN - In the FUN cycle, the actual arithmetic or logical operation is performed. The cycle time required is the basic 900 ns, plus the additional time required for shift, multiply, and divide operations.

NOR - In the NOR (normalize) cycle, the FMA is normalized by shifting. Rounding may also be requested. The basic NOR cycle requires 900 ns, plus an additional 150 ns for each shift necessary to normalize.

WRITE - During the WRITE cycle, the operands are transferred to memory. The operands transferred from the FP15 to memory are:

Single-precision integer--one 2's complement operand

Double-precision integer--two 2's complement operands

Single-precision floating-point--2's complement exponent and high-order mantissa

Double-precision floating-point--2's complement exponent and high-order and low-order mantissas.

Each transfer requires about 1.2 µs.

#### 1.3.2 Major Register Functional Descriptions

Buffered Memory Buffer Register (BMB) – The 36-bit Memory Buffer Register is loaded from the memory bus 18 bits at a time. The output of this register is connected to the ALU, the instruction register, and the address register. All inputs from the memory pass through the memory buffer.

Instruction Register (IR) - The 12-bit Instruction Register stores bits 6 through 17 of the instruction word retrieved from memory during the FETCH cycle. Bits 6 through 17 remain in the IR until another instruction is fetched from memory.

Address Register (AR) - The 17-bit Address Register stores the effective address used in fetching or storing operands.

Arithmetic Logic Unit (ALU) - The 36-bit ALU performs both arithmetic and logic operations in the FP15. The output of the ALU is connected to all major registers via the ALU bus. Most major registers are available as inputs to the ALU.

EPA - The 18-bit EPA is a synchronous up-down counter used to store the 2's complement exponent associated with the mantissa loaded in the FMA. The most significant bit of the EPA represents the sign of the exponent. For single-precision floating-point format, the most significant bit of the exponent is bit 9. The value of this bit is extended from bit 9 through bit 0. The EPA is loaded from the ALU bus and keeps track of the exponent associated with the mantissa in the FMA.

FMA – The 35-bit FMA stores an integer operand during integer arithmetic or a mantissa during floating-point arithmetic. The FMA is loaded from the ALU and can be shifted left or right. The FMA can also be loaded and shifted simultaneously from the ALU bus during multiplication and division. The EPA and A SIGN/FMA are the floating-point accumulator.

A SIGN - The 1-bit A SIGN register stores the sign of the operand loaded into the FMA. A 1 in this register indicates a negative number; a 0 indicates a positive number.

FMQ - The FMQ is a 36-bit extension of the FMA or FMB and is used primarily during arithmetic operations. Bits shifted out of the FMA or FMB, during alignment for addition and subtraction, are shifted into the FMQ. The most significant bit in the FMQ is used for rounding, if requested. The FMQ can be loaded from the ALU bus, or directly from the FMA, and has a shift-left and shift-right capability.

EPB – The 18-bit EPB register is loaded from the ALU bus and stores the 2's complement exponent associated with the mantissa loaded in the FMB. The most significant bit of the EPB represents the sign of the exponent. For single-precision floating-point format, the most significant bit of the exponent is bit 9. The value of this bit is extended from bit 9 through bit 0.

FMB - The 35-bit FMB register stores an integer operand during integer arithmetic or a mantissa during floating-point arithmetic. Unlike the FMA, the FMB can only be shifted right for alignment. The FMB is loaded directly from the ALU bus. The EPB and B SIGN/FMB are a second operand register.

B SIGN - The 1-bit B SIGN register stores the sign of the operand loaded into the FMB. A 1 in this register represents a negative mantissa; a 0 represents a positive mantissa.

Shift Counter - The shift counter performs the following functions:

- Keeps track of the number of words to be fetched from memory during the OPAND cycle.

- b. Keeps track of the number of words written into memory during the WRITE cycle.

- c. Keeps track of the number of shifts required for multiply and divide operations.

- d. Limits the number of shifts during normalizing to a maximum of  $35_{10}$ .

- e. Controls the number of shifts required during alignment.

- f. Checks for exponents having differences which exceed 35<sub>10</sub>.

JEA – The 15-bit JEA address register points to the interrupt handling routines in core that service the floating-point interrupts (underflow, overflow, abnormal divide, and FP memory trap). This register is loaded by software control.

Diagnostic Instruction Register (DIR) - The 7-bit DIR determines the number of steps through which an instruction is to be sequenced.

Diagnostic Address Register (DAR) - The 15-bit DAR specifies the address in core where the contents of the registers are to be stored.

# CHAPTER 2 MODULE DESCRIPTIONS

#### 2.1 GENERAL

This chapter provides descriptions of the following modules used in the FP15 Floating-Point Processor:

| M238  | SYNCHRONOUS UP/DOWN COUNTER        |

|-------|------------------------------------|

| M159  | ARITHMETIC LOGIC UNIT              |

| M191  | CARRY LOOK-AHEAD GENERATOR         |

| M248  | RIGHT-SHIFT PARALLEL LOAD REGISTER |

| M1701 | DATA SELECTOR                      |

| M1713 | 16-To-1 DATA SELECTOR              |

# 2.1.1 M238 Synchronous Up/Down Counter

The M238 Synchronous Up/Down Counter consists of two DEC 74193 4-bit synchronous up/down counters. Synchronous operation is provided by having all flip-flops in the counter clocked simultaneously so that the outputs change at the same time. The flip-flops are master-slave flip-flops and the outputs are triggered by a positive-going transition of one of two count (clock) inputs. One input is designated U (up count); the second input is designated D (down count). The direction of counting is determined by the count input that is pulsed while the other count input is high.

The outputs of the flip-flops may be preset to any desired state by entering the data at the data inputs while the load input (L) is low. The output will change to reflect the input, regardless of the count pulses.

A clear input (CLR) forces all outputs low on receipt of a high clear input. The clear input is independent of the count and load inputs.

Both borrow and carry outputs are available for cascading the up-counting and down-counting operations. When counter underflow occurs, the borrow output produces the same width pulse as the down-count input. When counter overflow occurs, the carry output produces the same width pulse as the count-up input. Cascading is accomplished by connecting the borrow and carry inputs to the count-down and count-up inputs, respectively, of the next counter.

The M238 Counter is used in the EPA, DIR, and DAR registers in the FP15 Floating-Point Processor. Figure 2-1 is an example of how the M238 Counter is used in the DIR register (see drawing D-BS-FP15-0-14).

#### NOTE

The up count is inhibited by +3V in the DIR register, indicating that this register can only be decremented.

Figure 2-1 M238 Synchronous Up/Down Counter

# 2.1.2 M159 Arithmetic Logic Unit

The M159 4-bit Arithmetic Logic Unit (ALU) contains a single DEC 74181 integrated circuit. Nine of these ALU modules are used in the FP15 Floating-Point Processor to perform 36-bit arithmetic and logic operations, as shown on drawings D-BS-FP15-0-19 through D-BS-FP15-0-27.

This integrated circuit performs 16, 4-bit arithmetic operations when the MODE control (MC) input is low and 16 logic functions when the MC input is high. The functions are selected by applying

combinations of function select inputs S0 through S3. For FP15 applications, the function select and MC inputs are generated by the ALU control logic shown on drawing D-BS-FP15-0-33.

Only two arithmetic operations, A plus B and A minus B minus 1, are selected in the FP15; five logic functions, A, -A, B, -B, and logical 0 are performed in the FP15. The combined ALU truth table for FP15 arithmetic operations and logic functions is listed as follows:

| *            | Function Select Inputs |    |     | outs | 0.1.5                                    |  |

|--------------|------------------------|----|-----|------|------------------------------------------|--|

| Mode Control | \$3                    | S2 | S1  | S0   | Output Function                          |  |

|              |                        |    |     |      |                                          |  |

| 0            | 1                      | 0  | 0   | 1    | A plus B (arithmetic operation)          |  |

| 0            | 0                      | 1  | 1   | 0    | A minus B minus 1 (arithmetic operation) |  |

| 0            | 0                      | 0  | 0   | 0    | A (logic function)                       |  |

| 1            | 0                      | 0  | 0   | 0    | -A (logic function)                      |  |

| 1            | 1                      | 0  | 1   | 0    | B (logic function)                       |  |

| 1            | 0                      | 1  | 0   | 1    | -B (logic function)                      |  |

| 1            | 0                      | 0  | ] 1 | 1    | Logical 0 (logic function)               |  |

|              |                        |    |     |      |                                          |  |

In addition, a comparator output, A=B, is provided when the four A inputs are equal to the four B inputs if the function A=B=1 is selected. A full-carry look-ahead provides fast, simultaneous carry generation by the M191 module.

Figure 2-2 shows the ALU configuration for bits 00 through 03 in the FP15 Floating-Point Processor.

#### 2.1.3 M191 Carry Look-Ahead Generator

The M191 Carry Look-Ahead Generator, consisting of two DEC 74182 integrated circuits, is a high-speed generator capable of anticipating a carry through a group of ALUs. A 13-ns delay occurs for each look-ahead level. The M191, when used in conjunction with the M159 ALU, provides carry, generate-carry, and propagate-carry functions for 36-bit words.

Figures 2-3 and 2-4 show how the M191 is used.

Each carry look-ahead circuit is associated with four ALUs (16 bits). Each circuit generates the anticipated carry through its respective group of ALUs, as well as providing a Generate (G) and Propagate (P) input to a third carry look-ahead circuit associated with the last ALU; hence, the term full-carry look-ahead in three levels (36 bits).

Depending on the selected function of the ALUs, the carry look-ahead circuitry determines whether a carry will be propagated through the particular ALU, or whether the selected function will generate a

Figure 2-2 M159 Arithmetic Logic Unit

Figure 2-3 M191 Carry Look-Ahead Generator

Figure 2-4 36-Bit ALU, Full-Carry Look-Ahead in Three Levels

carry. If a carry is produced, it is directed into the next ALU in line. This sequence is continued for each of the four ALUs in the section. The carry look-ahead circuitry then "looks" at the G and P signals of all four ALUs and determines whether a carry should be inserted into the next four ALUs and into the third level of carry look-ahead. This process is continued for the second section of ALUs (next 16 bits). Finally, the third level of carry look-ahead determines whether a carry should be inserted into the final ALU by examining the resulting G and P inputs of the other two look-ahead circuits.

The truth table for the first-stage carry is as follows:

| True | Carry | Insert | = L |

|------|-------|--------|-----|

|------|-------|--------|-----|

| P00              | G00         | C <sub>N00</sub> | c <sub>N+X</sub> |

|------------------|-------------|------------------|------------------|

| L<br>L<br>H<br>M | L<br>L<br>H | L<br>H<br>H<br>L | H<br>H<br>L<br>L |

True Carry Insert = Low

| POO                   | G00                        | C <sub>N00</sub>           | c <sub>N+X</sub>      |

|-----------------------|----------------------------|----------------------------|-----------------------|

| L<br>H<br>L<br>H<br>L | L<br>H<br>H<br>L<br>L<br>H | L<br>L<br>L<br>H<br>H<br>H | H<br>H<br>L<br>H<br>H |

The following are the logic equations for a carry look-ahead stage:

$$\overline{C_{N01}} = \overline{C_{N00}} * \overline{G_0} + \overline{G_0} * \overline{P_0}$$

$$\overline{C_{N02}} = \overline{G_1} * \overline{P_1} + \overline{P_0} * \overline{G_0} * \overline{G_1} + \overline{G_1} * \overline{G_0} * \overline{C_N}$$

$$\overline{C_{N03}} = \overline{P_2} * \overline{G_2} + \overline{G_1} * \overline{G_2} * \overline{P_1} + \overline{G_0} + \overline{G_1} * \overline{G_2} * \overline{P_0} + \overline{G_0} * \overline{G_1} * \overline{G_2} * \overline{C_N}$$

$$\overline{GG00} = \overline{P_3} * \overline{G_3} + \overline{P_2} * \overline{G_3} * \overline{G_2} + \overline{P_1} * \overline{G_3} * \overline{G_2} * \overline{G_1} + \overline{G_3} * \overline{G_2} * \overline{G_1} * \overline{G_0}$$

$$\overline{PP00} = \overline{P_3} + \overline{P_2} + \overline{P_1} + \overline{P_0}$$

where

$$\overline{C_{NXX}}$$

= True L

$\overline{GXX}$  = True H

$\overline{PXX}$  = True H

$\overline{GGXX}$  = True H

$\overline{PPXX}$  = True H

# 2.1.4 M248 Right-Shift Parallel Load Register

The M248 Right-Shift Parallel Load Register consists of two 4-bit DEC 7495 Right-Shift Parallel Load Registers connected to allow right-shifting between 4-bit sections. The registers perform load or right-shift operations, depending on the logical input to the MC. When a logical 0 is applied to the MC input, the output of each flip-flop is connected to the succeeding flip-flop and right-shift operation is performed by clocking at the input designated RS. During this time, the input designated LS is inhibited. When a logical 1 is applied to the MC input, the flip-flops are decoupled (to prevent right-shift); the register is loaded with parallel inputs when the input designated LS is clocked. The register can be configured for left-shift operation by connecting the output of each flip-flop to the parallel input of the previous flip-flop.

The M248 Right-Shift Parallel Load Register is used in the EPB, FMA, FMB, and FMQ registers in the FP15 Floating-Point Processor. Each module is capable of handling 8 bits. Figure 2-5 shows a sample of the application of this module in the FP15 Floating-Point Processor.

Figure 2-5 M248 Right-Shift Parallel Load Register

# 2.1.5 M1701 Data Selector

The M1701 Data Selector contains two DEC 74153 Dual 4-Line-to-1-Line Data Selector/Multiplexer integrated circuits. These integrated circuit modules comprise input multiplexers A and B of the

36-bit ALU in the FP15 Floating-Point Processor. They are also used as input multiplexers to the shift counter, MPO, FMA, and FMQ registers. A complete block schematic of the input multiplexers is shown on drawings D-BS-FP15-0-19 through D-BS-FP15-0-27.

For each section of each IC, one of four data inputs is selected by combinations of address input signals A and B. The selected data input is strobed to the output by a low strobe signal. Refer to the following truth table for a typical input multiplexer A section.

| Addres | ess Inputs Data Inputs |   | Address Inputs |   | Strobe | Output |        |

|--------|------------------------|---|----------------|---|--------|--------|--------|

| Α      | В                      | 0 | 1              | 2 | 3      | этгоре | Output |

| ×      | ×                      | × | ×              | × | ×      | 1      | 0      |

| ô      | Ô                      | Ô | ×              | × | ×      | 0      | 0      |

| Ö      | Ö                      | 1 | ×              | × | ×      | 0      | 1      |

| ì      | 0                      | × | 0              | × | ×      | 0      | 0      |

| 1      | 0                      | × | 1              | × | ×      | 0      | 1      |

| 0      | 1                      | × | ×              | 0 | ×      | 0      | 0      |

| Ö      | 1                      | × | ×              | 1 | ×      | 0      | - 1    |

| Ĭ      | li                     | × | ×              | × | 0      | 0      | 0      |

| i      | 1                      | × | ×              | × | 1      | 0      | 1      |

Address input signals A and B are common to both sections of each IC. Figure 2-6 is a typical application of the M1701 Data Selector in the FP15 Floating-Point Processor.

Figure 2-6 M1701 Data Selector

2-4

### 2.1.6 M1713 16-To-1 Data Selector

The M1713 16-To-1 Data Selector contains a single DEC 74150 integrated circuit. It is used in the output multiplexer section of the FP15 Floating-Point Processor, where up to 16 major register outputs are selected for transfer to the common MPO bus. The block schematic of the output multiplexer is shown on drawing D-BS-FP15-0-03.

Data inputs are selected by combinations of data select signals MXA, MXB, MXC, and MXD, which are generated by the multiplexer control logic shown on drawing D-BS-FP15-0-05. The strobe inputs are wired to ground so that each IC is always enabled. A typical truth table for the 16-to-1 Data Selector follows:

| Data Select Inputs |     |     |     | Data Input* |  |

|--------------------|-----|-----|-----|-------------|--|

| (D                 | MXC | MXB | MXA | Selected    |  |

|                    | 0   | 0   | 0   | DIR12       |  |

|                    | Ö   | o l | 1   | JEA12       |  |

| , l                | Ō   | 1   | 0   | ADD30       |  |

|                    | 0   | 1   | 1   | ADD12       |  |

| )                  | ì   | 0   | 0   | FMQ30       |  |

| )                  | ì   | 0   | 1   | FMQ12       |  |

| )                  | 1   | 1   | 0   | FMB30       |  |

| )                  | 1   | 1   | 1   | FMB12       |  |

|                    | 0   | 0   | 0   | EPB12       |  |

|                    | 0   | 0   | 1   | FMA30       |  |

|                    | 0   | 1   | 0   | FMA12       |  |

|                    | 0   | 1   | 1   | EPA12       |  |

|                    | l   | 0   | 0   | IR12        |  |

|                    | 1   | 0   | 1   | BMB30       |  |

|                    | 1   | 1   | . 0 | BMB12       |  |

|                    | 1   | 1 1 | 1   | MPI12       |  |

<sup>\*</sup> Signal mnemonics vary as shown on drawing D-BS-FP15-0-03.

Figure 2-7 is a typical example of the manner in which the M1713 Data Selector is utilized.

Figure 2-7 M1713 16-To-1 Data Selector

# CHAPTER 3 FP15/PDP-15 INTERFACE

#### 3.1 INTRODUCTION

This chapter describes the interface between the CPU, FP15, and memory. This interface is described by discussing the major events that occur during the FETCH, OPAND, WRITE, and Interrupt (INT) cycles, followed by a flow diagram description of each cycle. The EXP, FUN, and NOR cycles, internal to the FP15, are described in Chapter 4. Figure 3–1 shows the various control signals associated with the interface.

Figure 3-1 Major Signal Interface Diagram

# 3.2 FETCH CYCLE INTERFACE

Prior to the FETCH cycle, the floating-point instruction from memory is strobed into the FP15 BMB. During the FETCH cycle, the operand address is strobed into the FP15 Address Register (AR) (see Figure 3-2). If indirection is specified, a second FETCH cycle is performed to obtain the effective address.

Every instruction is monitored by both the CPU and the FP15, which are in parallel on the memory bus. Bits 00 through 05 of the instruction are examined for an octal code of 71. The 71 is recognized by the CPU as a NOP and by the FP15 as a floating-point instruction. The CPU strobes the instruction into the memory input (MI) register and then into the instruction register (IR), while the FP15 strobes the instruction into the BMB register.

The CPU executes the 71XXXX<sub>8</sub> (NOP) and makes a second memory reference to the next location, as if it were fetching the next instruction. This memory request (M REQ) actually fetches the operand address that is the second half of the two-word FP15 instruction. The normal interface signals between the CPU and memory take place; i.e., the CPU specifies an address, READ cycle, and issues M REQ. After M REQ is placed on the memory bus, the contents of the BMB in the FP15 are strobed into the IR; the DIS CP ACT and DIS CP RD RST signals are generated to inhibit the CPU from making further memory requests. Address Acknowledge (ADDR ACK) is returned from memory to clear M REQ in the CPU. The memory then places the operand address on the memory data line (MDL) and issues RD RST. The operand address is strobed into the BMB in the FP15.

The CPU does not see the operand address because DIS CP RD RST prevents RD RST from loading the MI and halts the CPU in Time State 3, Phase 3 (TS03\*PH03).

| SUBCYCLE                      | CENTRAL PROCESSOR                                                                   | FLOATING POINT UNIT                                                                                     | MEMORY                                                                                | REMARKS                                                                                                                                                                                                                                                             |

|-------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | M REQ, ADDR, RD—————————————————————————————————                                    |                                                                                                         | ADDR ACK  0 + ADDR ACK INSTR ON MDL AND RD RST ISSUED                                 | CPU REQUESTS MEM. CYCLE MEM. ACKNOWLEDGES ADDRESS CPU REMOVES ADDR FROM MDL MEM PLACES INSTR. ON MDL                                                                                                                                                                |

| FLOATING POINT<br>INSTRUCTION | 71XXXX <sub>8</sub> + MI MRLS  0 + MRLS  71XXXX <sub>8</sub> + IR (EXECUTED AS NOP) | 71XXXX <sub>8</sub> → BMB                                                                               | MRLS ACK  O → MRLS ACK                                                                | 71XXXX <sub>8</sub> RECOGNIZED AS FLOATING POINT INSTR. AND IS STROBED IN BMB OF FPU AND MI OF CPU. CPU COMPLETES REST OF MEM CYCLE. 71XXXX <sub>8</sub> STROBED INTO IR IN CPU                                                                                     |

| OPERAND ADDRESS               | M REQ—  0 → M REQ                                                                   | DIS CP ACT, DIS RD RST  BMB + IR  MDL + BMB FP MRDA  0 + FP MRDA  BMB + AR                              | ADDR ACK  O - ADDR ACK  OPERAND ADDR ON  MDL & RD RST  ISSUED  MRLS ACK  O - MRLS ACK | M REQ IS MADE FOR LOCATION CONTAINING OPERAND ADDR. CPU RD RST IS DISABLED, WHICH INHIBITS RD RST FROM RESTARTING CPU CLOCK.  OPERAND ADDR STROBED INTO BMB. 71XXXX <sub>8</sub> STROBED INTO IR IN FPU. REST OF MEM CYCLE COMPLETED.  OPERAND ADDR STROBED INTO AR |

| DUMMY SETUP                   | 710000 <sub>8</sub> + MI - MRLS - O + MRLS                                          | REMOVE DIS CP RD RST FPU ISSUES FP RD RST WITH 710000 <sub>8</sub> ON MDL  FP MRLS ACK  O - FP MRLS ACK |                                                                                       | CPU BECOMES ACTIVE FP RD RST LOOKS LIKE RD RST TO CPU. CPU STROBES 710000 <sub>8</sub> INTO MI. THE EXECUTION OF THE 710000 INSTRUCTION WAITING FOR CPU ACTIVE TO SET (WAITING TO ISSUE M REQ)                                                                      |

Figure 3-2 Memory Interface--FETCH Cycle

The FP15 now issues MRDA (Memory Release and Data Acknowledge) which releases the memory for additional requests and acknowledges receipt of the data (operanda ddress). The memory cycle is completed when the memory issues MRLS ACK, clears MRDA in the FP15 which, in tum, clears MRLS ACK (Memory Release Acknowledge). The operand address, which was loaded into the BMB, is now strobed into the FP15 AR. Since the CPU did not receive the operand address, it is still waiting for data from memory. The FP15 places a 710000<sub>8</sub> on the MDL, clears DIS RD RST, and sends RD RST to the CPU. The CPU loads the 710000<sub>8</sub> into the MI and generates MRLS. The FP15 generates MRLS ACK to allow the CPU to complete its cycle.

The CPU executes the 710000<sub>8</sub> but is prevented from making a M REQ because of DIS CP ACT. The CPU waits in TS03\*PH02 until completion of the FP15 instruction. The memory interface is now free for I/O memory requests.

#### 3.3 FETCH (INDIRECT) CYCLE INTERFACE

If bit 00 of the second FP15 word (address) is a 1, specifying indirection, a second FETCH (indirect) cycle is performed. This word, which is in the FP15 AR, and is the address of the effective address, is placed on the MDL (see Figure 3-3). The FP15 requests a memory cycle and the contents of the operand address (effective address) are accessed from memory, placed on the MDL, and RD RST issued. The address is then strobed into the BMB register. The FP15 issues FP MRDA to memory, which releases memory for further requests. The effective address, which was transferred into the BMB, is now strobed into the AR and represents the address of the first operand.

If bit 00 of the second FP15 word (address) is a 0, no indirection is specified and this cycle is omitted.

| SUB-<br>CYCLE     | CENTRAL<br>PROCESSOR | FLOATING-POINT UNIT                                       | MEMORY                                                                         | REMARKS                                                                                                                                       |

|-------------------|----------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| EFFECTIVE ADDRESS |                      | O - M REQ<br>REMOVE ADDR FROM MDL<br>MDL - BMB<br>FP MRDA | ADDR ACK  O + ADDR ACK  ADDR ON MDL AND  RD RST ISSUED  MRLS ACK  O + MRLS ACK | THIS IS THE INDIRECT CYCLE AND THE INDIRECT ADDRESS IS STROBED INTO AR.  OPERAND ADDR PLACED ON MDL AT RD RST. REST OF MEMORY CYCLE COMPLETED |

| If bit 0          | 0 of second w        | ord is 0 (Direct Addressing) o                            | omit indirect cycle.                                                           |                                                                                                                                               |

Figure 3-3 Memory Interface--FETCH Cycle (Indirect)

#### 3.4 FETCH CYCLE DESCRIPTION

The FP15 detects a floating-point instruction by monitoring MDL bits 00 through 05 for a 71XXXX<sub>8</sub> while FP SET FETCH is true (see drawings D-FD-FP15-0-45 through D-FD-FP15-0-47). FP SET FETCH indicates that the CPU is fetching an instruction. When the 71XXXX<sub>8</sub> is detected, the contents of the MDLs are strobed into the FP15 BMB bits 18 through 35 and the floating-point operation is started. The PI and API facilities are disabled at this point, to prevent an interrupt during the floating-point instruction.

The CPU executes the 71XXXX<sub>8</sub> as a NOP and makes a memory request for the next instruction that is actually the operand address associated with the floating-point instruction. The FP15 sets BUSY, DIS CP ACT, DIS RD RST, and loads the contents of BMB bits 18 through 35, which contain the floating-point instruction, into its IR. BUSY starts the floating-point phases and time states and DIS RD RST prevents the CPU from seeing the RD RST of the memory request for the operand address. The CPU waits in TS03\*PH03 for RD RST. When RD RST is returned by memory, the FP15 strobes the contents of the MDL into BMB bits 18 through 35 and issues MRDA to memory. The memory responds by issuing MRLS ACK which clears MRDA. The FP15 now completes the CPU memory request by clearing DIS RD RST, enabling 710000<sub>8</sub> (NOP) onto the MDL, and issuing FP RD RST, which strobes the NOP into the CPU's MI. The CPU responds with MRLS and the FP15 returns MRLS ACK. The CPU begins to execute the NOP but cannot issue a M REQ because DIS CP ACT holds the CPU in TS03\*PH02, thus allowing I/O memory requests to be made.

The FP15 loads BMB bits 18 through 35 (operand address) into the AR and determines if an I/O memory request is pending. If one is pending, the FP15 waits; if not, the FP15 determines if indirection has been requested. When indirection has not been requested, the FP15 enters the OPAND cycle, if an operand FETCH is requested, or the EXP cycle, if no operand FETCH is requested.

If indirection has been requested, the FP15 places the contents of the AR onto the MDL and issues M REQ. When RD RST is received from the memory, the contents of the MDL are strobed into BMB bits 18 through 35 and then loaded into the AR. The FP15 then enters OPAND or EXP, as described above.

Two other operations are also performed in the FETCH cycle. If the instruction is ADD, SUBTRACT, or FIX, the FMQ is cleared during TS03 of the FETCH cycle. If the instruction is a Reverse Divide, the FMA is loaded into the FMQ; if the instruction is a Reverse Subtract, the FMA is loaded into the FMB during TS02.

#### 3.5 OPAND CYCLE INTERFACE

After the FETCH cycle, the FP15 enters the OPAND cycle. If an instruction is specified in which operands are not fetched from memory (bit 10 of the floating-point instruction word on a 1), the OPAND cycle is omitted completely and no memory reference is made. The current contents of the FMA are used as the operand.

For memory reference instructions, the operand or operands from memory are transferred to the FP15 during the OPAND cycle. The number of operands is dependent on the format specified and is defined in the note associated with the OPAND cycle in Figure 3–4. This description assumes double—precision floating—point format in which the maximum number of operands (three) is transferred from memory. The first operand transferred is the exponent. The FP15 requests a memory cycle (M REQ) and transfers the effective address in the AR to memory via the MDL. Memory then places the first operand (the contents of the address specified) on the MDL and issues RD RST. The FP15 strobes the operand into the BMB and releases memory.

The next operand (high-order mantissa) to be obtained is in the next sequential location (exponent address plus one). As a result, the address in the AR is incremented so that the next memory access will transfer the second operand. The memory cycle is exactly like that described for the exponent operand.

The third operand (low-order mantissa) is in the next sequential location (high-order mantissa plus one). The address in the AR is incremented a second time to obtain the third operand address. The memory cycle is like that described for the exponent operand.

If bit 10 of first word (71XXXXg) is set, the OPAND cycle is omitted completely. If the bit is 00, the OPAND cycle is performed. However, certain operations in the OPAND cycle are excluded based on the following format:

Double-Precision Floating Point - All Operations Performed Single-Precision Floating Point - Omit Low-Order Mantissa

Double-Precision Integer - Omit Exponent

Single-Precision Integer - Omit Exponent and Low-Order Mantissa

| SUBCYCLE            | CENTRAL PROCESSOR | FLOATING-POINT UNIT                                                                                        | MEMORY                                                                                          | REMARK S                                                                                                                                                                                                        |

|---------------------|-------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXPONENT            |                   | AR - MDL M REQ, MRD 0 - M REQ REMOVE ADDRESS FROM MDL  MDL - BMB FP MRDA 0 - FP MRDA BMB - EPA AR + 1 - AR | ADDR ACK  0 - ADDR ACK EXPONENT ON MDL AND RD RST ISSUED MRLS ACK  0 - MRLS ACK                 | FPU REQUESTS MEMORY CYCLE WITH CONTENTS OF AR ON MDL.  FPU REMOVES ADDRESS FROM MDL. FPU WAITS FOR EXPONENT EXPONENT TRANSFERRED TO FPU AND STROBED INTO BMB. MEMORY CYCLE COMPLETED  ADDR REGISTER INCREMENTED |

| HIGH-ORDER MANTISSA |                   | AR - MDL M REQ, MRD, &  0 - M REQ REMOVE ADDR FROM MDL  MDL - BMB FP MRDA  0 - FP MRDA AR + 1 - AR         | O - ADDR ACK  O - ADDR ACK HIGH ORDER MAN- TISSA ON MDL & RD RST ISSUED  MRLS ACK  O - MRLS ACK | FP REQUESTS MEMORY CYCLE WITH INCREMENTED OPERAND ADDRESS  HIGH-ORDER MANTISSA STROBED INTO FPU MEMORY BUFFER  MEMORY CYCLE COMPLETED                                                                           |

|                     |                   | AR + MDL M REQ, MRD & O + M REQ  REMOVE ADDR FROM MDL                                                      | ADDR ACK                                                                                        | FP REQUESTS MEMORY CYCLE WITH TWICE INCREMENTED OPERAND ADDRESS                                                                                                                                                 |

| LOW-ORDER MANTISSA  |                   | MDL + BMB ← FP MRDA  0 + FP MRDA  BMB + FMA 00-35  AR + 1 + AR                                             | LOW ORDER MANTISSA ON MDL & RD RST ISSUED  MRLS ACK  0 - MRLS ACK                               | LOW-ORDER MANTISSA STROBED INTO FP MEMORY BUFFER MEMORY CYCLE COMPLETED CONTENTS OF BMB 00-35 STROBED INTO FMA                                                                                                  |

Figure 3-4 Memory Interface--OPAND Cycle

#### 3.6 OPAND CYCLE DESCRIPTION

During the OPAND cycle, the FMB and/or EPB is loaded from memory if the instruction specified is an arithmetic instruction (Add, Subtract, Multiply, or Divide). For other types of instructions (including Reverse Subtract and Reverse Divide), the FMA and/or EPA is loaded. For integer format, the EPA is not loaded.

Drawings D-FD-FP15-0-48 through D-FD-FP15-0-50 are flow diagrams of the OPAND cycle. The cycle is initiated when OPAND goes to 1. At TS02\*PH01 of this cycle, an FP M REQ is issued.

Since a WRITE operation is inhibited (-ALL WRITE), a memory read will occur. The address of the operand, located in the AR, is gated onto the MDL via the output multiplexer (MPO). FP M REQ, after a delay to allow the MDL to settle, produces M REQ to initiate the memory cycle.

When memory receives the address, it issues ADDR ACK, which clears FP M REQ. The data (operand) and RD RST are then placed on the MDL by the memory. Before strobing the data into its memory buffer, the FP15 waits for FP CYCLE. This signal is delayed by RD RST DLY to allow time for the data to settle before it is strobed. When the data is strobed into the buffer, the FP15 issues FP MRDA and the memory responds with MRLS ACK, which clears FP MRDA to complete the memory cycle.

The data format must now be determined. For each format, the shift counter is loaded with one less than the number of operands to be transferred to the FP15, so that the shift counter will detect a borrow rather than a 0 condition. For example, in double-precision integer format the shift counter is loaded with 1. Transferring the first word to memory decrements the counter to 0; transferring the second word decrements the counter to produce a borrow indicating completion of the transfers.

#### 3.6.1 Double-Precision Floating-Point Format

3-8

If double-precision, floating-point format is specified (IR 11 = 1, IR 12 = 1), the shift counter is loaded, during the FETCH cycle, with a count of 2 (SC 16 = 1, SC 17 = 0). A signal designated -STROBE loads the low-order bits (BMB bits 18-35) of the memory buffer with the operand. The A side of the ALU is selected. If the instruction is a Fix, Load, Float, Reverse Subtract, or Reverse Divide, an MA SEL signal is generated that causes the EPA to be loaded. If an arithmetic instruction is specified (Add, Subtract, Multiply, or Divide) MA SEL is not generated and the EPB is loaded.

The shift counter is decremented and, if no borrow is generated, the second memory reference of the OPAND cycle is initiated.

The second memory reference is similar to the first. The address in the AR has been incremented to access the next sequential memory location (high-order mantissa). The shift counter is now at a count of 1 (SC 16 = 0, SC 17 = 1). The STROBE signal loads the high-order bits of the memory buffer (BMB bits 00-17) with the second operand.

The shift counter is decremented a second time to a count of 0. The third memory reference is similar to the second except that the address is again incremented to fetch the third operand (low-order mantissa). The -STROBE signal loads the low-order mantissa into the low-order bits of the BMB. If the instruction is an arithmetic type, the B SIGN/FMB is loaded. If the instruction is a Fix, Load, Float, Reverse Subtract, or Reverse Divide, the A SIGN/FMA is loaded. The A multiplexer is again selected after the fetch of the third operand so that the A SIGN/FMA or B SIGN/FMB can be loaded as a 36-bit word from the 36-bit memory buffer.

The shift counter is decremented and now produces a borrow which indicates that all operands have been received. At this point, the OPAND cycle is cleared and the EXP cycle is enabled.

#### 3.6.2 Single-Precision Floating-Point Format

In single-precision floating-point format (IR 11 = 0, IR 12 = 1), the shift counter is loaded in the FETCH cycle with a count of 1 (SC 16 = 0, SC 17 = 1). A memory reference is made just as for double-precision floating point and the exponent operand is strobed into the low-order bits of the BMB, as a result of -STROBE. The B side of the ALU is selected for the first word of single-precision floating-point format. The first word consists of nine bits of exponent and nine bits of mantissa. The nine bits of exponent are loaded in the EPA or EPB. The value of bit 09 (exponent sign) is extended through bit 00. The nine bits of the mantissa remain stored in bits 18 through 26 of the BMB, since the A SIGN/FMA or B SIGN/FMB are loaded 36 bits at a time. The exponent bits in the BMB are cleared (bits 27 through 35).

At the end of the memory reference, the shift counter is decremented to 0. Since no borrow is detected, a second memory reference is initiated to fetch the 18 bits of high-order mantissa from memory. The address in the FP15 AR is incremented to access the next sequential memory location. The 18 bits of high-order mantissa are loaded into the high-order bits of the BMB by STROBE. The A side of the ALU is selected and the A SIGN/FMA or B SIGN/FMB is loaded with the 27 bits of mantissa.

At the end of the cycle, the shift counter is decremented and produces a borrow indicating that the operation is complete. The OPAND cycle is cleared and the EXP cycle is enabled.

#### 3.6.3 Extended Integer Format

In extended integer format (IR 11 – 1, IR 12 = 0) the shift counter is loaded with a count of 1 (SC 16 = 0, SC 17 = 1) during the FETCH cycle. The normal memory reference is made, and STROBE causes the 18 bits from memory to be loaded into the high-order bits of the BMB.

After completing the transfer, the shift counter is decremented to 0, no borrow is detected, the AR is incremented, and a second memory reference is initiated.

The second memory reference causes the 18 bits in the next sequential memory location to be loaded into the low-order bits of the BMB by -STROBE. The A side of the ALU is selected and the FMA or FMB is loaded with the 35-bit integer.

After the transfer of the second word, the shift counter is decremented from 0 to a borrow condition. The OPAND cycle is cleared and the EXP cycle is enabled.

## 3.6.4 Single-Precision Integer Format

In singl-precision integer format (IR 11 = 0, IR 12 = 0) only one memory reference is made. The shift counter is loaded in the FETCH cycle with a count of 0. A memory reference is performed to obtain the operand. The operand is loaded into the low-order bits of BMB 18-35. The value of bit 18 (sign bit) is entered through bit 00. The A side of the ALU is selected and the A SIGN/FMA or B SIGN/FMB is loaded.

At the end of the cycle, the shift counter is decremented from 0 to produce a borrow that clears the OPAND cycle and enables the EXP cycle.

#### 3.7 WRITE CYCLE

If a Store instruction is specified, the WRITE cycle is initiated. During the WRITE cycle the contents of the desired major registers are written into memory. Drawing D-FD-FP15-0-51 is a flow diagram of the WRITE cycle. At TS02\*PH03 of the NOR cycle, the shift counter is loaded with one less than the number of words to be transferred to memory.

The FP15 places the contents of the AR on the MDL and issues a delayed FP M REQ that allows for settling time. The AR contains the address where the first operand is to be stored. Memory receives the address on the MDL and issues ADR ACK indicating receipt of the address. This signal also clears FP M REQ and enables the data to be placed on the MDL.

The particular word (depending on the count in the shift counter) is strobed on the MDL. FP MRDA is delayed by ADDR ACK to allow address settling. The operand is strobed into memory by FP MRDA. Memory responds with MRLS ACK that clears FP MRDA to complete the cycle.

The number of memory references during the WRITE cycle depends on the instruction and/or data format. When the shift counter produces a borrow, the WRITE cycle is terminated. BUSY and DIS CP ACT signals are cleared and control is returned to the CPU.

3-12

The various types of store instructions are described below:

#### 3.7.1 Store JEA

If the instruction is Store JEA, the contents of the JEA are transferred to the output multiplexer (MPO) and then to the MDL.

#### 3.7.2 Double-Precision Floating Point

In double-precision floating-point format, the shift counter is loaded with a count of 2. The first word (contents of EPA register) is transferred to the output of the multiplexer. When the shift counter is decremented to 1, the second word (high-order mantissa ADD 00-17) is transferred to the output of the multiplexer. When the shift counter is decremented to 0, the third word (low-order mantissa ADD 18-35) is transferred to the output of the multiplexer.

#### 3.7.3 Single-Precision Floating Point

In single-precision floating-point format, the shift counter is 1; EPA bits 09 through 17 and FMA bits 18 through 26 are transferred to the output of the multiplexer. When the shift counter goes to 0, FMA bits 00 through 17 are transferred to the output of the multiplexer.

#### 3.7.4 Extended Integer

The shift counter is loaded with a count of 1 for this format. When the shift counter is 1, the high-order bits (ADD 00-17) are transferred to the output of the multiplexer and, if the shift counter is 0, the low-order bits (ADD 18-35) are transferred to the output of the multiplexer. When an Integer Store instruction is specified, positive or negative integers are transferred from the FMA to the FMB and are 1's complemented during FUN\*TS02. At NOR\*TS01, the FMB is incremented so the contents of the FMB are now a 2's complement representation of the integer in the FMA. During the WRITE cycle, the sign (A SIGN) of the FMA is examined. If the sign is positive, the integer is a positive integer and the contents of the FMA are stored in memory. If A SIGN is negative, however, the contents of the FMB are stored in memory, since the FMB is the 2's complement of the FMA and negative integers are 2's complemented before being transferred to memory.

#### 3.7.5 Single-Precision Integer

When a single-precision integer Store instruction is specified, the contents of the FMA are transferred to the FMB and 1's complemented during FUN\*TS02. At NOR\*TS01, the FMB is incremented and now

represents the 2's complement of the FMA. During the WRITE cycle, A SIGN is examined. If it is positive, the contents of the FMA are stored in memory; if it is negative, the 2's complement of the negative integer are stored in memory. This 2's complement is contained in the FMB and, consequently, the contents of the FMB are stored in memory.

#### 3.8 INTERRUPT CYCLE INTERFACE

The following conditions in the FP15 can cause an interrupt in the CPU.

- a. Overflow

- b. Underflow

- c. Abnormal division (divide by zero)

- d. Memory violations (trap)

An interrupt generated as a result of an overflow or underflow condition can occur during the FUN cycle, where the arithmetic operation is being performed, or during the NOR cycle, where the result of an arithmetic operation is being normalized. An abnormal divide interrupt can occur only during the FUN cycle; a memory violation interrupt can occur during the FETCH, OPAND, or WRITE cycles. If an interrupt should occur while an FP15/CPU cycle is in progress, the cycle is completed, the remaining sequence is aborted, and INT 1 and INT 2 interrupt cycles are initiated.

If an interrupt caused by a memory violation occurs in the OPAND cycle while the exponent is being fetched, this part of the sequence is completed, fetching of the high-order and low-order mantissas is aborted, and the interrupt occurs. If the interrupt occurs during fetching of the high-order mantissa, The FP15 completes this part of the cycle and aborts fetching of the low-order mantissa.

#### 3.8.1 INT 1 Cycle

When a floating-point interrupt is raised, the FP15 forces a JMS\*0 to the CPU by placing 120000<sub>8</sub> on the MDL. Figure 3-5 shows the communication between the CPU and FP15. It is assumed that a memory violation interrupt occurred during the fetching of the high-order mantissa. When the high-order mantissa has been fetched, the OPAND cycle is aborted and a dummy setup initiated. The FP15 removes DIS CP ACT and the CPU is allowed to make a memory request. DIS RD RST is raised and the FP15 completes the memory cycle. The FP15 then removes DIS RD RST, places 120000<sub>8</sub> (JMS\*0) on the MDL, and issues FP RD RST. The 120000<sub>8</sub> is strobed into the MI in the CPU and then executed. The remainder of the cycle between the FP15 and CPU is completed.

3-14

| SUB-<br>CYCLE                         | CENTRAL<br>PROCESSOR          | FLOATING-POINT<br>PROCESSOR                    | MEMORY                                             | REMARKS                                                                                 |

|---------------------------------------|-------------------------------|------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                       | M REQ · CP ACT                | 0 - DIS CP ACT  1 - DIS CP ACT  L - DIS RD RST | ADDR ACK                                           | CPU CONTINUES FROM TS03*PH02<br>CPU MAKES MEMORY REQUEST<br>FP15 COMPLETES MEMORY CYCLE |

| INT 1 CYCLE<br>JMS*0<br>(DUMMY FETCH) | O MINES                       | FP MRDA                                        | O + ADDR ACK<br>RD RST<br>MRLS ACK<br>O + MRLS ACK |                                                                                         |

| ))                                    | 120000 <sub>8</sub> + MI MRLS | FP MRLS ACK                                    |                                                    | FP15 FORCES JMS*0 (120000 <sub>8</sub> ) ON<br>MDL AND COMPLETES CPU CYCLE              |

|                                       | MI + IR                       | 0 - MRLS ACK<br>0 - DIS CP ACT                 |                                                    | 120000 <sub>8</sub> (JMS*0) LOADED IN IR                                                |

Figure 3-5 INT 1 Cycle Interface Diagram

#### 3.8.2 INT 2 Cycle

The FP15 initiates a second dummy setup that forces the CPU to accept the JEA (JMS Exit Address) instead of the contents of location 0 (see Figure 3-6). The JEA address is under programmer control and will vary depending on the cause of the interrupt.

| 0        |                             |

|----------|-----------------------------|

| JMP OVR  | /GO TO OVERFLOW             |

| 0        |                             |

| JMP UND  | /GO TO UNDERFLOW            |

| 0        |                             |

| JMP DIV  | /GO TO DIVIDE               |

| 0        |                             |

| JMP TRAP | /GO TO MEMORY VIOLATION     |

|          | O OIU 9ML<br>O VIO 9ML<br>O |

In the example presented, where a memory violation caused the interrupt, the JEA address +6 will contain the address of the PC (71XXXX8 instruction) +3 when the JMS is complete. JEA +7 may contain a jump instruction to an entry of a service routine associated with the interrupt.

| SUB-<br>CYCLE      | CENTRAL<br>PROCESSOR                   | FLOATING<br>POINT UNIT                           | MEMORY                             | REMARKS                                                                         |

|--------------------|----------------------------------------|--------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------|

|                    | M REQ · CP ACT -                       | 1 → DIS CP ACT<br>1 → DIS RD RST                 | ADDR ACK                           | CPU MAKES MEMORY REQUEST<br>FP15 COMPLETES MEMORY CYCLE                         |

| CYCLE<br>IMY FETCH | U + M REQ                              | FP MRDA                                          | 0 + ADDR ACK<br>RD RST<br>MRLS ACK |                                                                                 |

| INT 2 CYC          | JEA +0 OVR<br>2 UND<br>4 DIV<br>6 TRAP | 0 - DIS RD RST<br>JEA ADDRESS - MDL<br>FP RD RST | 0 → MRLS ACK                       | FP15 FORCES JEA ADDRESS ON MDL<br>AND COMPLETES CPU CYCLE                       |

|                    |                                        | FP MRLS ACK  0 + FP MRLS ACK  0 + DIS CP ACT     |                                    | JEA ADDRESS IS ACCEPTED BY CPU<br>AS IF IT WERE CONTENTS OF<br>LOCATION 0000008 |

Figure 3-6 INT 2 Cycle Interface Diagram

### 3.9 INTERRUPT CYCLE

On entering INT 1, DIS CP ACT is removed; this allows the CPU to continue (see drawing D-FD-FP15-0-62). When CP Active is clocked high, and a M REQ is made by the CPU to obtain the next instruction, the FP15 is set up to take control over memory. In addition, DIS RD RST is raised to inhibit communication between the CPU and memory, and DIS CP ACT is raised to temporarily suspend the CPU. Memory responds to the CPU M REQ with ADDR ACK, places the contents of the specified address on the MDL, and issues RD RST. The CPU never sees the contents of the address because of DIS RD RST. The FP15 issues MRDA and the memory responds with MRLS ACK to complete the cycle. Control is returned to the CPU. The FP15 then initiates a dummy setup that places 120000<sub>8</sub> on the MDL via the input multiplexer (MPI) and output multiplexer (MPO). FP RD RST is also placed on the MDL. At this point, the FP15 simulates memory and communicates with the CPU to complete the cycle. The 120000<sub>8</sub> is loaded into the MI register in the CPU. When the CPU receives the 120000<sub>8</sub>, it issues MRLS. The FP15 responds with FP MRLS ACK, both are then cleared and the INT 2 cycle is initiated.

The INT 2 cycle is similar to INT 1 except that the JEA address, instead of 120000<sub>8</sub>, is placed on the MDL, the CPU executes the 120000<sub>8</sub> as a JMS\*0 and makes a second M REQ. The FP15 again suspends the CPU with DIS RD RST, gains control of memory, and completes the memory cycle. The JEA address is placed on the MDL along with FP RD RST. At this point, the FP15 releases control to the CPU and simulates a memory so the CPU can load the JEA address into the MI register. The CPU can now complete its cycle which was initially suspended by the FP15. The action is concluded by BUSY and DIS CP ACT being cleared, thereby returning control to the CPU.

#### 3.10 FP15/CPU CONTROL

As an aid in understanding the exchange of control between the CPU and the FP15, Figure 3–7 shows a typical program describing what instructions the CPU would see and what instructions the FP15 would see if the program were executed. The first instruction (DAC 500) is recognized by the CPU and the contents of the accumulator are deposited in location 000500. The second instruction is a floating-point instruction that is recognized by both the CPU and FP15. The next three sequential locations (000110, 000111, and 000112) are recognized by the FP15. The FP15 takes control and forces a 710000 NOP on the MDL so that the CPU does not use the floating-point operand address as an instruction. Consequently the CPU waits, since the FP15 has control of memory. When the FP15 completes the instruction, both the CPU and FP15 again monitor the next instruction fetched from core. A similar process can be traced through the remaining steps in the program.

Figure 3-7 CPU/FP15 Sample Program

# CHAPTER 4 INSTRUCTION SET

#### 4.1 INTRODUCTION

The following paragraphs describe the classes of instruction used in the FP15. Several functions are applicable to many classes; these will be described first. The flow diagrams of the instructions specify where these functions occur, if applicable. These functions include: converting negative integers to sign and magnitude format, normalizing, and rounding.

#### 4.2 CONVERTING NEGATIVE INTEGERS TO SIGN AND MAGNITUDE FORMAT

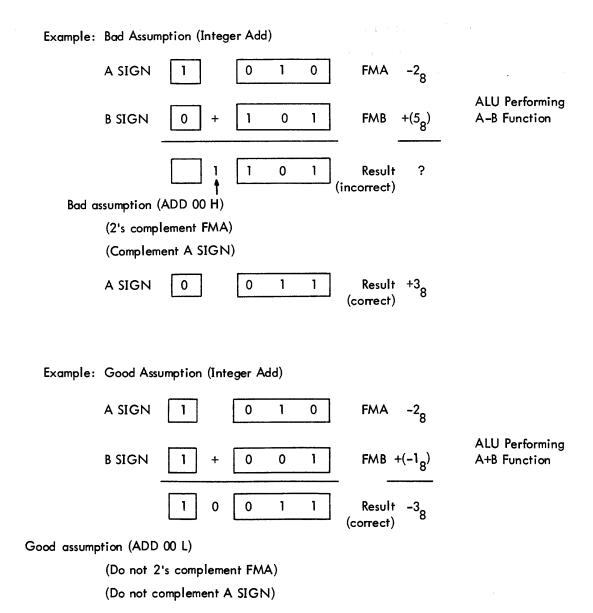

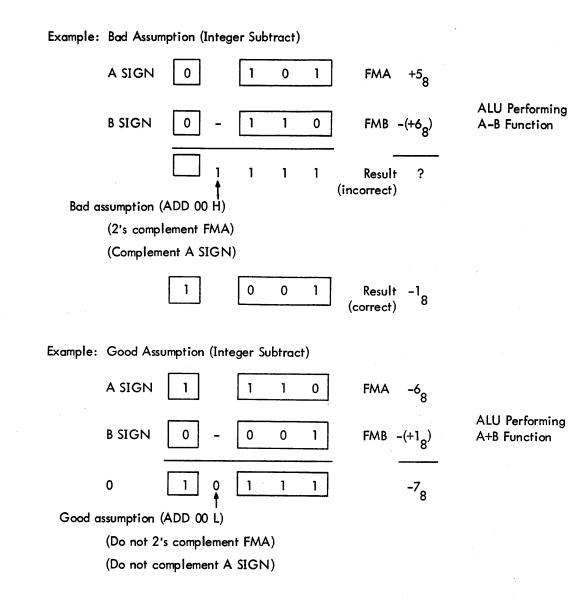

When a 2's complement negative integer is loaded into the FMA during the OPAND cycle, it is converted to sign and magnitude format during the EXP cycle. Two's complement positive integers are already in sign and magnitude format and require no conversion. If the instruction requires no memory reference, the number in the FMA is in sign and magnitude format. Two's complementing the number again is undesirable, since it would convert the sign and magnitude number back to a 2's complement number.

For FMA conversion during TS01 of the EXP cycle, FMA is complemented as a result of COMP MA (see Figure 4-1). This signal takes the 1's complement of the integer in the FMA and puts it on the ALU bus. During PH03\*TS01, the number on the ALU bus is strobed back into the FMA.

When the FP15 sequences to TS02 of the EXP cycle, INCA is generated; this puts the contents of the FMA plus one on the ALU bus. During PH03\*TS02, INCA-P is generated, and the output of the ALU bus is strobed back to the FMA. The number now in the FMA is the 2's complement of the number initially contained there and is a negative number in sign and magnitude format.

For FMB conversion, during TS01 of the EXP cycle, the FMB is complemented as a result of COMP MB. This signal takes the 1's complement of the integer in the FMB and puts it on the ALU bus. In PH03\*TS01, COMP MB P is generated which strobes the 1's complement integer back into the FMB.

Figure 4-1 Converting Negative Integers to Sign and Magnitude