**International Technical Support Centers**

**IBM RT PC SYSTEM ARCHITECTURE**

GG24-3024-00

## IBM RT PC System Architecture

Document Number GG24-: 324-00

## April 1986

International Technical Support Center Austin

۰.

First Edition (April 1986) This edition applies to the first release of the IBM RT PC system.

The information contained in this document has not been submitted to any formal IBM test and is distributed on an "as is" basis without any warranty either expressed or implied. The use of this information or the implementation of any of these techniques is a customer responsibility and depends on the ability of customers to evaluate and integrate them into their operational environment. While each item may have been reviewed by IBM for accuracy in a specific situation, there is no guarantee that the same or similar results will be obtained elsewhere. Customers attempting to adapt these techniques to their own environments do so at their own risk.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this document. If the form has been removed, comments may be addressed to International Technical Support Center - Austin, Dept. 948 / Bldg. 808, IBM Corporation, 11400 Burnet Road, Austin, Texas 78758, U.S.A.

All occurrences of the term Unix in this document refer to the trademark of AT&T Bell Labs.

c Copyright International Business Machines Corporation 1986

### ABSTRACT

For IBM RT PC the System Architecture is described by giving a reasonably technical presentation of both the hardware and software structure. In addition several other issues are covered such as an introduction to RISC technology and the UNIX enhancements added to the IBM RT PC operating system environment.

This bulletin is addressed to IBM systems engineers who wish to acquire a strong foundation on the system architecture of the IBM RT PC. The background needed to understand it is being familiar with interactive operating systems and knowing some basic concepts of computer hardware. Familiarity with UNIX is a plus, but it is not a prerequisite.

iv IBM RT PC System Architecture

This bulletin represents a compact presentation of both the hardware and software aspects of the system architecture of the IBM RT PC system.

This product combines:

- A very fast Reduced Instruction Set 32-bit processor for efficient execution of programs compiled from a high-level language.

- A resource manager that provides virtual machine, storage and I/O functions in order to assure data integrity and processing continuity.

- A multitasking, multiuser operating system based on the AT & T UNIX System V, but with a lot of IBM extensions allowing it to serve different user requirements.

- An 80286 Coprocessor feature that allows users to run programs written for the IBM Personal Computer without interfering with the normal native operation of the IBM RT PC.

- A wide variety of displays, printers, communications adapters and processing features are included in a system.

- All that can fit on or under a desk.

The structure of this bulletin is as follows:

- The first chapter: "Reduced Instruction Set Computers", covers the RISC topic, by showing the evolution of CPU technology and explaining what RISC technology is and why it is state-of-the-art.

- The second chapter: "IBM RT PC System Architecture Overview", covers the overall architecture of the IBM RT PC by giving equal emphasis to the hardware as well as to the software structure. It introduces the specific terminology and it allows the reader to better understand and combine the more in-depth treatment that follows.

- The third and fourth chapters: "The ROMP/MMU Processor Complex" and "Virtual Resource Manager (VRM) and Virtual Machine Interface (VMI)", cover in more detail, respectively, the hardware basis and the layered software architecture of the IBM RT PC.

- The appendices cover other topics, such as the Floating Point Accelerator option, the Coprocessor card, the system memory boards, the I/O adapters available and the UNIX enhancements implemented with the operating system of the IBM RT PC.

- A glossary with IBM and non-IBM references is also provided at the end of this bulletin.

vi IBM RT PC System Architecture

戴

an e d

# TABLE OF CONTENTS

| Reduced Instruction Set Computers                                        |

|--------------------------------------------------------------------------|

| Introduction to RISC                                                     |

| RISC Overview                                                            |

|                                                                          |

| IBM RT PC System Architecture Overview                                   |

| Introduction                                                             |

| System Hardware Architecture Summary 6                                   |

| Hardware Architecture                                                    |

| Software Architecture                                                    |

|                                                                          |

| The ROMP/MMU Processor Complex                                           |

| Introduction                                                             |

| ROMP Processor                                                           |

| ROMP Instruction Set                                                     |

| Interrupt Facility                                                       |

| Memory Management Unit (MMU)                                             |

| Virtual Address Translation                                              |

| Memory Protection                                                        |

| ECC and Parity Checking                                                  |

|                                                                          |

| Virtual Resource Manager (VRM) and Virtual Machine Interface (VMI) 33    |

| Introduction                                                             |

| Highlights of VRM                                                        |

| Functional Aspects of VRM                                                |

| I/O support                                                              |

| Real time tasking structure (for I/O processes)                          |

| Logical disk support and virtual storage control 40                      |

| Coprocessor support                                                      |

| Virtual console support                                                  |

| Development support                                                      |

| VRM Management routines                                                  |

| VMI characteristics                                                      |

| System integrity and virtual machine architecture                        |

|                                                                          |

| Appendix A. The IBM PC/AT Coprocessor                                    |

|                                                                          |

| Appendix B. Floating Point Accelerator (FPA)                             |

|                                                                          |

| Appendix C. System Memory Boards                                         |

|                                                                          |

| Appendix D. Other I/O bus options                                        |

|                                                                          |

|                                                                          |

| Appendix E. UNIX Enhancements                                            |

| Appendix E. UNIX Enhancements                                            |

| Appendix E. UNIX Enhancements                                            |

|                                                                          |

|                                                                          |

| Appendix F. Conclusions       61         Appendix G. References       63 |

| Appendix F. Conclusions                                                  |

Index

•

.

. . . . .

. . .

.

. . 73

• • • •

## LIST OF ILLUSTRATIONS

| Figure | 1.  | Overview of the hardware architecture             |

|--------|-----|---------------------------------------------------|

| Figure | 2.  | IBM RT PC software design                         |

| Figure | 3.  | Processor Board Data Flow and Board Interfaces 17 |

| Figure | 4.  | Data Units in System Memory 20                    |

| Figure | 5.  | SCR Organization                                  |

| Figure | 6.  | MMU Functional Parts                              |

| Figure | 7.  | Generation of Virtual Address                     |

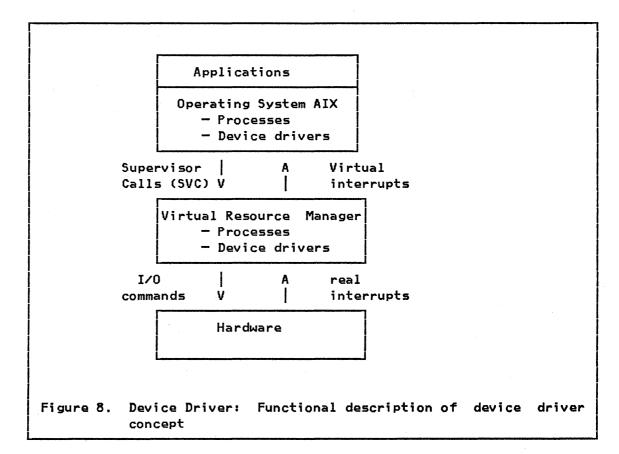

| Figure | 8.  | Device Driver                                     |

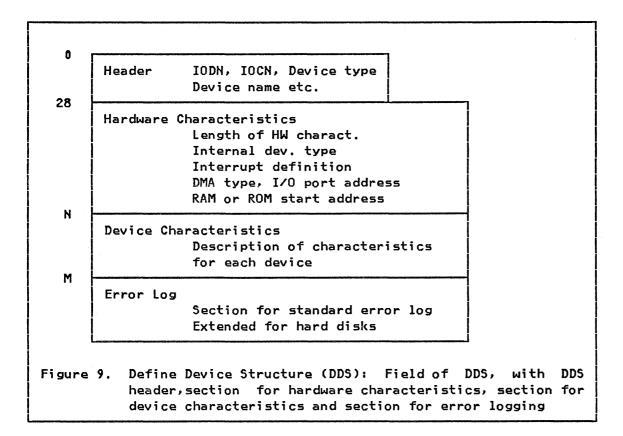

| Figure | 9.  | Define Device Structure (DDS)                     |

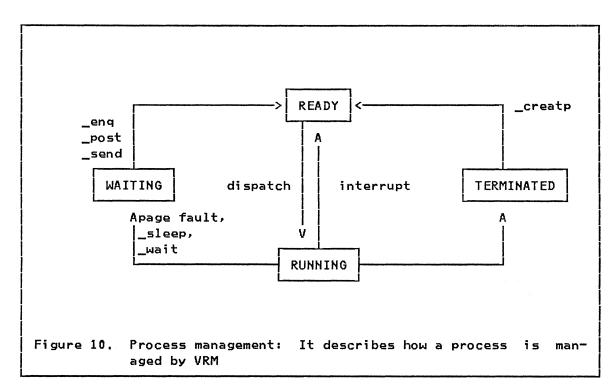

| Figure | 10. | Process management                                |

x IBM RT PC System Architecture

### Introduction to RISC

Before addressing why RISC technology is used on the IBM RT PC we shall first explain what RISC is. Since it is a relatively new concept most readers have probably never heard about it.

The abbreviation stands for Reduced Instruction Set Computers, and, as the term itself implies, we are talking about processors with only a basic set of instructions. This means that a RISC processor is not equipped with powerful instructions like the ones found in machines such as the IBM System/370 or even those at the microprocessor level.

Thus far we have only discussed the definition of RISC and it is imperative now to explain why this new concept exists in state-of-the-art computers like the IBM RT PC.

As VLSI technology advances, the new generation processor chips can implement the architecture of powerful minicomputers on a single chip. Such an implementation has to cope with certain purely technological constraints which engineers will not know how to overcome for several years. On one hand, the perspective of single-chip designs is rather limited by the resources one disposes of in terms of silicon real-estate, or more practically speaking, of the transistors and power dissipation the chip can handle. Typical designs today contain several tens (and at times even hundreds) of thousands of transistors.

On the other hand, the clear trend of current MOS technology is scaling down successful designs to narrower line widths. When a scaling takes place the devices on the chip become smaller and smaller. The distances electrons now have to travel are shrinking, and the devices become faster. Faster transistors, on a processor chip for example, immediately means an increase in the processor's throughput.

Since transistors become smaller and smaller the communications between different parts of the same chip become crucial. The signal delays introduced by long wiring connections are not at all negligible and it actually becomes one of the most difficult problems to resolve.

This shows that intra-chip communications have to be carefully addressed and random logic as well as long-distance communications have to be kept to an absolute minimum.

One can now understand that it is not only a matter of generating a proportionally scaled layout (in order to successfully map on a chip the architecture of a mini or a mainframe). The constraints we have discussed have to be well studied, understood, evaluated and dealt with accordingly. The system partitioning in different chips as well as the allocation of certain chip areas has to be done prudently and judiciously. In this context, IBM researchers have found that a reasonable restriction to a smaller set of instructions, combined with an architecture customized for fast execution of all the instructions in the set, can result in a machine with a surprisingly high throughput.

Such a Reduced Instruction Set Computer can be designed with a relatively small control section and a short machine cycle. The ROMP processor used in the IBM RT PC for example is characterized by a 170 nsec cycle. The design of such a processor is then much more straight-forward than traditional designs in the sense that both design time and the influence on the final result of the eventual architectural flaws are drastically reduced.

IBM has been directly involved in RISC research since 1975 when a team from the Yorktown Heights Research Center, led by George Radin, started experimenting with these ideas. The project was called "Project 801" from the site building number they were working in. An operational result was functional in 1979 based on standard off-the-shelf Establishment Communications Link (ECL) components, but the results were not made public for obvious reasons until 1982. Another project pursued by IBM engineers resulted in the ROMP processor, a very powerful 32-bit RISC microprocessor, which is the base of the IBM RT PC.

RISCs are not something only IBM has been working on. The University of California at Berkeley has developed two distinct designs; the RISC I in 1981 and the more sophisticated RISC II in 1983. A team from Stanford University has also recently introduced with the MIPS (Microprocessor without Interlocked Pipelined Stages) processor. Industry is also moving fast in this direction.

## RISC Overview

Computer architecture started existing as a concept in 1964 when IBM introduced the System/360. It was the first time that a differentiation was made between the computer architecture - the abstract structure of a computer that a machine-language programmer needs to know in order to write programs - and the actual hardware implementation of that structure.

Before that, the criteria to rate a computer was the cost of an implementation. However, researchers now tried to come up with new measures of performance. The decreasing hardware cost gave birth to arguments for richer instruction sets. Rich instruction sets were said to simplify compilers, compensate for the rising cost of software development and even improve the architecture quality. The new means of evaluating architectures was program size and the design mentality that prevailed in the 1970's was that large programs are invariably slow programs.

This philosophy is responsible for the exotic instruction formats one can find in machines like the IBM 370/168.

The use of microcode in that generation of machines was very intensive. The reasons are very simple to understand. Memory costs were steadily decreasing and large microcoded modules would add almost nothing to the overall cost. Microinstructions were faster than normal instructions. Registers made the writing of compilers very difficult and this was why stacks or memory-to-memory architectures were adopted.

In the meantime the cache memory, or high speed buffer, was invented, yielding substantial improvement in the implementation speed of the architecture, while compilers started finding it difficult to generate those complex new functions. A special breed of compilers, the optimizing compilers, were removing so many of the unknown elements at compile-time that they almost never made use of the powerful instruction set at run-time.

When computers made the transition from physical to virtual memory, the microcode had to ensure that any routine could start over if any memory operand caused a page fault. The performance gained by microcode was lost by a tremendous overhead which incurred during swapping in a multiprocess environment. When each program has its own microcode, a multiprocessing operating system has to reload the Writable Control Storage (WCS) with the corresponding microcode. This reloading time ranges between 1,000 and 25,000 memory accesses depending on the machine.

This latter point led researchers to decide that future computers should have virtual control storage, which meant that page faults could occur even during microcode execution. The distinction between programming and microprogramming was becoming less and less obvious.

It was clear that the attempt to bridge the "semantic gap" by using writable control storage had led to a "performance gap". The motives were still valid: programmers should write operations that mapped directly to microinstructions, and instructions should be no faster than microinstructions. However, the caches allowed main memory accesses at the same speed microcode was accessed in control storage. Microcode no longer enjoyed a ten-to-one speed advantage.

It was this whole context that gave rise to a new computer design philosophy. Optimizing compilers could be used for the compilation of high-level programming languages down to the level of simple instructions of comparable efficiency to microinstructions, and to make the instruction cycle as fast as technology would allow.

These machines are characterized by fewer instructions - hence the name RISC - which in general execute in one cycle.

RISCs have set up a new set of architectural design principles:

- All functions should be kept as simple as possible unless there is an extraordinary reason not to do so.

- Microinstructions should not be faster than simple instructions because caches are built from the same technology as WCS.

- Software is not better if microcode is used, it only becomes more difficult to change. All the hardware primitives available to microcode have to be accessible to assembly language programming.

- Simple decoding techniques and pipelined execution are much more important than program size. This leads to simple instruction formats which do not cross word boundaries.

- Compiler technology should be used to simplify instructions rather than to generate complex instructions.

The last point is of crucial importance and it deserves explanation. RISC compilers will try at compile-time to remove as much work as possible so that simple instructions can be used. This means, for example, that such a compiler will try to keep operands in registers, so that simple register-to-register instructions can be used. A traditional compiler will try to discover the ideal addressing mode and the shortest instruction format to add the operands in memory. In general, RISC compilers favor register-to-register operations because operands kept in registers are easily reused without new memory accesses and address calculations. RISC compilers use only LOADs and STOREs to access memory so that operands are not implicitly discarded after being fetched, as happens in the memory-to-memory model of execution.

Several unique features of RISC processors such as delayed branches and loads are described in depth in this document (see the Index).

## IBM RT PC SYSTEM ARCHITECTURE OVERVIEW

#### Introduction

The IBM RT PC is characterized by a totally new architecture and it is useful to talk a little about the goals identified right from the start of the development work.

The next generation of workstation systems had to be implemented using state-of-the-art technology both in hardware and software. This implied that the heart of the system should be a processor offering unprecedented capabilities in speed and functionality. Advanced memory management functions should be provided for and the system's physical size should be proportional to the potential of current integrated circuits technology. It also implied that an ingenious software structure had to be devised which would render the software applications practically independent of hardware configuration changes.

IBM RT PC designers wanted to assure a compatibility with the IBM Personal Computer architecture in order to provide the IBM RT PC user with the capability of using the vast amount of IBM and non-IBM applications which run on the PC.

The Research Oriented Mini Processor (ROMP) is a 32-bit IBM proprietary processor capable of about 4 MIPS (Million Instructions Processed per Second) execution speed and reduced instruction set. IBM researchers realized that instead of having a processor with very powerful instructions taking the system a lot of time to decode and being idle when branches and loads happened, they would rather develop a new processor, which would need less silicon real estate and which would only be armed by a basic instruction set. This would result in a system taking less time to run an application. The major development effort needs to be in coming up with really powerful compilers, which will be in position to fully exploit the capabilities offered by the processor. The IBM RT PC is the result of a joint effort development based on RISC system architecture work from Austin, the Yorktown Heights state-of-the-art compiler technology and the 2 micron silicon-gate NMOS process from Burlington, Vt.

Efficient compilers are possible now, where a lot of different optimization techniques are used in order to take advantage of the processor capabilities. For example the PL.8 compiler used internally for the IBM RT PC development generates code about 10% less efficient than good hand-written assembly.

Another concern was the addressability. Sixteen-bit computers are limited to addressing only 64K bytes or words. The only way to overcome this limitation is by using special hardware provisions or segment registers. However, it turns out that it is not that simple to handle objects larger than 64K even when using segment registers. Accordingly, the following goals are set up:

- The processor should be an all-32 bit machine, where registers, addresses and data are all 32-bits long.

- Virtual memory capabilities are a must in such a powerful workstation environment.

- The addressable space should be linear and practically not limited.

- The architecture should ensure the compatibility with existing IBM PC and PC/AT applications.

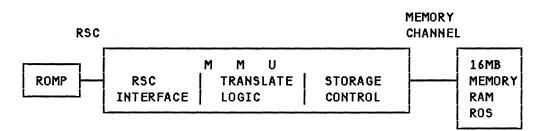

Reducing the cost of a system means using state-of-the-art VLSI design and packaging. For silicon area reasons the 2 major subsystems, i.e. processor and memory management unit, have been implemented in 2 different chips (actually the MMU is slightly larger than ROMP).

The IBM RT PC development team had in mind that the system should be characterized by a remarkably high performance without using expensive memory. The 801 minicomputer designed by a team at the IBM Thomas J. Watson Research Center was one of the first to investigate the effectiveness of RISCs. By using directly off-the-shelf ECL MSI components it gave tremendously encouraging results and inspired other teams to go on and mplement different appoaches on the RISC issue. The 801 was using 2 caches, which could deliver an instruction word and a data word at each cycle. However such caches are extremely expensive for small to medium systems and hence the IBM RT PC designers opted for pipeline-techniques. More details are given later on in this bulletin at the discussion of the system boards ("Appendix C. System Memory Boards" on page 51) and in the chapter discussing ROMP and MMU more deeply ("The ROMP/MMU Processor Complex" on page 17).

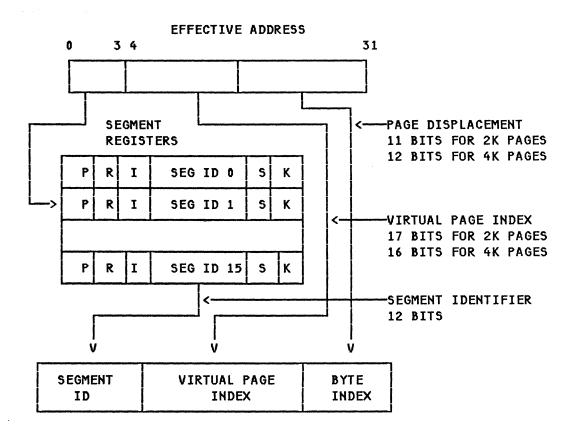

The IBM RT PC is offering a 40-bit virtually addressable space and it supports real memory size up to 16Mbytes. There are some concepts from the System/38 that are used and the system architecture provides a means of controlling access to virtual memory sections lying within a page. This proves especially useful in database locking schemes.

The system architecture was meant to assure the effective integration of such a virtual memory processor with existing as well as with new 8-bit and 16-bit I/O adapters. The attachment of coprocessors for compatibility and performance enhancement was also considered a must and the open architecture should allow the user to install practically everything he would think would enhance the performance of the machine.

#### System Hardware Architecture Summary

The IBM RT PC system architecture is the same for both the desktop and the floor-standing model. The floor-standing model offers the maximum

extensions because of more free slots, however most options are available to all models.

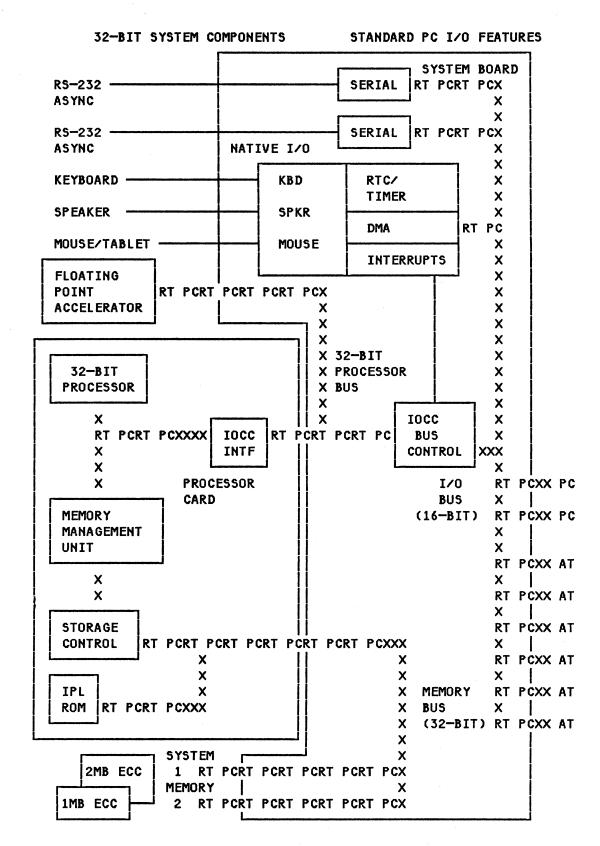

The IBM RT PC systems have a wide range of standard and optional hardware features. A system planar board is used with all basic circuits and I/O slots. Figure 1 on page 9 gives an illustration of the system architecture and its structuring. The I/O slots are designed in such a way that many existing IBM PC and PC/AT cards can also be plugged into the system. The operator keys-in the input from a 101-key keyboard or an optional 2-button mouse or even from a tablet-pointing device. Besides all the I/O slots there are specific slots in the system for each of the 32-bit system components. The ROMP processor and its Memory Management Unit lie on the processor card which comes with every model. On the same card lies also the ROM with the microcode used by the machine at IPL time. The Storage Control is also on the processor card, as well as the Error Correcting Code logic used by MMU when accessing the main memory. Data storage is provided on 5-1/4 inch hard disks and diskettes. One of the optional cards is the FPA (Floating Point Accelerator) card and it plugs into a separate 32-bit slot. Two other dedicated slots are used for system memory cards. Because of technological limitations, for the time being the only memory cards that are available are of 1 Megabyte and 2 Megabytes. This gives at this time a real storage capacity of up to 4 Megabytes. The hardware architecture however allows an expansion up to 16 Megabytes real memory.

The optional 80286 coprocessor card plugs in one unique slot and provides the ability to execute both IBM PC and PC/AT programs concurrently with native ROMP code. The I/O bus slots offer the possibility of using other coprocessor-options such as PC/AT memory cards and a mathematical coprocessor chip.

Several monochrome and color APA displays are supported by the system in addition to existing IBM PC displays and adapters. For computer-aided design applications a serial link adapter is provided allowing to attach an IBM 5085 graphics workstation in a host-based network.

### Hardware Architecture

The IBM RT PC system contains a 32-bit microprocessor and memory management unit combined with a 16-bit I/O bus. In order to provide high performance 32-bit processing capabilities as well as compatibility with standard 16-bit I/O adapters a system partitioning had to be done. The interface between the 2 buses is being taken care of by the IOCC (Input Output Channel Converter). The microprocessor is implemented using RISC architecture with only 118 instructions and a full 32-bit data flow for both data and addresses. The performance is rated at about 1.5 to 2.1 MIPS and the majority of register-to-register operations execute in one 170 nanosecond cycle.

The translation mechanism from a 32-bit system address to a 40-bit virtual address is provided by a "single level store" architecture implemented

by the MMU. The MMU also contains internal translation buffers which take care of the conversion between the 40-bit virtual address and the 24-bit real address. The MMU hardware also automatically reloads from the main memory space the translation buffers as needed. The ECC logic for system memory is contained in the MMU as well as some of the memory control logic and the IPL and power-on self test ROM. More details about the ROMP and the MMU chips can be found in "The ROMP/MMU Processor Complex" on page 17.

Figure 1 on page 9 shows the two distinct buses on the processor board. From that it is seen that on the processor card, except for the processor itself and its MMU, there are logic circuits accounting for adapting the high-speed 32-bit packet-switching processor bus to an asynchronous 32-bit bus processor to which directly connect the floating point accelerator card and the System Board IOCC (Input Output Channel Converter). The MMU interfaces with the system memory cards through a dedicated memory bus.

An interesting feature is that I/O channel timing does not affect the processor timing because the clock generation for the processor, its MMU and system memory is provided on the processor card. This will eventually allow the use of higher performance processor and memory cards as technology advances, without disrupting the I/O channel timing.

The optional FPA card can be attached to the 32-bit processor bus and provides much higher performance for floating point applications. The FPA card is based on the National Semiconductor NS32081 coprocessor and can operate totally independent from ROMP. The actual form of the FPA is relatively poor for such a machine and is evaluated to about 200,000 Whetstone Instructions per Second (200 KWIPS).

As already mentioned the system memory attaches to the processor card through two dedicated slots. The memory bus consists of a 40-bit data bus (32 bits of data plus 8 bits of (ECC) error correcting code) and a 24-bit address bus. The 24-bit addressing allows up to 16 Megabytes of real system memory. The ECC allows automatic detection and correction of all single bit system memory errors, as well as detection of all double bit errors.

The technology used is 256K dynamic RAM and on each memory card the system memory is two-way interleaved. This means that the available memory is always logically partitioned into two distinct banks. One bank contains only even addresses while the other contains only odd ones. This simple technique provides a very high system memory bandwidth of 23.5 megabytes per second (4 bytes per 170 nanoseconds) and renders cache architectures totally useless. This memory bandwidth is by far higher than the ones implemented in every other competitive machine of this class.

In order to adapt the 32-bit processor bus to a PC/AT-like I/O bus special conversion logic is needed. This logic is implemented on the system board. All the I/O channel support functions, such as the real time clock and timer, DMA controller and interrupt controller are also provided on the system board. Considerable effort was given to the task of keeping the IBM RT PC I/O channel as compatible as possible with the PC/AT I/O

Figure 1. Overview of the hardware architecture

bus. Besides timings and address, DMA and interrupt assignments that had to be kept as close to those of the PC/AT as possible, there have been new provisions such as burst and buffered DMA and shareable interrupts in order to enhance the channel performance. The IBM RT PC system supports eight channels of Direct Memory Access (DMA) by using two Intel 8237 DMA controllers. A DMA Adapter is either a DMA device or an alternate controller. The terms are explained in the glossary at the end of this bulletin. DMA channels 0-3 support 8-bit devices or 16-bit alternate controllers. DMA channels 5-7 support 16-bit devices or 16-bit alternate controllers. DMA channel 8 supports only alternate controllers. This DMA channel is only available on the coprocessor slot. The coprocessor has the lowest DMA priority on the I/O channel. However when it is executing out of system memory or I/O channel, attached RAM, it can hold on to the channel for multiple cycles to improve performance. More details can be found in the "IBM RT PC Hardware Technical Reference Manual" (see "Appendix G. References" on page 63).

Timing and performance of the I/O channel is the same for both models, however the 6150 provides two 8-bit PC slots and six 16-bit PC/AT slots in distinction to the 6151 which provides one 8-bit PC slot and five 16-bit PC/AT slots.

Adapters on the I/O channel can easily access system memory through hardware facilities responsible for programmable translation control on the system board.

The system board contains a separate microprocessor which is handling the keyboard, the mouse, the tablet interface and the speaker. The 6150 includes two built-in RS-232 serial ports with DMA capabilities for the attachment of terminals, printers or other I/O devices.

The optional coprocessor card is based on the 80286 and the optional extension 80287 as a math coprocessor. This card plugs in to an I/O channel slot and provides compatibility with IBM PC and PC/AT programs. On this card there is a considerable amount of control logic that protects the system against improperly written PC code, supports the sharing of system resources between the coprocessor and ROMP and is used by ROMP software to emulate current PC/AT adapters while using new adapters.

PC application programs for the coprocessor are stored in either system memory, or in dedicated I/O channel attached memory. Typically the coprocessor performance is that of a PC when executing programs in system memory, and about 80% that of a PC/AT when using I/O channel attached memory.

Concerning the hard disk possibilities of the system, the 5-1/4 inch industry standard disk units are available with 40 and 70 Megabytes with the possibility of having uo to three hard disks per system. The adapters are the existing IBM PC/AT Fixed-Disk and Diskette Drive adapters, something that shows how flexible the system is.

An external streaming tape drive and separate adapter card that attaches to the I/O channel is also available as an option. Using a standard 1/4

inch tape cartridge the streaming tape unit provides a backup capacity of 55 Megabytes.

Since this system is supposed to work at a multi-user multi-tasking environment different displays are supported offering the user the choice of the display that best suits his or her needs.

In the first place the system provides for the attachment of several existing IBM PC adapters and displays, such as the Monochrome Display and the Enhanced Color Display with their respective adapters.

The new displays and adapters for the IBM RT PC provide direct processor access to a 1024 x 512 bit map with a display viewing area of 720 x 512 pixels. Special hardware assist provides for text and graphics alignment down to the pixel level.

At a functionally higher level another display subsystem provides a considerably larger viewing area of 1024 x 768 pixels as well as extensive hardware assist for very high speed vector-to-raster conversion from a vector list buffer.

A full 1024 x 1024 color display with existing advanced computer-aided design applications is provided by the unique ability to attach an IBM 5085 Graphics Workstation to the IBM RT PC system in a host-based network.

The conclusion is that the IBM RT PC system is a very powerful system designed by IBM in order to bridge the gap between the rapidly expanding Personal Computer market and the more demanding market of 32-bit supermini level workstations with extensive virtual memory management facilities. This new generation of workstations has already become the basis of powerful computing systems that have extensive storage, display and communications requirements as they are supposed to offer THE solution to rapidly growing and evolving applications.

Specifically the IBM RT PC:

- Introduces an IBM developed high performance 32-bit RISC architecture with virtual memory.

- Combines the 32-bit features with a standard PC I/O channel.

- Provides an optional PC coprocessor for compatibility with already existing PC application programs.

- Allows future performance and feature upgrades by replacement of the processor, memory, and floating point cards as technology improves.

The usefulness of the open architecture of the IBM RT PC is a phenomenon already seen from the IBM PC family. It allows both IBM and vendors to very easily come up with different products which will enhance the functionality and the usability of the system. The architecture supports numerous possibilities of performance enhancement, such as increased memory capacity, larger hard-disk capacity, higher performance displays, different local-area networks, higher speed host attachments and different kinds of coprocessors.

## Software Architecture

Besides a new hardware architecture the IBM RT PC is implementing a totally new software architecture offering the user a powerful and easily reconfigurable environment.

In order to render this environment as functionally complete as possible, a three-level scheme is used. First, the built-in functions are powerful enough to satisfy most applications. Second, for the cases where the built-in functions are not complete controlled access is provided to the hardware, and third, the operating system is open-ended enough to allow for extensions to cover things such as new types of devices.

Another issue is that most of the IBM PC applications can be executed on the IBM RT PC, and there are vendors who would like to give those applications the maximum benefit from accessing the ROMP and MMU.

The layered structure (as shown in Figure 2 on page 13) of the VRM (Virtual Resource Manager) provides a lot of flexibility allowing the user to easily meet his needs.

The VRM is a software package which provides a high level operating system environment. The VRM is not an operating system itself. Its goal is to directly control the real devices and provide a standardized interface to applications. This interface is called the VMI (Virtual Machine Interface) and gives the applications the capabilities of a virtual machine and of virtual devices.

The VRM is designed to work on hardware consisting of a RISC processor and a PC/AT compatible I/O bus, but it should be kept in mind that this does not at all limit VRM to only such an environment. An example that VRM is able to support different I/O hardware is the VRM's support of the IBM 5080 graphics hardware, which is designed to an IBM 370 architecture channel interface.

We have already seen that the idea behind the RISC concept is to minimize hardware functions providing only a limited set of primitives. Since the processor is designed with a minimum logic, the native instructions enjoy a corresponding increase in execution speed. In such an environment, functions traditionally provided by hardware such as integer multiply and divide, or instructions like character string manipulations have to be replaced by software functions. That is exactly what VRM builds on the hardware. Namely VRM:

Provides a high-level machine interface, simplifying the development of guest operating systems and their applications.

|   |                  | ROGRAMS                           | LICATION PR     | APF            |                   |  |  |  |  |

|---|------------------|-----------------------------------|-----------------|----------------|-------------------|--|--|--|--|

|   | MANAGEMENT       | USABILITY PACKAGE DATA MANAGEMENT |                 |                |                   |  |  |  |  |

|   | (CE)             | TEM INTER                         | RATING SYST     | (BASE OPE      |                   |  |  |  |  |

| ] | vstem Management | lities                            | System Uti:     | Shells         | DOS & UNIX        |  |  |  |  |

|   |                  |                                   |                 |                |                   |  |  |  |  |

|   | EVICE DRIVERS    |                                   | C L             | KERM           |                   |  |  |  |  |

| F | Ξ                | E INTERFA                         | UAL MACHINI     | VIR            |                   |  |  |  |  |

| ' |                  | ·                                 |                 |                |                   |  |  |  |  |

|   |                  | VIRTUAL                           | VIRTUAL         | VIRTUAL        | VIRTUAL           |  |  |  |  |

|   | COMMUNICATIONS   | TERMINAL                          | DISK<br>MANAGER | I∕O<br>MANAGER | MEMORY<br>Manager |  |  |  |  |

IBM RT PC HARDWARE

Figure 2. IBM RT PC software design

- Maximizes performance for real-time applications, although the virtual memory capabilities of the machine can be of harm to a real-time environment as we will see later on.

- Allows users to easily reconfigure and customize their system according to their needs, by providing a very flexible and extendable interface.

- Provides compatibility with IBM-PC applications thanks to the 80286 coprocessor.

The VMI implements these points with a set of functions which facilitate the use of a variety of concurrent operating systems. Except for the problem isolation instruction set, the VMI assures the isolation of simultaneously running operating systems and applications from the actual hardware.

The concept of a virtual machine is not something new on IBM machines. One of the major IBM operating systems, VM/370 implemented on IBM 370 architecture mainframes provides a virtual machine environment. There are however many important differences between the way VM implements it and the way VRM does it on the IBM RT PC. VM/370 provides a complete functional simulation of the actual S/370 hardware. This means that an operating system designed and written to run on \$/370 hardware, such as MVS for example, will also run under VM in a virtual machine. The VMI support provided by the VRM provides much more functional support than the IBM RT PC hardware can. This means that if an operating system is written at the VMI level it will run as a guest under VRM but it will never run on the actual hardware.

Judging from the VM experience, we know that a virtual machine suffers in performance due to the overhead associated with the simulation of the different hardware functions. The VRM really is an exception to this rule because the vast majority of the guest operating system instructions execute directly on the hardware. The slight overhead VRM introduces is actually due to the VRM interference when it is invoked mainly to handle I/O operations at a relatively high functional level. This overhead was wanted, because the IBM RT PC designers opted for a more flexible and much more functionally rich programming environment than what a rigid native operating system could give.

The IBM RT PC operating system is the AIX, which was derived from AT & T's UNIX System V. Several enhancements to the original version have been included and the kernel has totally been rewritten by IBM. This assures a better integration of all additional and eventual functions as well as a differentiation from the UNIX-me-too vendors. For more details the reader is referred to "Appendix E. UNIX Enhancements" on page 55 and to "Appendix G. References" on page 63.

A key concept to understanding the support of multiple simultaneous interactive applications is the idea of the virtual terminal supported by AIX. A virtual terminal is the virtual counterpart of an IBM RT PC real device, such as the mouse, a display, or the keyboard. Each application works on a single virtual terminal which can either be a simulated ASCII terminal or a high-function terminal equivalent in power with the real device.

One of the responsibilities of the VRM is to take care of controlling all ROMP/MMU virtual memory functions. This relieves the operating system from having to handle page faults and management of real memory and paging space.

The operating system is also provided by the VRM with a queued interface to the I/O devices, insulating in this way the virtual machines from the burden of management of shared devices. AIX can dynamically add code to support and activate specialized devices while the VRM is running; that is without IPL.

The 80286 coprocessor is seen by the VRM as another virtual machine. When the coprocessor is active, all user input is presented to the coprocessor as if it was produced by the corresponding PC/AT devices. The VRM ensures that there will not be any interference between the 80286 coprocessor's and ROMP's distinct processing.

Two types of programs can be installed into the VRM: Device Drivers and Device Managers. Device Drivers are a set of subroutines which support a specific type of hardware device. Every time the VRM needs to cope with device-specific functions like handling interrupts and timeout conditions, and processing I/O commands from the virtual machines, it will call the corresponding Device Driver. The VRM Device Driver supports relatively simple devices, such as printers, diskette drivers, and tape drives.

On the other hand the Device Managers provide an additional level of support for more sophisticated devices, such as virtual terminals or communications subsystems. These subsystems usually have different requirements to handle multiple asynchronous events as well as to manage different kinds of shareable or non-shareable resources. The Device Managers and virtual machines are implemented by the VRM like "processes", which are served by the processor according to the control of a prioritized round-robin scheduling algorithm.

VRM support for processes includes the following features:

- Inter-process communications and queueing of messages and events are supported by queues.

- Semaphores are used for synchronization and serialization.

- Time of day and timer capabilities are equally available.

- Resources like DMA channels and interrupt levels are controlled and allocated by special functions.

A final note on the impact of virtual memory to the real-time performance of the system: Although real-time applications can in principle run on the ROMP, the current version of the operating system supports things like that rather weakly. The reason for that is that whenever there is a page fault, the interrupts from the real-time applications cannot be served before the missing pages are brought into system memory. This can be very harmful for delicate real-time applications when one cannot afford losing extra time. Although the development team is already implementing ways to bypass this shortcoming of virtual-memory systems, one should keep in mind that it is the 80286 which for the time being assumes the real-time responsibilities on the I/O channel.

١

16 IBM RT PC System Architecture

## Introduction

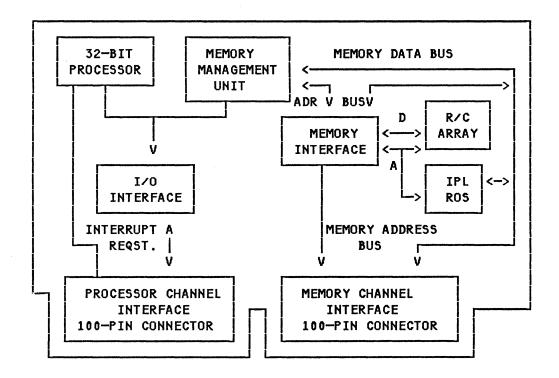

The Central Processing Unit (CPU) and the Memory Management Unit (MMU) of the IBM RT PC system are provided on a separate processor card, which plugs into a dedicated 200-pin slot on the system board. The Research Office Product Division MicroProcessor (ROMP) implements a full 32-bit RISC architecture. Current VLSI technology did not allow combining the ROMP CPU and the Memory Management Unit (MMU) on a single chip. The solution was to use two chips, one for the processor and one for the MMU. They are connected via a high performance channel, called RSC (ROMP Storage Channel). The RSC is a packet-switched 32-bit bus with a bandwidth of 23.5 Mbytes per second. This kind of performance is required to support the pipelined RISC architecture of the ROMP processor, which is able to execute an instruction almost every CPU cycle (170 ns).

Figure 3. Processor Board Data Flow and Board Interfaces

The following list summarizes some basic features of the processor card. In depth coverage will be given in later chapters.

| ROMP | processor |

|------|-----------|

|------|-----------|

|                     | •    | VLSI chip, housed in a 175-pin package                                                                                                                                              |

|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | •    | Fetches and executes instructions                                                                                                                                                   |

|                     | •,   | Pipelined 32-bit RISC architecture                                                                                                                                                  |

|                     | •    | Implements priority based interrupt scheme                                                                                                                                          |

|                     | •    | Supports user and system states                                                                                                                                                     |

| MMU                 |      |                                                                                                                                                                                     |

|                     | •    | VLSI chip, housed in a 175-pin package                                                                                                                                              |

|                     | •    | Supports 40-bit virtual address space (1024<br>GigaBytes or 1 TeraByte)                                                                                                             |

|                     | •    | Supports up to 16 Mbyte real memory                                                                                                                                                 |

|                     | ٠    | High resolution memory protection scheme                                                                                                                                            |

| RSC bu <del>s</del> |      |                                                                                                                                                                                     |

|                     | ٠    | Packet-switched 32-bit ROMP Storage Channel                                                                                                                                         |

|                     | ٠    | Bandwidth: 23.5 Mbyte/sec (4 bytes every 170<br>ns)                                                                                                                                 |

|                     | •    | Ability to support overlapped memory access                                                                                                                                         |

| IPL ROM             |      |                                                                                                                                                                                     |

|                     | •    | 32 Kbyte Read Only Memory for Initial Program<br>Load                                                                                                                               |

| PROCESSOR CHANNEL   | Conr | nects the processor board to                                                                                                                                                        |

|                     | •    | the (optional) Floating Point Accelerator,<br>which plugs into a dedicated slot on the system<br>board                                                                              |

|                     | •    | the I/O subsystem, located on the system board,<br>providing access to the I/O channel. The I/O<br>channel consists of 8-bit IBM PC and 16-bit IBM<br>PC/AT slots for attachment of |

|                     |      | – standard I/O adapters                                                                                                                                                             |

|                     |      | - IBM PC AT coprocessor                                                                                                                                                             |

IBM PC At memory boards

MEMORY CHANNEL

- Connects the processor board to the system memory

- Two dedicated slots on the system board

- 32-bit data bus plus 8-bit Error Correction Code (ECC)

- Bandwidth : 23 .5 Mbyte/sec (4 bytes every 170 ns)

It is important to distinguish between 32-bit ROMP system memory on the memory channel and 16-bit IBM PC/AT memory on the I/O channel.

### **ROMP** Processor

The register set of the ROMP processor consists of sixteen 32-bit General Purpose Registers (GPR's) and sixteen 32-bit System Control Registers (SCR's). All data and address manipulations are handled by any of the GPR's, which are grouped into eight pairs. These register pairs are implicitly used in certain instructions such as non-destructive shifts. The contents of a GPR can be treated as either a double word (4 bytes), a half word (2 bytes) or a character (1 byte) quantity.

The sixteen System Control registers (SCR's) are shown in Figure 5.

Some SCR's and special SCR fields are reserved. The others are assigned to system facilities such as

counter source system timer facility to provide real time functions

counter system timer facility

TS Timer Status (system timer facility)

- MQ Multiplier Quotient: The MQ is an extension of the MUL-TIPLY STEP and DIVIDE STEP instructions

- MCS Machine Check Status

- PCS Program Check Status

- IRB Interrupt Request Buffer

- ICS Interrupt Control Status

- IAR Instruction Address Register (instruction pointer)

| 0 | 8     | 3 :  | 16 2                                | 24 | 31 |  |  |  |

|---|-------|------|-------------------------------------|----|----|--|--|--|

|   | 0     | 1    | 2                                   | 3  |    |  |  |  |

| ſ | UPPER | HALF | LOWER                               |    |    |  |  |  |

| ſ | 0     |      |                                     |    |    |  |  |  |

|   |       |      | a chana a ghanna a fao hanna an ann |    |    |  |  |  |

BITS CHARACTERS OR BYTES HALF WORDS REGISTER IMAGE WORD

## Figure 4. Data Units in System Memory

#### CS

## Condition Status (flags)

The ability of the ROMP processor to execute an instruction almost every CPU cycle (170 ns) requires an on-chip instruction queue. The ROMP has four 32-bit Instruction Prefetch Buffers (IPB's) and they are usually at least partially filled, due to the high bandwidth of the ROMP Storage Channel (RSC), which is by far greater than necessary for program execution. The RSC has still enough bandwidth left to handle data references from the ROMP to system memory and to keep up with DMA traffic from the I/O channel to system memory.

Looking at the pipelined architecture of the ROMP it is obvious that instruction execution is relatively independent of memory requests. Instructions are prefetched into the IPB's, and having usually two or so instructions in its IPB's keeps the processor busy at almost any time. Several CPU cycles are necessary to complete one instruction. Execution of a single instruction consists of the following steps:

- InFt Instruction Fetch

- InDc Instruction Decode

- ExOp Execution of Operands in ALU

- HOLD hold-offs (wait cycles)

- RgWr Register Write to save results from ExOp step

The instruction fetch time can be assumed to be zero because of the on-chip prefetch buffers (IPB's). During every cycle the RSC receive area of the ROMP captures whatever is on the RSC bus. The tag lines of the RSC indicate if the incoming data is an instruction, to be stored in the appropriate IPB, or data to be stored into one of the registers.

At least three cycles are needed to complete a single instruction. The first cycle is used to decode the instruction (InDc), the second manipulates the operands in the ALU (ExOp) and the third stores the results of

| RESERVED       |                                                             |                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                    |  |  |  |

|----------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ERVE           | ED                                                          |                                                                                         | SCR                                                                                                                                           | 1                                                                                                                                                                                                                                                  |  |  |  |

| ERVE           | ED                                                          |                                                                                         | SCR                                                                                                                                           | 2                                                                                                                                                                                                                                                  |  |  |  |

| ERVE           | ED                                                          |                                                                                         | SCR                                                                                                                                           | 3                                                                                                                                                                                                                                                  |  |  |  |

| ERVE           | ED                                                          |                                                                                         | SCR                                                                                                                                           | 4                                                                                                                                                                                                                                                  |  |  |  |

| ERVI           | ED                                                          |                                                                                         | SCR                                                                                                                                           | 5                                                                                                                                                                                                                                                  |  |  |  |

| COUNTER SOURCE |                                                             |                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                    |  |  |  |

| COUNTER        |                                                             |                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                    |  |  |  |

|                | T                                                           | 5                                                                                       | SCR                                                                                                                                           | 8                                                                                                                                                                                                                                                  |  |  |  |

| RVEI           | D                                                           |                                                                                         | SCR                                                                                                                                           | 9                                                                                                                                                                                                                                                  |  |  |  |

| IER            | QUOT                                                        | FIENT                                                                                   | SCR                                                                                                                                           | 10                                                                                                                                                                                                                                                 |  |  |  |

| M              | CS                                                          | PCS                                                                                     | SCR                                                                                                                                           | 11                                                                                                                                                                                                                                                 |  |  |  |

| )              | -                                                           | IRB                                                                                     | SCR                                                                                                                                           | 12                                                                                                                                                                                                                                                 |  |  |  |

| IAR            |                                                             |                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                    |  |  |  |

| )              |                                                             | ICS                                                                                     | SCR                                                                                                                                           | 14                                                                                                                                                                                                                                                 |  |  |  |

| )              |                                                             | CS                                                                                      | SCR                                                                                                                                           | 15                                                                                                                                                                                                                                                 |  |  |  |

|                | ERVI<br>ERVI<br>ERVI<br>ERVI<br>ERVI<br>ERVI<br>SOU<br>NTEF | ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>IER QUOT<br>MCS | ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>ERVED<br>IER QUOTIENT<br>MCS PCS<br>IRB<br>IAR<br>IAR<br>ICS | ERVED SCR<br>ERVED SCR<br>ERVED SCR<br>ERVED SCR<br>ERVED SCR<br>SOURCE SCR<br>NTER SCR<br>TS SCR<br>IER QUOTIENT SCR<br>IER QUOTIENT SCR<br>IER QUOTIENT SCR<br>IER SCR<br>IER SCR<br>SCR<br>SCR<br>SCR<br>SCR<br>SCR<br>SCR<br>SCR<br>SCR<br>SCR |  |  |  |

### Figure 5. SCR Organization

the ExOp step into the specified register(s) on the ROMP. Only a few instructions need more than one cycle for the execution of the operands in the ALU (ExOp step).

In certain cases an instruction may be idle for a couple of cycles. So called hold-offs (HOLD cycles) occur if the instruction is waiting for data from the RSC. Since only LOAD/STORE and successful BRANCH instructions reference memory (via RSC) there are no HOLD cycles during the execution of a "normal" instruction. A highly overlapped processing scheme allows the execution of an instruction (InDc+ExOp+RgSt) almost every CPU cycle:

|    | 1           |      | Cycles . |      |      |      |    |   |   |   |    |   |

|----|-------------|------|----------|------|------|------|----|---|---|---|----|---|

|    |             | 1    | 2        | 3    | 4    | 5    | 6  | 7 | 8 | 9 | 10 |   |

| 1. | instruction | InDc | Ex0p     | RgWr |      | I    | 1  | I | 1 | I | 1  | 1 |

| 2. | instruction | I    | InDc     | Ex0p | RgWr | 1    | 1  | 1 | I | I | I  | 1 |

| 3. | instruction | 1    | I        | InDc | Ex0r | RgWr | ·1 | 1 | I | 1 | 1  | I |

ovel as

The one-cycle execution rate is prevented when an instruction needs more than one cycle to manipulate the operands in the ALU (very few instructions need that), because the decoding of the next instruction will be controlled by the LAST ExOp cycle of the preceding instruction:

|    |             |     | cycles |     |     |        |      |     |       |    |   |   |     |

|----|-------------|-----|--------|-----|-----|--------|------|-----|-------|----|---|---|-----|

|    |             | 1   |        | 2   | 3   | 4      | 5    | 6   | 7     | 8  | 9 | 1 | L O |

| 1. | instruction | Inl | )c E   | x0p | Ex0 | p Ex0p | RgWr | 1   | I     | ľ  | I | I | 1   |

| 2. | instruction | I   | 1      |     |     | InDo   | ExOp | 1   | 1     | 1. | I | 1 | 1   |

| 3. | instruction | I   | I      |     | I   | I      | InDc | Ex0 | p RgW | rl | 1 | I | 1   |

The first instruction needs three cycles to manipulate the operands in the ALU and therefore full overlapping cannot be achieved. The DIVIDE STEP instruction of the ROMP is an example for that.

References to memory require a two cycle hold-off. This time is required

- to get the data request out on the RSC,

- give the MMU time to access storage

- and get the reply from the RSC into the register.

Later, it will be shown that these hold-offs may be overlapped by the execution of subsequent instructions that do not reference the unloaded register(s). The following example examines a LOAD instruction:

| LOAD R1,VarA #load variable from memory into r | register 1 |

|------------------------------------------------|------------|

|------------------------------------------------|------------|

|           | cycles |      |      |       |     |      |   |

|-----------|--------|------|------|-------|-----|------|---|

|           | 1      | 2    | 3    |       | 4   | 5    |   |

| processor | InDc   | ExOp | HOLD | HO    | LD  | RgWr | I |

| RSC       | Į      | I    | requ | I     | Ire | pl   | I |

|           | I      | I    | data | I     | da  | tal  | I |

| Storage   |        |      | sta  | orage | I   |      |   |

|           |        |      | ac   | cess  | 1   |      |   |

At least five cycles are needed to get the job done. Memory will be referenced during the two hold-offs. ROMP puts the address of the variable (VarA) on the RSC at the beginning of the first hold-off cycle (data request) and the corresponding data reply from the MMU will be on the RSC at the end of the following cycle. Additional hold-offs may occur. The 2-cycle memory access includes address translation, address and data buffering and ECC error detection but not error correction. If an error is detected the reply from the MMU to ROMP is cancelled and retransmitted on a subsequent cycle if the error is correctable.

ROMP needs about 60% to 70% of the RSC bandwidth to support its inherent performance. The remainder is available for DMA I/O traffic without causing processor performance degradation. The ROMP can handle four outstanding instruction fetches and two outstanding data requests before requiring a reply. This decoupled nature of ROMP and memory is implemented by using tag lines on the RSC allowing ROMP and MMU to handle data and instructions on the RSC correctly.

As mentioned earlier, it is possible to keep the ROMP busy during the hold-off cycles of an instruction referencing memory. Due to the fact that the instruction queue on the ROMP (IPB's) is at least partially filled, subsequent instructions can be executed if they do not reference the unloaded register of the preceding instruction. Consider the following piece of code:

| LOAD | R1,VarA | # load variable into register 1   |

|------|---------|-----------------------------------|

| INC  | R2      | <pre># increment register 2</pre> |

| ADD  | R8,R12  | # add values of register 8 and 12 |

|      |         | and store result in register 8    |

|                 |     |        |      |      | 1    | cycl | es |   |   |   |   |

|-----------------|-----|--------|------|------|------|------|----|---|---|---|---|

|                 | 1   | 2      | 3    | 4    | 5    | 6    | 7  | 8 | 9 | 1 | 0 |

| 1. LOAD R1,VarA | InD | c ExOp | HOLD | HOLD | RgWr | 1    | 1  | 1 | 1 | 1 |   |

| 2. INC R2       | 1   | InDc   | Ex0p | RgWr | I    | 1    | 1  | I | I | 1 | 1 |

| 3. ADD R8,R12   | 1   | 1      | InDc | Ex0p | RgWr | I    | I  | I | I | I | I |

The example shows the high overlapping of instruction execution during hold-off cycles. The point is that useful work can be done during memory access if the compiler (or programmer) is able to place the loading of registers and their actual use in subsequent instructions not too close to each other in the instruction stream. In other words, there is a substantial difference in execution time. Consider the following example:

| progra | am 1:   | program 2: |         |  |  |  |  |

|--------|---------|------------|---------|--|--|--|--|

| LOAD   | R1,VarA | LOAD       | R1,VarA |  |  |  |  |

| ADD    | R1,+5   | INC        | R2      |  |  |  |  |

| INC    | R2      | ADD        | R8,R12  |  |  |  |  |

| ADD    | R8,R12  | INC        | R7      |  |  |  |  |

| INC    | R7      | ADD        | R1,+5   |  |  |  |  |

|        |         |            |         |  |  |  |  |

Without altering the program logic proper arrangement of the instructions results in shorter total execution time (7 cycles instead of ten):

program 1:

|    |      |         |      |         |       |      |      | CACT | es    |       |       |       |    |

|----|------|---------|------|---------|-------|------|------|------|-------|-------|-------|-------|----|

|    |      |         | 1    | 2       | 3     | 4    | 5    | 6    | 7     | 8     | 9     | 10    | I  |

| 1. | LOAD | R1,VarA | InDo | :   Ex0 | pHOL  | DHOL | DRg  | nr   | 1     | I     | I     | I     |    |

| 2. | ADD  | R1,+5   | I    | InD     | c HOL | DHOL | DHOI | DExO | pRgW  | rl    | I     | 1     |    |

| 3. | INC  | R2      | 1    | 1       | I     | 1    | I    | InD  | c Ex0 | ⊳ Rg₩ | rl    | 1     |    |

| 4. | ADD  | R8,R12  | I    | I       | 1     | I    | I    | 1    | InD   | c Ex0 | p RgW | rl    |    |

| 5. | INC  | R7      | I    | I       | I     | 1    | I    | 1    | I     | InD   | c Ex0 | p RgW | Ir |

----

program 2:

|      |      |      |                                                              |                                                                              | cycl                                                                                        | 25                                                                                                                                      |                                                                                                                               |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                   |                                                                                                               |

|------|------|------|--------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1    | 2    | 3    | 4                                                            | 5                                                                            | 6                                                                                           | 7                                                                                                                                       | 8                                                                                                                             | 9                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                | )                                                                                                             |