# 82365SL PC CARD INTERFACE CONTROLLER (PCIC)

- Designed for Use in Notebooks which Implement either an 8-Bit or 16-Bit External System Bus.

- ExCA™ Implementation of ISA Bus to PCMCIA 2.0 /JEIDA 4.1 Interface

- Each PCIC Supports Two PCMCIA 2.0 / JEIDA 4.1 68-pin Standard PC Card Sockets

- Cascadable up to Eight Sockets

- Each Socket Interchangeably Supports either Memory or I/O PC Cards

- System Bus Timings Compatible with Intel386™ SL Microprocessor SuperSet

- Direct Support for Most Integrated EISA/ISA Chipsets

- Easily Configured to Support Other Standard Architectures

- **Power Management Support**

- Individual Socket Power Control

- Insertion/Removal Capability

- Eliminates Need for System Configuration Jumpers

- Address Mapping Support for PCMCIA 2.0 /JEIDA 4.1 PC Card Memory and Address Windowing Support for I/O Space

- Selectable Interrupt Steering from PC Card to System Bus

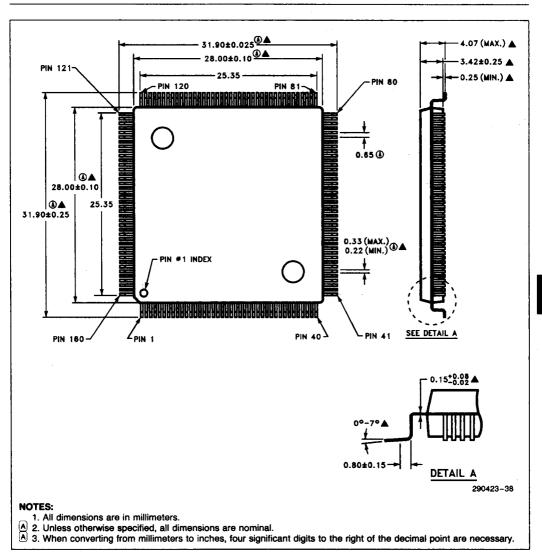

- 160-Pin JEDEC QFP Package (See Packaging Specifications Order Number 240800-001.)

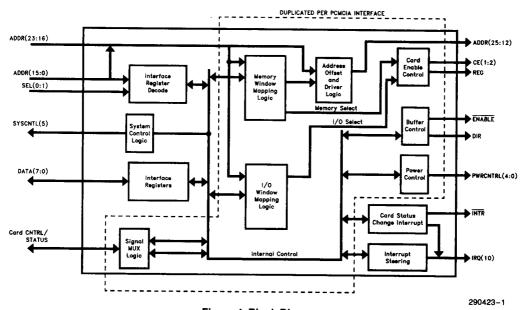

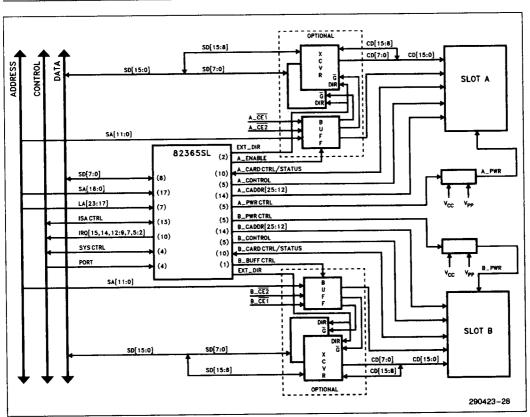

Figure 1. Block Diagram

ExCA™ and Intel386™ are trademarks of Intel Corporation.

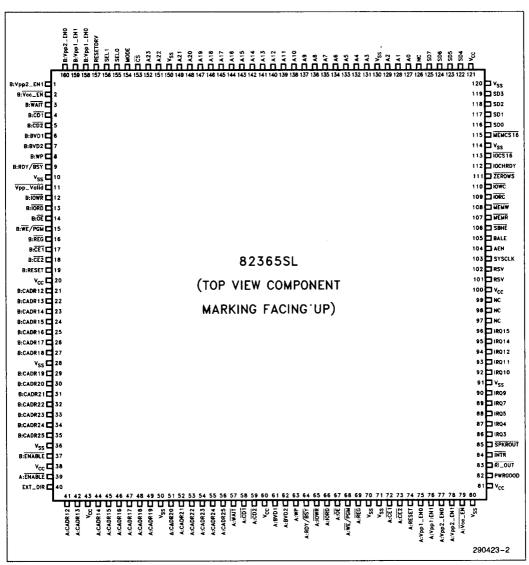

Figure 2. 82365SL Pin Out

### **PIN ASSIGNMENT**

### Pin Cross Reference by Pin Name

|    |                                       |    | 1 111 0103      |

|----|---------------------------------------|----|-----------------|

| 1  | B: V <sub>PP</sub> 2_EN1              | 18 | B: CE2          |

| 2  | B: V <sub>CC</sub> EN                 | 19 | B: RES          |

| 3  | B: WAIT                               | 20 | Vcc             |

| 4  | B: CD1                                | 21 | B: CAD          |

| 5  | B: CD2                                | 22 | B: CAD          |

| 6  | B: BVD1                               | 23 | B: CAD          |

|    | (B: STSCHG/<br>B: RI)                 | 24 | B: CAD          |

| 7  | · · · · · · · · · · · · · · · · · · · | 25 | B: CAD          |

| ′  | B: BVD2<br>(B: SPKR)                  | 26 | B: CAD          |

| 8  | B: WP                                 | 27 | B: CAD          |

|    | (B: <del>IOIS16</del> )               | 28 | V <sub>SS</sub> |

| 9  | B: RDY/BSY                            | 29 | B: CAD          |

|    | (B: ĪREQ)                             | 30 | B: CAD          |

| 10 | V <sub>SS</sub>                       | 31 | B: CAD          |

| 11 | V <sub>PP</sub> _Valid                | 32 | B: CAD          |

| 12 | B: ĪOWR                               | 33 | B: CAD          |

| 13 | B: ĪORD                               | 34 | B: CAD          |

| 14 | B: ŌE                                 | 35 | B: CAD          |

| 15 | B: WE/PGM                             | 36 | V <sub>SS</sub> |

| 16 | B: REG                                | 37 | B: ENA          |

| 17 | B: CE1                                | 38 | V <sub>CC</sub> |

|    |                                       |    |                 |

|    | rin Ciuss neie  |

|----|-----------------|

| 18 | B: CE2          |

| 19 | B: RESET        |

| 20 | V <sub>CC</sub> |

| 21 | B: CADR12       |

| 22 | B: CADR13       |

| 23 | B: CADR14       |

| 24 | B: CADR15       |

| 25 | B: CADR16       |

| 26 | B: CADR17       |

| 27 | B: CADR18       |

| 28 | V <sub>SS</sub> |

| 29 | B: CADR19       |

| 30 | B: CADR20       |

| 31 | B: CADR21       |

| 32 | B: CADR22       |

| 33 | B: CADR23       |

| 34 | B: CADR24       |

| 35 | B: CADR25       |

| 36 | V <sub>SS</sub> |

| 37 | B: ENABLE       |

| 00 | .,              |

| 39 | A: ENABLE          |  |  |

|----|--------------------|--|--|

| 40 | EXT_DIR            |  |  |

| 41 | A: CADR12          |  |  |

| 42 | A: CADR13          |  |  |

| 43 | V <sub>CC</sub>    |  |  |

| 44 | A: CADR14          |  |  |

| 45 | A: CADR15          |  |  |

| 46 | A: CADR16          |  |  |

| 47 | A: CADR17          |  |  |

| 48 | A: CADR18          |  |  |

| 49 | A: CADR19          |  |  |

| 50 | 50 V <sub>SS</sub> |  |  |

| 51 | 51 A: CADR20       |  |  |

| 52 | 52 A: CADR21       |  |  |

| 53 | A: CADR22          |  |  |

| 54 | A: CADR23          |  |  |

| 55 | A: CADR24          |  |  |

| 56 | A: CADR25          |  |  |

| 57 | A: WAIT            |  |  |

| 58 | A: CD1             |  |  |

| 59 | A: CD2             |  |  |

| 60 | V <sub>CC</sub>                  |

|----|----------------------------------|

| 61 | A: BVD1<br>(A: STSCHG/<br>A: RI) |

| 62 | A: BVD2<br>(A: <del>SPKR</del> ) |

| 63 | A: WP<br>(A: <del>IOIS16</del> ) |

| 64 | A: RDY/BSY<br>(A: ĪREQ)          |

| 65 | A: IOWR                          |

| 66 | A: ĪŌRD                          |

| 67 | A: OE                            |

| 68 | A: WE/PGM                        |

| 69 | A: REG                           |

| 70 | V <sub>SS</sub>                  |

| 71 | V <sub>SS</sub>                  |

| 72 | A: CE1                           |

| 73 | A: CE2                           |

| 74 | A: RESET                         |

| 75 | A: V <sub>PP</sub> 1EN0          |

| 76 | A: V <sub>PP</sub> 1_EN1         |

### PIN ASSIGNMENT (Continued)

### Pin Cross Reference by Pin Name (Continued)

| 77 | A: V <sub>PP</sub> 2EN0  |

|----|--------------------------|

| 78 | A: V <sub>PP</sub> 2_EN1 |

| 79 | A: V <sub>CC</sub> _EN   |

| 80 | V <sub>SS</sub>          |

| 81 | V <sub>CC</sub>          |

| 82 | PWRGOOD                  |

| 83 | RIOUT                    |

| 84 | INTR                     |

| 85 | SPKROUT                  |

| 86 | IRQ3                     |

| 87 | IRQ4                     |

| 88 | IRQ5                     |

| 89 | IRQ7                     |

| 90 | IRQ9                     |

| 91 | V <sub>SS</sub>          |

| 92 | IRQ10                    |

| 93 | IRQ11                    |

| 94 | IRQ12                    |

| 95 | IRQ14                    |

| 96 | IRQ15                    |

| 97 | NC                       |

| Fill Cross Reference L |                 |  |

|------------------------|-----------------|--|

| 98                     | NC              |  |

| 99                     | NC              |  |

| 100                    | V <sub>CC</sub> |  |

| 101                    | Reserved        |  |

| 102                    | Reserved        |  |

| 103                    | SYSCLK          |  |

| 104                    | AEN             |  |

| 105                    | BALE            |  |

| 106                    | SBHE            |  |

| 107                    | MEMR            |  |

| 108                    | MEMW            |  |

| 109                    | IORC            |  |

| 110                    | <u>IOWC</u>     |  |

| 111                    | ZEROWS          |  |

| 112                    | IOCHRDY         |  |

| 113                    | IOCS16          |  |

| 114                    | V <sub>SS</sub> |  |

| 115                    | MEMCS16         |  |

| 116                    | SD0             |  |

| 117                    | SD1             |  |

| 118                    | SD2             |  |

|                        |                 |  |

| 119 | SD3             |

|-----|-----------------|

| 120 | V <sub>SS</sub> |

| 121 | V <sub>CC</sub> |

| 122 | SD4             |

| 123 | SD5             |

| 124 | SD6             |

| 125 | SD7             |

| 126 | NC              |

| 127 | A0              |

| 128 | A1              |

| 129 | A2              |

| 130 | V <sub>SS</sub> |

| 131 | A3              |

| 132 | A4              |

| 133 | <b>A</b> 5      |

| 134 | A6              |

| 135 | A7              |

| 136 | A8              |

| 137 | A9              |

| 138 | A10             |

| 139 | A11             |

|     |                 |

| A12                      |

|--------------------------|

| A13                      |

| A14                      |

| A15                      |

| A16                      |

| A17                      |

| A18                      |

| A19                      |

| A20                      |

| A21                      |

| V <sub>SS</sub>          |

| A22                      |

| A23                      |

| <u>cs</u>                |

| MODE                     |

| SEL0                     |

| SEL1                     |

| RESETDRV                 |

| B: V <sub>PP</sub> 1_EN0 |

| B: V <sub>PP</sub> 1EN1  |

| B: V <sub>PP</sub> 2_EN0 |

|                          |

#### NOTE:

Pins 102 (RSV) and 101 (RSV) must be pulled up. A 10 K $\Omega$  is recommended.

### **QUICK PIN REFERENCE**

| Symbol                            | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interface Pin Descriptions |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

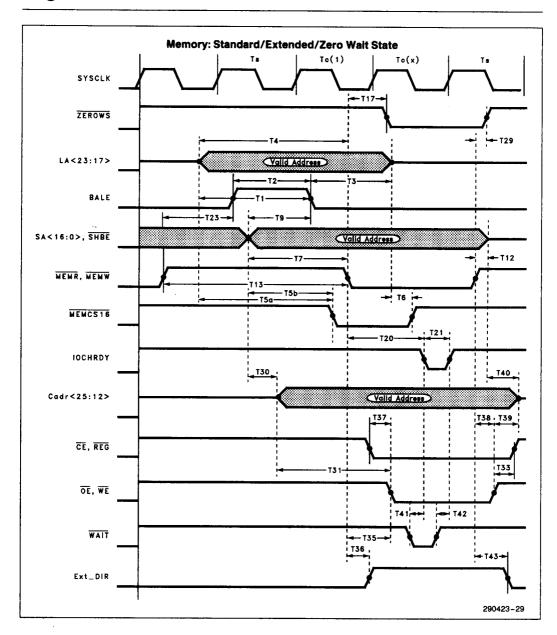

| A0:A23                            | I    | ADDRESS BUS lines driven by the host system which enable direct addressing of up to 16 Mbytes of memory on a card. Signal A0 is not used in word access mode. Signal A23 is the most significant bit. In a 16-bit ISA system, LA < 23:17 > should be connected to A < 23:17 > and SA < 16:00 > should be connected to A < 16:00 > .                                                                                                                 |

| AEN                               | ı    | SYSTEM ADDRESS ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BALE                              | ı    | BUS ADDRESS LATCH ENABLE: This active HIGH input is used to latch A23-A17 at the beginning of any bus cycle.                                                                                                                                                                                                                                                                                                                                        |

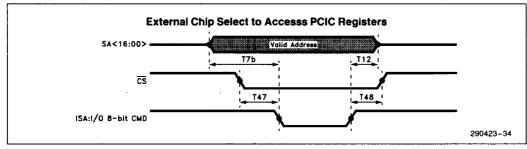

| CS                                | l    | <b>CHIP SELECT:</b> This signal is driven from an address decode if $Mode = 1$ , or is tied low. For internal chip select, $Mode = 0$ .                                                                                                                                                                                                                                                                                                             |

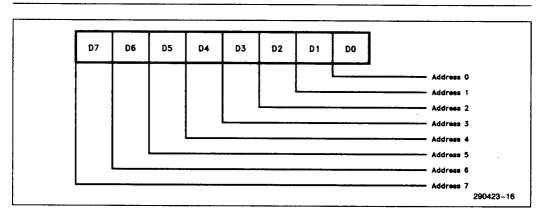

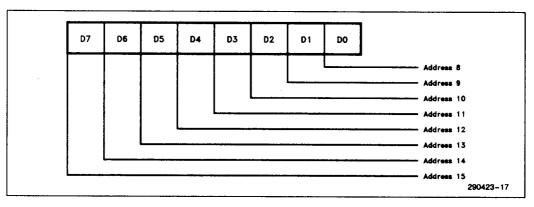

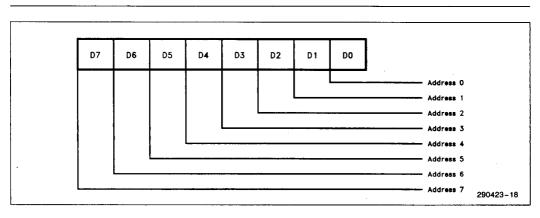

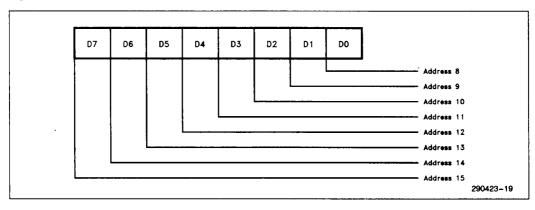

| SD0:SD7                           | 1/0  | <b>DATA INPUT/OUTPUT</b> lines constitute a bidirectional bus. D0 through D7 are used to access the PCIC internal registers.                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>                   |      | <b>GROUND:</b> Provides the 0V connection from which all inputs and outputs are referenced.                                                                                                                                                                                                                                                                                                                                                         |

| INTR                              | 0    | INTERRUPT REQUEST: This active LOW output requests a standard maskable interrupt to the CPU. INTR is intended to be connected to the EXTSMI of the Intel386 SL CPU.                                                                                                                                                                                                                                                                                 |

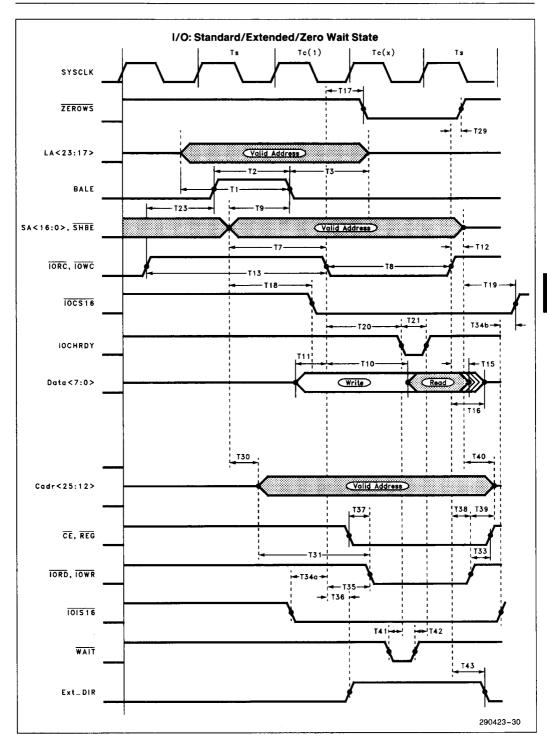

| IOCHRDY                           | 0    | I/O CHANNEL READY: This active HIGH signal is issued as an indication that the current I/O bus cycle is completed. When a PC Card peripheral needs to extend a READ or WRITE cycle, the PCIC pulls IOCHRDY LOW. IOCHRDY can be deasserted by either the PCMCIA signal WAIT, or by programming the PCIC to add wait states for 16-bit memory and I/O cycles. If Wait is used in 16-bit mode, the wait state generator has to be set to 1 wait state. |

| IOCS16                            | 0    | 16-BIT I/O TRANSFER MODE CHIP SELECT: This signal is used by the host system to determine when a 16-bit to 8-bit conversion is needed for CPU accesses. A 16 to 8 conversion is done anytime the System Controller requests a 16-bit I/O cycle and IOCS16 is sampled high.                                                                                                                                                                          |

| IORC                              | I    | I/O PORT READ: Driven to an active state (low) indicates to the PCIC that an I/O read cycle is occurring on the system bus.                                                                                                                                                                                                                                                                                                                         |

| IOWC                              | I    | I/O PORT WRITE: Driven to an active state (low) indicates to the PCIC that an I/O write cycle is occurring on the system bus.                                                                                                                                                                                                                                                                                                                       |

| IRQs                              | 0    | <b>SYSTEM INTERRUPT BACKPLANE REQUESTS:</b> These active high signals are used to request interrupt service.                                                                                                                                                                                                                                                                                                                                        |

| MEMCS16                           | 0    | 16-BIT MEMORY TRANSFER MODE CHIP SELECT: This signal is used by the host system to determine when a 16-bit to 8-bit conversion is needed for CPU accesses. A 16 to 8 conversion is done anytime the System Controller requests a 16-bit memory cycle and MEMCS16 is sampled high.                                                                                                                                                                   |

| MEMR                              | I    | SYSTEM MEMORY READ: Active LOW signal indicates a read cycle.                                                                                                                                                                                                                                                                                                                                                                                       |

| MEMW                              | I    | SYSTEM MEMORY WRITE: Active LOW signal indicates a write cycle.                                                                                                                                                                                                                                                                                                                                                                                     |

| MODE                              | l    | <b>DECODE MODE:</b> Used to determine if the Port Address Chip Select will be decoded internally (Mode $= 0$ ), or with external logic (Mode $= 1$ ).                                                                                                                                                                                                                                                                                               |

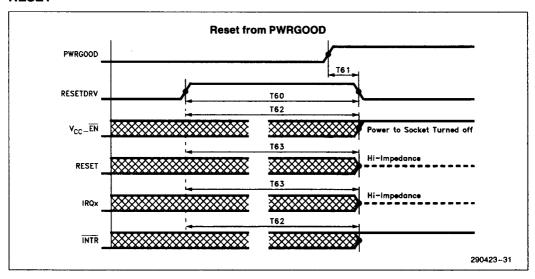

| PWRGOOD                           | _    | <b>POWER GOOD:</b> Active high signal indicates that power to the system is stable. Implementations not using the POWER GOOD signal should tie this signal low.                                                                                                                                                                                                                                                                                     |

### QUICK PIN REFERENCE (Continued)

| Symbol                                        | Туре | Name and Function                                                                                                                                                                                                                                    |

|-----------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interface Pin Descriptions (Continued) |      |                                                                                                                                                                                                                                                      |

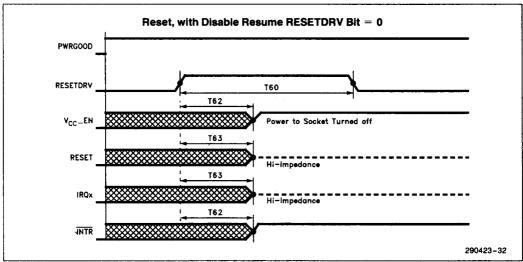

| RESETDRV                                      | ı    | RESET DRIVE: Active HIGH signal indicates a main system cold reset, generated by the Intel386 SL CPU as a combination of POWERGOOD and the Intel 386 SL CPU resume.                                                                                  |

| RSV                                           |      | <b>RESERVED:</b> Must be pulled high by an external resistor. A recommended value is 10K.                                                                                                                                                            |

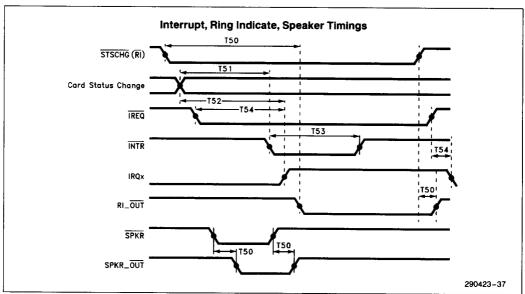

| RI_OUT                                        | 0    | RING INDICATE OUTPUT: Pass through of Ring Indicate output from I/O PC Card.                                                                                                                                                                         |

| SBHE                                          | ı    | SYSTEM BUS HIGH ENABLE: When this signal is LOW, it indicates that data is valid on the upper byte of the 16-bit data bus.                                                                                                                           |

| SEL0, SEL1                                    | 1    | SELECT PCIC BASE I/O ADDRESS: Strapping options that determine the PCIC registers base I/O address. All PCIC registers are accessed indirectly using an offset from the base I/O address. These signals allow chaining several PCICs together.       |

| SPKROUT                                       | 0    | SPEAKER OUT: Digital audio signal used to provide a single amplitude (digital) audio waveform intended to be driven to the system's speaker. Pass through of SPKR from I/O PC Card. When no audio signal is present, this signal shall be held high. |

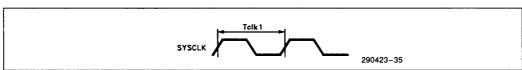

| SYSCLK                                        | 1    | SYSTEM CLOCK: 4.77 MHz-8.33 MHz. The value of the clock will effect the following:  INTR Timing characteristic INTR pulse width is 3 SYSCLKs in length  16 bit MEMR Delay  16 bit MEMW Delay                                                         |

| Vcc                                           |      | DEVICE POWER SUPPLY: 5V ± 10%.                                                                                                                                                                                                                       |

| ZEROWS                                        | 0    | <b>ZERO WAIT STATE:</b> This active LOW output indicates that a PC Card wishes to execute an 8-bit zero wait state bus cycle. This signal will not be driven during a 16-bit access.                                                                 |

## QUICK PIN REFERENCE (Continued)

NOTE:

The I/O PC Card Functions are listed below the Memory PC Card functions and in ().

| Symbol                                                                                                                 | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCMCIA/JEIDA PC Card Socket Interface Pin Descriptions                                                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BVD1, BVD2                                                                                                             |      | BATTERY VOLTAGE DETECT: Generated by memory PC Cards that include batteries. The signals are an indication of the condition of the battery on the memory PC Card.  Both BVD1 and BVD2 are kept asserted (high) when the battery is in good condition. When BVD2 is negated while BVD1 is still asserted, the battery is in a warning condition and should be replaced, although data integrity on the memory PC Card is still assured. If BVD1 is negated (low) with BVD2 either asserted or negated, the battery is no longer serviceable and data is lost. Signal status available by reading the Interface Status Register.  CHANGED STATUS: Signal is held high when either or both the "Signal on |

| (SPKR)                                                                                                                 | ı    | Change" bit and "Changed" bit in the Card Status Register on the PC Card are set to zero. When both the bits are one, the signal is held low. The Changed bit is the logical or of the bits CVBAT1, CVBAT2, CWP and CBSYRDY in the Pin Replacement Register on the PC Card.  Ring Indicate. Signal is qualified by the Ring Indicate Enable bit (Interrupt and General Control Register bit 7). If enabled the input signal is passed on to the RI_OUT output pin.  DIGITAL AUDIO: Is used to provide a single amplitude (digital) audio                                                                                                                                                               |

| CADR < 25:12 >                                                                                                         |      | waveform intended to be driven to the system's speaker.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CADH < 25:12 >                                                                                                         | 0    | CARD ADDRESS: Used with the lower 11 bits of Address Bus to generate Card Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CD1, CD2                                                                                                               | 1    | CARD DETECT: Provides for proper card insertion detection. The signals have been positioned at opposite ends of the connector to facilitate the detection process. The signals are connected to ground internally on the PC Card; thus they will be forced low whenever a card is placed in a host socket. Signal status is available by reading Interface Status Register.                                                                                                                                                                                                                                                                                                                            |

| CE1, CE2                                                                                                               | 0    | CARD ENABLE: Active low card enable signals driven by the PCIC. CE1 is used to enable even bytes, CE2 for odd bytes. A multiplexing scheme based on A0, CE1, CE2 allows 8-bit hosts to access all data on D0-D7 if desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

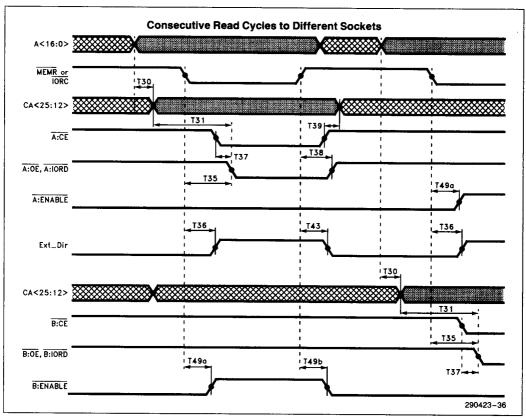

| ENABLE                                                                                                                 | 0    | <b>ENABLE:</b> Signal used to select PC Card socket to activate. This signal controls the external address buffer logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EXT_DIR                                                                                                                | 0    | <b>EXTERNAL TRANSCEIVER DIRECTION CONTROL:</b> This signal is high during a read, and is low during a write. The default power up condition is write (low.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IORD                                                                                                                   | 0    | I/O READ: Active low signal driven by the host system. It is used with the REG line to gate I/O Read data from the PC Card. IORD gates I/O Read data from a memory PC Card only when the REG line is also asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOWR                                                                                                                   | 0    | I/O WRITE: Signal is driven by the host system and used together with the REG line for gating I/O Write data to the memory PC Card. IOWR gates the I/O Write data to the PC Card only when the REG line is also asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ŌĒ                                                                                                                     | 0    | OUTPUT ENABLE: The $\overline{OE}$ line is an active low signal driven by the host system which is used to gate Memory Read data from memory PC Cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CC</sub> EN<br>V <sub>PP</sub> 1_EN0<br>V <sub>PP</sub> 1_EN1<br>V <sub>PP</sub> 2_EN0<br>V <sub>PP</sub> 2_EN1 | 0    | POWER CONTROL: Five signals used to control voltages (V <sub>PP</sub> 1, V <sub>PP</sub> 2 and V <sub>CC</sub> ) for PCMICA/JEIDA socket interface.  Logic is detailed in Power and RESETDRV Control Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# QUICK PIN REFERENCE (Continued)

#### NOTE:

The I/O PC Card Functions are listed below the Memory PC Card functions and in (). (Continued)

| Symbol                | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCMCIA/JEI            | OA PC Ca | rd Socket Interface Pin Descriptions (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>PP</sub> VALID | I        | V <sub>PP</sub> VALID: This active Low input indicates that the V <sub>PP</sub> power lines have reached the user specified range. Signal status is available by reading Interface Status Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RDY/BSY               | I        | READY/BUSY: Driven low by memory PC Cards to indicate that the memory card circuits are busy processing a previous write command. READY/BUSY is set high when memory PC Cards are ready to accept a new data transfer command. READY/BUSY is used as an interrupt request for I/O PC Cards. Signal status is available by reading Interface Status Register.  INTERRUPT REQUEST: Signal is asserted by an I/O PC Card to indicate to the host that a device on the I/O PC Card requires service by the host software. The signal is held at the inactive level when no interrupt is requested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REG                   | 0        | ATTRIBUTE MEMORY SELECT: Inactive (high) for all normal accesses to what is known as Main Memory of the PC Card. I/O PC Cards will not respond to IORD or IOWR when the REG signal is kept inactive. During DMA operations the REG signal must be kept inactive to ensure that PC cards do not respond to the I/O portion of a DMA transfer and to ensure that DMA accesses to the memory portion of a PC Card takes place to the Common Memory of the PC Card. This may be accomplished on an ISA compatible signal by forcing REG inactive whenever the ISA bus signal AEN (Address Enable) is inactive. When this signal is active (low), access is limited to Attribute Memory when WE or OE are active, and to I/O ports when IORD or IOWR are active.  For configurable memory PC Cards and I/O PC Cards, the PC Cards contain configuration and status registers in the Attribute Memory Space.                                                                                                                                                                                                                                                                                                                          |

| RESET                 | 0        | CARD RESET: Forces a hard reset to a PC card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WAIT                  | ı        | BUS CYCLE WAIT: Signal driven by the PC card to delay completion of the memory or I/O cycle which is in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WE/PRGM               | 0        | WRITE ENABLE: WE is used by the host for gating Memory Write data. WE is also used for memory PC Cards that employ programmable memory technologies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WP<br>(ĪŌIS16)        | 1        | WRITE PROTECT: Reflects the status of the Write Protect switch on memory PC Cards. If the memory PC Card switch is present, this signal will be asserted by the memory PC Card when the switch is enabled, and deasserted when the switch is disabled. If the memory PC Card has no Write Protect switch, the card will connect this line to ground or V <sub>CC</sub> , depending on the condition of the card memory. If the memory PC Card can always be written, the pin will be connected to ground. If the memory PC Card is permanently Write Protected, the pin will be connected to V <sub>CC</sub> .  For I/O PC Cards, WP is used for the Card is 16-Bit Port (IOIS16) function.  Signal status is available by reading the Interface Status Register.  CARD IS 16-BIT PORT: Signal is asserted by the PC Card when the address on the bus corresponds to an address to which the PC Card responds, and the I/O Port which is addressed is capable of 16-bit accesses. If this signal is not asserted during a 16-bit I/O access, the system will generate a second, 8-bit reference to the odd byte of the 16-bit word which is accessed by the initial cycle. If 8-bit window size is selected, IOIS16 is ignored. |

#### NOTE:

PCMCIA Input Acknowledge (INPACK) signal is not supported by the PCIC.

#### **OVERVIEW**

Intel's PC Card Interface Controller (PCIC) — is the ExCATM interface solution for notebook PCs. Currently, the PCIC allows OEMs to design their systems to provide the PC user with a wide range of connectivity options (Modem, Twisted Pair Ethernet, etc.) as well as eliminating rotating electro-mechanical media (via Intel Flash Memory Cards). Through the use of the ExCA standard interface, the PCIC will provide access to an even broader range of functions in the future.

The PCIC is the heart of the Intel ExCA implementation of the PCMCIA/JEIDA standard. ExCA and the PCIC provide an open standard system interface for PC Cards at the hardware and data interchange level. The PCIC insures that PC Card compatibility is maintained across manufacturers of PC Cards, as well as between systems from multiple notebook PC vendors.

The PCIC simplifies designing the PC Card socket to the ISA bus interface in a notebook PC. To fulfill this requirement, there were two main criteria which had to be met:

- Minimize chip count between an ISA bus and PC Card socket(s).

- Maximize flexibility by providing benefits such as programmable PC Card select decoding, multiple memory address translation maps, power management and I/O Interrupt steering.

In addition, the PCIC supports a jumperless configuration mechanism which allows the system manufacturer to support PC Card setup either through a configuration (CONFIG.SYS) driver or through an extension to the BIOS called "System Socket Services".

#### ARCHITECTURAL OVERVIEW

The PCIC functional blocks include the ISA interface, PCMCIA/JEIDA PC Card socket interface, Memory and I/O Window mapping, Power Management Support, Interrupt Steering, Configuration Registers and Digital Audio Signal.

#### ISA interface

The PCIC interfaces directly to the ISA bus, such as that found on the Intel386 SL Microprocessor Super-Set and most other integrated ISA chipsets. For systems based on the Intel386 SL Microprocessor SuperSet, the PCIC provides additional signals such as PowerGood, SPKROUT, INTR and RI\_OUT.

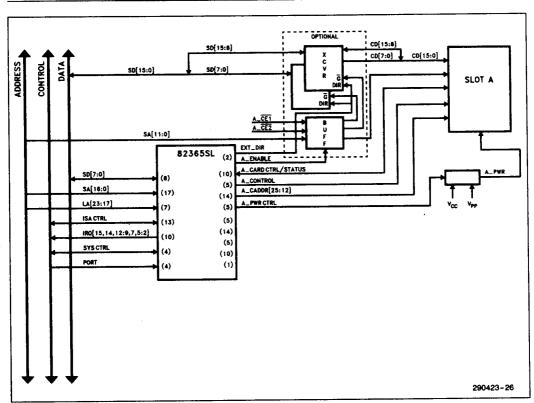

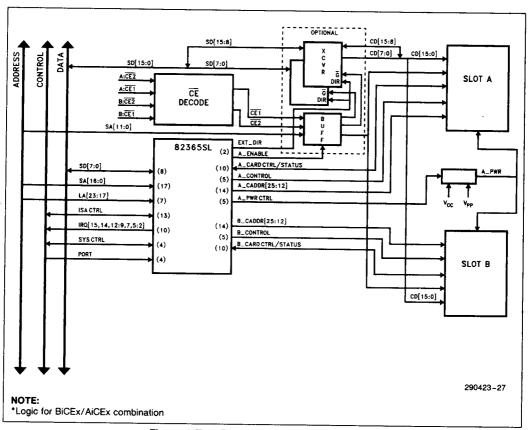

# PCMCIA/JEIDA PC Card Socket Interface

The PCMCIA/JEIDA interface consists of 60 signals and 8 power connections that interface to PC Cards through a 68 pin socket. A single PCIC can be configured to support either one or two PC Cards sockets directly, with the provision to allow up to eight PC Card sockets in multiples of two. The PCIC supports two PC Card types (either memory or I/O) interchangeably. It accomplishes this by multiplexing some of the static signals that are defined differently for memory and I/O PC Cards. These signals are configured appropriately by accessing the PC Card's card configuration registers.

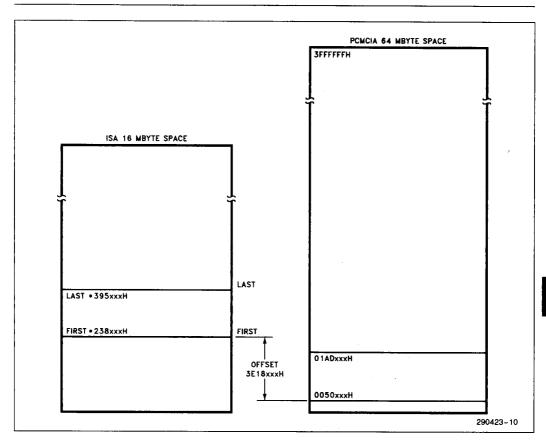

### Memory and I/O Window Mapping

As with standard PC add-in cards, multiple PC Cards in a system can conflict if they try to utilize the same system memory and I/O range. The PCIC allows the Operating System to map each PC Card into a separate memory range, and a separate I/O range, thus avoiding system configuration conflicts.

The PCIC provides memory paging, memory address mapping for both PC Card attribute and common memory, and I/O address mapping. The PCIC includes registers to allow access to the card information structure and card configuration registers within the attribute memory described by the PCMCIA/JEIDA PC Card Standard.

### **Power Management**

The PCIC implements power management for each PC Card socket. Socket power management is controlled through programming the **Power** and **RE-SETDRV** control register (Base + 02/42h). Additionally, each socket can be independently buffered to allow for insertion and removal of PC Cards. The system designer can add external buffer(s) and transceiver(s) to the system to provide electrical isolation between the PCMCIA sockets and the system

Buffering system examples are included in this data sheet.

### Interrupt Steering

The PCIC steers the one interrupt from the PC Card to one of ten system bus interrupts. Multiple PC Cards in a system can conflict if they try to utilize the same interrupt level (i.e.,  $\overline{\text{IRQ7}}$ ). The PCIC can be programmed to eliminate this conflict by steering each PC Card interrupt request to a different system interrupt.

### **Configuration Registers**

The PCIC provides a register containing interface identity and revision information for each socket.

### **Digital Audio Signals**

The PCIC supports special signals such as digital audio (SPKR). These signals are passed through to the system bus without signal conditioning.

# PC Card Interface I/O Register Addressing

All PCIC control registers are byte wide and accessed using an indirect indexing scheme. Two I/O addresses, are used to access the PCIC's control registers. The first I/O address is the PCIC's index register. The second I/O address is the PCIC's data register. Each PC Card socket can have up to 64 indirectly addressed registers. This allows for the support of two separate PC card sockets using only two I/O addresses. In order to support up to eight sockets in a system, another 2 I/O addresses are used which are selected by input lines (SEL0 and SEL1). Any system conflicts with the default I/O addresses can be overcome (setting the mode line) by using external address decode logic to map to another I/O addresss.

The PCIC index register and data register I/O address for the interface registers support both Intel386 SL CPU and ISA system configurations. The index register and the data register are read/write registers. The PCIC will not respond to a data register read or write operation or to an index register read operation unless the index register has first been written to with a valid index.

The **SEL1** and **SEL0** lines are strapping options for the PCIC, which determine the starting base for the index register values. **SEL1** and **SEL0** determine the mapping of socket A and socket B to one of four groups.

#### Index Base Values for Group 0 thru Group 3

| Mode | cs | SEL1 | SELO | Base | Index<br>I/O Add | Data<br>I/O Add |

|------|----|------|------|------|------------------|-----------------|

| 0    | 0  | 0    | 0    | 00h  | 3E0h             | 3E1h            |

| 0    | 0  | 0    | 1    | 80h  | 3E0h             | 3E1h            |

| 0    | 0  | 1    | 0    | 00h  | 3E2h             | 3E3h            |

| 0    | 0  | 1    | 1    | 80h  | 3E2h             | 3E3h            |

| 1    | 0  | Х    | Х    | 00h  | A0 = 0           | A0 = 1          |

| 1    | 0  | Х    | Х    | 80h  | A0 = 0           | A0 = 1          |

| Х    | 1  | Х    | Х    | XXh  | PCIC Not         | Selected        |

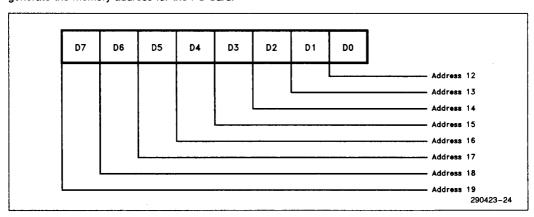

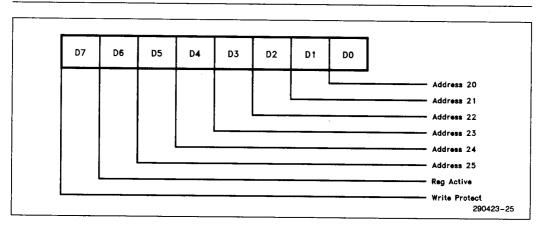

#### **REGISTER SET**

The following is a list of PCIC registers and their offset values. Each register is byte wide and can be read only or read/write.

#### **PCIC Registers Table**

| Socket A<br>Offset | Socket B<br>Offset | Register Name                              |  |

|--------------------|--------------------|--------------------------------------------|--|

| + 00h              | + 40h              | Identification and Revision                |  |

| + 01h              | + 41h              | Interface Status                           |  |

| + 02h              | + 42h              | Power and RESETDRV Control                 |  |

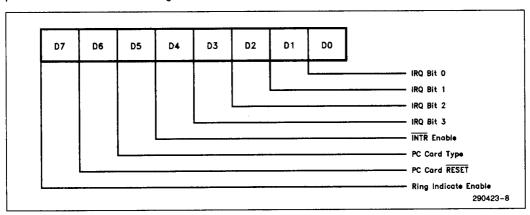

| + 03h              | + 43h              | Interrupt and General Control              |  |

| + 04h              | + 44h              | Card Status Change                         |  |

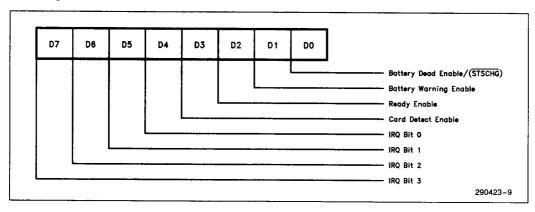

| + 05h              | + 45h              | Card Status Change Interrupt Configuration |  |

| + 06h              | + 46h              | Address Window Enable                      |  |

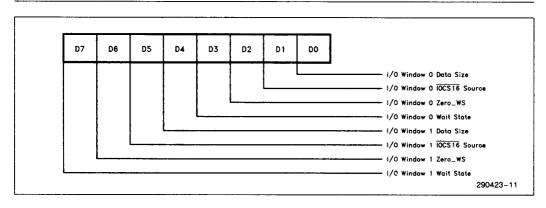

| + 07h              | + 47h              | I/O Control                                |  |

| + 08h              | + 48h              | I/O Address 0 Start Low Byte               |  |

| + 09h              | + 49h              | I/O Address 0 Start High Byte              |  |

| + 0Ah              | + 4Ah              | I/O Address 0 Stop Low Byte                |  |

| + 0Bh              | + 4Bh              | I/O Address 0 Stop High Byte               |  |

| + 0Ch              | + 4Ch              | I/O Address 1 Start Low Byte               |  |

| + 0Dh              | + 4Dh              | I/O Address 1 Start High Byte              |  |

| + 0Eh              | + 4Eh              | I/O Address 1 Stop Low Byte                |  |

### **REGISTER SET** (Continued)

### **PCIC Registers Table (Continued)**

|                    | - Toto negisters rable (Continued) |                                                                               |  |  |  |

|--------------------|------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Socket A<br>Offset | Socket B<br>Offset                 | Register Name                                                                 |  |  |  |

| + 0Fh              | + 4Fh                              | I/O Address 1 Stop High Byte                                                  |  |  |  |

| + 10h              | + 50h                              | System Memory Address 0 Mapping Start Low Byte                                |  |  |  |

| + 11h              | + 51h                              | System Memory Address 0 Mapping Start High Byte                               |  |  |  |

| + 12h              | + 52h                              | System Memory Address 0 Mapping Stop Low Byte                                 |  |  |  |

| + 13h              | + 53h                              | System Memory Address 0 Mapping Stop High Byte                                |  |  |  |

| + 14h              | + 54h                              | Card Memory Offset Address 0 Low Byte                                         |  |  |  |

| + 15h              | + 55h                              | Card Memory Offset Address 0 High Byte                                        |  |  |  |

| + 16h              | + 56h                              | Reserved                                                                      |  |  |  |

| + 17h              | + 57h                              | Reserved                                                                      |  |  |  |

| + 18h              | + 58h                              | System Memory Address 1 Mapping Start Low Byte                                |  |  |  |

| + 19h              | + 59h                              | System Memory Address 1 Mapping Start High Byte                               |  |  |  |

| + 1 <b>A</b> h     | + 5Ah                              | System Memory Address 1 Mapping Stop Low Byte                                 |  |  |  |

| + 1Bh              | + 5Bh                              | System Memory Address 1 Mapping Stop High Byte                                |  |  |  |

| + 1Ch              | + 5Ch                              | Card Memory Offset Address 1 Low Byte                                         |  |  |  |

| + 1Dh              | + 5Dh                              | Card Memory Offset Address 1 High Byte                                        |  |  |  |

| + 1Eh              | + 5Eh                              | Reserved                                                                      |  |  |  |

| + 1Fh              | + 5Fh                              | Reserved                                                                      |  |  |  |

| + 20h              | + 60h                              | System Memory Address 2 Mapping Start Low Byte                                |  |  |  |

| + 21h              | + 61h                              | System Memory Address 2 Mapping Start High Byte                               |  |  |  |

| + 22h              | + 62h                              | System Memory Address 2 Mapping Stop Low Byte                                 |  |  |  |

| + 23h              | + 63h                              | System Memory Address 2 Mapping Stop High Byte                                |  |  |  |

| + 24h              | + 64h                              | Card Memory Offset Address 2 Low Byte                                         |  |  |  |

| + 25h              | + 65h                              | Card Memory Offset Address 2 High Byte                                        |  |  |  |

| + 26h              | + 66h                              | Reserved                                                                      |  |  |  |

| + 27h              | + 67h                              | Reserved                                                                      |  |  |  |

| + 28h              | + 68h                              | System Memory Address 3 Mapping Start Low Byte                                |  |  |  |

| + 29h              | + 69h                              | System Memory Address 3 Mapping Start High Byte                               |  |  |  |

| + 2Ah              | + 6Ah                              | System Memory Address 3 Mapping Stop Low Byte                                 |  |  |  |

| + 2Bh              | + 6Bh                              | System Memory Address 3 Mapping Stop High Byte                                |  |  |  |

| + 2Ch              | + 6Ch                              | Card Memory Offset Address 3 Low Byte                                         |  |  |  |

| + 2Dh              | + 6Dh                              | Card Memory Offset Address 3 High Byte                                        |  |  |  |

| + 2Eh              | + 6Eh                              | Reserved                                                                      |  |  |  |

| + 2Fh              | + 6Fh                              | Reserved                                                                      |  |  |  |

| + 30h              | + 70h                              | System Memory Address 4 Mapping Start Low Byte                                |  |  |  |

| + 31h              | + 71h                              | System Memory Address 4 Mapping Start High Byte                               |  |  |  |

| + 32h              | + 72h                              | System Memory Address 4 Mapping Stop Low Byte                                 |  |  |  |

| + 33h              | + 73h                              | System Memory Address 4 Mapping Stop Low Byte                                 |  |  |  |

| + 34h              | + 74h                              | Card Memory Offset Address 4 Low Byte                                         |  |  |  |

| + 35h              | + 75h                              | Card Memory Offset Address 4 Low Byte  Card Memory Offset Address 4 High Byte |  |  |  |

| + 36h              | + 76h                              | Reserved                                                                      |  |  |  |

| + 37h              | + 77h                              | Reserved                                                                      |  |  |  |

| + 38h              | + 78h                              | Reserved                                                                      |  |  |  |

| + 39h              | + 79h                              | Reserved                                                                      |  |  |  |

| + 3Ah              | + 7Ah                              | Reserved                                                                      |  |  |  |

| + 3Bh              | + 7Bh                              | Reserved                                                                      |  |  |  |

| + 3Ch              | + 7Ch                              | Reserved                                                                      |  |  |  |

| + 30h              | + 7Dh                              | Reserved                                                                      |  |  |  |

| + 3Eh              | + 7Eh                              | <b>♣</b>                                                                      |  |  |  |

| + 3En<br>+ 3Fh     | + 7En<br>+ 7Fh                     | Reserved                                                                      |  |  |  |

| T 3FII             | _ T /FN                            | Reserved                                                                      |  |  |  |

### **General Setup Registers**

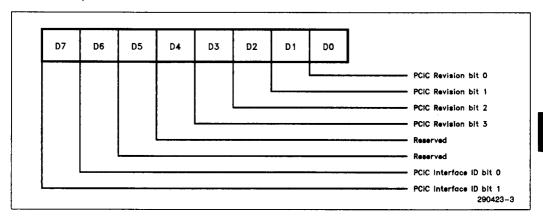

#### Identification and Revision Register (Read Only)

Socket A: Index Value (Base + 00h) Socket B: Index Value (Base + 40h)

The Identification and Revision Register is used by the system software to determine the type of PC Cards supported, and to identify what version of a PCIC is present. System software reads the Identification and Revision Register and then compares the result value against existing revision numbers (82h for Rev. 0 PCIC silicon ID code).

Bit 7 and Bit 6: PCIC Interface Type

These bits indicate the type of PC Cards supported by the PCIC at the particular socket. These bits do not identify the type of card that is present at the socket.

| ID 1 | ID 0 | Interface    |

|------|------|--------------|

| 0    | 0    | I/O Only     |

| 0    | 1    | Memory Only  |

| 1    | 0    | Memory & I/O |

| 1    | 1    | Reserved     |

#### NOTE:

These bits will read back as 10.

Bit 5 and Bit 4: Reserved

These bits will be read back as zero.

Bit 3 thru Bit 0: PCIC Revision

These four bits indicate the current revision level of the PCIC.

The initial revision code will be 0010.

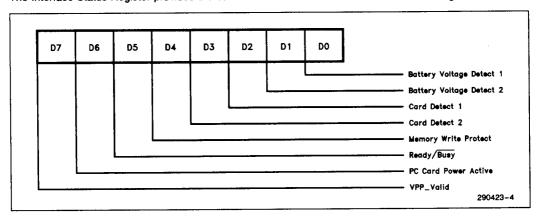

#### **Interface Status Register (Read Only)**

Socket A: Index Value (Base + 01h) Socket B: Index Value (Base + 41h)

The Interface Status Register provides the current status of the PC Card socket interface signals.

Bit 7: Vpp\_Valid.

Indicates the state of the  $\overline{V_{PP}\_Valid}$  pin. If this bit is set to a one, the  $\overline{V_{PP}\_Valid}$  pin is active  $\overline{(V_{PP}\_Valid} = 0$ ). If this bit is set to zero, the  $\overline{V_{PP}\_Valid}$  pin is inactive  $\overline{(V_{PP}\_Valid} = 1)$ .

#### NOTE:

The logic level of this bit is the reverse of the VPP\_VALID pin.

#### Bit 6: PC Card Power Active

Indicates the current power status of the socket. If bit is set to zero, power to the socket is turned off ( $V_{CC}$ ,  $V_{PP}1$ , and  $V_{PP}2$  are all no connects). If bit is set to one, power is provided to the socket ( $V_{CC} = 5V$  and  $V_{PP}1$  and  $V_{PP}2$  are set according to bits 3-0 in the power control register).

#### Bit 5: Ready/Busy

Indicates the ready condition of the PC Card. If bit is set to one, the PC Card is ready. If bit is zero the PC Card is busy.

#### Bit 4: Memory Write Protect

Bit value is the logic level of the **WP** signal on the memory PC Card interface. When bit is set to zero the PC Card is not write protected. When bit is set to one the PC Card is write protected, and the card enable signals to the PC Card are not enabled during a memory write cycle to common or attribute memory.

#### Bit 3: Card Detect 2

Together with card detect 1 indicates a card is present at the socket and fully seated. Bit is set to one if the CD2 signal on the PC Card interface is active. Bit is set to zero if the CD2 signal on the PC Card interface is inactive.

#### Bit 2: Card Detect 1

Together with card detect 2 indicates a card is present at the socket and fully seated. Bit is set to one if the  $\overline{\text{CD1}}$  signal on the PC Card interface is active. Bit is set to zero if the  $\overline{\text{CD1}}$  signal on the PC Card interface is inactive.

Bit 1 and Bit 0: Battery Voltage Detect 2 and 1

| BVD1 | BVD2 | Status       |

|------|------|--------------|

| 0    | 0    | Battery Dead |

| 0    | 1    | Battery Dead |

| 1    | 0    | Warning      |

| 1    | 1    | Battery Good |

For I/O PC Cards, bit 0 indicates the current status of the (STSCHG/RI) signal from the PC Card when the ring indicate enable bit in the Interrupt and General control register is set to zero.

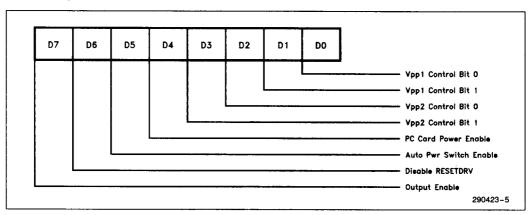

#### Power and RESETDRV Control Register (Read/Write)

Socket A: Index Value (Base + 02h) Socket B: Index Value (Base + 42h)

This register controls the PC Card power and resetting of the PCIC registers. A **RESETDRV** clears all bits in this register, unless the **RESETDRV** is a result of a Intel386 SL CPU resume (PWRGOOD = 1) and the disable resume RESETDRV bit is set to one. Output Enable should not be set until the register has been previously written setting PC Card Power Enable.

Bit 7: Output Enable

If this bit is set to zero, the PC Card outputs listed below are tri-stated and the ENABLE pin to the corresponding socket is inactive.

CADR < 25:12 > , CE1, CE2, IORD, IOWR, OE, REG, RESET, WE

Refer to the Slot Power Control Table for the functionality of the Output Enable bit.

Bit 6: Disable Resume RESETDRV

If bit is set to one and the **RESETDRV** is a result of a Intel386 SL CPU resume (PWRGOOD = 1), the resetable registers of the PCIC will remain intact and will not be reset. If bit is set to zero and the **RESETDRV** is a result of a Intel386 SL CPU resume, the resetable registers of the PCIC will be reset. If the **RESETDRV** is a result of a system reset, the resetable registers of the PCIC will be reset regardless of the setting of bit.

Bit 5: Auto Power Switch Enable

If bit is set to zero, automatic socket power switching based on card detects is disabled. If bit is set to one, automatic socket power switching based on card detects is enabled.

Bit 4: PC Card Power Enable

If bit is set to zero, all power to the PC Card is disabled ( $V_{CC}$ ,  $V_{PP}1$  and  $V_{PP}2$  = no connect). When bit is set to one,  $V_{CC}$  = 5V and  $V_{PP}1$  and  $V_{PP}2$  are set according to bit 3 through bit 0 in this register.

Bit 3 and Bit 2: PC Card Vpp2 Power Control

#### NOTE:

The 11 combination is reserved and should not be used, but if these bits are set to 11 then V<sub>PP</sub>2 will be a no connect.

Bit 1 and Bit 0: PC Card VPP1 Power Control

#### NOTE:

The 11 combination is reserved and should not be used, but if these bits are set to 11 then V<sub>PP</sub>1 will be a no connect.

#### **Power Control**

The PCIC provides each socket with 5 power control pins.

| Ctrl Bit | Name                  | Description                          |

|----------|-----------------------|--------------------------------------|

| 0        | V <sub>PP</sub> 1_EN0 | V <sub>PP</sub> 1 control pin, bit 0 |

| 1        | V <sub>PP</sub> 1EN1  | V <sub>PP</sub> 1 control pin, bit 1 |

| 2        | V <sub>PP</sub> 2EN0  | V <sub>PP</sub> 2 control pin, bit 0 |

| 3        | V <sub>PP</sub> 2_EN1 | Vpp2 control pin, bit 1              |

| 4        | V <sub>CC</sub> _EN   | Master enable pin                    |

| Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | V <sub>CC</sub> _EN | V <sub>PP</sub> x_EN1 | V <sub>PP</sub> x_EN0 |

|-------|-------|-------|-------|-------|---------------------|-----------------------|-----------------------|

| 1     | 0     | 0     | 0     | 0     | 0                   | 0                     | 0                     |

| 1     | 0     | 1     | 0     | 1     | 0                   | 0                     | 1                     |

| 1     | 1     | 0     | 1     | 0     | 0                   | 1                     | 0                     |

| 1     | 1     | 1     | _ 1   | 1     | 0                   | 0                     | 0                     |

| 0     | Х     | Х     | Х     | Х     | 1                   | 0                     | 0                     |

| 0     | Х     | Х     | Х     | Х     | 1                   | 0                     | 0                     |

| 0     | Х     | X     | Χ     | Х     | 1                   | 0                     | 0                     |

| 0     | X     | Х     | Х     | Х     | 1                   | 0                     | 0                     |

These pins allow the designer to control two unique voltage levels to each socket VPP pin.

A PC card is considered detected when:  $\overline{CD2} = 0$  and  $\overline{CD1} = 0$ .

The PC Card Active Power bit of the Interface Status Register indicates the current power status of the socket. If bit is set to zero, power to the socket is turned off ( $\overline{V_{CC}}$ \_EN,  $\overline{V_{PP}1}$ \_EN0,  $\overline{V_{PP}1}$ \_EN1,  $\overline{V_{PP}2}$ \_EN0, and  $\overline{V_{PP}2}$ \_EN1 are all inactive). If this bit is set to one, power is provided to the socket ( $\overline{V_{CC}}$ \_EN = 0V and  $\overline{V_{PP}1}$  and  $\overline{V_{PP}2}$  are set according to bits 3-0 in the power control register).

The following table describes the slot power control function.

| Po     | wer Cntrl F             | Reg                       | PC ( | Card |           | IF Stat                    |

|--------|-------------------------|---------------------------|------|------|-----------|----------------------------|

|        | PC                      | Auto                      | Pi   | ns   | Tri-state | Reg                        |

| Output | Card<br>Power<br>Enable | Power<br>Switch<br>Enable | CD1  | CD2  | Outputs   | PC Card<br>Power<br>Active |

| X      | 0                       | X                         | Х    | Х    | OFF       | 0                          |

| 0      | 1                       | 0                         | 0    | 0    | OFF       | 1                          |

| 1      | 1                       | 0                         | 0    | 0    | ON        | 1                          |

| X      | 1                       | 0                         | Х    | 1    | OFF       | 1                          |

| Х      | 1                       | 0                         | 1    | Х    | OFF       | 1                          |

| 0      | 1                       | 1                         | 0    | 0    | OFF       | 1                          |

| 1      | 1                       | 1                         | 0    | 0    | ON        | 1                          |

| Х      | 1                       | 1                         | Х    | 1    | OFF       | 0                          |

| Х      | 1                       | 1                         | 1    | Х    | OFF       | 0                          |

NOTE:

PC Card Power Active = 0 → V<sub>CC</sub>, V<sub>PP</sub>1, and V<sub>PP</sub>2 are no connects

The power control register also contains control bits in which to independently and separately select 5V, 12V, or no connect for Vpp1 and Vpp2.

The power control circuitry only switches the applicable voltages and does not provide voltage generation.

It is recommmended that on all designs using the PCIC, a 1 Amp 125V fuse be installed on each PCMCIA socket voltage line to comply IEC 950 and UL 1950.

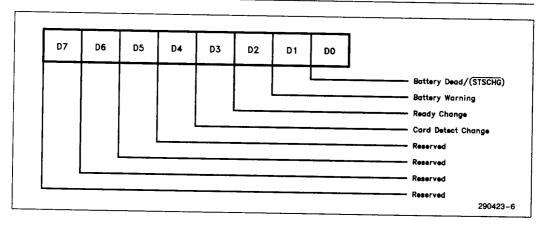

#### Card Status Change Register (Read Only)

Socket A: Index Value (Base + 04h) Socket B: Index Value (Base + 44h)

The Card Status Change Register contains the status for sources of the card status change interrupt. These sources can be enabled to generate a card status change interrupt by setting the corresponding bit in the card status change interrupt configuration register. Reading the Card Status Change Register causes the register bits to be reset to zero.

If the card status change interrupt is enabled to one of the system bus interrupt request lines, the corresponding IRQ signal remains active high until this register is read.

#### NOTE:

Bit descriptions in parenthesis indicate valid signals after the interface is configured for I/O PC Cards.

Bit 7 thru Bit 4: Reserved

These reserved bits always read zero.

Bit 3: Card Detect Change

Bit is set to one when a change has been detected on either the CD1 or CD2 signals.

Bit 2: Ready Change

Bit is set to one when a low to high has been detected on the **Ready/Busy** signal indicating that the memory PC Card is ready to accept a new data transfer. Bit reads zero for I/O PC Cards.

Bit 1: Battery Warning

Bit is set to one when a battery warning condition has been detected. Bit reads zero for I/O PC Cards.

Bit 0: Battery Dead (STSCHG)

For memory PC Cards, bit is set to one when a battery dead condition has been detected.

For I/O PC Cards, bit is set to one if ring indicate enable bit in the interrupt and general control register is set to zero and the (STSCHG/RI) signal from the I/O PC Card has been pulled low. The system software then has to read the status change register in the PC Card to determine the cause of the status change signal (STSCHG). This bit reads zero for I/O PC Cards if the ring indicate enable bit in the interrupt and general control register is set to one.

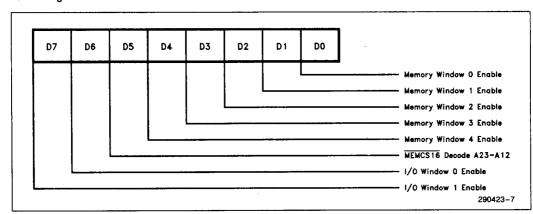

### Address Window Enable Register (Read/Write)

Socket A: Index Value (Base + 06h) Socket B: Index Value (Base + 46h)

This register controls the enabling of the memory and I/O mapping windows to the PC Card memory or I/O space. **RESETDRV** clears all bits in this register, unless the **RESETDRV** is a result of a Intel386 SL CPU resume (PWRGOOD = 1) and the disable resume RESETDRV bit is set to one in the power and RESETDRV control register.

#### Bit 7: I/O Window 1 Enable

If bit is set to zero, an I/O access within the I/O address 1 window will inhibit the card enable signals to the PC Card. If bit is set to one, an I/O access within the I/O address 1 window will generate the card enables to the PC Card. I/O accesses pass addresses from the system bus directly through to the PC Card. The start and stop register pairs must all be set to the desired window values before setting bit to one.

#### Bit 6: I/O Window 0 Enable

If bit is set to zero, an I/O access within the I/O address 0 window will inhibit the card enable signals to the PC Card. If bit is set to one, an I/O access within the I/O address 0 window will generate the card enables to the PC Card. I/O accesses pass addresses from the system bus directly through to the PC Card. The start and stop register pairs must all be set to the desired window values before setting bit to one.

#### Bit 5: MEMCS16 Decode A23-A12

If this bit is set to zero, **MEMCS16** is generated from a decode of the system (ISA) address lines **A23–A17** only. This means that at a minimum, a 128K block of system (ISA) memory address space is set aside as 16-bit memory only. If this bit is set to a one, **MEMCS16** is generated from decode of the system (ISA address lines **A23–A12**).

When decoding in the first 128K block of address space, full line address decode should be used.

#### Bit 4: Memory Window 4 Enable