SEL 840

GENERAL PURPOSE

DIGITAL COMPUTER

| tec | hnica      | al pr | oposa |

|-----|------------|-------|-------|

|     | 1 11 11 00 | 3, P, | 0000  |

| SEL | Technical Proposal | S |

|-----|--------------------|---|

|     | Date               |   |

SEL 840

GENERAL PURPOSE

DIGITAL COMPUTER

REV 2-17-66

## TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                                                                                                                                                                                                                                |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2.0 | SEL 840 GENERAL PURPOSE COMPUTER                                                                                                                                                                                                                            |  |  |  |  |

|     | 2.1 SEL 840 Computer - Basic Hardware Configuration                                                                                                                                                                                                         |  |  |  |  |

|     | 2.1.1 SEL 840 Specifications 2.1.2 Input/Output Configurations 2.1.3 SEL 800 Series Peripheral Equipment 2.1.4 SEL 840 Control Console 2.1.5 SEL 840 Programming Characteristics 2.1.6 SEL 840 Software System 2.1.7 System Logic 2.1.8 System Construction |  |  |  |  |

| 3.0 | FIELD MAINTENANCE PROVISIONS                                                                                                                                                                                                                                |  |  |  |  |

| 4.0 | TRAINING                                                                                                                                                                                                                                                    |  |  |  |  |

| 5.0 | INSTALLATION                                                                                                                                                                                                                                                |  |  |  |  |

| 6.0 | ACCEPTANCE TESTING                                                                                                                                                                                                                                          |  |  |  |  |

| 7.0 | DOCUMENTATION                                                                                                                                                                                                                                               |  |  |  |  |

|     | 7.1 Drawings 7.2 Technical Manuals 7.3 Reports                                                                                                                                                                                                              |  |  |  |  |

| 8.0 | MANAGEMENT                                                                                                                                                                                                                                                  |  |  |  |  |

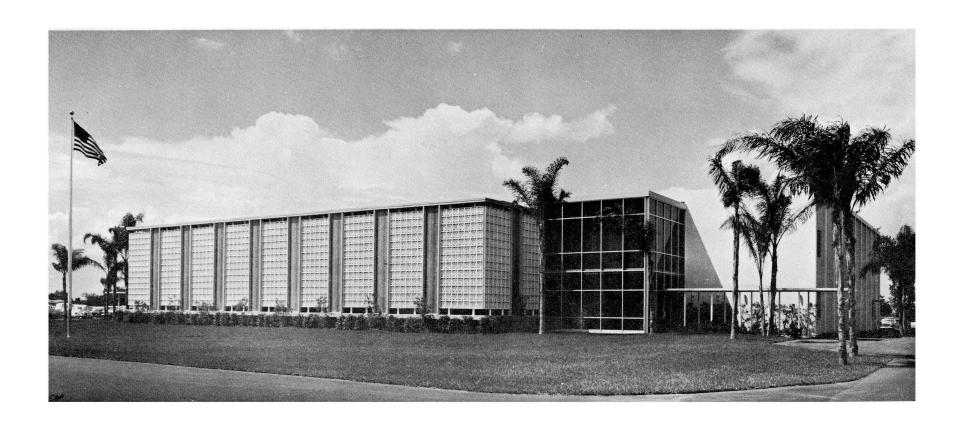

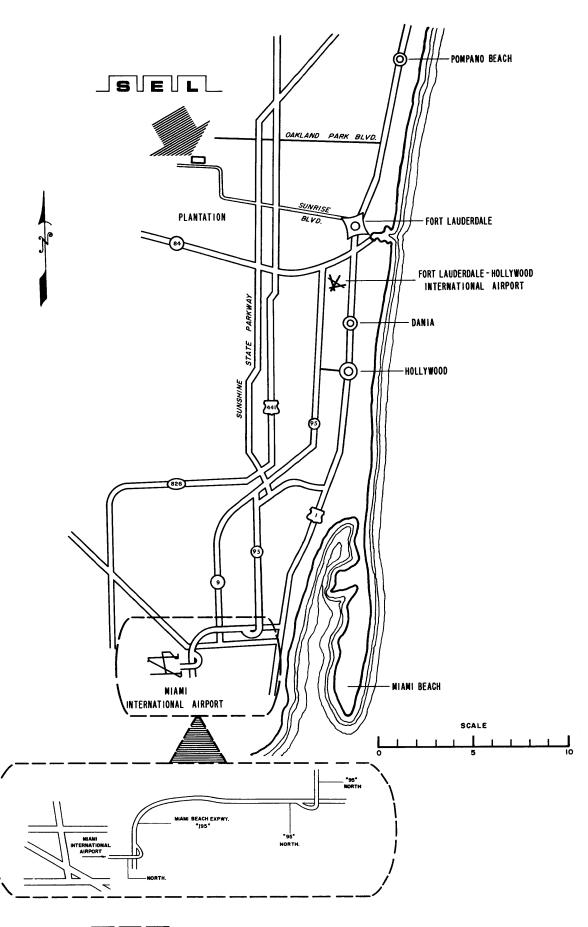

| 9.0 | FACILITIES                                                                                                                                                                                                                                                  |  |  |  |  |

|     | APPENDIX                                                                                                                                                                                                                                                    |  |  |  |  |

Systems Engineering Laboratories, Incorporated (SEL) is pleased to submit our Technical Proposal for an 840 Scientific Digital Computer.

SEL specializes in the design, development and fabrication of general-purpose digital data acquisition, processing and control systems and system components. Our firm has designed and fabricated numerous special-purpose wired program and stored program data processing systems. Application bulletins describing several of these are enclosed in the Appendix. Recently, SEL introduced a new series of high-speed integrated circuit general-purpose digital computers. These are designated as the SEL 810 and 840.

We propose the SEL 840 for your requirement, which is a high-speed general-purpose 24-bit binary computer. The single address instruction words utilize a 1.75 microsecond memory cycle time and parallel transfers to accomplish most of the 68 different instructions within 3.5 microseconds.

This computer is well suited for use as a real time data processor, or as an off-line scientific or business computer. A FORTRAN IV compiler satisfying the latest ASA standards is available with the 840 provided the machine is ordered with 8K of memory (see Figure 1.0).

The SEL 840 is the most outstanding machine in its price range as shown by the following list of significant advantages:

1. All digital logic, silicon monolithic integrated circuits.

FIGURE 1.0

- 2. Hardware index register in basic system. No extra time required to index. (One index is standard in basic system; two additional index registers are available as options.)

- 3. All hardware required for two separate Input/Output channels in basic system.

- 4. Hardware multiply/divide is in the basic system.

- 5. Hardware instructions that allow Input/Output directly from core or via accumulator.

- 6. Six hundred nanosecond access time, 1.75 microseconds full cycle time.

- 7. Ninety instructions. (68 for Basic System, 22 for Extended Arithmetic Unit.)

- 8. Memory is expandable to 32,768 words, all directly addressable.

SEL is known throughout the industry as a true "systems" company. We produce all of the major components of any digital data system with the exception of the tape transports. SEL, however, produces the electronics for the transports. The following is a list of the system components manufactured by SEL. These are described in the Appendix of this proposal.

Analog-to-Digital Converters

Digital-to-Analog Converters

Low-Level Multiplexers

High Level Multiplexers

Magnetic Core Memories

Wide Band D. C. Instrumentation Amplifiers

We have established Regional Sales Offices in Washington,

Operational Amplifiers

Digital Logic Modules

Micrologic Modules

dresses and telephone number are as follows:

D. C., Philadelphia, Boston and Los Angeles. The Area Managers in charge of these offices are qualified systems engineers who are always available to provide you with assistance. The names of these Area Managers, along with their ad-

Mr. George J. Burke Area Manager 10400 Connecticut Avenue Kensington, Maryland 27095 301-946-7100 Mr. James H Geers Area Manager 885 N. San Antonio Road Los Altos, California 94023 415-941-1185

Mr. Marvin L. Bunn Area Manager P. O. Box 1141 Huntsville, Alabama 35812 205-539-2181

Mr. William A. Gannon Area Manager P. O. Box 672 Framingham, Massachusetts 01701 617-879-0080

Mr. Karl R. Grice Area Manager 637 North Park Avenue Pomona, California 91767 714-623-5235

The performance and reliability of SEL systems may be verified by calling any of the contacts listed in the contracts completed and in the

progress document at the end of this section. This is a list of all SEL contracts, with the computer contracts listed on a separate page. We urge you to call these customers and verify the accuracy, performance and other characters of our products.

### SEL CONTRACTS COMPLETED

| Contract No.                         | Description ,                                                       | Customer                                                                | Technical<br>Contact                  | Administrative<br>Contact             | Approximate  Dollars |

|--------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------|

| N62269-1453                          | Two Analog-to-<br>Digital Converters                                | Naval Air Development<br>Center, Johnsville, Pa.                        | H. Tremblay<br>OS 5-7000              | R. Harmon<br>OS 5-7000                | \$ 15,000            |

| DA44-177-<br>TC-760                  | Two Digital Data<br>Acquisition Systems                             | U.S. Army Transporta-<br>tion Research Command<br>Fort Eustis, Virginia | W. M. Allen<br>TR 7-1311              | T. Domino<br>TR 7-1131                | 80,000               |

| BGP-458<br>(Now61-0647-U)            | 24-Channel Data<br>Acquisition System                               | Hercules Powder Co.<br>Magna, Utah                                      | R. Wright<br>OL 6-9811                | R. Sawyer<br>BY 7-5911                | 308,000              |

| 62-4-DESCS<br>(AF40(600)800)         | Data Translation<br>System                                          | ARO, Inc. Arnold Air<br>Force Station, Tenn.                            | G. Sheraden<br>GL 5-2611              | J. Gary<br>GL 5-2611                  | 152,000              |

| 61-07970                             | Two Data Acquisition<br>Systems                                     | Thiokol Chemical Corp.<br>Brigham City, Utah                            | D. Sherar<br>AL 7-7111                | C.R. Turner<br>PA 3-3481              | 49,000               |

| 2-300067-7025                        | Three Digital<br>Function Generators                                | Boeing Co., Aerospace<br>Div., Seattle, Wash.                           | W. Munday<br>CH 3-4222                | R. Danell<br>MA 3-7025                | 32,700               |

| RS-79248                             | Digital Data<br>Acquisition System                                  | Thiokol Redstone Div.<br>Huntsville, Alabama                            | J. Epps<br>876-9509                   | C. Duke<br>876-9475                   | 65,000               |

| Nonr3717(00)(X)                      | Digital Data Recording<br>System & Card Tester                      | Naval Research Laboratory, Washington, D.C.                             | A. M. Knopp<br>JO 3-6600              | J. Somers (ONR)<br>OX 6-2266          | 108,000              |

| FSC 5820<br>(AF08(606)52 <b>2</b> 9) | PCM Conversion<br>System                                            | USAF Missile Test Ctr.<br>Patrick A. F. L., Fla.                        | E. Herrberger<br>UL 7-2661            | H.A. Brown<br>UL 7-6920               | 56,000               |

| N62306-1064                          | Airborne Data Re-<br>cording System                                 | Navy Oceanographic Office, Washington D.C.                              | W. Geddes<br>RE 6-2700                | Mrs. H. Bright<br>RE 6-2700           | 35,000               |

| LW-04073-1                           | Low Level Multiplexers<br>for ROVER Program                         | Los Alamos Scientific<br>Lab, Los Alamos, N.M.                          | D. Stephenson<br>7-5255               | J.P. Harrison<br>7-4147               | 105,000              |

| 0216-0001-TK                         | Digital Data Acquisition<br>System                                  | Thiokol Chemical Co.<br>Elkton, Maryland                                | D. Williamson<br>EX 8-3000            | T.A. King<br>EX 8-3000                | 100,000              |

| NAS 8-4609                           | High Speed Data<br>Acquisition System                               | NASA Marshall SFC<br>Huntsville, Alabama                                | J. Lucas<br>877-2152                  | W.L. Troupe<br>534-1678               | 94,500               |

| NAS 3-2627                           | L-L Multiplexer & A/D Converter                                     | NASA Lewis Res. Ctr.<br>Cleveland, Ohio                                 | R. Crowl<br>252-7700<br>Ext. 385      | J. Cash<br>252-7700                   | 27,000               |

| 97-6-X-78035                         | SEL Model ADC-1B<br>A/D Converter                                   | Westinghouse Elec. Corp.<br>Pittsburgh, Penna.                          | James Belz<br>CH 2-1500               | R. Endean<br>391-2800                 | 7,500                |

| NAS 8-5032                           | Digital Data<br>Acquisition System                                  | NASA Marshall SFC<br>Huntsville, Alabama                                | R. Brouns<br>876-1403                 | L. Wilkins<br>534-1678                | 80,000               |

| NAS 5-2706                           | SEL A/D Converter<br>& L-L Multiplexer                              | NASA Goddard SFC<br>Hyattsville, Maryland                               | W. Stallings<br>474-9000<br>Ext. 4459 | L. Purschwitz<br>982-4161             | 16,000               |

| PO62-04973                           | High Level Data<br>Acquisition System                               | Thiokol, Wasatch Div.<br>Brigham City, Utah                             | D. Sherar<br>AL 7-7111                | C.R. Turner<br>PA 3-3481              | 34,000               |

| AM3-211528                           | One SEL Low-Level<br>Multiplexer                                    | Jet Propulsion Laboratory<br>Pasadena, Calif.                           | R. Purves<br>790-6811                 | W.A. Frohn<br>790-6811                | 16,000               |

| SC 168334                            | Digital Data Processor<br>Set for POLARIS and<br>Satellite Programs | Applied Physics Lab The John Hopkins Univ. Silver Spring, Maryland      | A. Town<br>776-7100<br>Ext. 2243      | C. H. Walters<br>JU 97700<br>Ext. 785 | 340,000              |

| NAS 1-1770                           | Aralog-to-Digital<br>Transcriber                                    | NASA Langley Res. Ctr.<br>Hampton, Virginia                             | L. Taylor<br>722-7961                 | J. Stowers<br>722-7961                | 216,000              |

| Contract No. | Description                                    | Customer                                                              | Technical<br>Contact                                              | Administrative<br>Contact                | Approximate<br>Dollars |

|--------------|------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|------------------------|

| NAS 1-1900   | High Speed Digital<br>Data Recording<br>System | NASA Langley Research<br>Center, Langley Station<br>Hampton, Virginia | C. Russell<br>722-7961<br>Ext. 4616                               | W. Simmons<br>722-7961<br>Ext. 3303      | 200,000                |

| NAS 1-2088   | H.S. Digital Data<br>Recording System          | NASA Langley Research<br>Center, Langley Station<br>Hampton, Virginia | C. Russell<br>722-7961<br>Ext. 4616                               | J. Munick<br>722-7961<br>Ext. 2024       | 140,000                |

| NAS 8-7000   | Direct Computer<br>Entry System                | NASA Marshall Space<br>Flight Center<br>Huntsville, Alabama           | Frank Hay<br>877-2151                                             | W.C. Vaughn<br>534-6404                  | 60,000                 |

| PO 167191    | Low Level Data<br>Acquisition System           | Pratt & Whitney Aircraft<br>W. Palm Beach, Florida                    | Wm. Missimer<br>VI 4-7311<br>Ext. 8383                            | F. D. Burk<br>VI 4-7311<br>Ext. 2332     | 160,000                |

| NAS 8-7018   | 150 Operational<br>Amplifiers                  | NASA Marshall Space<br>Flight Center<br>Huntsville, Alabama           | Gene Lee<br>877-2151                                              | W. C. Vaughn<br>534-6404                 | 57,000                 |

| PO 6-803590  | 300-Channel Low Level<br>Data Acqsn. System    | Allison Division, GMC<br>Indianapolis, Indiana                        | Karl Wacker<br>CH 4-1511                                          | F. C. Cassell<br>CH 4-1511               | 160,000                |

| PO976X5102   | 5 Analog-to-Digital<br>Converters              | Westinghouse Electric<br>Pittsburgh, Penna.                           | James Belz<br>CH 2-1500                                           | R. J. Endean<br>391-2800                 | 30,700                 |

| PO 47511     | Data Acquisition<br>System                     | University of Florida<br>Gainesville, Fla.                            | Dr. R. Uhrig<br>FR 6-3261<br>Ext. 2271                            | T.N. Wells<br>FR 6-3261                  | 36,000                 |

| NAS 8-4496   | Two Data<br>Acquisition Systems                | NASA Marshall SFC<br>Huntsville, Alabama                              | W. Baker<br>876-3794                                              | <b>G</b> .Troupe 534-1678                | 230,000                |

| 97-6-X-85555 | One A/D Converter (less register)              | Westinghouse Electric<br>Pittsburgh, Penna.                           | James Belz<br>CH 2-1500                                           | R. J. Endean<br>391-2800                 | 7,000                  |

| 97-6-X-91415 | Five A/D<br>Converters                         | Westinghouse Electric<br>Pittsburgh, Penna.                           | James Belz<br>CH 2-1500                                           | R. J. Endean<br>291-2800                 | 31,000                 |

| NAS 8-5100   | Telemetry Ground Station Digitzg. Sys.         | NASA Marshall SFC<br>Huntsville, Alabama                              | J. Eichelberger<br>876-7910                                       | W. L. Troupe<br>534-7315                 | 70,000                 |

| NAS 8-7062   | High Density Tape<br>Error Checker             | NASA Marshall SFC<br>Huntsville, Alabama                              | J. Lucas<br>877-2152                                              | W. Troupe 534-7315                       | 14,000                 |

| NAS 3-2977   | Format Control Unit & Integration of Units     | NASA Lewis Res. Ctr.<br>Cleveland, Ohio                               | C. Mealey<br>216-252-7700<br>Ext. 353                             | P. Pirko<br>216-252-7700<br>Ext. 532     | 29,500                 |

| NAS 3-3151   | One Multiplexer<br>Three D/A Converters        | NASA Lewis Res. Ctr.<br>Cleveland, Ohio                               | <ul><li>C. Mealey</li><li>216-252-7700</li><li>Ext. 353</li></ul> | P. Pirko<br>216-252-7700<br>Ext. 532     | 23,000                 |

| PO 3X-14304  | One Coder and One High<br>Level Multiplexer    | ARO, Inc.<br>Tullahoma, Tenn.                                         | W. R. Prater<br>615-GL 5-2611<br>Ext. 584                         | C. Solomon<br>615-GL 5-2611<br>Ext. 7113 | 16,000                 |

| NAS 8-8043   | Digital Data Acqsn.<br>System                  | NASA, Marshall Space<br>Flight Center<br>Huntsville, Alabama          | J. Heaman<br>205-876-7227                                         | W. L. Troupe<br>534-7315                 | 58,300                 |

| PO 370391    | 48-Channel Digital<br>Data Acqsn. System       | Marquardt Corporation<br>Van Nuys, California                         | G. B. Kubicek<br>ST 1-2121<br>Ext. 1281                           | J. Nugent<br>ST 1-2121<br>Ext. 1553      | 78,000                 |

| NAS 10-780   | Analog High Level<br>Multiplexer               | NASA, Cape LOC<br>Cocoa Beach, Florida                                | R. Bivans<br>UL 3-3362                                            | Mr. Mazzanoble<br>783-7709               | 12,000                 |

| Contract No.                    | Description                                                        | Customer                                                                | Technical<br>Contact                        | Administrative<br>Contact                                      | Approximate Dollars |

|---------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------|---------------------|

| NAS 3-4653                      | Tape Search Unit                                                   | NASA, Lewis Res. Ctr.<br>Cleveland, Ohio                                | R. Crowl<br>216-252-7700<br>Ext. 225        | P. Pirko<br>216-252-7700<br>Ext. 532                           | \$ 7,400            |

| SC63-34-RTF-T                   | Low-Level Data<br>Acquisition System                               | ARO, Inc.<br>Tullahoma, Tenn.                                           | J. D. Freeman<br>615-GL 5-2611              | C. Solomon<br>615-GL 5-2611                                    | 111,000             |

| NAS 8-7394                      | Data Acquisition<br>System                                         | NASA, Marshall Space<br>Flight Center<br>Huntsville, Alabama            | B. Henson<br>877-2590                       | M.W. Moore                                                     | 130,000             |

| NAS 8-5461                      | Digital Tape Writing<br>Station                                    | NASA, Marshall Space<br>Flight Center<br>Huntsville, Alabama            | R. Eichelberger<br>205-876-5275             | J. Sanford<br>205-539-4233                                     | 45,000              |

| PO 63-03987<br>(AF33(600)34468) | Tape to Tape<br>Translator                                         | Thiokol Chem. Corp.<br>Wasatch Division<br>Brigham City, Utah           | Gene Davis<br>801-863-3511                  | L. B. Pyper<br>801-863-3511<br>Ext. 63287                      | 112,000             |

| NAS 9-1845                      | Two Low-Level Data<br>Acquisition Systems                          | NASA, Manned Space-<br>craft Center<br>Houston, Texas                   | J. Lowery<br>713-928-2811<br>Ext. 2565      | J. Stroup<br>713-928-2811<br>Ext. 3611                         | 195,000             |

| PON-691504D                     | Low-Level Data<br>Acquisition System                               | Martin Company<br>Orlando, Florida                                      | B. Wigle<br>305-855-6100<br>Ext. 2396       | J.T. Brady<br>305-855-6100<br>Ext. 2265                        | 70,000              |

| M3J7XA-700,007                  | 800-Channel Data<br>Acquisition and<br>Processing System           | North American Avia.<br>Downey, California                              | D. E. Herbst<br>213-923-8141<br>Ext. 6161   | S. Ramage<br>213-639-7870<br>Ext. 1635<br>(Montebello, Calif.) | 800,000             |

| PO SB 0387                      | 100-Channel Data<br>Acquisition System                             | Thiokol Chemical Corp.<br>Space Booster Plant<br>Brunswick, Georgia     | E. L. Checketts<br>912-265-0180<br>Ext. 315 | Douglas Bell<br>912-265-0180<br>Ext. 378                       | 275,000             |

| NAS 9-2189                      | Portable Low-Level<br>Data Acquisition<br>System                   | NASA Manned Space-<br>craft Center<br>Houston, Texas                    | R. J. Sachen<br>713-928-2811<br>Ext. 2475   | R. P. Clyatt<br>713-928-2811<br>Ext. 7311                      | 105,000             |

| PO 72511                        | Compressor Data<br>Acquisition System                              | Texas Gas Trans.Corp.<br>Owensboro, Kentucky                            | C. McCulley<br>502 -MU 3-2431               | P. Fedde<br>502-MU 3-2421<br>Ext. 452                          | 19,000              |

| PO 470518                       | 96-Channel Digital<br>Data Recording System                        | Marquart Corporation<br>Van Nuys, California                            | M. Feffer<br>781-2121<br>Ext. 1217          | J. Nugent<br>781-2121<br>Ext. 1217                             | 75,000              |

| NAS 8-8864                      | 150 Operational<br>Amplifiers                                      | NASA Marshall Space<br>Flight Center,<br>Huntsville, Alabama            | Gene Lee<br>205-877-2151                    | W. L. Troupe<br>205-534-4586                                   | 57,000              |

| PO 34X6853                      | 10 Analog-to-Digital<br>Converters with SEL<br>Amplifiers Included | Westinghouse Electric<br>Pittsburgh, Penna.                             | J. McCann<br>412-242-1500<br>Ext. 7628      | R. J. Endean<br>412-391-2800<br>Ext. 7471                      | 65,000              |

| NAS 8-8179                      | Telemetry Data<br>Analysis Equipment                               | NASA Marshall Space<br>Flight Center,<br>Huntsville, Alabama            | R. Eichelberger<br>205-876-5275             | W. L. Troupe<br>205-534-7315                                   | 330,000             |

| NAS 1-4272                      | System Verifier                                                    | NASA Langley Research<br>Center, Langley Station<br>Hampton, Virginia   | C. Russell<br>722-7961<br>Ext. 4616         | W.E. Hutcheson<br>703-722-7961                                 | 19,000              |

| PH 108-64-14 (P)                | MOBIDAC 1                                                          | U.S. Public Health Ser.<br>Bureau of State Services<br>Washington, D.C. | Dr. B.H. Fox<br>202-962-8092                | Miss M. Porter<br>202-962-8092                                 | 18,000              |

|                      | 4.5                                                                | (Continued)                                                      |                                         |                                           |                        |

|----------------------|--------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------|-------------------------------------------|------------------------|

| Contract No.         | Description                                                        | Customer                                                         | Technical<br>Contact                    | Administrative<br>Contract                | Approximate<br>Dollars |

| NAS 3-5195           | 400 Channel and 200<br>Channel Facility Sub-<br>Systems            | NASA - Lewis Res. Ctr.<br>Cleveland, Ohio                        | C. Mealey<br>216-252-7700<br>Ext. 353   | M. Kapral<br>216-252-7700<br>Ext. 550     | \$280,000              |

| N62306-1473          | Modification & Expansion of Airborne Digital Data Recording System | U.S. Naval Oceanograph, Washington, D.C.                         | F. Dorsey<br>RE 6-2700<br>Ext. 543      | H. Crain<br>RE 6-2700                     | 20,000                 |

| NAS 8-12259          | 130 Operational<br>Amplifiers                                      | NASA - Marshall Space<br>Flight Center, Huntsville<br>Alabama    | J. Lewis<br>205-876-7233                | P. Clancy<br>205-876-7233                 | 50,000                 |

| NAS 3-3735           | Two Digital Data<br>Logging Systems                                | NASA - Lewis Res. Ctr.<br>Cleveland, Ohio                        | C. Mealey<br>216-252-7700<br>Ext. 353   | M. Kapral<br>216-252-7700<br>Ext. 550     | 610,000                |

| NAS 3-4514           | Two Multiplexers                                                   | NASA - Lewis Res. Ctr.<br>Cleveland, Ohio                        | R. Crowl<br>216-252-7700<br>Ext. 225    | M. Kapral<br>216-252-7700<br>Ext. 550     | 23,000                 |

| NAS 1-3506           | High Speed Digital<br>Recording System                             | NASA - Langley Res. Ctr.<br>Langley Station<br>Hampton, Virginia | C. Russell<br>703-722-7961<br>Ext. 4616 | J. Munick<br>703-722-7961<br>Ext. 2024    | 170,000                |

| L-011298-7030        | Four Telemetry Digitizing Systems                                  | Boeing Aerospace<br>Division, Huntsville<br>Alabama              | R. Anfield<br>205-536-4461              | W.G. Dooley<br>205-536-4461               | 260,000                |

| NAS 8-12645          | l Digital Tape<br>Playback System                                  | NASA - Marshall Space<br>Flight Center<br>Huntsville, Alabama    | F. Hay<br>205-877-2151                  | W. L. Troupe<br>205-534-4586              | 15,000                 |

| NAS 3-6145-PE        | 5-Channels of Digital-<br>to-Analog Converters                     | NASA - Plum Brook<br>Station, Sandusky, Ohio                     | R. Reust<br>419-625-1123<br>Ext. 434    | R. J. Koch<br>216-433-4000                | 10,000                 |

| PO 34-X-8676         | 5 Analog-to-Digital<br>Converters                                  | Westinghouse Electric<br>Corporation<br>Pittsburgh, Pa.          | J. McCann<br>412-242-1500<br>Ext. 7628  | R. J. Endean<br>412-391-2800<br>Ext. 7471 | 33,000                 |

| PO 504-477           | 3 14-Channel Consoles<br>Hydrostatic Data<br>Acquisition Systems   | Sundstrand Hydrostatic<br>Rockford, Illinois                     | C. J. Ricketts<br>815-962-4477          | A. K. Nuckles<br>815-962-4477             | 45,000                 |

| PO 34-X-5782         | 2 Analog-to-Digital<br>Converters without<br>Amplifiers            | Westinghouse Electric<br>Corporation<br>Pittsburgh, Pa.          | J. McCann<br>412-242-1500<br>Ext. 7628  | R. J. Endean<br>412-391-2800<br>Ext. 7471 | 12,000                 |

| NAS 8-12991          | Digital-to-Analog<br>Conversion System                             | NASA - Marshall Space<br>Flight Center<br>Huntsville, Alabama    | B. Broad<br>205-876-6344                | J. Grosser<br>205-539-2410                | 31,000                 |

| DA04353 ENG-<br>9009 | High Speed Digital<br>Data Acquisition<br>System                   | F & M Systems Company<br>Dallas, Texas                           | W. T. Russell<br>214-428-1573           | K. Bishop<br>214-428-1573                 | 73,000                 |

| NAS 8-11702          | Telemetry Digitizing<br>System                                     | Lockheed Aircraft Service<br>Company<br>Ontario, California      | E. Young 714-984-1234                   | F. Tade<br>714-984-1234                   | 55,000                 |

| PO L-24959-<br>6010  | 2 SEL Model 2051-SIM<br>Systems                                    | The Boeing Company<br>New Orleans, La.                           | Mr. Ushakoff<br>504-255-3311            | H. Reardon<br>504-255-8134                | 1,700                  |

| NO w 61-0647-u       | Auxillary Control Pane                                             | l Hercules Powder Co.<br>Magna, Utah                             | D. Carroll<br>801-297-5911              | R. W. Wright<br>801-297-5911              | 1,300                  |

| Contract No.         | Description                                                      | Customer                                                                      | Technical<br>Contact                          | Administrative<br>Contact                                             | Approximate Dollars |

|----------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------|---------------------|

| PO 240674            | MOBIDAC III                                                      | Pratt and Whitney<br>West Palm Beach, Fla.                                    | W. Missimer<br>844-7311<br>Ext. 8383          | C. R. Brooks (144)<br>844-7311<br>Ext. 2426                           | \$50,000            |

| NAS 8-13906          | Precision Oscillator                                             | NASA Marshall Space<br>Flight Center<br>Huntsville, Alabama                   | G. Lee<br>205-877-2151                        | D. McCreless<br>205-534-6405                                          | 34,000              |

| NAS 8-11654          | Telemetry Digitizing<br>System                                   | NASA Marshall Space<br>Flight Center<br>Huntsville, Alabama                   | J. Rees<br>205-876-6445                       | D. D. Firestone<br>205-539-2795                                       | 80,000              |

| AT(29-1)-1183        | 537-Channel Digital<br>Data System                               | Edgerton, Germeshausen<br>and Grier, Incorporated<br>Boston 15, Massachusetts | K. Foster<br>617-271-5131<br>(Bedford, Mass.) | H. R. Silver<br>617-267-9700<br>Boston, Mass.                         | 421,000             |

| NAS 8-12646          | Airborne Link Data<br>Simulator                                  | NASA - Marshall Space<br>Flight Center<br>Huntsville, Alabama                 | F. Hay<br>205-877-2151                        | W. L. Troupe<br>205-534-4586                                          | 50,000              |

| NAS 9-3071           | High Speed Analog-to-<br>Digital Data<br>Acquisition System      | NASA Manned Spacecraft<br>Center, Houston, Texas                              | M. Oberschmidt<br>713-483-7678                | S. R. Nevin<br>713-928-2811                                           | 130,000             |

| AF 04(611)-<br>10221 | 3 Digital Data Recordin<br>Systems and 2 Patch-<br>board Systems | ag Edwards Air Force Base<br>California                                       | W. Severin<br>714-762-5161<br>Ext. 82-7111    | Mrs. G. M. Plock<br>805-258-2111<br>Ext. 3-3141<br>Mojave, California | 365,000             |

| NAS 3-6516-PB        | Central Timing System<br>and Remote Timing<br>System             | NASA Lewis Research<br>Center; Cleveland, Ohio                                | J. Harrold<br>419-625-1123<br>Ext. 533        | R. J. Koch<br>216-433-4000                                            | 49,000              |

| PO NA 256396         | l Model 9029 Analog-<br>to-Digital Converter                     | The Boeing Company<br>Morton, Pennsylvania                                    | F. Wilson<br>215-522-3950                     | C. B. Craskey<br>215-522-3950                                         | 20,000              |

| PO 337050            | SEL 700 Data Processo                                            | or Grumman Aircraft<br>Engineering Corp.,<br>Bethpage, New York               | R. LeCann<br>516-575-1896                     | F. Bolda<br>516-575-0574<br>Ext. 2115                                 | 113,000             |

| NAS 8-13852          | Modulated Digital-to-<br>Analog Converter<br>System              | NASA Marshall Space<br>Flight Center<br>Huntsville, Alabama                   | P. D. Belton<br>205-877-2151                  | W. C. Vaughn<br>205-534-7315                                          | 58,000              |

| PO L-024529-<br>7030 | One Telemetry<br>Digitizing System                               | The Boeing Company<br>Huntsville, Alabama                                     | R. Anfield<br>205-536-4461                    | R. T. Meyer<br>205-842-2304                                           | 55,000              |

| PO 17887965          | High Level Multiplexer                                           | Naval Weapons Laboratory<br>Dahlgren, Virginia                                | T. H. Tharp 703-663-2511                      | J. J. Hanzel<br>703-663-2511                                          | 3,000               |

| NAS9-3195            | Two Low Level<br>Analog-to-<br>Digital Converters                | NASA Manned Space-<br>craft Center<br>Houston, Texas                          | H. J. Lowery<br>713-928-2811<br>Ext. 2565     | J. L. Vyner<br>713-483-5521                                           | 173,000             |

| NAS8-13851           | Digital Data<br>Acquisition<br>System                            | NASA Marshall<br>Space Flight Center<br>Huntsville, Alabama                   | J. C. Duffey<br>205-876-4132                  | W C. Vaughn<br>205-534-6404                                           | 122, 000            |

| NAS8-14436           | PB Buffer                                                        | NASA Marshall<br>Space Flight Center<br>Huntsville, Alabama                   | P. D Belton<br>205-877-2151                   | D. McCreless<br>205-534-6405                                          | 30, 000             |

| C-530-62A-PB         | Remote Display<br>& Channel<br>Selector                          | NASA Plum Brook<br>Station<br>Sandusky, Ohio                                  | J Harrold<br>419-625-1123                     | A Grabach<br>419-625-1123<br>Ext. 331                                 | 3,000               |

| Contract No.         | Description                                            | Customer                                                                      | Technical<br>Contact                                                         | Administrative Contact                   | Approximate<br>Dollars |

|----------------------|--------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|------------------------|

| NAS 9-3626           | 200-Channel Digital<br>Data Acquisition                | NASA - Manned Spacecraft<br>Center, Houston, Texas                            | R. Bozeman<br>713-483-4991                                                   | J. Vyner<br>713-483-5521                 | 42,000                 |

| NAS 3-6941PB         | 200-Channel Sub-<br>System                             | NASA - Lewis Research<br>Center<br>Cleveland, Ohio                            | J. Harrold<br>419-625-1123<br>Ext. 533                                       | R. J. Koch<br>216-433-4000               | 85,000                 |

| AF 08(635)4825       | Data Acquisition<br>System                             | Eglin Air Force Base<br>Florida                                               | J. Himes<br>305-881-6668<br>Ext. 67-3314                                     | Mrs. C. Hudgins<br>305-881-6668          | 82,000                 |

| NAS 8-13619          | High Speed Data<br>Acquisition System                  | NASA - MSFC<br>Huntsville, Alabama                                            | J. Heaman<br>205-876-7227                                                    | D. Hall<br>205-534-4586                  | 110,000                |

| SN PN 565<br>CTA 155 | Eight Multiplexers                                     | Pan American World<br>Airways, Inc.<br>Las Vegas, Nevada                      | D. Brindenstein<br>702-986-5357                                              | J. G. McGuffin<br>702-735-9182           | 90,000                 |

| 28X7563              | Two Analog-to-<br>Digital Converters<br>with Amplifier | Westinghouse Corp.<br>Pittsburgh, Pa.                                         | R. Squires<br>412-391-2800                                                   | R. Endean<br>412-391-2800<br>Ext. 7471   | 18,000                 |

| LZ238051             | MOBIDAC IV                                             | Los Alamos<br>Scientific Lab.<br>Los Alamos, New Mexico                       | T. Springer 505-066-82526                                                    | J. N. Halliday<br>505-066-75084          | 40,000                 |

| 16678                | Digital Data<br>Acquisition &<br>Logging System        | Brown University Providence, R. I.                                            | B. W. Costerus<br>401-861-2900                                               | R. L. Crowley<br>401-861-2900            | 28, 200                |

| NAS 8-11911          | Modulated Digital<br>to Analog Converter               | NASA - MSFC<br>Huntsville, Alabama                                            | P. D. Belton<br>205-877-2151                                                 | W. L. Troupe<br>205-534-7315             | 60, 000                |

| NAS 8-11911          | Data Link                                              | NASA - MSFC<br>Huntsville, Alabama                                            | P. D. Belton<br>205-877-2151                                                 | W. L. Troupe<br>205-534-7315             | 40,000                 |

| NAS 8-11911          | Real Time<br>Entry                                     | NASA - MSFC<br>Huntsville, Alabama                                            | F. Hay<br>205-877-2151                                                       | W. L. Troupe<br>205-534-7315             | 45, 000                |

| 541-11418            | Low Level<br>48-Channel<br>Multiplexer                 | ARO, Inc.<br>Arnold AFS<br>Tennessee                                          | W. N. Brock<br>615-GL 5-2611                                                 | C. Solomon<br>615-GL 5-2611<br>Ext. 7113 | 20,000                 |

| NAS 8-11584          | Two Navigation System<br>Test Stations                 | NASA - MSFC<br>Huntsville, Alabama                                            | J. Mitchell<br>205-876-4413                                                  | D. Marshall<br>205-539-0617              | 270 000                |

| PO 60111             | Digital Data Acquisition<br>System                     | Brown Engineering Co.<br>Huntsville Alabama                                   | B. Goldman<br>205-532-1221                                                   | G. Sharpe<br>205-532-1221                | 120.000                |

| NAS 1-5151           | Adding 20 Channels                                     | NASA - Langley<br>Research Center<br>Hampton, Va.                             | L. E. Taylor<br>703-722-7961<br>Ext. 4851                                    | W. T. Quinn<br>703-722-7961<br>Ext. 4410 | 20,000                 |

| NAS 3-6514           | 800-Channel Data<br>Acquisition System                 | NASA Lewis Research<br>Center; Cleveland, Ohio                                | C. Mealey<br>216-433-4000<br>Ext. 356                                        | M. Kapral<br>216-433-4000<br>Ext. 356    | 545,000                |

| J-30441, C-4         | Sub-System # 2                                         | Edgerton, Germeshausen<br>and Grier, Incorporated<br>Boston 15, Massachusetts | <ul><li>K. J. Foster</li><li>617-271-5131</li><li>(Bedford, Mass.)</li></ul> | H. R. Silver 617-267-9700                | 133,000                |

| NAS 1-5404           | Multiplexed<br>Encoder                                 | NASA Langley Research<br>Center, Hampton, Virginia                            | J. Harrell<br>703-722-7961                                                   | J. Dorst<br>703-722-7961<br>Ext. 4414    | 25,000                 |

| NAS 1-5437           | System Calibrator                                      | NASA Langley Research<br>Center, Hampton, Virginia                            | M. Limburg<br>703-722-7961                                                   | J. Leo<br>703-722-7961<br>Ext. 4683      | 10,000                 |

| 230602               | Count Down<br>Timers                                   | Applied Physics Lab<br>Johns Hopkins Univ.<br>Silver Spring, Md.              | R. Mack<br>202-545-6700                                                      | C. Walters<br>301-589-7700<br>Ext. 330   | 35, 000                |

| Contract No.  | Description                             | Customer                                                            | Technical<br>Contact                      | Administrative<br>Contact              | Approximate Dollars |

|---------------|-----------------------------------------|---------------------------------------------------------------------|-------------------------------------------|----------------------------------------|---------------------|

| NAS 8-20021   | Telemetry Measuring<br>System (Rees #2) | NASA - MSFC<br>Huntsville, Alabama                                  | L. Etheredge 205-876-6143                 | J. McMurry<br>205-842-3597             | \$ 95,000           |

| NAS 8-16371   | Anelex Printer                          | NASA - MSFC<br>Huntsville, Alabama                                  | F. Hay<br>205-877-2151                    | J. Barker<br>205-842-3187              | 30, 000             |

| NAS 8-17451   | Priority Interrupts                     | NASA - MSFC<br>Huntsville, Alabama                                  | F. Hay<br>205-877-2151                    | T. Johnson<br>205-842-3146             | 10, 560             |

| NAS 8-11841   | High Speed Data<br>Acquisition System   | NASA - MSFC<br>Huntsville, Alabama                                  | F. Hay<br>205-877-2151                    | P. B. Higdon<br>205-539-2796           | 940, 000            |

| 337050        | SEL 700 Data<br>Processor               | Grumman Aircraft<br>Engineering Corp.<br>Bethpage, N. Y.            | R. LeCann<br>516-575-1896                 | F. Bolda<br>516-575-0574<br>Ext. 2115  | 125, 000            |

| 230582        | SEL 840 Computer                        | Applied Physics Lab.<br>Johns Hopkins Univ.<br>Silver Spring, Md.   | J. W. Jenkins<br>301-589-7700<br>Ext. 284 | C. Walters<br>301-589-7700<br>Ext. 330 | 280, 000            |

| NAS 8-15388   | 2nd Plotter<br>Interface                | NASA - MSFC<br>Huntsville, Alabama                                  | F. Hay<br>205-877-2151                    | K. Harrell<br>205-842-2155             | 120, 000            |

| NAS 8-16365   | Digital Data Ac-<br>quisition System    | NASA - MSFC<br>Huntsville, Alabama                                  | J. Heaman<br>205-876-7227                 | J. Barker<br>205-842-3187              | 75, 000             |

| NAS 3-8439-PB | Remote Display                          | NASA - Lewis Research<br>Center - Plum Brook Sta.<br>Sandusky, Ohic | J. Harrold<br>419-625-1123                | A. Grabach<br>419-625-1123<br>Ext. 206 | 5, 000              |

| NAS 8-17034   | Two Input<br>Simulators                 | NASA - MSFC<br>Huntsville, Alabama                                  | B. Adair<br>205-876-2668                  | T. Johnson<br>205-842-3146             | 15, 000             |

#### SEL CONTRACTS IN PROGRESS

| Contract No.              | Description                                                           | Customer                                                               | Technical<br>Contact         | Administrative<br>Contact                 | Approximate<br>Dollars |

|---------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------|-------------------------------------------|------------------------|

| NAS 8-13874               | Vehicle Instrumenta-<br>tion Simulator                                | NASA - MSFC<br>Huntsville, Alabama                                     | W. W. Watts<br>205-876-0713  | W. C. Vaughn<br>205-534-7315              | \$180,000              |

| 163730                    | SEL 810 Computer<br>Controlled Locomotive<br>Metering System          | General Motors Corp.<br>Electro-Motive Division<br>La Grange, Illinois | G. E. Harper<br>312-485-7000 | A. J. Purok<br>312-485-7000               | 100, 000               |

| 167633                    | SEL 810 Computer<br>Controlled High<br>Voltage Cabinet Test<br>System | General Motors Corp.<br>La Grange, Illinois                            | H. E. Quinn<br>312-485-7000  | D. J. Gothard<br>312-485-7000             | 260,000                |

| DM75846                   | Data Acquisition<br>System                                            | General Motors Corp.<br>Detroit Diesel Division<br>Detroit, Michigan   | R. Wellington 313-531-7100   | W. Fogarty<br>313-539-5000                | 370, 000               |

| 9802                      | Datatally Electronic<br>Estimating Devices                            | Datatype Corporation<br>Hialeah, Florida                               | M. Zappia<br>696-3832        | W. Runnstrom<br>696-3832                  | 25, 000                |

| NAS 8-15998               | ASR-33 IBM<br>Selectric                                               | NASA - MSFC<br>Huntsville, Alabama                                     | F. Hay<br>205-877-2151       | J. Barker<br>205-842-3187                 | 5, 000                 |

| NAS 8-14427               | Telemetry<br>Measuring System                                         | NASA - MSFC<br>Huntsville, Alabama                                     | J. Toney<br>205-877-2444     | D. McCreless<br>205-534-6405              | 140,000                |

| NAS 8-11911               | Plotter Interface<br>System                                           | NASA - MSFC<br>Huntsville, Alabama                                     | F. Hay<br>205-877-2151       | W. Troupe<br>205-534-7315                 | 80, 000                |

| NAS 8-16552               | Digital Data Ac-<br>quisition System                                  | NASA - MSFC<br>Huntsville, Alabama                                     | J. Heaman<br>205-876-7227    | T. Johnson<br>205-842-3146                | 50, 000                |

| DA-28-043-<br>AMC-0-1606- | Stored Program Analog-to-Digital Tape Formatting System               | U. S. Army<br>White Sands Missile<br>Range, New Mexico                 | S. Scott<br>915-678-1923     | G. Tucker<br>201-535-2428<br>(New Jersey) | 220, 000               |

| A2351S                    | Computer Simula-<br>tion Systems                                      | Melpar, Inc.<br>Falls Church, Va.                                      | F. E. Pappin<br>703-534-6000 | D. Oglesby 703-534-6000                   | 160,000                |

| Withheld                  | SEL 810 Computer                                                      | Withheld by Request                                                    | Withheld                     | Withheld                                  | 95, 000                |

| NAS 9-5092                | Data Acquisition<br>System with SEL 840                               | NASA - MSC<br>Houston, Texas                                           | R. Sachen<br>713-928-2811    | D. Humes<br>713-928-2811                  | 155, 000               |

| L-036535-                 | Central Control<br>System                                             | Boeing Company<br>Huntsville, Alabama                                  | P. Thiel 205-539-8371        | R. Meyer<br>205-842-2304                  | 240,000                |

| DA18-119-AMC<br>02765(X)  | SEL 810 Computer                                                      | Procurement Division<br>Fort George Meade<br>Maryland                  | D. Albert                    | W. Clark                                  | 75, 000                |

| NAS 4-956                 | 1200 Channel<br>Digital Data Ac-<br>quisition System                  | NASA - Edwards<br>Air Force Base<br>California                         | K. Anderson<br>805-258-3311  | W. Taliaferro<br>805-258-3311<br>Ext. 301 | 520, 000               |

| NAS 8-16455               | Digital Flow<br>Converter                                             | NASA - MSFC<br>Huntsville, Alabama                                     | J. Duffy<br>205-876-4132     | R. Culbreth 205-842-2201                  | 140,000                |

| 6-345424                  | 16 Channel<br>Multiplexer                                             | Bell Telephone Labs.<br>Burlington, N. C.                              | J. Hahn<br>919-228-7811      | J. F. Cox<br>201-887-1000                 | 45, 000                |

| 6-601455                  | 16 Channel D/A<br>Converter                                           | Bell Telephone Labs.<br>Burlington, N. C.                              | J. Hahn<br>919-228-7811      | A. Petersen<br>201-887-1000<br>Ext. 3374  | 8, 000                 |

### SEL CONTRACTS IN PROGRESS (Continued)

| Contract No.      | Description                        | Customer                                                            | Technical<br>Contact                        | Administrative<br>Contact             | Approximate<br>Dollars |

|-------------------|------------------------------------|---------------------------------------------------------------------|---------------------------------------------|---------------------------------------|------------------------|

| A36125S           | SEL 810 Computers                  | Melpar, Inc.<br>Falls Church, Va.                                   | F. E. Pappin<br>703-534-6000                | D. Oglesby<br>703-534-6000            | 225, 000               |

| NAS 9-5562        | Boundary Control<br>Unit           | NASA - MSC<br>Houston, Texas                                        | R. Bozeman<br>713-483-4991                  | T. McPhillips<br>713-483-4991         | 8, 000                 |

| NAS 1-5848        | Real Time ID and<br>Logging System | NASA - Langley<br>Hampton, Virginia                                 | C. Bryant<br>703-722-7961<br>Ext. 3483      | W. Quinn<br>703-722-7961<br>Ext. 4410 | 70, 000                |

| MD509180          | Process Control<br>Oriented DAS    | General Motors Corp.<br>Mfg. Develop. Center<br>Warren, Michigan    | D. Larson<br>313-539-5000<br>Ext. 5081      | J. Burgin<br>313-539-5000             | 105, 000               |

| E-21513           | Digital Controller<br>System       | Hamilton Standard<br>Windsor Locks, Conn.                           | J. Woloszynski<br>203-623-1621<br>Ext. 2291 | R. Eckelman<br>203-623-1621           | 145, 000               |

| FNP-49163         | SEL 810                            | General Motors Corp.<br>AC Electronics Div.<br>Milwaukee, Wisconsin | R. Wagner<br>414-762-7000                   | A. Gray<br>414-762-7000               | 45, 000                |

| N0016366<br>C0234 | Digital Data Re-<br>cording System | U. S. Naval Avionics<br>Indianapolis, Indiana                       | J. Carr<br>317-357-8311                     | M. Dooley<br>317-357-8311<br>Ext. 549 | 30, 000                |

1/25/66

## SEL COMPUTER CONTRACTS

## SEL 810

|                                                |                            |                                             | Customer           |

|------------------------------------------------|----------------------------|---------------------------------------------|--------------------|

| Customer                                       | Contract No.               | Description                                 | Engineer           |

| NASA - QUAL Div<br>Huntsville, Alabama         | NAS 8-13874                | Simulator                                   | W. Watts           |

| GM - Electro-Motive Div.<br>LaGrange, Illinois | P.O. 163730                | High Voltage<br>Cabinet Test<br>System      | H. Quinn           |

| NASA - ASTR Div.<br>Huntsville, Alabama        | NAS 8-11911                | Plotting System                             | F. Hay             |

| NASA - QUAL Div.<br>Huntsville, Alabama        | NAS 8-20021                | Telemetry<br>Digitizing<br>System           | J. Rees            |

| GM - Electro-Motive Div.<br>LaGrange, Illinois | P.O. 163733                | Metering<br>System                          | G. Harper          |

| NASA - ASTR Div.<br>Huntsville, Alabama        | NAS 8-15388                | Plotting System<br>Number 2                 | F. Hay             |

| GM - Detroit Diesel<br>Detroit, Michigan       | DM75846                    | Data Acquisi-<br>tion System                | R. Wellington      |

| White Sands Missile<br>Range, New Mexico       | DA-28-043-AMC<br>0-1606-CE | Stored Program A/D Tape For- matting System | S. Scott           |

| Melpar, Inc.<br>Falls Church, Va.              | A24515                     | Two Computer<br>Simulation<br>Systems       | F. E. Pappin       |

| Withheld by Request                            | Withheld by Request        | Direct Digital<br>Control System            | Withheldby Request |

| Boeing Company<br>Huntsville, Alabama          | L-036535-7022              | Central Control<br>System                   | P. Thiel           |

| NASA, GSE Br.<br>Huntsville, Alabama           | NAS 8-16455                | Digital Flow<br>Converter                   | J. E. Duffy        |

| NASA<br>Edwards, California                    | NAS 4-956                  | 1200 Ch. DAS                                | K. Anderson        |

| Procurement Div.<br>Ft. Geo. G. Mead, Md.      | DA18-119-AMC-<br>02765(X)  | 810 Computer                                | D. Albert          |

| Melpar, Inc.<br>Falls Church, Va.              | A36125S                    | 3 810 Computers                             | F. E. Pappin       |

| GM - Technical Center<br>Warren, Michigan      | MD509180                   | Process Control Oriented DAS                | D. Larson          |

| Hamilton Standard<br>Windsor Locks, Conn.      | E-21513                    | Digital Controlling<br>System               | J. Woloszynski     |

| GM - AC Electronics<br>Milwaukee, Wisconsin    | FNP-49163                  | SEL 810                                     | R. Wagner          |

| NASA - ASTR Div<br>Huntsville, Alabama         | NAS 8-14427                | Telemetry<br>Measuring System               | J. Toney           |

| Phillips Petroleum<br>Bartlesville, Oklahoma   | 102709G                    | SEL 810                                     | R.E. Garrison      |

## SEL COMPUTER CONTRACTS

## SEL 840

| Customer                                              | Contract No. | Description                            | Customer<br>Engineer |

|-------------------------------------------------------|--------------|----------------------------------------|----------------------|

| NASA - ASTR Division<br>Huntsville, Alabama           | NAS 8-11841  | Fourier Processing<br>System           | F. Hay               |

| Johns Hopkins University<br>Silver Spring, Maryland   | 230582       | Modification to Polaris Data Processor | J. Jenkins           |

| NASA, MSC<br>Houston, Texas                           | NAS 9-5092   | Data Conversion System                 | R. Sachen            |

| Mass. Inst. of Technology<br>Lexington, Massachusetts | BB-242       | SEL 840                                | F.E. Heart           |

### 2.0 SEL 840 COMPUTER

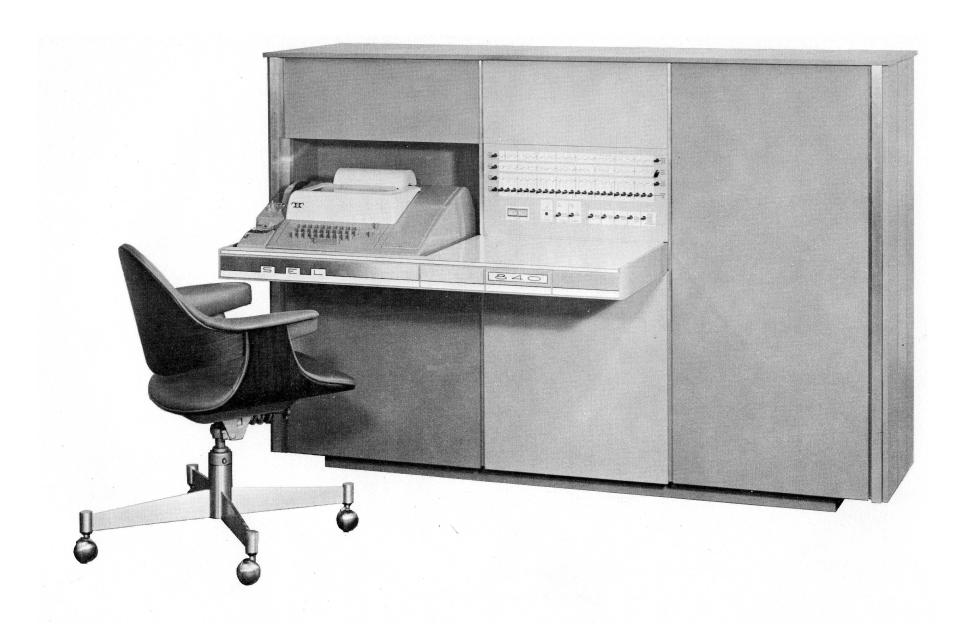

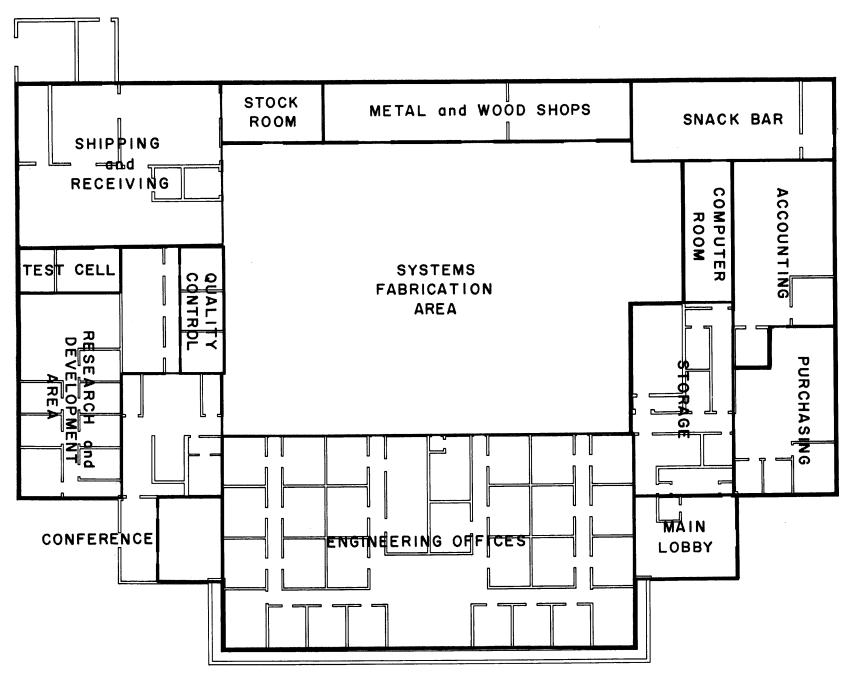

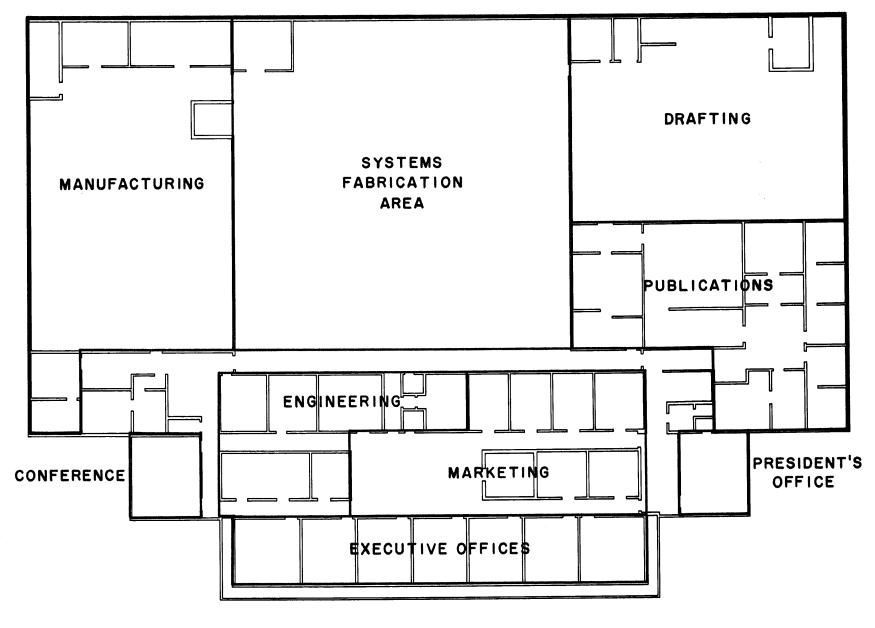

The SEL 840 general purpose computer is a fast (1.75 microseconds full cycle time) general purpose computer developed especially for real-time processing and process control as well as full scientific computation applications. The SEL 840 is offered in a standard configuration having 4096 memory locations, ASR 33 typewriter, paper tape punch and reader with the option of adding numerous standard, catalogue items to expand the basic configuration to meet any application. Section 2.1 defines the specifications of the SEL 840 basic configuration. The optional items available with your basic 840 are described individually following Section 2.1.

## 2.1 SEL 840 Computer - Basic Hardware Configuration

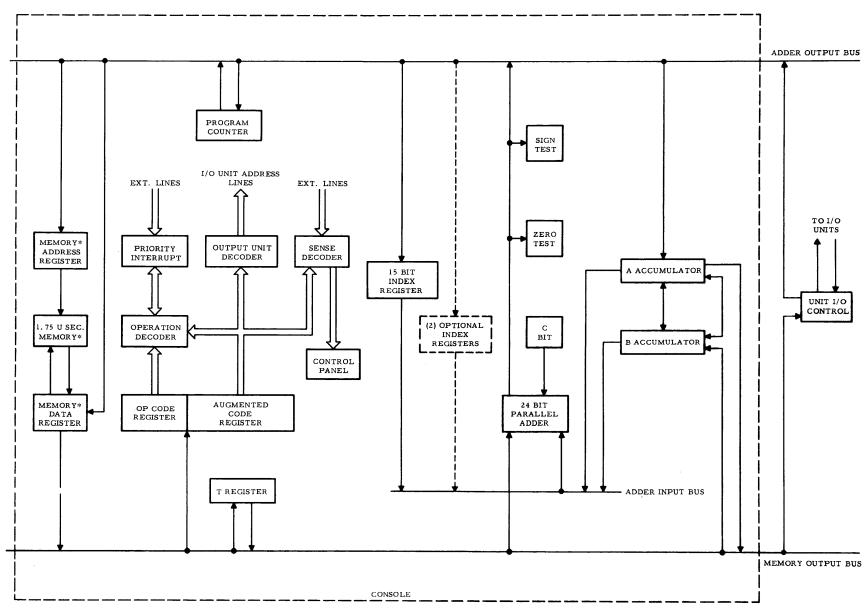

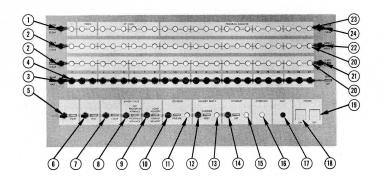

Figure 2. 1 is a block diagram of the SEL 840 computer. The basic configuration is shown in solid lines.

The functional blocks shown have the following basic capabilities:

Memory

Up to eight 4096-address magnetic core modules used to store main programs, constants, subroutines and data awaiting output transfers or program manipulation. One 4096 word module is provided in the basic configuration.

"T" Register

The transfer register into which all words from memory are stored pending operation. Has complementing capability and holds the multiplicand, augend, subtrahend and divisor during arithmetic operations.

<sup>\*</sup> UP TO EIGHT MEMORIES OPTIONAL

A Accumulator

Main arithmetic register holds the addend, minuend, dividend, sum, difference, product and quotient of arithmetic operations.

B Accumulator

The extension of the A accumulator holds the least significant bits of double-precision words and the multiplier, least significant bits of product and remainder of arithmetic operations.

Index Register

Up to three 15-bit registers used in the modification of operand addresses to index files of data words. May be incremented or decremented by an instruction. One index register is provided in the basic configuration.

Adder

Full 24-bit parallel adder used in all arithmetic and logical operations and to add the index register to the operand address.

Memory Address Register

One 12-bit register is associated with each memory module to hold the instruction word and operand addresses. A master 3-bit address register is used to select the module to be accessed. The complete 15-bit address is included in each instruction word and operand address.

Program Counter

An incremental counter that provides the memory address from which the instruction words are taken. The counter is normally increased by one during each instruction cycle, but may be preset to any count by branch instructions.

## 2.1.1 SEL 840 Specifications

Classification

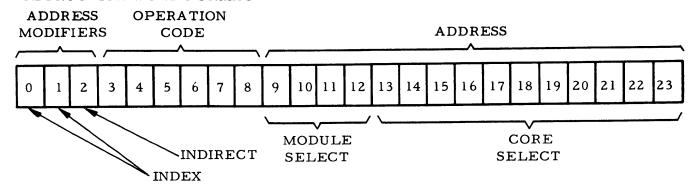

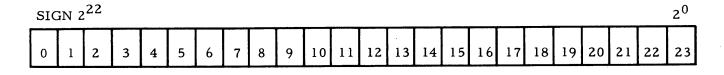

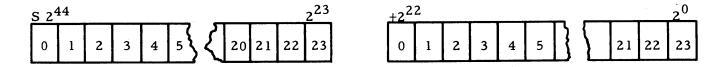

Parallel 24-bit binary, single address with index and indirect address modifiers.

Magnetic Core Memory

600 nanosecond access time, 1.75 microseconds full cycle time.

The basic SEL 840 includes one 4096 word module, but is arranged to address up to 32,768 words of storage formed by the addition of 4096 word modules.

#### Arithmetic

Two's complement fully parallel adder with double-length accumulator. Full right and left, logical and arithmetic shift capabilities with single or double length accumulator.

Sample arithmetic process times are:

Add and Subtract

Multiply

Divide

23. 5 microseconds

22. 75 microseconds

24. 5 microseconds

23-bit shift,

right or left

12. 25 microseconds

#### Control

A powerful instruction repertoire allows direct access of all memory locations and full arithmetic capabilities as well as a wide selection of input/output controls. A hardware program counter and a hardware index register allow instructions to be accessed and modified in the same cycle.

## Input/Output

Systems I/O structure capable of handling 64 units. Four armable multi-level priority interrupt lines. Teletype ASR 33 typewriter, including paper tape punch and reader.

#### Control Console

Register and status indicators.

Priority interrupt inhibit.

Single step instruction execution.

Four sense switches.

Wired for all options - requires no field modification.

### Packaging

Integrated micrologic modular construction operating ranges:

Input Voltage - 115 V60 cycle ±10%

Temperature - 10° to 35°C

Humidity - to 90%

System Weight - 1700 pounds

Space Requirement - Refer to Section 2.1.8

Maintenance Clearance - 36 inches front & rear

No special installation requirements.

Compatible with other equipment through supplied translators.

## 2.1. 2 Input/Output Configurations

## 2.1. 2. 1 System Input/Output Control

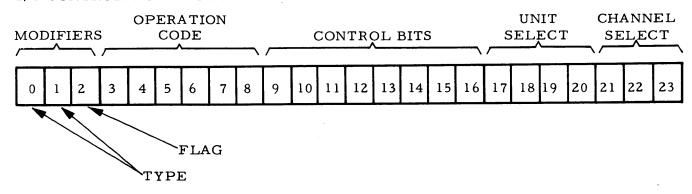

The 840 computer uses an automatically synchronized time-shared I/O bus to communicate with up to 128 units. The six I/O instructions defined below perform all necessary data transfers and control functions.

## DATA TRANSFER:

| Mnemonic                       | Description                                                                                                                              |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1) MOP (Memory Output)         | 24-bit word output from memory location. No registers affected.                                                                          |

| 2) AOP (Accumulator Output)    | 24-bit word output from the A accumulator.                                                                                               |

| 3) MIP (Memory Input)          | 24-bit word input to specified memory location. No registers affected.                                                                   |

| 4) AIP (Accumulator Input)     | 24-bit word input to A accumulator                                                                                                       |

| CONTROL:                       |                                                                                                                                          |

| 5) CEU (Command External Unit) | 24-bit command output from instruction location. Interpreted by unit as a command to perform some function. No registers affected.       |

| TEST:                          |                                                                                                                                          |

| 6) TEU (Test External Unit)    | 24-bit test code output from instruction location. Interpreted by unit as a test of some status. Reply from unit is on test return line. |

All I/O instructions incorporate automatic hardware tests to insure synchronization with the unit, regardless of the speed capabilities of the unit. Instructions do not need to be changed if the same software is run with units of varying speed capabilities.

Several tests are performed by the computer to insure proper instruction execution.

Each I/O instruction addresses the unit desired, so no "Select""Deselect" operation is necessary. The I/O bus is used by the addressed unit

only during the instruction time.

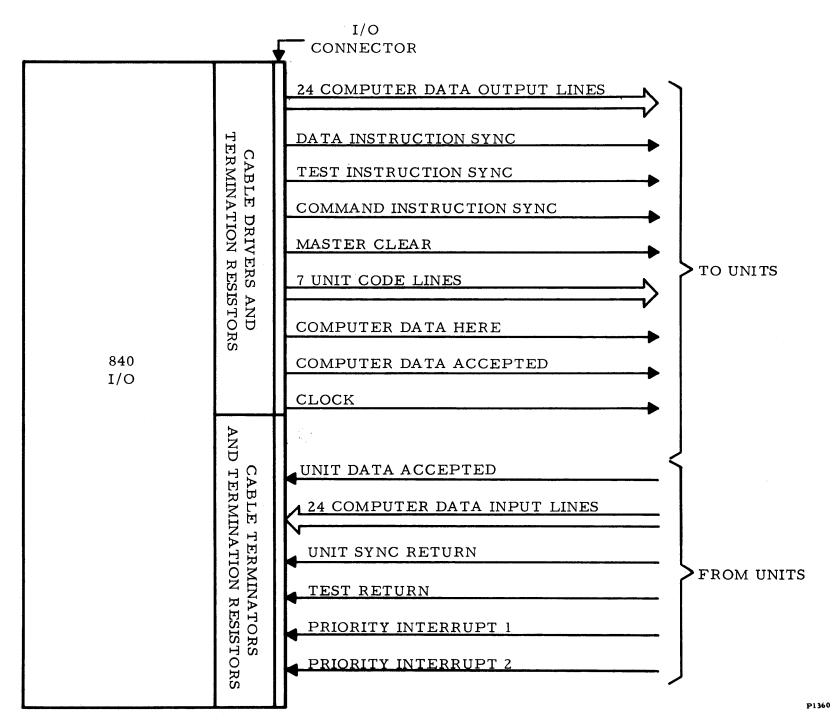

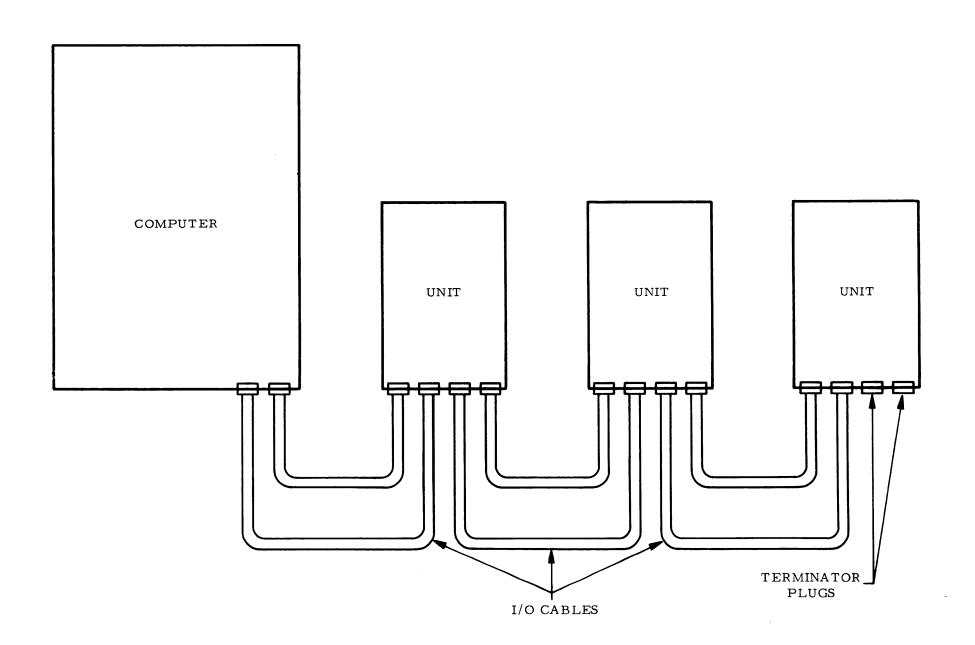

The 840 I/O connectors contain the logic signals shown in Figure 2.1.2-1. Each line is, in fact, a twisted pair and the two I/O cables are standard 51-pair cable.

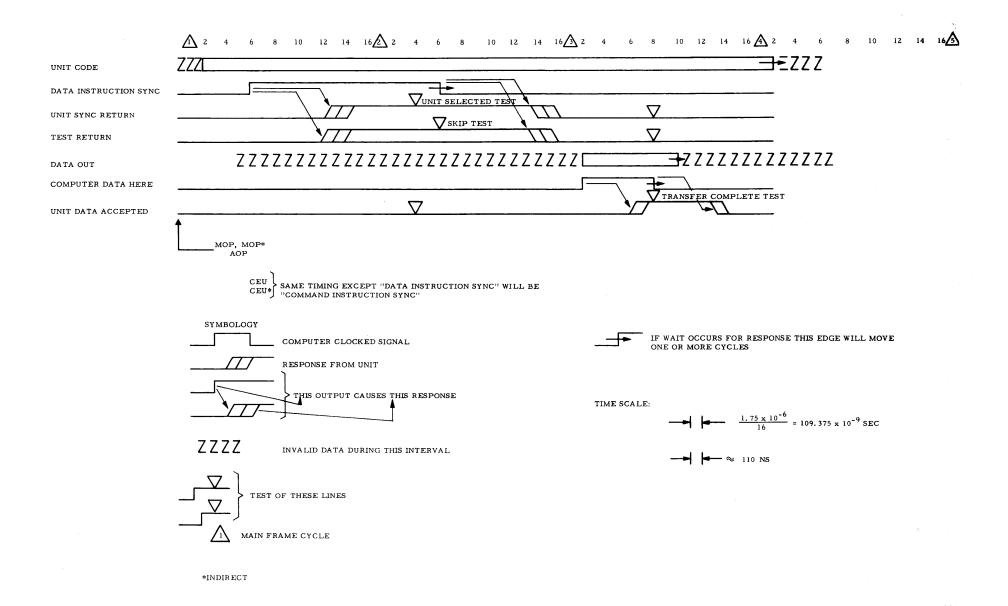

The I/O instructions involve several operations. Unit addressing, test of unit response, test of ready for data transfer, and test of transfer complete, are performed on each instruction. A "Wait Flag" can be included in the data transfer and control instructions to cause the computer to "Wait" until the unit addressed is ready for data transfer. If a "Wait" occurs, it occurs as one or more "cycles" (1.75 microseconds).

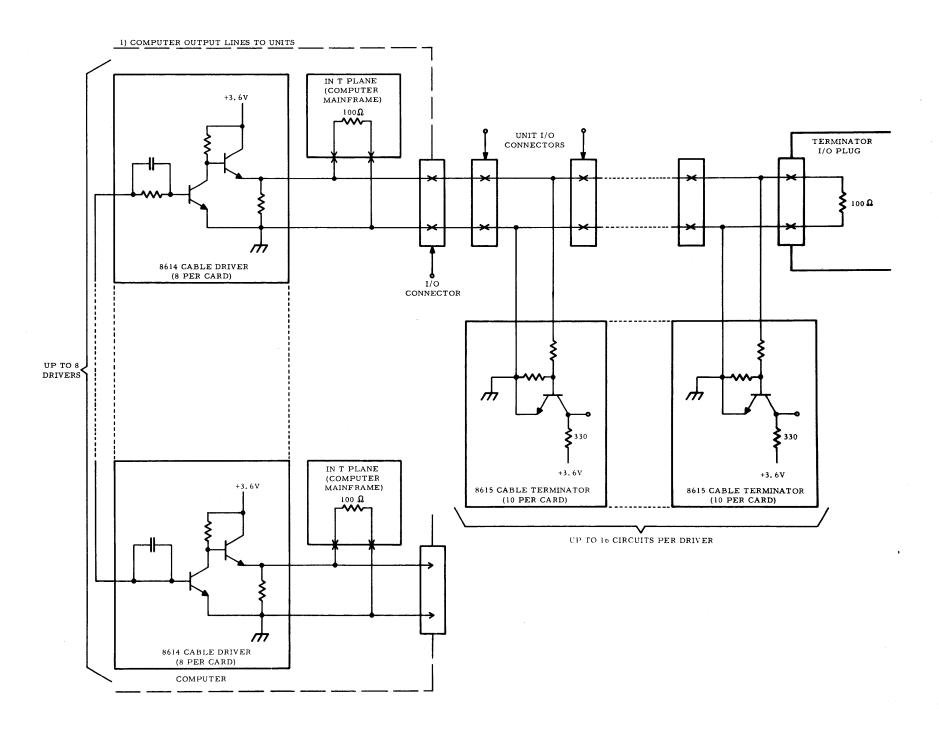

Computer outputs appear as indicated in Figure 2. 1. 2-2. The cable driver (SEL #8614) will supply sufficient drive current to drive 16 cable terminators (SEL #8615), and a total of 100 feet of I/O cable. It should be noted that unnecessarily long cables may add cycles to the I/O instruction. The <u>Basic</u> 840 includes one set of drivers for the I/O channel. If more than 16 units are to be driven, additional drivers are available as an option. It should be noted

FIGURE 2.1.2-1 840 I/O INTERFACE

that all data is presented to all units. Gating of data which pertains to the unit is done in the control logic for the unit.

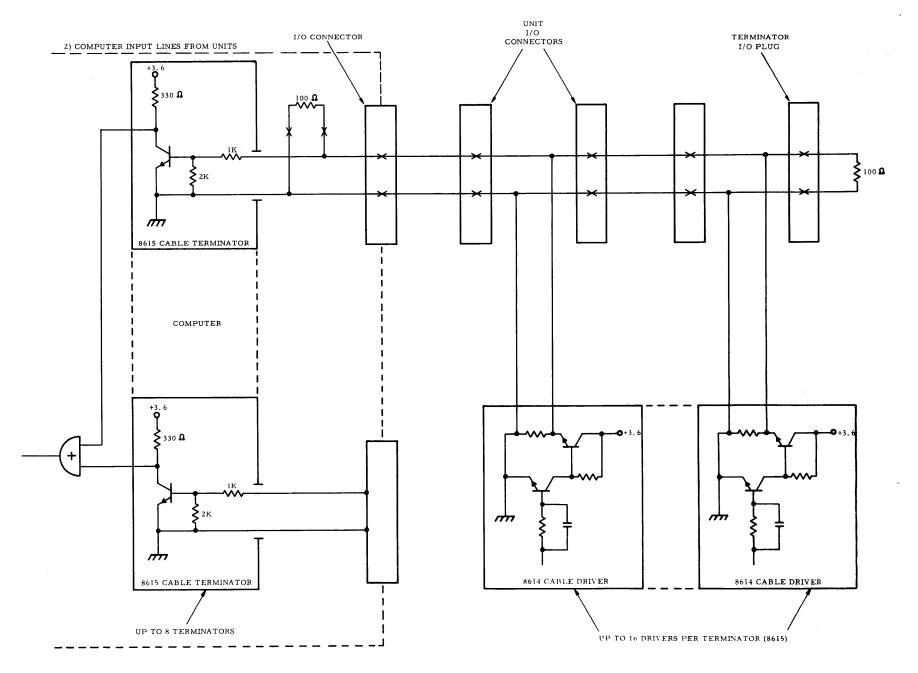

Inputs to the computer appear as indicated in Figure 2.1.2-3. The emitter-follower configuration of the 8614 cable driver allows any unit to "lift" the line to the "true" level (+2V, +1.5V, -.5V). Gating to insure that only the unit addressed "on line" is done in the unit control logic. A total of 16 units can drive the input line. If additional units are required, additional terminators (and connectors) are available as an option. A total of 100 feet of cable can be used to connect the 16 units. Again, it should be noted that unnecessarily long cables should be avoided.

In Figure 2.1.2-4 the I/O cables are "daisy chained" from unit to unit, with a termination resistor plug on the end units output connector.

Power is not supplied through the I/O cable.

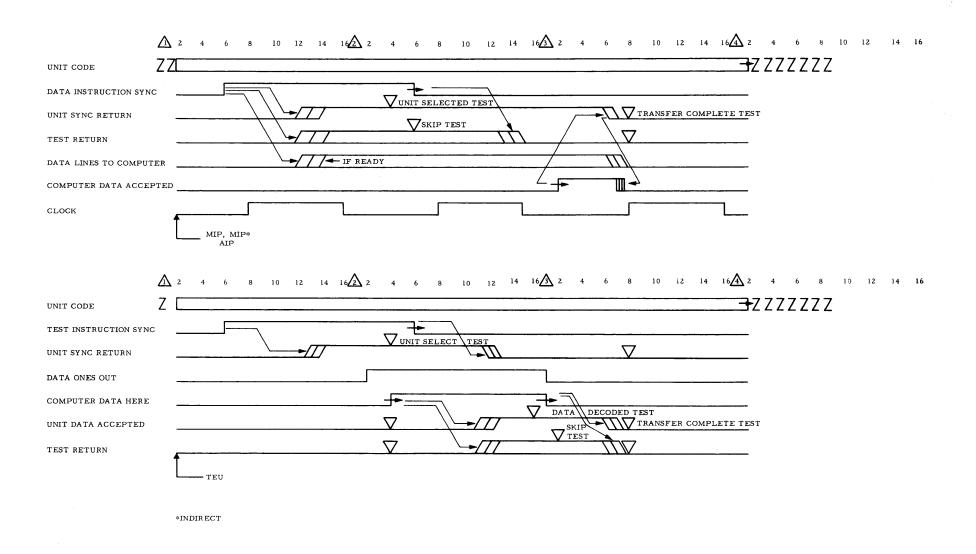

Figures 2.1.2-5 and -6 illustrate the details of the timing of the I/O instructions, as seen from the main frame end. The symbology used is explained below the timing chart on Figure 2.1.2-5.

The timing shown assumes high-speed units with I/O cable of 50 feet or less. Delays of one or more cycles may take place with longer cable or lower speed logic.

The instructions operate as indicated in Figures 2.1.2-5 and -6. The unit code includes six bits of unit address and one bit which indicates input or output. This line is a 1 (+V on line) for output. In all I/O instructions, the unit code is placed on the unit code lines, then a sync line is raised. The

FIGURE 2.1.2-3 INPUT LINES TO COMPUTER

FIGURE 2.1.2-4 I/O CABLING

FIGURE 2.1.2-5 TIMING, OUTPUT COMMANDS

FIGURE 2.1.2-6 TIMING, INPUT AND TEST COMMANDS

specific line raised indicates what type of instruction follows. There are three sync lines: Data Instruction Sync (DIS), Command Instruction Sync (CIS), and Test Instruction Sync (TIS). The addressed unit is expected to reply on the sync return line as soon as it recognizes its unit code and which sync line is up. A unit-selected test is made at T<sub>4</sub>. If this fails, a one-cycle wait will occur and then the test will be repeated. This continues until the addressed unit responds. The unit addressed gives a "status report" on the test return line to indicate if it can execute the indicated instruction (except for TEU, which will be discussed later). If the I/O instruction has a "Wait Flag", this test is repeated, adding a cycle each time, until the test return line goes "true", indicating the unit is ready to execute the instruction.

If the data or control I/O instruction does <u>not</u> have a "Wait Flag", the results of the skip test determine what action occurs. If the unit says "Ready To Execute", the data transfer takes place, then "skip" occurs in the program counter. If the unit says "Not Ready To Execute" during the skip test, no data transfer takes place and the instruction following the I/O instruction is accessed as the next instruction. This allows the programm to "branch out" when the unit is not ready. The final test on all I/O instructions involves a "Transfer Complete Test", which insures that slow units are "off line" before proceeding.

The lower part of 2. 1. 2-6 illustrates the timing of the Test External Unit (TEU) instruction. It is used specifically to test the status of a unit at the time it is executed; therefore, no "Wait Flag" is allowed.

"Wait" or "hold" may occur to allow unit response time but not to wait for a "ready" response to the skip test.

### 2.1.2.2 Block Transfer Control Unit

The SEL block transfer control (BTC) is an optional computer input/output control unit which enables fully buffered transfer of data between peripheral units and computer memory. The salient features of this unit are listed below.

Bits per Transfer . . . . . . Full computer word

Maximum Words per Block . . . 8,191

Maximum Transfer Rate . . . . 286,000 words per second

Memory Cycles Stolen per Transfer . 1

Block Transfer Re-initialization . . Automatic

Maximum Number of BTC's per

Computer. . . . . . . . . . . . 8

Maximum Number of Peripheral

Units per BTC . . . . . . . 16

## 2.1.2.3 BTC Operation

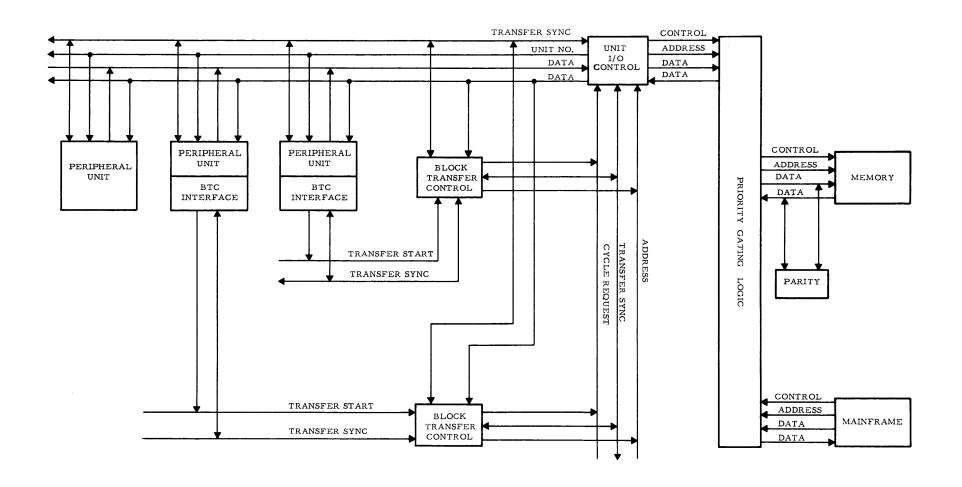

The BTC contains two binary counters plus transfer initialization and synchronization logic. One of the counters stores the current word address (CWA) and the second stores the block length (BL). CWA defines the storage location for each word transferred to/from memory and BL defines the number of words to be transferred. The initial values for CWA and BL are obtained from two fixed locations in computer memory by the BTC each time a new block transfer is initiated. Each time a word is transferred between memory

and the selected peripheral unit, the hardware counters containing CWA and BL are incremented and decremented reseptively. The block transfer is completed and an interrupt is generated when BL = 0. After a block transfer is completed, the BTC automatically initiates a new block transfer by obtaining a new initial set of CWA and BL values from the two dedicated memory locations. The block transfer sequence is terminated by placing a unique stop code in the BL word.

### 2.1.2.4 BTC Initialization and Data Flow

The BTC is initialized through the peripheral unit to/from which the block transfer is to be made. Figure 2.1.2.4 shows the data and control paths involved. The figure shows two peripheral units, each connected to a different BTC. Execution of a Command External Unit (CEU) instruction causes the unit specified by the instruction to send a transfer start signal to the BTC to which it is cabled. In many peripheral units this instruction also causes the unit to initiate action to produce/accept data. When the BTC receives the Transfer Start signal from the unit, it requests a memory cycle through the Unit I/O Control. It also generates the address of the CWA memory location assigned to it. When the memory cycle is granted, the CWA value is transferred from memory to the CWA counter in the BTC over the Unit I/O data lines connected to all peripheral units. A request for a second cycle is then made by the BTC, and the address of the memory location containing BL is placed on the address lines, again by the BTC. When the second cycle occurs, BL is transferred from memory to the BL counter in the BTC over the Unit I/O data output bus. A control code contained in the BL word is also decoded and a latch is set if the terminate code is detected, signifying that

no more block transfers are to be made after completion of the one being initialized. The maximum time for the entire initialization is three cycles for the CEU, 2 cycles for the CWA and BL transfers plus a maximum of three cycles for execution of a mainframe instruction between the CEU and CWA, BL transfers, resulting in a maximum time of 14 microseconds.

After BTC initialization, words are transferred between the selected peripheral unit and memory over the Unit I/O data lines under the joint control of the BTC and Unit I/O. A word transfer is initiated by the unit, which sends a Ready line to the BTC. The Ready signal causes the BTC to request a memory cycle through the Unit I/O Control. When the Unit I/O determines that the next cycle can be granted, memory available signal is sent to the BTC. The BTC, in turn, sends a signal to the peripheral unit which causes it to connect to the Unit I/O data lines, execute the data transfer, and then disconnect from the data lines. After completion of a word transfer, the CWA value is incremented and the BL value is decremented in the BTC counters. All words are transferred by repetition of this cycle, which is always initiated by the peripheral unit.

When the value of BL is decremented to zero, the block transfer is terminated. If the terminate latch in the BTC had not been set by the control code in the last BL word acquired from memory, a new block transfer is automatically initiated by the BTC. Re-initialization consists of acquiring new CWA and BL values from the memory locations assigned to the BTC. After reinitialization, an interrupt is generated which signifies that the transfer of the last block is completed and a new block transfer is initialized. The interrupt

processing routine may then store in the dedicated locations the CWA and BL values for the next block transfer anytime prior to the completion of the current block transfer. This re-initialization technique eliminates the problem of re-initializing block transfers under program control between the times of occurrence of two successive words in a continuous data stream.

If the terminate latch in the BTC had been set by the control code in the last BL word acquired from memory, an interrupt is generated when the value of BL is decremented to zero and no new transfer is initialized by the BTC. In addition, the Ready line from the peripheral unit is disconnected until a new Transfer Start signal is received. Hence, the BTC disconnects from the peripheral unit.

# 2. 1. 2. 5 BTC Priority and Timing

BTC's are granted memory cycle requests on a priority basis.

A unique priority is assigned to each BTC. The priority logic is structured similar to that of the interrupt priority logic, insuring that higher priority BTC's are always serviced before lower priority units. However, once a word transfer is initiated, it is not interrupted by a request from a higher priority BTC. In addition, BTC requests for memory cycles always take precedence over mainframe requests and can effectively "lock out" the mainframe if the peripheral transfer rate is high enough.

The maximum collective transfer rate for a BTC (or group of BTC's) is 572 KHz. Cycle stealing (or lockout) from the program is automatic and each BTC word transferred removes one cycle from the program. The BTC

can gain access to the memory after a delay of one cycle except for the following instructions:

| Two Cycles |                                  | Three Cycles |     |

|------------|----------------------------------|--------------|-----|