# SPECIFICATIONS

# Tile-Computer System MODEL 1

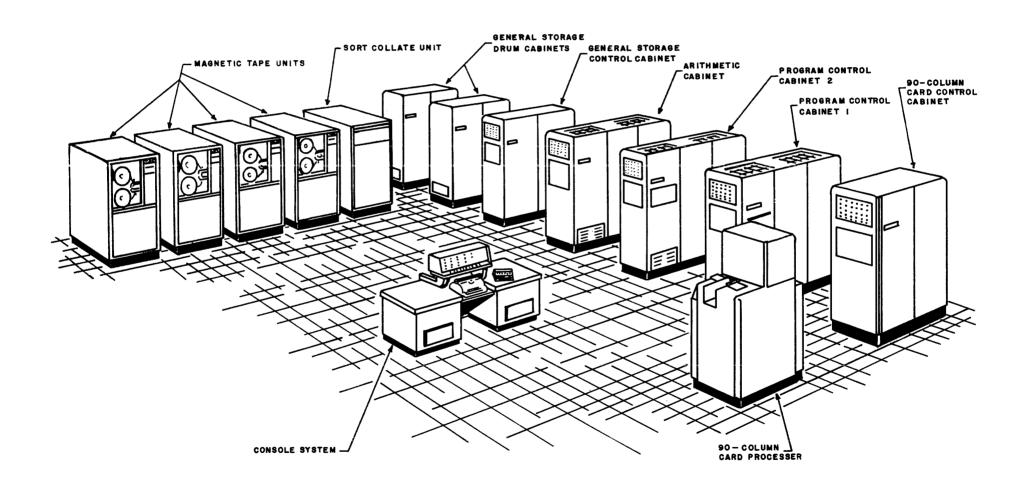

Central Computer and General Storage System

# SPECIFICATIONS

Central Computer and General Storage System

© 1958 - SPERRY RAND CORPORATION

Remington Rand Univac

## TABLE OF CONTENTS

| INTR | ODUC' | rion |                                       | хi               |

|------|-------|------|---------------------------------------|------------------|

| I    | UFC   | MODI | DEL 1 SYSTEM RESUME                   | [-1              |

|      | A.    | MODI | DEL 1 CENTRAL COMPUTER                | [ <b>-</b> 2     |

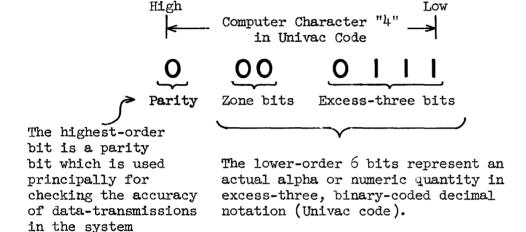

|      |       | 1.   | Units of Data                         | [-2              |

|      |       |      |                                       | [-2              |

|      |       |      |                                       | [ <b>-</b> 3     |

|      |       |      | c. Units of Storage                   | [-3              |

|      |       |      | (1) Word                              | [ <b>-</b> 3     |

|      |       |      |                                       | <b>[-</b> 3      |

|      |       |      | (3) Blockette                         | [-3              |

|      |       | 2.   | Three-Address Instructions            | I <b>-</b> 5     |

|      |       |      | a. Instruction Words                  | r-6              |

|      |       |      |                                       | I-7              |

|      |       | 3.   |                                       | <br>[ <b>-</b> 9 |

|      |       | ٠٠   |                                       |                  |

|      |       |      |                                       | I <b>-</b> 9     |

|      |       |      |                                       | -10              |

|      |       |      |                                       | -11              |

|      |       |      |                                       | -12              |

|      |       |      | e. General Storage Control Section    | -13              |

|      | В.    | UFC  | C MODEL 1 INPUT/OUTPUT SYSTEM         | -13              |

|      |       | 1.   | UFC Input/Output Units                | -13              |

|      |       | 2.   |                                       | -14              |

|      |       | 3.   | Principal Features of the UFC Model 1 |                  |

|      |       |      | Input/Output System                   | -15              |

|      | C.    | UFC  | MODEL 1 GENERAL STORAGE SYSTEM        | -15              |

|      |       | 1.   | Units of Data                         | -15              |

|      |       | 2.   |                                       | -16              |

|      |       | 3.   | Principal Features of UFC Model 1     |                  |

|      |       | 3.   |                                       | -16              |

| II   | PRO   | GRAM | CONTROL                               | [-1              |

|      | Α.    | INT  | TERNALLY-STORED PROGRAMS              | [ <b>-</b> 2     |

|      |       | 1.   | Instruction Words                     | [ <b>-</b> 2     |

|      |       |      |                                       | [ <b>-</b> 3     |

|      |       |      |                                       | [ <b>-</b> 6     |

|      |       |      | c. Sub-Instructions                   |                  |

|      |       |      |                                       |                  |

| (1)                                                                                  | Sub-Instructions for the Central Computer II-1                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                      | (a) Set Conditional Storage       II-12         (b) Suppress Check       II-15         (c) Stop       II-15                                                                                                                                                                                                                                    |

| (2)                                                                                  | Sub-Instructions Which Initiate General Storage Operations II-15                                                                                                                                                                                                                                                                               |

|                                                                                      | (a) Clear GSB to Ignores       II-16         (b) Read UR       II-16         (c) Write UR       II-16         (d) Write UR and Check       II-16         (e) CS =       II-16         (f) CS ≠       II-16                                                                                                                                     |

| (3)                                                                                  | Sub-Instructions Which Can Produce a Pulse on the Program Control Plugboard II-16                                                                                                                                                                                                                                                              |

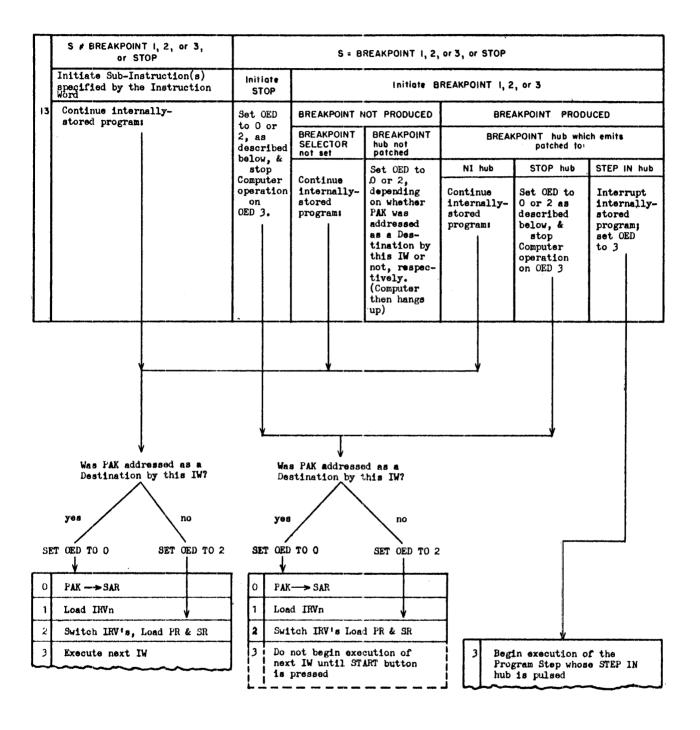

|                                                                                      | (a) Breakpoint 1, 2, or 3                                                                                                                                                                                                                                                                                                                      |

|                                                                                      | etation, Execution, and Sequencing of Instruction                                                                                                                                                                                                                                                                                              |

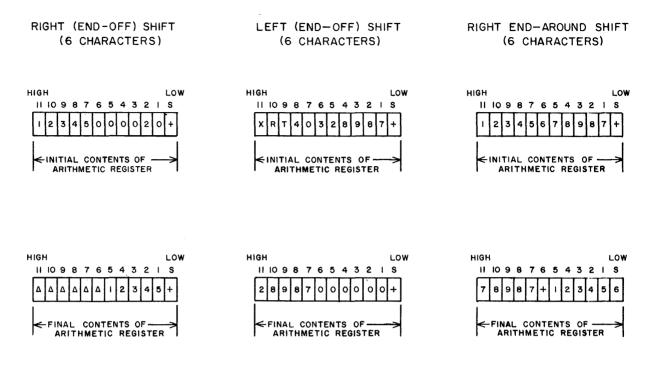

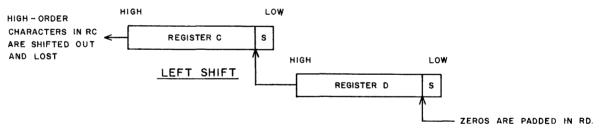

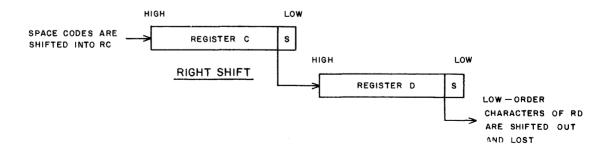

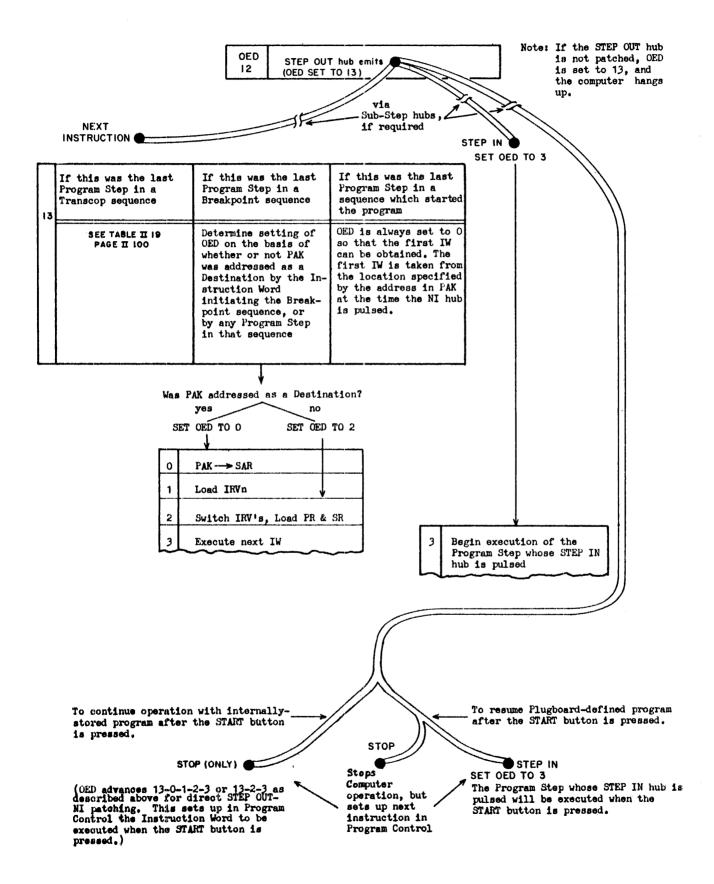

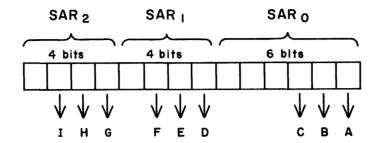

| b. Prog<br>c. Inst<br>d. Prog<br>e. Prog<br>f. Spec<br>g. Stor<br>h. Tran<br>i. Prog | ration Pulse/Enable Distributor, OED II-18 gram Address Counter, PAK II-20 truction Revolver, IRV II-23 cess Register, PR II-25 gram Control Translator, PCT II-21 cial Character Register, SR II-26 rage Address Register, SAR II-26 nsfer Address Control, TAC II-28 grammable Shifts II-28 ft Word, Shift Revolver, and Shift Counter II-34 |

| PLUGBOARD DI                                                                         | EFINED PROGRAMS II-38                                                                                                                                                                                                                                                                                                                          |

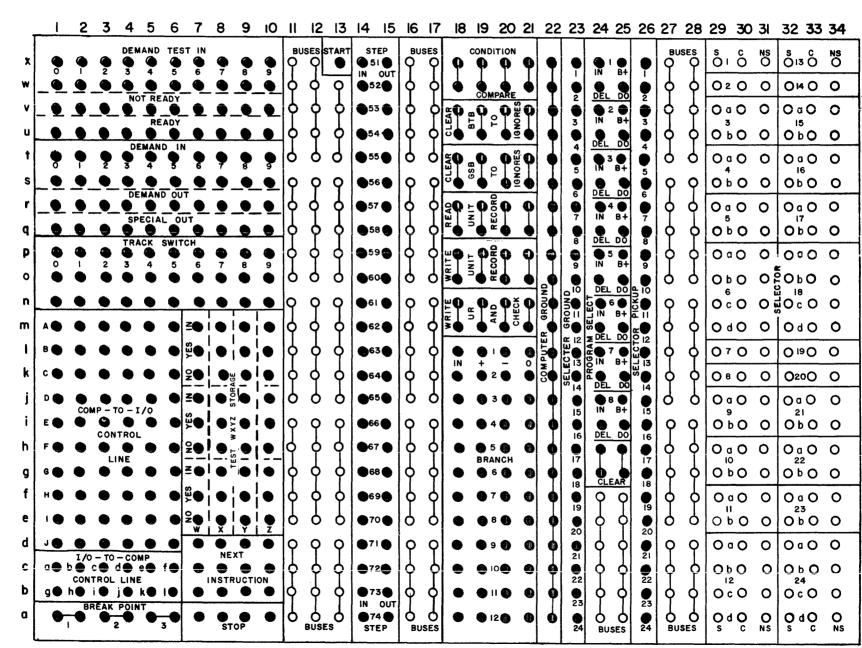

| 1. Program                                                                           | Control Plugboard II-39                                                                                                                                                                                                                                                                                                                        |

| b. Bas:<br>c. Plug<br>d. Plug                                                        | gram Step                                                                                                                                                                                                                                                                                                                                      |

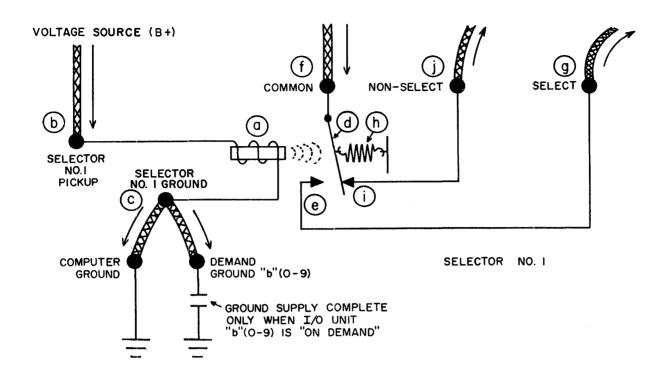

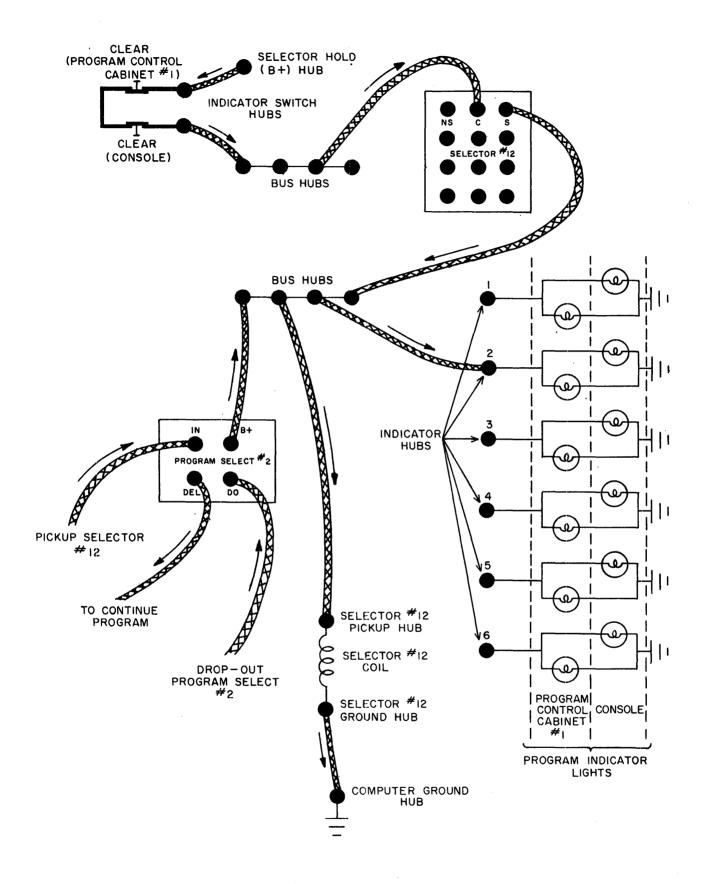

| (1)                                                                                  | Selector Pickup (1-48) Patching II-52                                                                                                                                                                                                                                                                                                          |

|                                                                                      | (a) From Program Select (B+) II-52<br>(b) From Selector Hold (B+) II-53                                                                                                                                                                                                                                                                        |

В.

| • II-55                                                                   |                                         |                                       |                                       |                                         | ne       | L   | 1       | rc           | ont       | ıter (                                                           | I/O-Com                                                                                                  | rom (LS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (c)                                                                                              |                                                                                               |    |

|---------------------------------------------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------|----------|-----|---------|--------------|-----------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----|

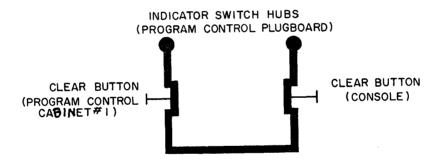

|                                                                           | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            | •         |                                                                  |                                                                                                          | ubs (a-1<br>rom Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ( ~ )                                                                                            |                                                                                               |    |

| . II-5                                                                    | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            | •         | • •                                                              | Te B+                                                                                                    | rom Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (d)                                                                                              |                                                                                               |    |

| • II-5                                                                    | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            | ng        | Patch                                                            | (1-48)                                                                                                   | or Grou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Selec                                                                                            | (2)                                                                                           |    |

| . I <b>I-</b> 5                                                           |                                         |                                       |                                       |                                         |          |     |         | •            | •         |                                                                  | r Groun                                                                                                  | o Comput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (a)                                                                                              |                                                                                               |    |

| • II <b>-</b> 5                                                           | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            | •         | 9)                                                               | Ground                                                                                                   | o Demand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (b)                                                                                              |                                                                                               |    |

| • II-5                                                                    | •                                       |                                       | •                                     |                                         | •        | •   |         |              | •         |                                                                  | A-F) .                                                                                                   | witches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rnate                                                                                            | . Alte                                                                                        | f. |

| . II-60                                                                   | •                                       |                                       | •                                     | •                                       | •        | •   | •       | •            | •         | 3 <b>.</b> .                                                     | r Enabl                                                                                                  | ements i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | sion E                                                                                           | . Deci                                                                                        | g. |

| . II-60                                                                   | •                                       |                                       | •                                     | •                                       | •        | •   | •       | 3            | hes       | Swit                                                             | lternat                                                                                                  | ors and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Selec                                                                                            | (1)                                                                                           |    |

| . II-60                                                                   | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            |           |                                                                  | es                                                                                                       | IABLE Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CDR E                                                                                            | (2)                                                                                           |    |

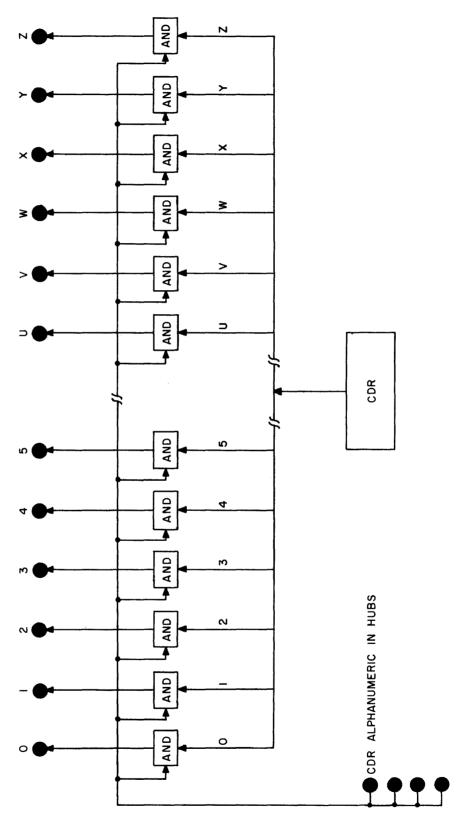

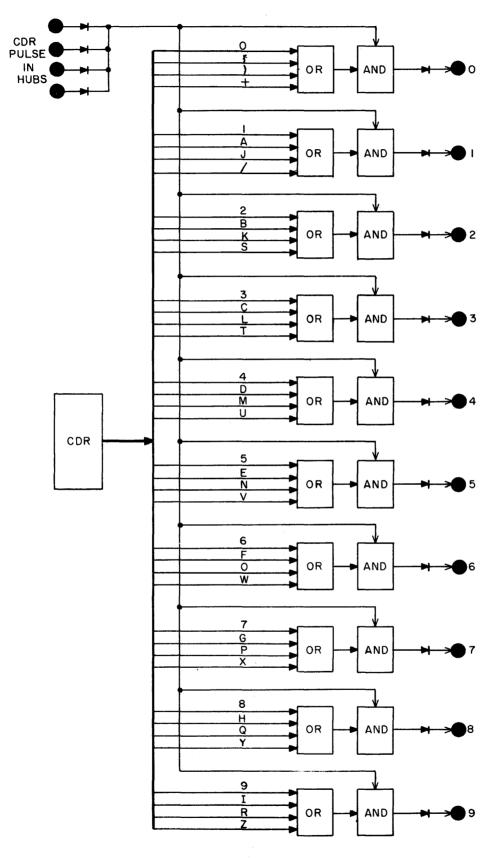

| . II-60                                                                   |                                         | _                                     |                                       | )                                       | CD       | r.  | വ       | )12 <b>†</b> | rib       | Dis                                                              | n of Co                                                                                                  | xplanati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (a)                                                                                              |                                                                                               |    |

|                                                                           |                                         |                                       |                                       |                                         |          |     |         |              |           |                                                                  |                                                                                                          | DR GROUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                               |    |

|                                                                           | •                                       | •                                     | •                                     |                                         | •        |     | •       | •            | e         | Pro                                                              | UMERIC                                                                                                   | DR ALPHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (c)                                                                                              |                                                                                               |    |

| . II-60                                                                   | •                                       | •                                     | •                                     |                                         | •        | •   | )       | n)           | tic       | form                                                             | eneral                                                                                                   | tching (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | S <b>tep</b> P                                                                                   | . Sub-                                                                                        | h. |

| . II-66                                                                   | •                                       | •                                     | •                                     | •                                       | •        | •   | •       | •            | •         |                                                                  | r Pulse                                                                                                  | ements i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | sion E                                                                                           | i. Deci                                                                                       | i. |

| . II-6                                                                    |                                         |                                       |                                       |                                         |          |     |         |              |           |                                                                  |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                  |                                                                                               |    |

|                                                                           |                                         |                                       | •                                     |                                         | _        |     | _       | _            |           |                                                                  |                                                                                                          | Sub-Ste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Branc                                                                                            | (1)                                                                                           |    |

| . II-6'                                                                   | •                                       |                                       |                                       |                                         |          |     |         |              |           |                                                                  |                                                                                                          | Sub-Ste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                  | (1)<br>(2)                                                                                    |    |

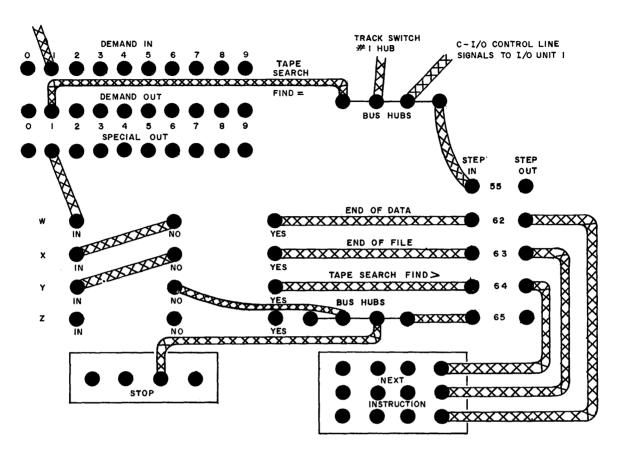

|                                                                           |                                         | •                                     | •                                     | •                                       | •        | •   | •       | •            | •         | -Ste                                                             | Probe S                                                                                                  | l Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chann                                                                                            | (2)                                                                                           |    |

| . II-68                                                                   | •                                       | •                                     | •                                     | •                                       | •        | tej | ·St     | ·<br>ib-     | •<br>Su   | -Ste<br>l Wai                                                    | Probe S<br>Probe a                                                                                       | el Search<br>el Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Chann<br>Chann                                                                                   |                                                                                               |    |

| . II-68                                                                   | •                                       | ·<br>eps                              | ·<br>te                               | •<br>•                                  | Sub      | te: | ·St     | ib-          | Su<br>"Pr | o-Ste<br>l Wai<br>vitch                                          | Probe S<br>Probe a<br>ernate                                                                             | el Search<br>el Search<br>for or Al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chann<br>Chann<br>Selec                                                                          | (2)<br>(3)<br>(4)                                                                             |    |

| . II-68<br>. II-68                                                        | 5.                                      | ·<br>eps                              | Ste                                   |                                         | •<br>Sub | tej | Stoe'   | ib-          | Su<br>"Pr | o-Ste<br>l Wai<br>ritch<br>ceps                                  | Probe S<br>Probe a<br>ernate<br>ce Sub-                                                                  | el Search<br>el Search<br>or or Al<br>on Seque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Chann<br>Chann<br>Selec<br>Funct                                                                 | (2)<br>(3)<br>(4)<br>(5)                                                                      |    |

| . II-68<br>. II-69<br>. II-79                                             |                                         | eps                                   | :<br>:<br>:                           | •<br>•                                  | o<br>Sub | tej | Stoe'   | ib-          | Su<br>"Pr | o-Ste<br>l Wai<br>witch<br>ceps                                  | Probe S<br>Probe a<br>ernate<br>ce Sub-<br>Sub-St                                                        | el Search<br>el Search<br>or or Al<br>on Seque<br>ILSE Prob                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chann<br>Chann<br>Selec<br>Funct<br>CDR P                                                        | (2)<br>(3)<br>(4)<br>(5)<br>(6)                                                               |    |

| . II-68<br>. II-69<br>. II-79<br>. II-79                                  | •                                       | eps                                   | :<br>:<br>:                           | - S                                     | Sub      | te  | stoe'   | ib-          | Su<br>"Pr | o-Ster<br>l Wai<br>vitch<br>ceps                                 | Probe S<br>Probe a<br>ernate<br>ce Sub-<br>Sub-St<br>Sub-Ste                                             | el Search<br>el Search<br>or or Al<br>on Seque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Chann<br>Chann<br>Selec<br>Funct<br>CDR P                                                        | (2)<br>(3)<br>(4)<br>(5)                                                                      |    |