## IEEE 1394-1995 High Performance Serial Bus

#### **Michael D. Johas Teener**

Chief Technical Officer, Firefly, Inc. 269 Mt. Herman Rd. #102 Scotts Valley, CA 95066-4000 mike@fireflyinc.com

## **Background** (the way things are now)

- No I/O Integration

- lots of PCB area, silicon & software

- no common architecture

- Hard to change

- no realtime transport

- performance not scalable

# Goals

- Low cost, high performance ergonomic peripheral bus

- Read/write memory architecture

- NOT an I/O channel

- Compatible architecture with other IEEE busses

- Follow IEEE 1212 CSR (Control and Status Register) standard

- Isochronous service

# "Isochronous" ??

- Iso (same) chronous (time) :

- Uniform in time

- Having equal duration

- Recurring at regular intervals

| Data Type | Sample size & rate              | Bit rate       |

|-----------|---------------------------------|----------------|

| ISDN      | 8 kHz x 8 bits                  | 64 kbps        |

| CD        | 44.1 kHz x 16 bits x 2 channels | 1.4 Mbps       |

| DAT       | 48 kHz x 16 bits x 2 channels   | 1.5 Mbps       |

| Video     | variable to 30 fps              | 1.5 – 216 Mbps |

## Asynch vs. Isoch

- Asynchronous transport

- "Guaranteed delivery"

- Reliability more important than timing

- Retries are OK

- Isochronous transport

- "Guaranteed timing"

- Late data is useless

- Never retry

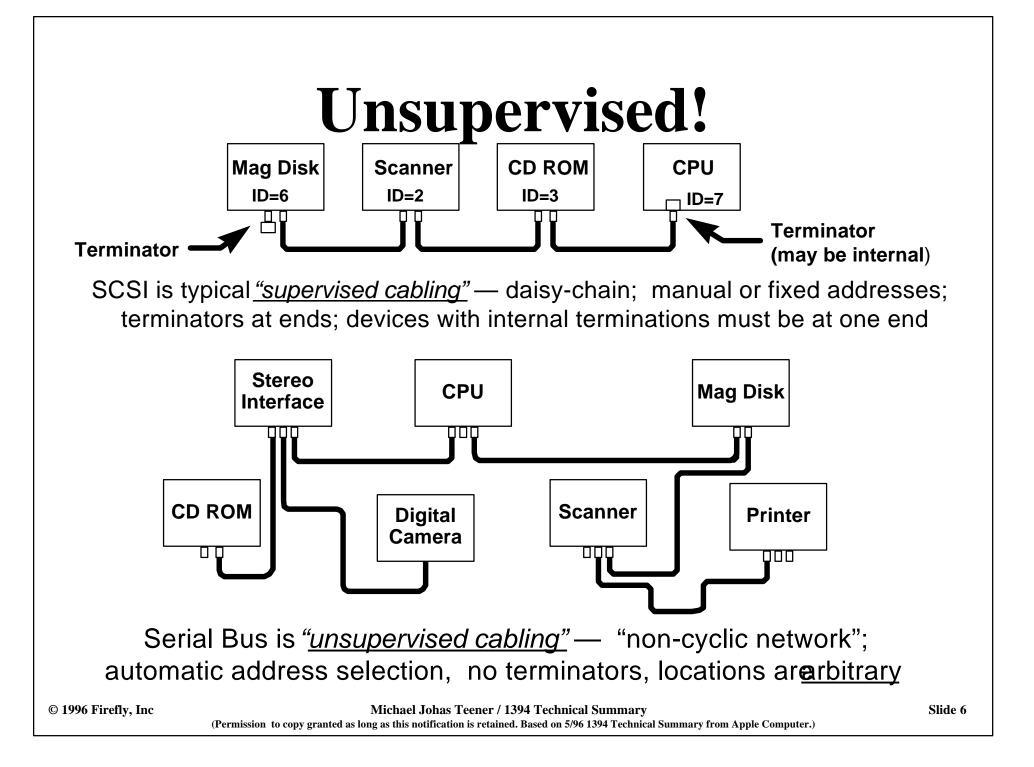

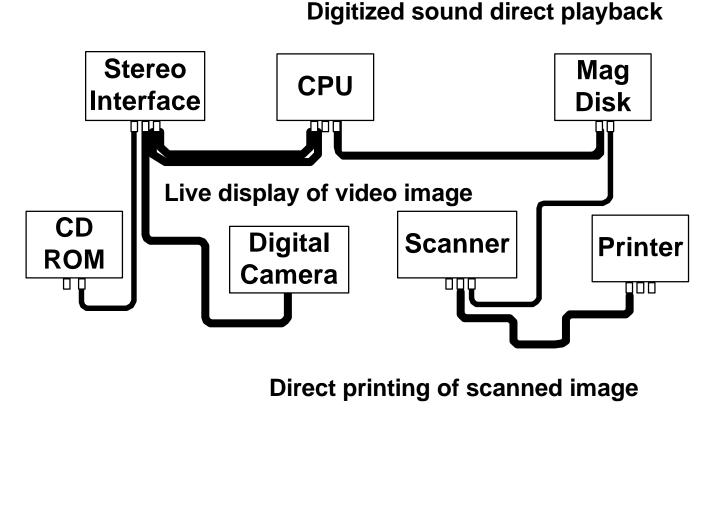

### Data paths (peer-to-peer)

Michael Johas Teener / 1394 Technical Summary (Permission to copy granted as long as this notification is retained. Based on 5/96 1394 Technical Summary from Apple Computer.)

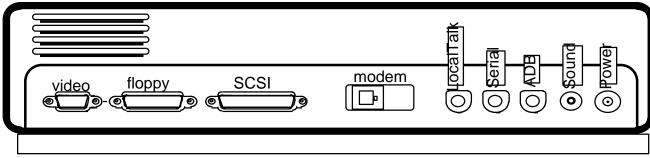

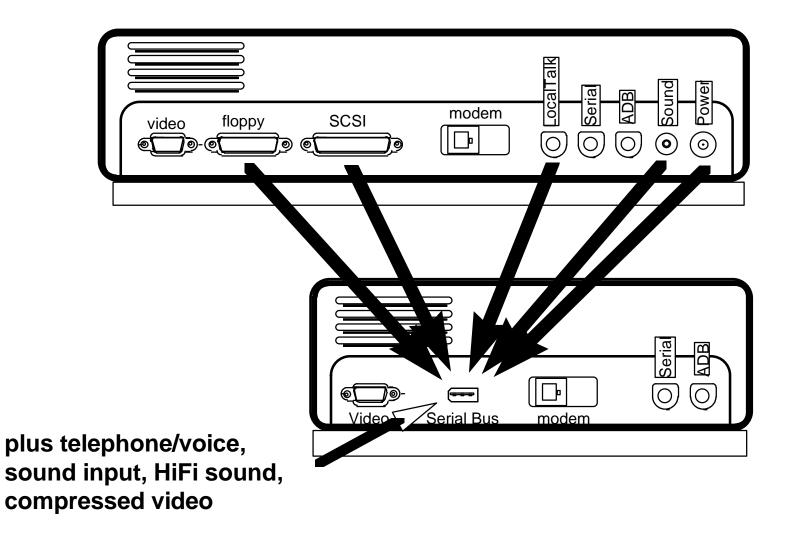

## **Clean up the desktop cable mess!**

© 1996 Firefly, Inc

# Protocols

### IEEE 1394-1995 High Speed Serial Bus

- "Memory-bus-like" logical architecture

- Serial implementation of 1212 architecture

#### ♦ IEEE 1212-1991 CSR Architecture

- Standardized addressing

- Well-defined control and status registers

- Standardized transactions

### X3T10 Serial Bus Protocol and IEEE P1285

- Integration of DMA into I/O process

- SBP is based on SCSI-3 CDB structures

- IEEE P1285 treats disk as software-managed slow cache

© 1996 Firefly, Inc

## **Some terminology**

- "quadlet" 32-bit word

- "node" basic addressable device

- "unit" part of a node, defined by a higher level architecture ...

examples:

- SBP disk drive (X3T10 standard)

- A/V device VCR, camcorder (1394 TA standard)

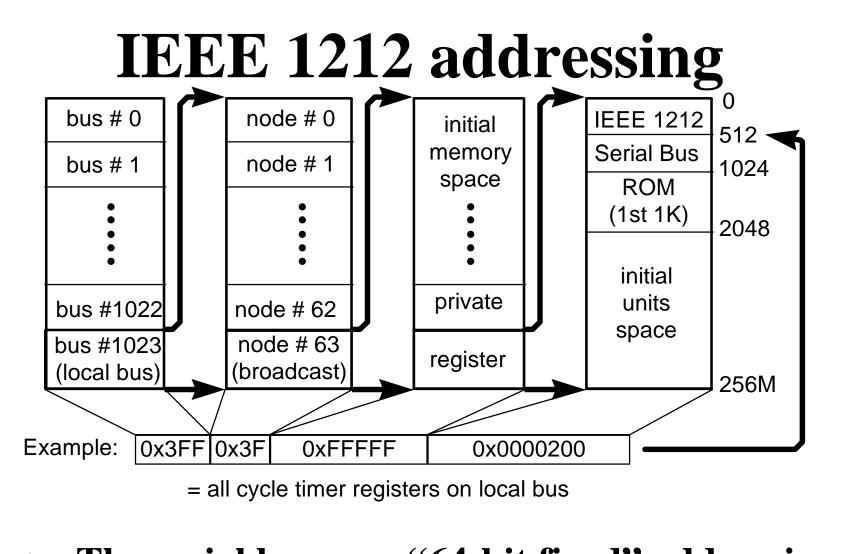

#### The serial bus uses "64-bit fixed" addressing

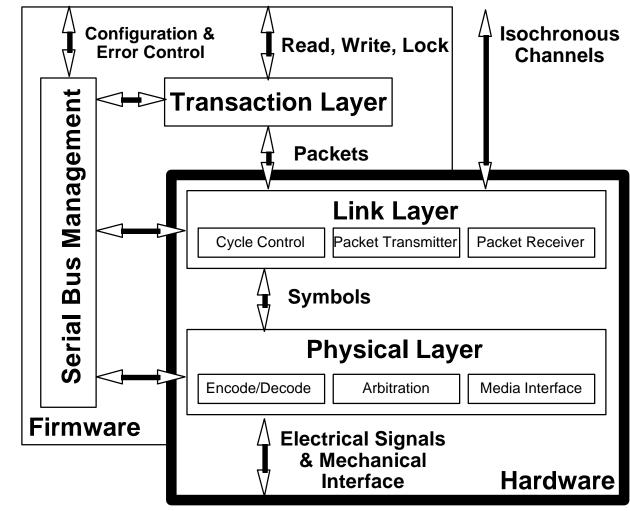

# **IEEE 1394 protocol Stack**

© 1996 Firefly, Inc

Michael Johas Teener / 1394 Technical Summary (Permission to copy granted as long as this notification is retained. Based on 5/96 1394 Technical Summary from Apple Computer.)

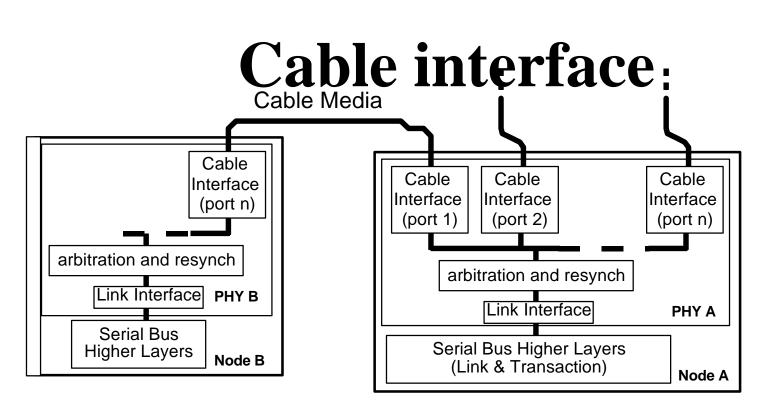

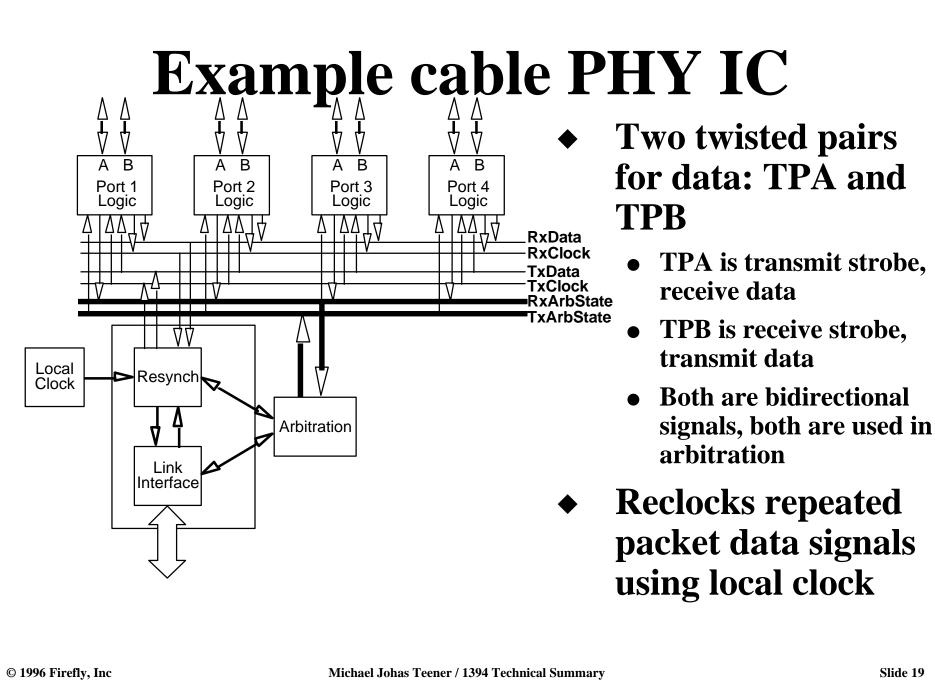

- PHY transforms point-to-point cable links into a logical bus

- Cables and transceivers are bus repeaters

- Baseline limit of 4.5 m between nodes

- farther possible with thicker cables or <400 Mbit/sec

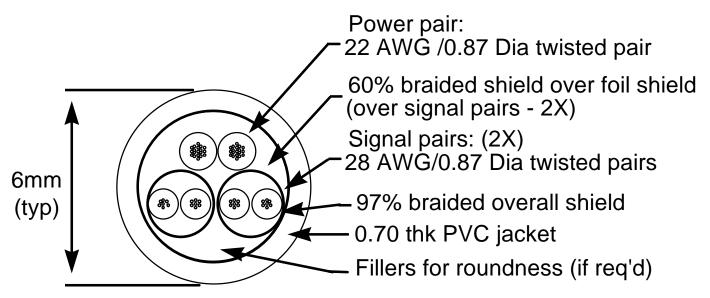

## Cable media

- 3-pair shielded cable

- Two pairs for data transport

- One pair for peripheral power

- Small and rugged connector

- Two sockets in the same area as one mini-DIN socket

- CMOS transceiver

- 220 mv differential

- 4 ma drive

- < 500 ps worst case jitter

Capable of operation at 400 Mbit/sec for 4.5 m

Slightly thicker wire allows 10 meter operation

## **Cable interface features**

#### Live attach/detach

- System protected from power on/off cycling

- Higher layers provide simple management

# **Peripheral power**

- ♦ 8-40 VDC carried by cable

- Total available power is system dependent

- Node power requirements must be declared in configuration ROM

- Cable system allows up to 1.5 A (60 watts) per link

- Nodes can either source or sink power

- Multiple power sources on one bus provide additional flexibility

### 1394 TA defining tighter standards

# **Physical layer**

- 98.304 Mbit/sec half duplex transport

- Data reclocked at each node

- 196.608, 393.216, ... Mbit/sec growth paths

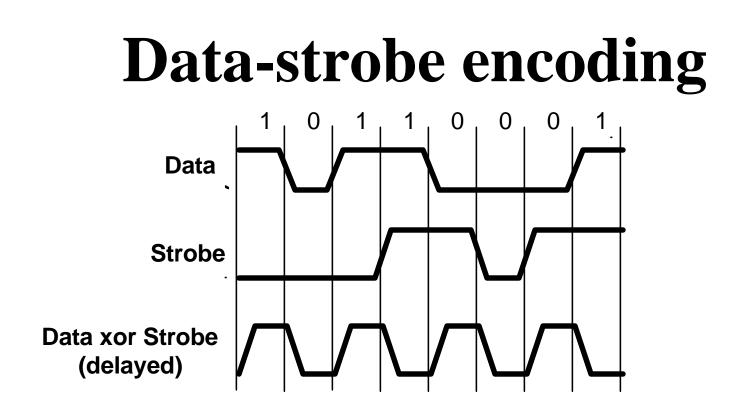

- Data encoding

- Data and strobe on separate pairs

- Automatic speed detection

- Fair and priority access

- Tree-based handshake arbitration

- Automatic assignment of addresses

(Permission to copy granted as long as this notification is retained. Based on 5/96 1394 Technical Summary from Apple Computer.)

Either Data or Strobe signal changes in a bit cell, not both

• Gives 100% better jitter budget than conventional clock/data

© 1996 Firefly, Inc

Michael Johas Teener / 1394 Technical Summary (Permission to copy granted as long as this notification is retained. Based on 5/96 1394 Technical Summary from Apple Computer.)

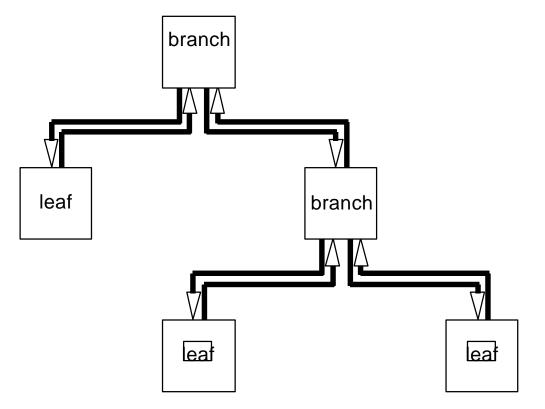

# **Cable arbitration phases**

#### • Reset

• Used whenever reconfiguration needed

• Live insertion & new cycle master are examples

### • Tree Identification

• Transforms a simple net topology into a tree

### Self Identification

- Assigns physical node number (Node ID)

- Exchange speed capabilities with neighbors

#### Normal Arbitration

• Root has highest priority

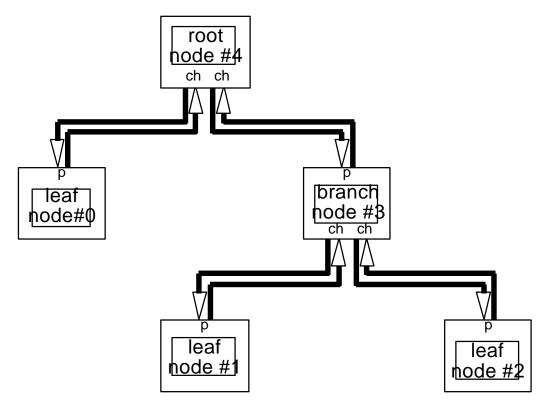

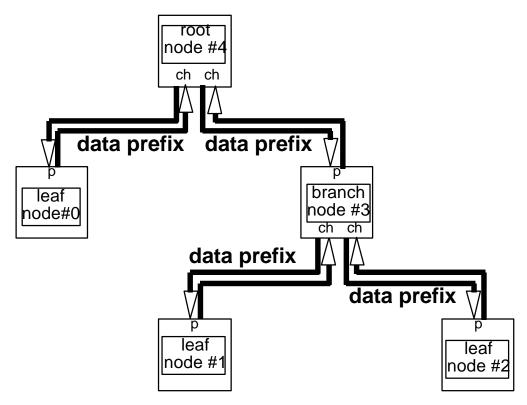

## **Tree identification #1**

After reset, each node only knows if it is a leaf (one connected port) or a branch (more than one connected port)

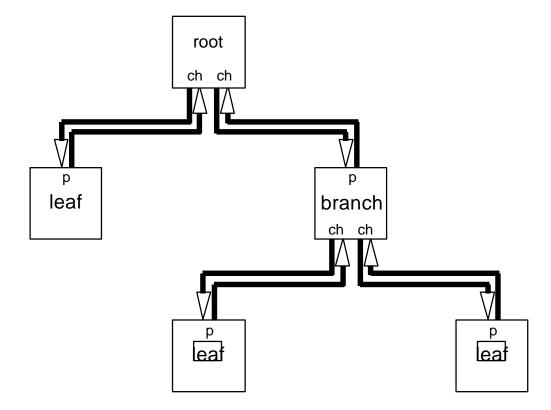

# **Tree identification #2**

- After Tree ID process, the Root node is determined and each port is labeled as pointing to a child or a parent

- Root assignment is "sticky", will normally persist across a bus reset.

© 1996 Firefly, Inc

## Self identification

After the self ID process, each node has a unique physical node number, and the topology has been broadcast

© 1996 Firefly, Inc

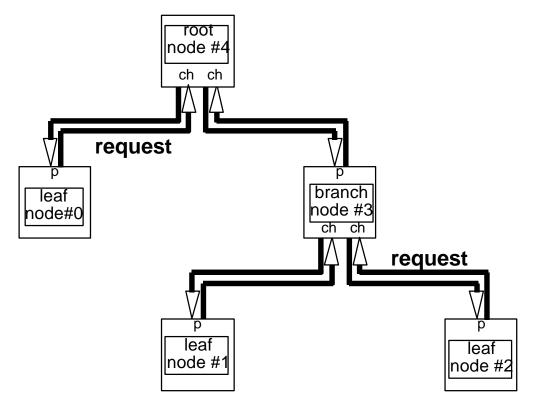

Suppose nodes #0 and #2 start to arbitrate at the same time, they both send a request to their parent ...

The parents forward the request to their parent and deny access to their other children ...

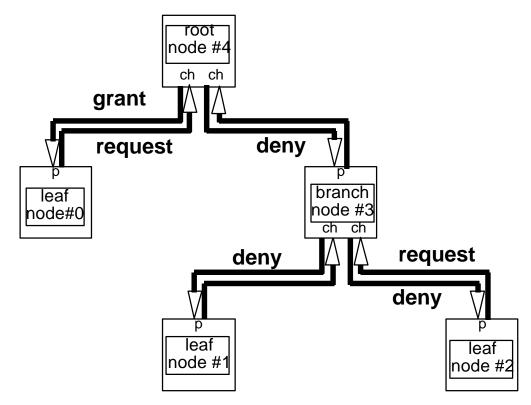

The root grants access to the first request (#0), and the other parent withdraws it's request and passes on the deny ...

• The winning node #0 changes its request to a data transfer prefix, while the loosing node #2 withdraws its request ...

© 1996 Firefly, Inc

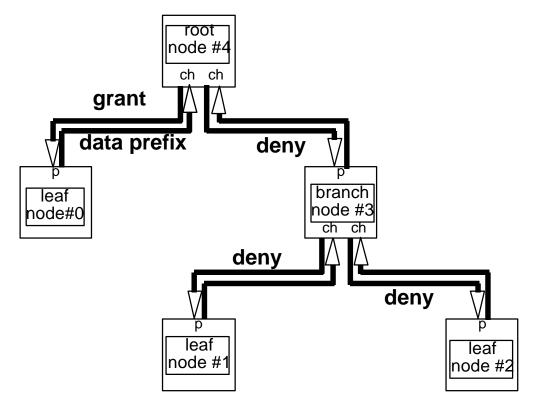

• The parent of node 1 sees the data prefix and withdraws the grant, and now all nodes are correctly oriented to repeat the packet data (a "deny" is a "data prefix!) ...

© 1996 Firefly, Inc

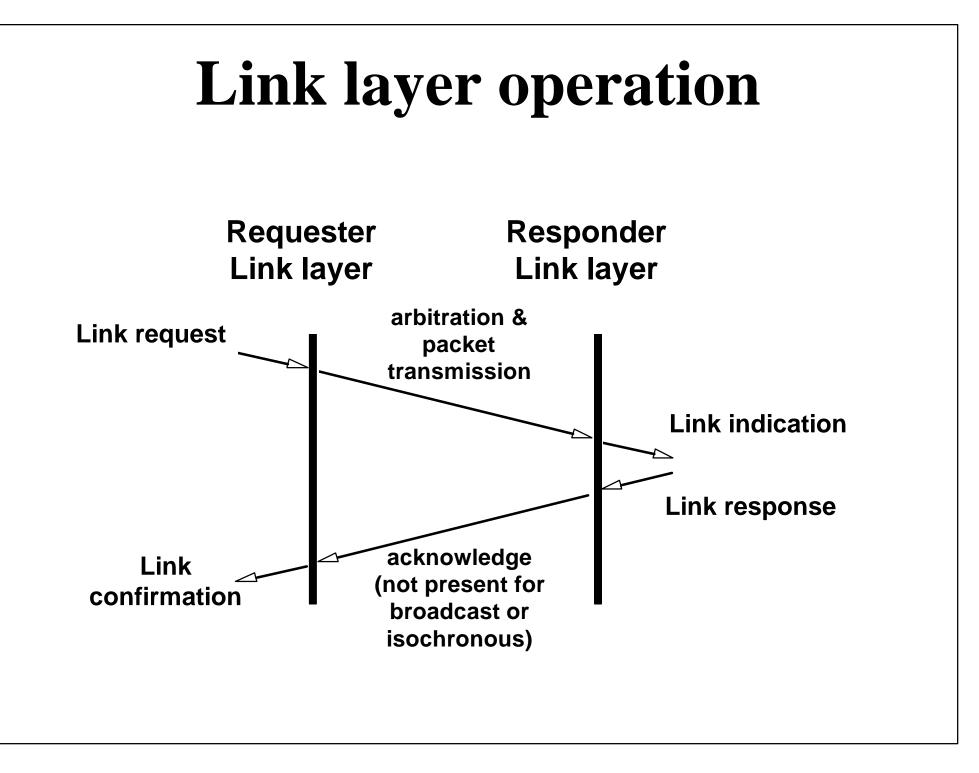

# Link layer

- Implements acknowledged datagram service

- Called a "subaction" of arbitration, packet transmission, and acknowledge

- Flexible addressing using 1212 architecture

- Direct 64-bit addressing (48 bits per node)

- Hierarchical addressing for up to 63 nodes on 1023 busses

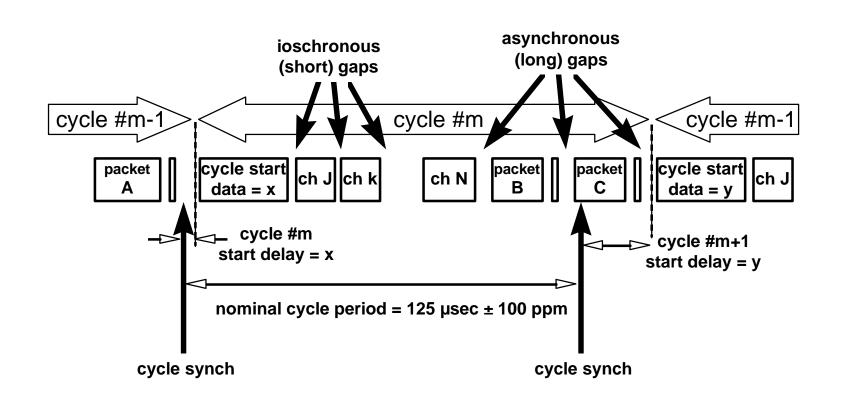

## **Isochronous transport**

### Optional

• But required for multimedia applications

- Multiple "channels" each 125 µsec "cycle" period

- Channel count limited by available bandwidth

- Variable channel size up to -1000 bytes/cycle

- Up to -2000 bytes/cycle at 196 Mbit/sec

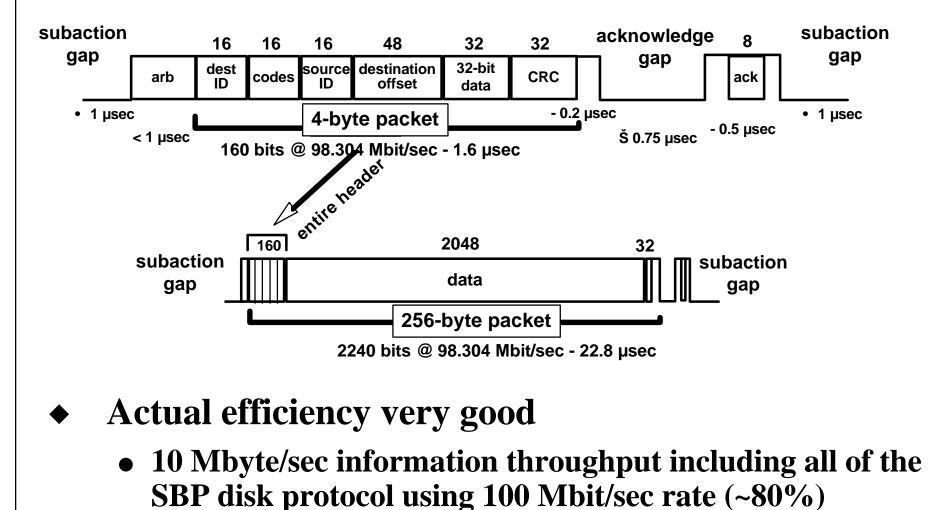

## **Example packets**

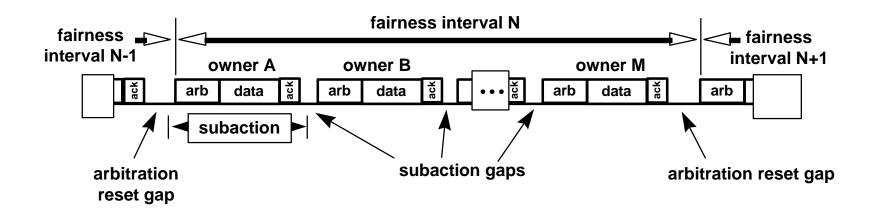

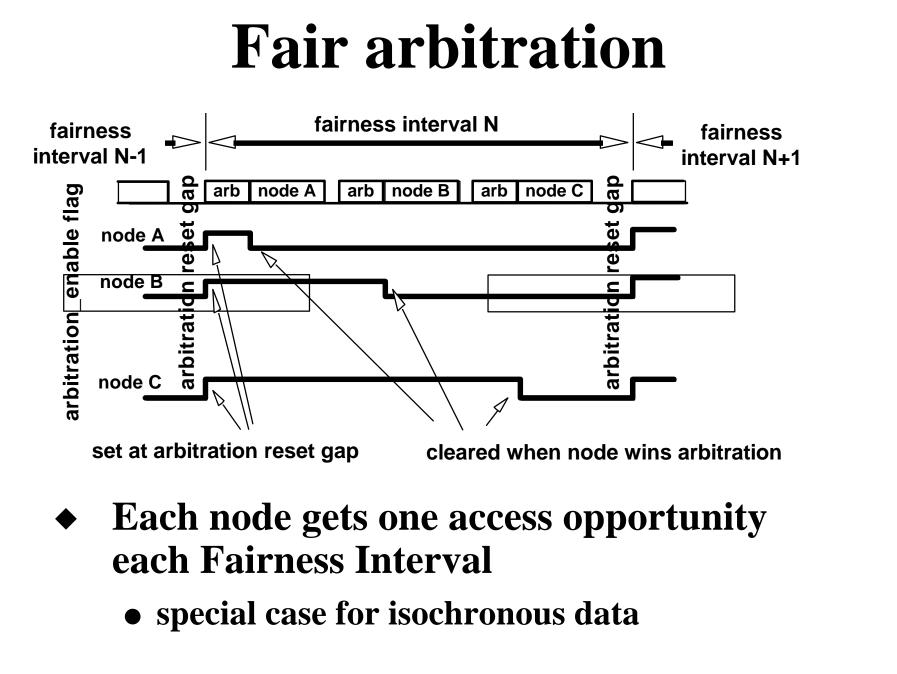

## **Fairness interval**

- Fairness Interval is bounded by "arbitration reset gaps"

- Reset gaps are longer than normal subaction gaps

Slide 35

## **Cycle structure**

• The cycle start is sent by the cycle master, which must be the root node

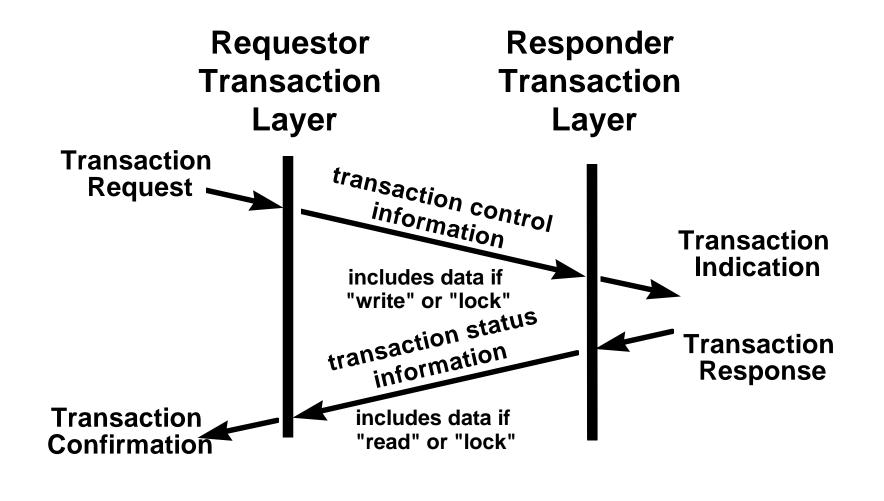

# **Transaction layer**

# **Multiple transaction types**

- Simplified 4-byte (quadlet) read and write are required

- Variable-length block read and write are optional

- Lock transactions optional

- Swap, Compare-and-swap needed for bus management

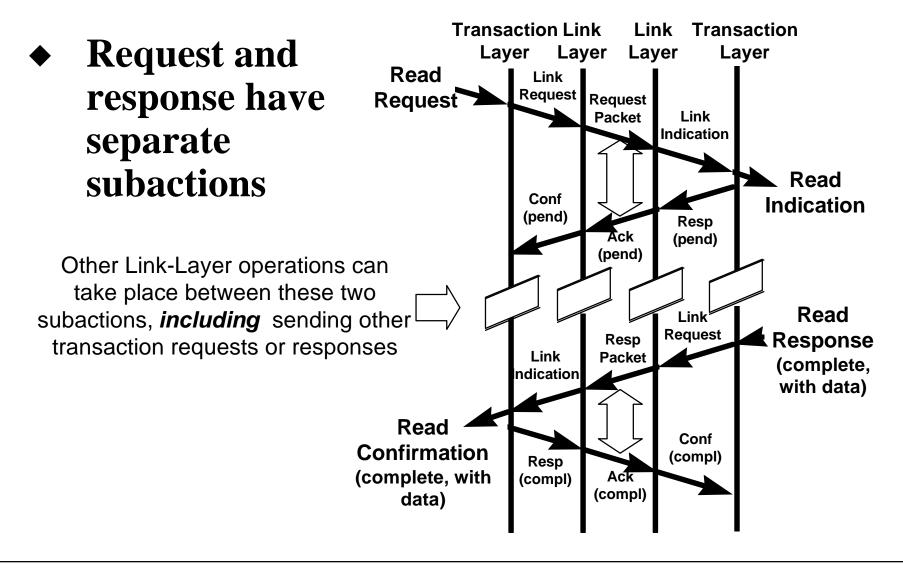

# Efficient media usage

- Split transactions required

- Transactions have request and response parts

- Bus is never busy unless data is actually being transferred

- Request and response can be unified two ways

- "Read" and "Lock" can have concatenated subactions

- "Write" can have immediate completion

## **Split transaction**

**Requester Responder**

## **Concatenated transaction**

Requester Responder Used if Transaction Link Transaction Link Layer Layer Layer Layer responder is fast Read Link Request Request enough to return Request Packet Link Indication data before ack Read is completed Conf Indication (pend) Resp Ack (pend) the responder does not release the bus (pend) Link Read Request after sending the ack, sends response Resp Response Link Packet packet within 1.5µsec (complete, Indication with data) Read Conf Confirmation (compl) Resp (complete, with Ack (compl) (compl) data)

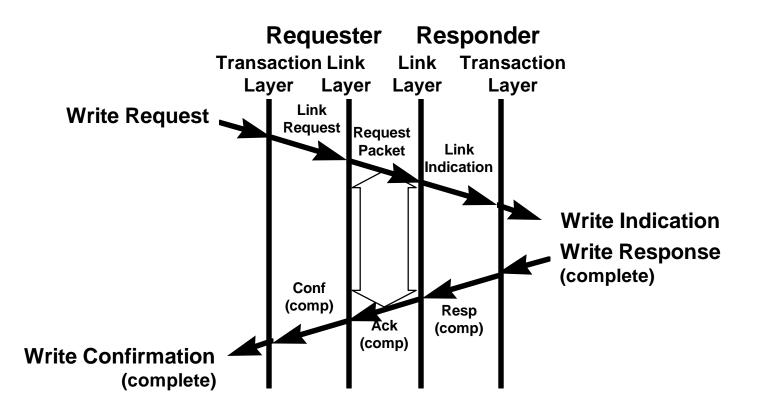

## **Unified transaction**

Only used for write transactions

# **Bus management**

## Automatic address assignment

- Done in physical layer with self-ID process

- Root (cycle master) is "sticky" between bus resets

### • Resource management

- Isochronous channels and bandwidth (also "sticky" ... stay allocated between bus resets).

- Power

## Standardized addresses and configuration ROM from IEEE 1212 architecture

# **Resource management**

- Done with 4 registers, each with compare-swap capability

- Bus manager ID

- holds 6-bit physical ID of current bus manager

- Bandwidth available

- holds 13-bit count of time available for isochronous transmission

- Channels available

- two 32-bit registers with a bit for each of the 64 possible isochronous channels

# **Compare-swap operation:**

- request has "new data" and "compare" values

- responder compares current value ("old data") at requested address with "compare" value

- if equal, the data at the address is replaced with "new data" value

- in all cases, "old data" is returned to requester

# Using compare-swap

#### **Example: allocate bandwidth**

```

test_bw = read4 (addr = bandwidth_available);

old_bw = test_bw + 1; // force entry into loop 1st time

while (old_bw != test_bw) {

old_bw = test_bw;

new_bw = old_bw - bandwidth_needed;

if (new_bw < 0) fail; // all out of bandwidth

test_bw = compare_swap (addr = bandwidth_available,

new_data = new_bw, compare = old_bw); }

```

test\_bw will be equal to old\_bw if no other node has altered the bandwidth\_available register between the time it was read and the time of the compare\_swap

# Where are the bus resource registers?

- On bus reset PHY builds network, assigns addresses, sends self-ID packets

- power requirements/capabilities, maximum speed rating, port status (child, parent, unconnected)

- "contender" or not

- link (higher layers) running or not

- Highest numbered node with both contender and link-on bit is "isochronous resource manager"

- this is the node that has the four resource manager registers

© 1996 Firefly, Inc

Michael Johas Teener / 1394 Technical Summary

(Permission to copy granted as long as this notification is retained. Based on 5/96 1394 Technical Summary from Apple Computer.)

## Automatic reallocation & recovery of resources • When self\_ID completes:

- all nodes with allocated bandwidth and channels before bus reset reallocate their resources

- after one second:

- nodes with new bandwidth or channel request may ask for new resources

- nodes keep resources they had before bus reset!

- resources allocated to nodes removed from bus are automatically restored!

#### •

Bus manager reallocated the same way

© 1996 Firefly, Inc

# Automatic restart of isochronous operation

### • Root assignment is persistent across bus reset

- Cycle master operation restarts after bus reset if node is still root (normal case)

- Nodes assume that bandwidth and channel allocations are still good

- Automatically restart sending when receive cycle start

- Only fails if two operating subnets are joined

- If reallocation fails, node terminates sending

- If bus overallocated, cycle master detects isoch data sent for longer than 100 µsec and stops sending cycle starts

## Futures

• Gigabit rates (P1394A high speed)

• 800 Mbit/sec - 3.2 Gbit/sec

- Incremental addition of nodes without bus reset (P1394A)

- Redundant gap removal (P1394A)

- "Accelerated ACK", fly-by arbitration

- Bridging issues (P1394.1)

- for > 63 devices, or for isolation of highbandwidth local traffic

# How does 1394 help?

## • Much better human interface

- smaller, more rugged connectors with defined usage

- Hot plugging, no manual configuration

## Excellent real performance

- High true data rates

- Direct map to processor I/O model

- DMA is simple: CPU memory directly available to peripherals

- examples: SBP and IEEE 1285 support direct scatter/gather buffers

# ... but even more important

## • It's inexpensive

- For computers, it's already almost as cheap as single-ended 8-bit SCSI

- will be cheaper since it's silicon-intensive

- Much less expensive for peripherals and consumer electronics

- Direct support for isochronous data

- Likely choice for digital consumer video, high-end audio

- Media servers get cheaper

# **Getting documentation**

### "IEEE 1394-1995 High Performance Serial Bus"

- IEEE Standards Office +1-908-981-1393

- http://www.ieee.org

- Internet email reflector

- "p1394@Sun.COM" and "p1394.1@Sun.COM"

- Administrator is "Bob.Snively@Eng.Sun.COM"

- ♦ 1394 Trade Association

- http://www.1394ta.org