#### Implementation Examples

Peter Teng Staff Engineer S3, Inc.

December 18-19, 1996

Peter Teng / 1394 Open HCI, Implementation Examples

Slide 1

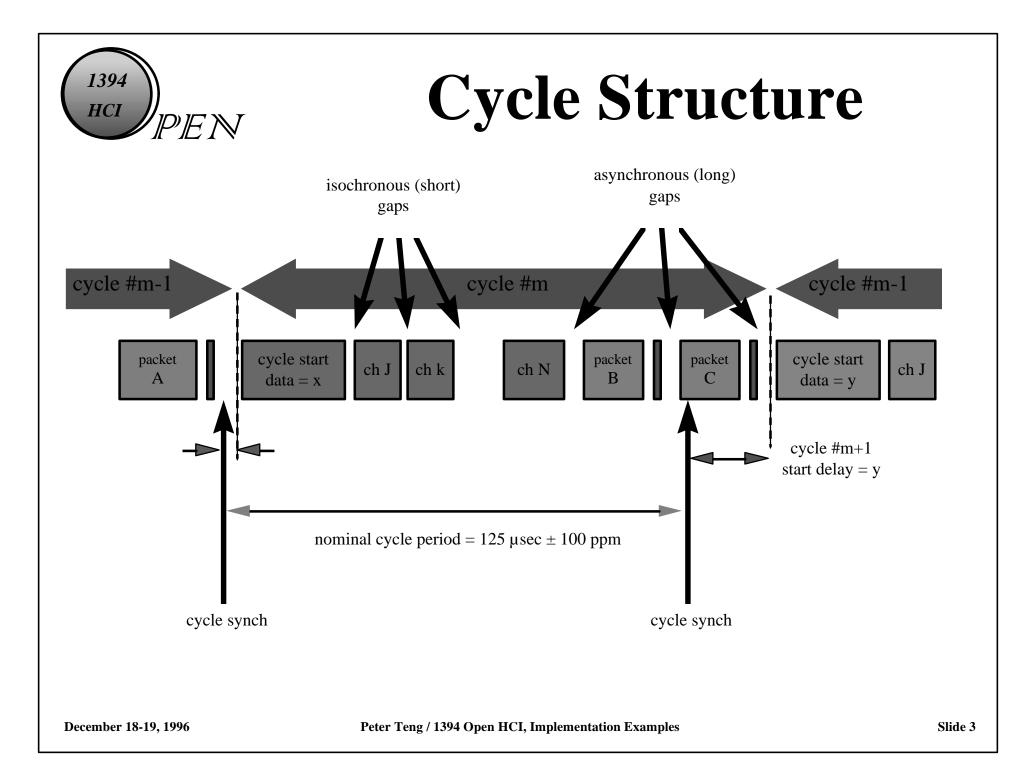

# **Isochronous timing**

Calculate timings for isochronous packets, and its effect on PCI FIFO requirement

#### Time Components of High Efficiency Isochronous Packet

| Timing parameter                    | time (µs) |

|-------------------------------------|-----------|

| speed_signal with data_prefix       | .10       |

| post_speed signal data_prefix       | .04       |

| Iso packet @400Mbps                 | 83.58     |

| max size of (4096B Data+12B Header) |           |

| Min. packet separation              | .34       |

| Iso packet @400Mbps                 |           |

| size of (758B Data+12B Header)      | 15.67     |

| data end time                       | .24       |

| Total                               | ~100.00   |

| Peak bandwidth                      | 50MB/s    |

| Average bandwidth                   | 48.7MB/s  |

| 1394<br>HCI<br>PEN    | ]                | PCI FIFO Size<br>Test Case #1 |                |            |  |

|-----------------------|------------------|-------------------------------|----------------|------------|--|

|                       |                  |                               | secon<br>pack  |            |  |

| data prefix           | 100              | first packet                  | data prefix    | data end   |  |

|                       | 100usec          |                               |                | → 32usec → |  |

| 1394 bus              |                  | ¥                             | * *            | ×          |  |

| PCI burst             |                  |                               | XINGER         |            |  |

| <del>300</del><br>250 |                  |                               |                |            |  |

| 250<br>200            |                  |                               |                |            |  |

|                       |                  | $\wedge \wedge \vee$          |                | <u> </u>   |  |

| <del>150</del>        |                  | lated data in FIFO            |                |            |  |

|                       |                  |                               |                |            |  |

|                       |                  |                               |                |            |  |

| • w                   | ith 2.5usec a    | arbitrati                     | on latenc      | v and      |  |

|                       |                  |                               |                |            |  |

| b                     | urst size of 3   | 52                            |                |            |  |

| December 18-19, 1996  | Peter Teng / 139 | 94 Open HCI, Implementa       | ntion Examples | Slide      |  |

| 1394<br>HCI<br>PEN          | PCI FIFO Size<br>Test Case #2                          |  |  |

|-----------------------------|--------------------------------------------------------|--|--|

|                             |                                                        |  |  |

| data prefix                 | packet<br>first packet data prefix data end            |  |  |

| 1394 bus                    |                                                        |  |  |

|                             |                                                        |  |  |

| PCI burst<br><del>300</del> |                                                        |  |  |

| 250                         |                                                        |  |  |

| 200                         |                                                        |  |  |

| <del>150</del>              |                                                        |  |  |

| <del>100</del><br>50        | Accumulated data in FIFO                               |  |  |

|                             |                                                        |  |  |

|                             | ith 1.6usec arbitration latency and urst size of 32    |  |  |

| December 19 10 100/         | Deter Tang / 1204 On an HOL Interlander to the English |  |  |

December 18-19, 1996

Peter Teng / 1394 Open HCI, Implementation Examples

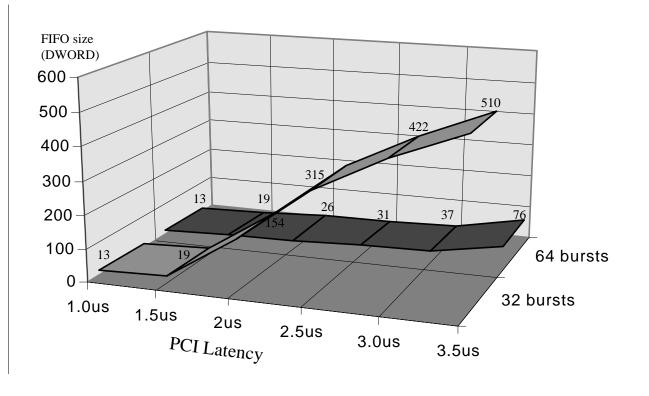

#### Relationship between Burst size, Latency and FIFO length

Peter Teng / 1394 Open HCI, Implementation Examples

# **Isochronous Receive Operation**

- Link receives isochronous packet and header CRC is checked OK

- Search through isochronous receive context control registers for multichannel mode support

- if found, check corresponding bit in the IRMultiChanMask\* registers is enabled. If enabled, fetch context descriptor from CommandPtr register.

# **Isochronous Receive Operation**

- if multiChanMode is not found, search through all IRContextMatch registers for channel number match. If match found, fetch the context descriptor from CommandPtr register. Or else, the packet is ignored.

- Get the dataaddress pointer from the descriptor and start unloading the data.

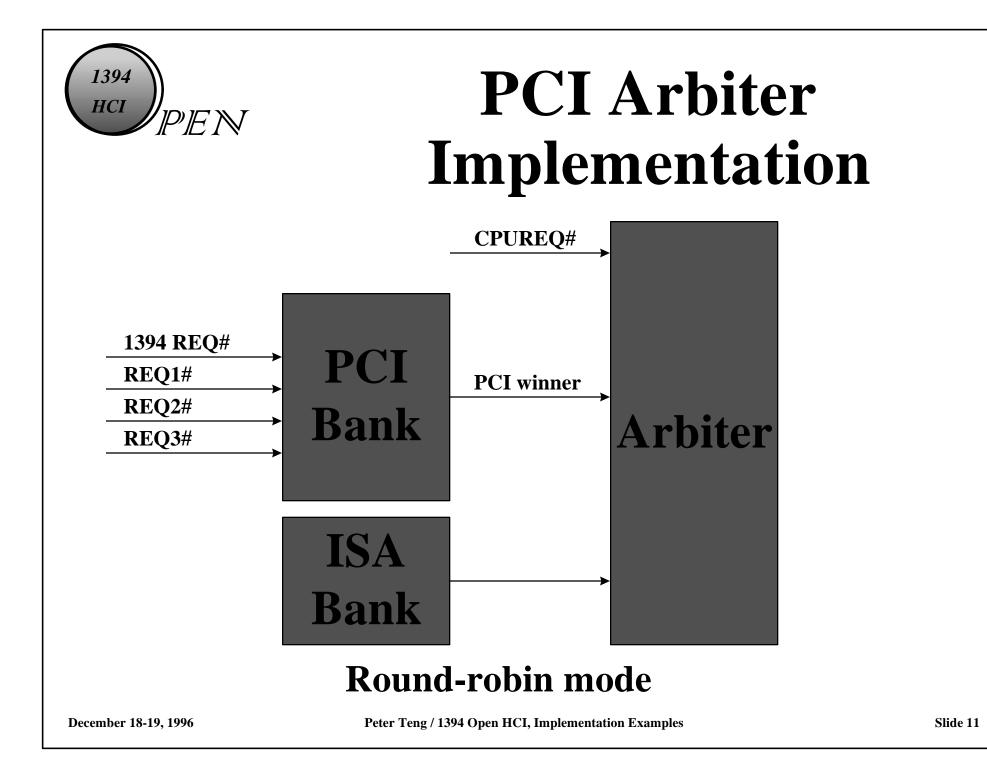

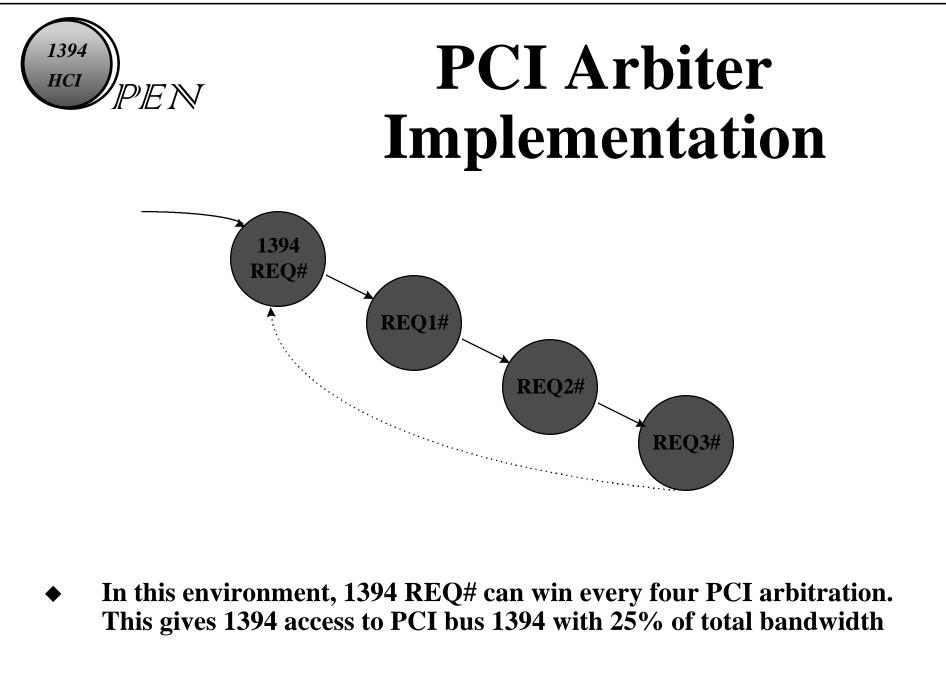

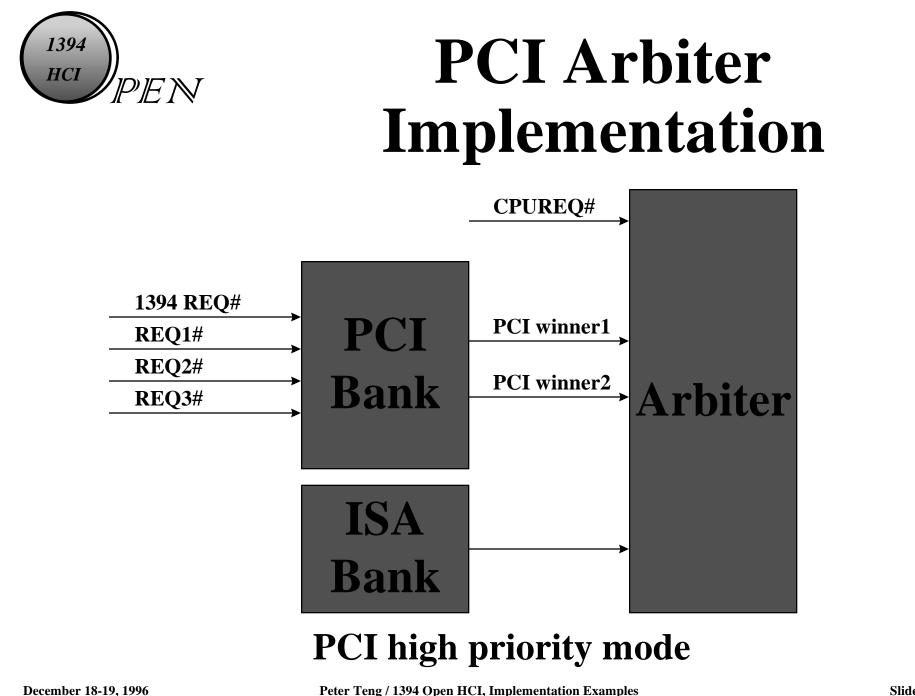

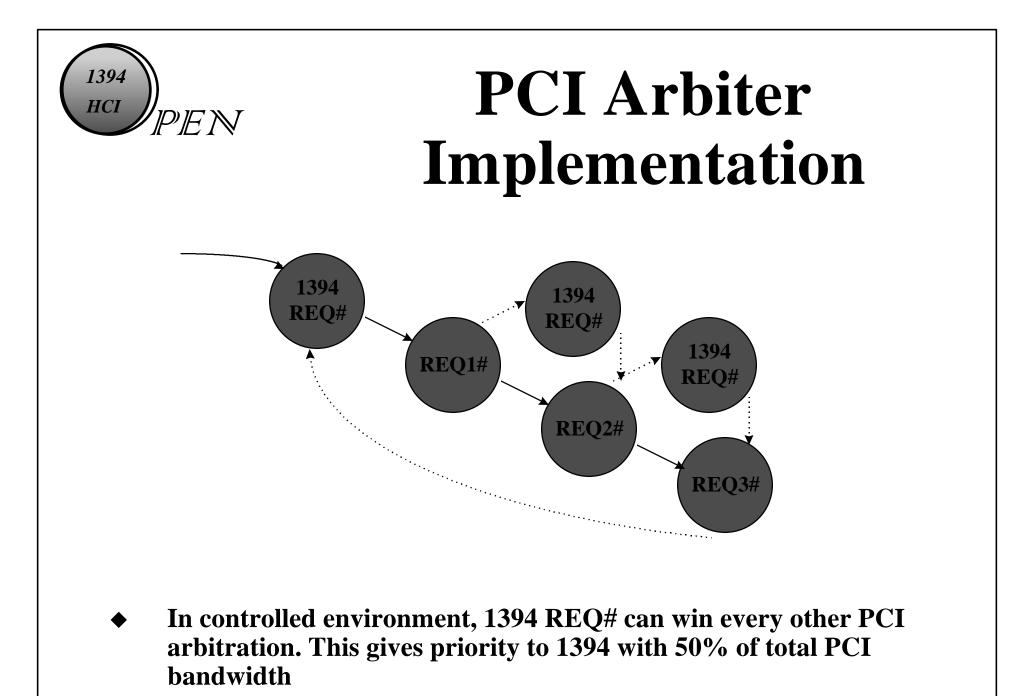

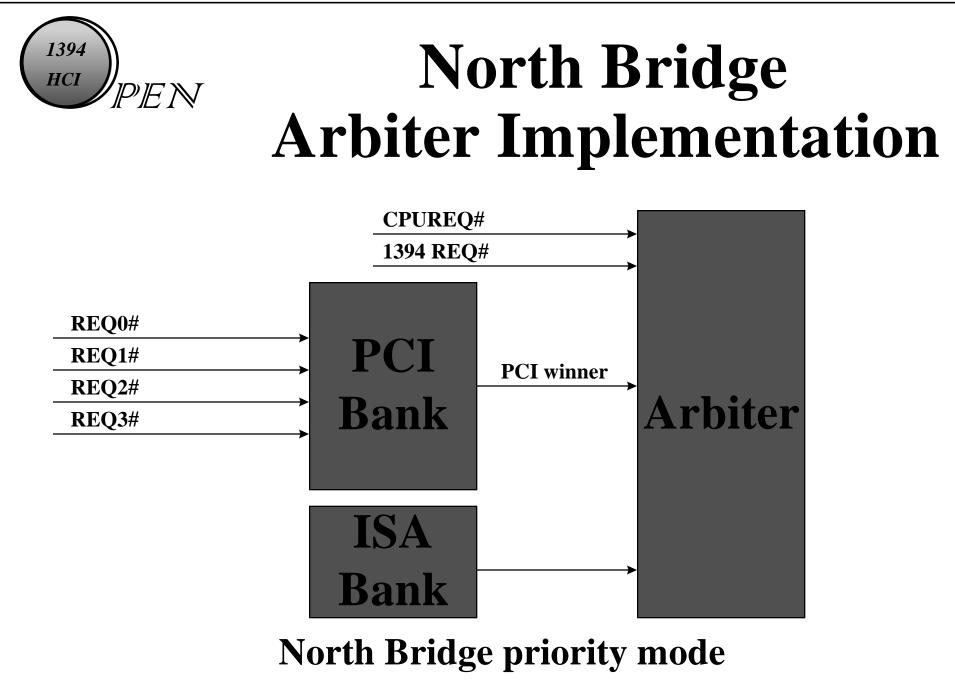

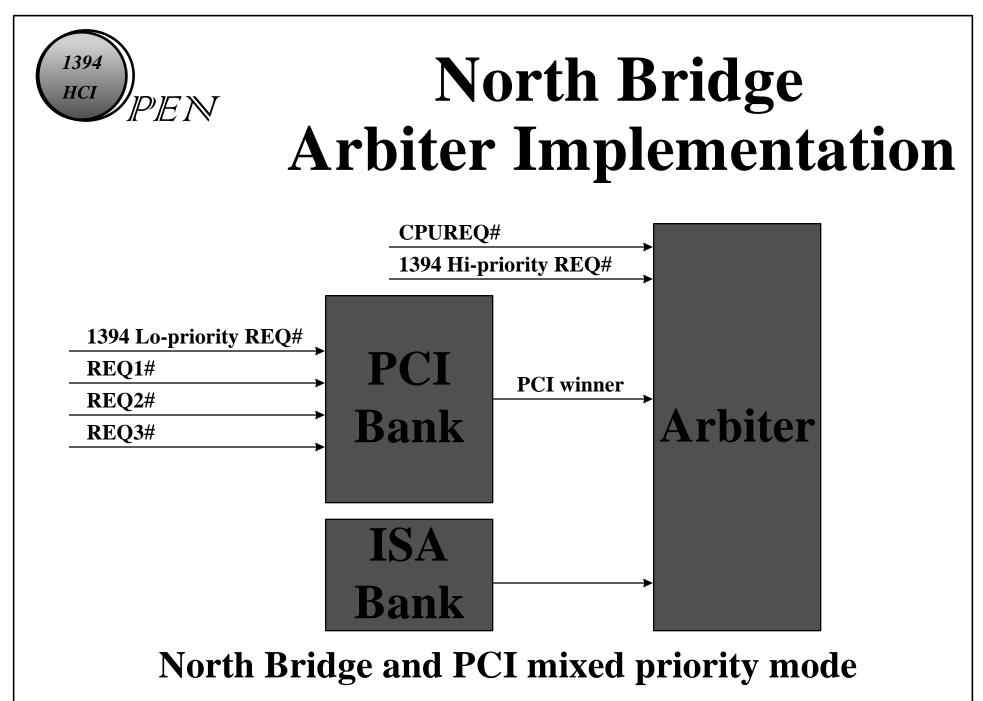

# **PCI** Arbiter

- Implementation reflects the time to assert the GNT# signal line of a PCI bus master that asserted its REQ# signal line to request bus ownership

- Arbitration algorithm of the central arbiter and the priority of the PCI resources requesting bus ownership affect the FIFO requirement

- Predictability and low latency are important

mentation Ex

Slide 13

December 18-19, 1996

Peter Teng / 1394 Open HCI, Implementation Examples

Slide 15

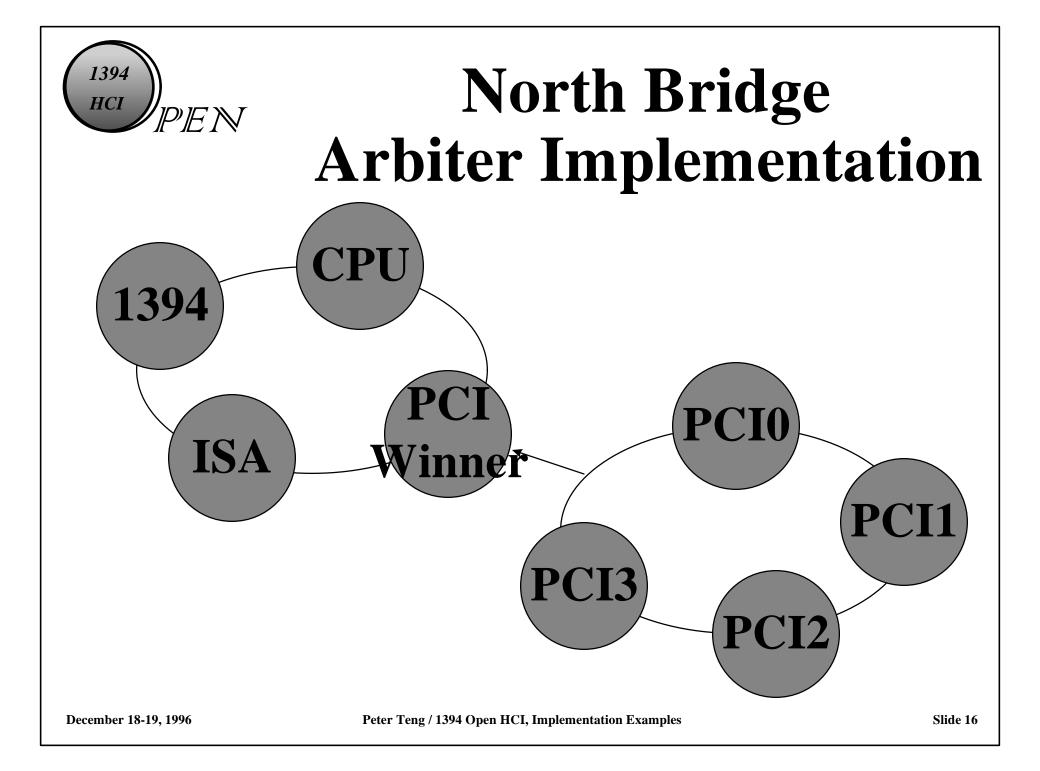

December 18-19, 1996

Peter Teng / 1394 Open HCI, Implementation Examples

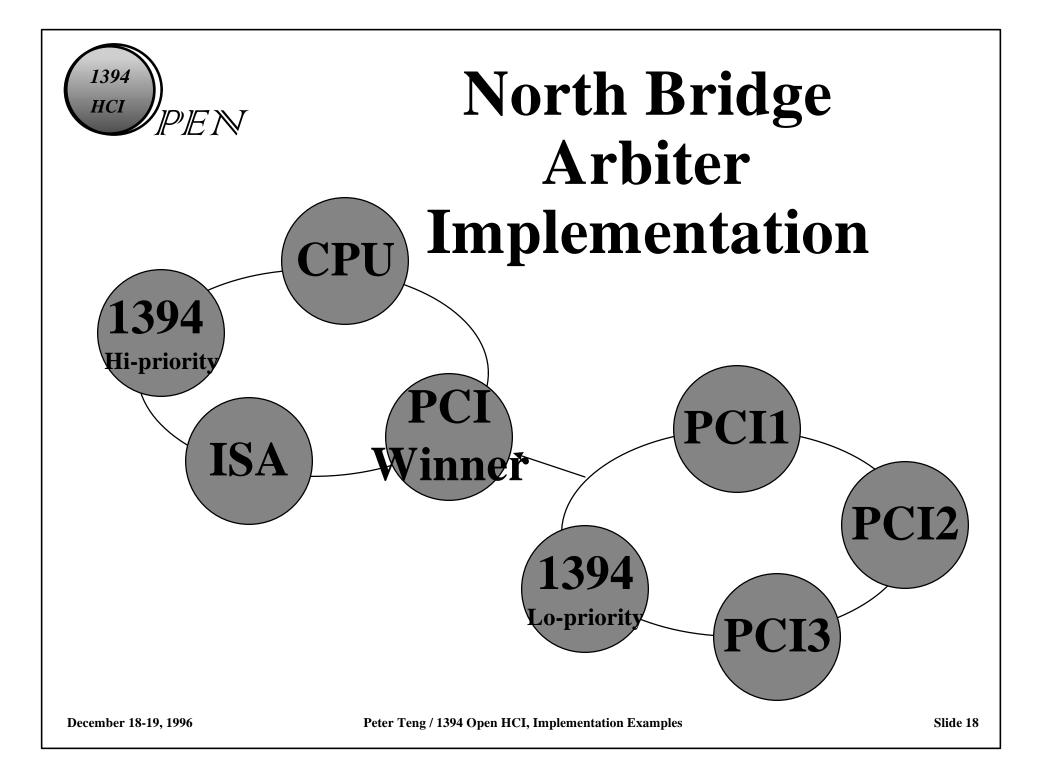

#### High Priority Arbitrations

- Physical read and write requests if phyReqResources\* are enabled to allow concatenated asynchronous subaction

- Isochronous receive for fetching input\* descriptors

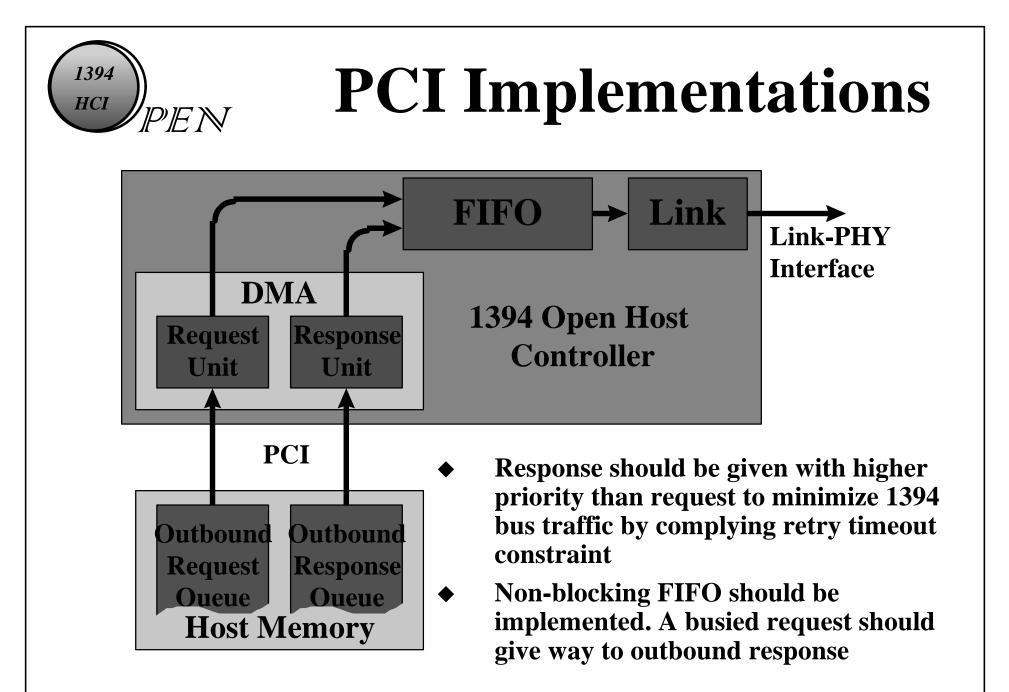

# **PCI Features Needed**

• FIFO requirement depends on

- long bursts

- fastest possible TRDY# as a target

- continuous IRDY# as initiator

- fast back-to-back

- eliminates idle cycle following a write

- memory write and invalidate eliminates system cache snoop

- memory read line multiple

- optimize system memory pre-fetching

#### **PCI Features Needed**

• FIFO requirement depends on

- Corelogic should allow bus master to perform more than one transaction per arbitration

- This allows the arbiter to maintain ownership of the bus after completion of the current transaction. This is particular useful for continuous operation during descriptor fetching and data moving.

# Bus Management CSR Register Operation

- To update the Bus Management CSR registers:

- updates csrData with the desired value

- updates csrCompare with the current value

- updates csrSel with proper offset

- the csrData should have the old content as the one updated in the csrCompare value if compare-swap operation is successful when csrDone is set.

# Bus Management CSR Register Operation

- To read the Bus Management CSR registers

- updates the csrData and csrCompare with the same arbitrary values

- updates the csrSel with proper offset

- the value is returned on the csrData if csrDone is set

#### • Disable control per port

This ensures the Open HCI systems is safe from the external environment by running only on the internal nodes

- During self-ID process, the maximum physical\_ID remains at 63 if more than 63 nodes are on the local bus. No roll over of physical\_ID is allowed.

- Any PHY of physical\_ID of 63 will ignore link-on and PHYconfiguration packet.

- Link of physical\_ID of 63 will not send any packet

- Bus manager algorithm must support 3 bit speed code.

- If LK\_EVENT.ind(cycle\_too\_long) is set, CONTROL.cyclemaster is cleared.

- The cycle\_too\_long is defined as since the last cycle start packet was received, an 125usec has passed, and a subaction gap was not yet detected.

- A timeout interrupt for PHY register read shall be implemented.

- Response in first try need not to follow the fairness protocol

#### **BUS INFO BLOCK Implementations BUS INFO BLOCK is loaded by:**

- Hardware loaded after chip reset by serial or parallel ROM.

- Software loaded during execution of boot code

### **BUS INFO BLOCK Implementations**

- Global Unique ID may only be written once either by hardware or software and shall be writeprotected afterward

- No linkEnable shall be enabled before the Global Unique ID is written

#### Source node's BUS ID in Response Packet

- Two BUS IDs may be used from requesters to identify the node

- 10'h3FF (local-bus) or Specific BUS ID assigned from bus manager

- Same ID shall be used for read response packet as was used in the request packet

#### Source node's BUS ID in Response Packet

- Bit 23 SrcBusID of the first quadlet in the packet header is provided to the link layer on which BUS ID to be used in the response packets

- 0 10'h3FF is used

- 1 NodeID.BusNumber is used

#### Other Implementation Details

- OpenHCI implements only CSR registers of BUS MANAGEMENT CSR, and BUS INFO BLOCK, NODE\_IDS in hardware. All other request packets shall be sent to asynchronous receive or physical request DMA accordingly

- Only quadlet read/compare swap within HCI implemented CSR registers are allowed. Otherwise, type error in response code is returned.