#### **IBM Connect 2015**

Seize the Moment 06/02/15

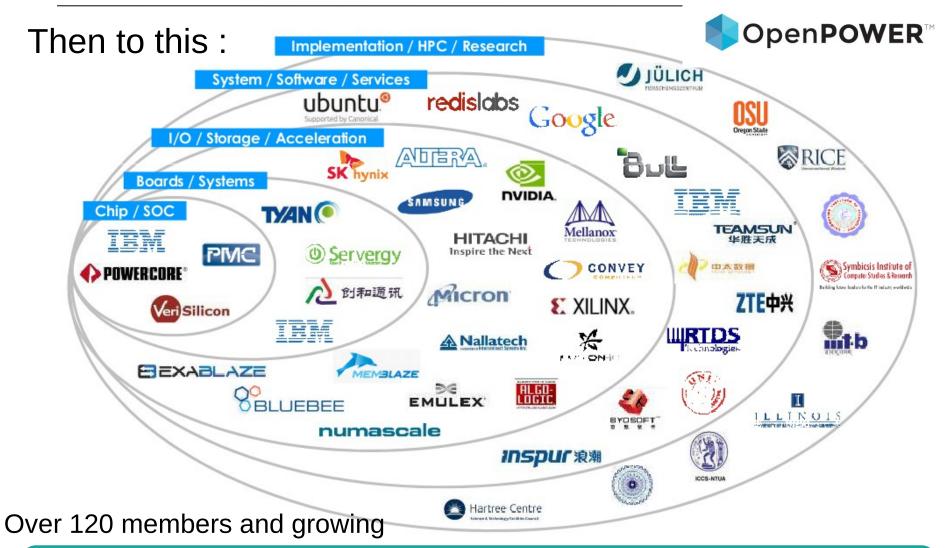

# The OpenPOWER Foundation

How IBM, Google and 120 others are reinventing the datacenter

#### **Franz Bourlet**

Power Systems Technical Sales IBM Belgium & Luxembourg

# New ways of acquiring servers

# The number of companies designing and building servers is increasing:

- Traditionally there have been few companies designing systems:

HP, IBM, SUN, Dell, etc.

- Today there are many more: Google, Microsoft, Facebook, Rackspace, Huawei, Sugon, Inspur, etc.

- A fairly mature ecosystem including the Taiwanese ODMs is a key enabler of this trend

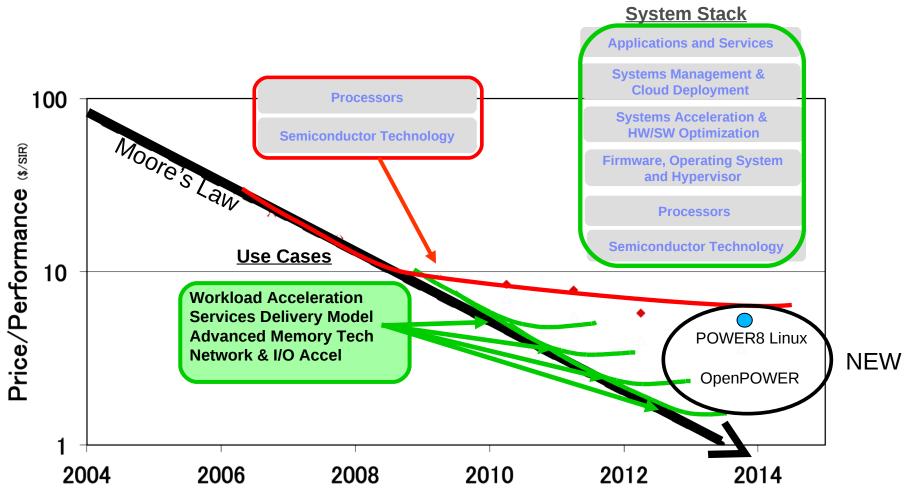

# Industry trends drive innovation beyond the chip

Microprocessors alone no longer drive sufficient Cost / Performance improvements

System stack innovations are required to drive Cost/Performance

## ARM Ltd: another economic model

- Founded in November 1990 www.arm.com

- Spun out of Acorn Computers

- Runs 95% of mobile phones and tabs

- Arm designs a range of RISC processor cores but does not fabricate silicon itself

- Licenses ARM core designs to semiconductor partners who fabricate and sell to their customers

- Examples include Apple, Samsung, Nvidia, Qualcomm,...

- Also develops technologies to assist with the design-in of the ARM architecture

- Software tools, boards, debug hardware, application software, bus architectures, peripherals, etc

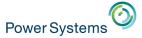

## POWER has evolved into the ARM of the datacenter: from this...

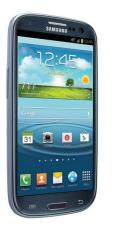

#### **IBM Research: Innovation Strengthens the Stack**

### **IBM** is Unique in the World

- No other company plays in all the layers. IBM is world-class in all layers

- Those that play in multiple layers are world-class only in few.

#### **IBM R&D investment**

- \$6 Billion annually

- Human capital and culture

- 3000+ Researchers

- 6478 U.S. patents in 2012

- Patent leader past 20 years

As CMOS scaling slows, Value comes from Innovating across the Stack

## To this...

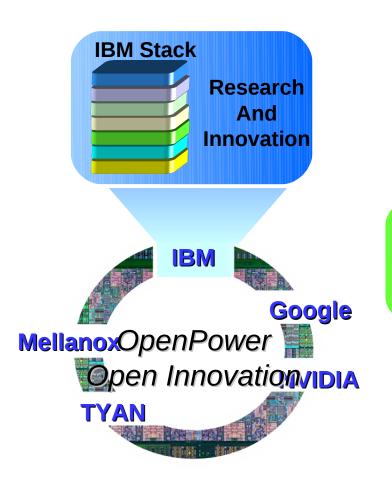

#### **IBM POWER8**

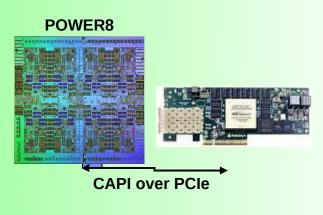

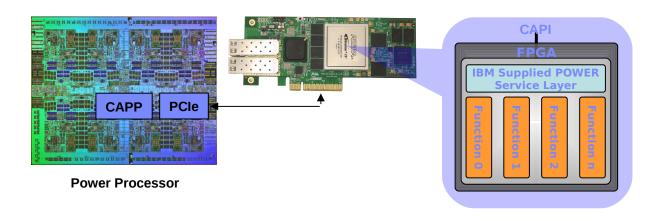

## CAPI / PCI G3

Directly Integrate

Partner IP into Power8

Chip protocols

# Mellanox World class Networking and

Mellanox

World class

**Networking and**

Switching

Switching

#### Google

IDC System, Software Stack

#### **NVidia**

World class

GPU Compute

Capabilities

The goal of the OpenPOWER Foundation is to create an open ecosystem, using the POWER Architecture to share expertise, investment and server-class intellectual property to serve the evolving needs of customers.

Hardware

# The most open server architecture in the industry

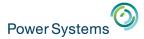

#### **System Operating Environment Software Stack**

A modern development environment is emerging based on this type of tools and services

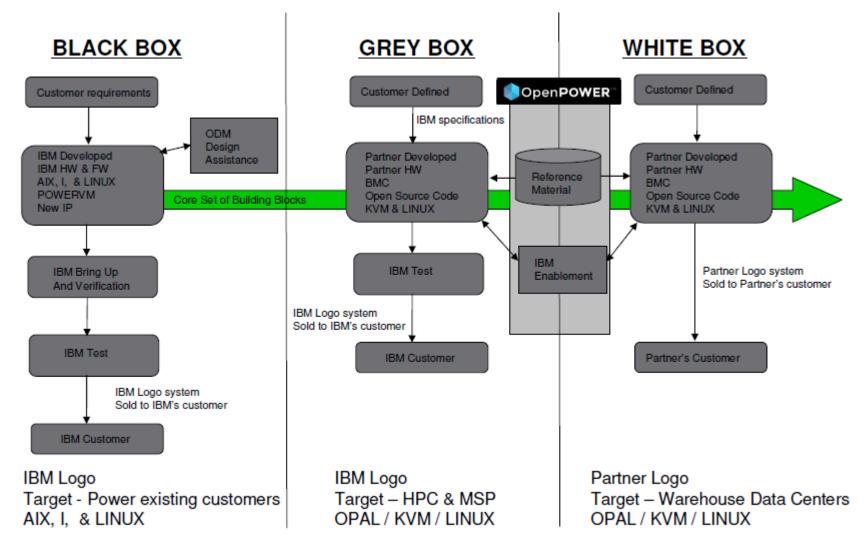

#### **Multiple Options to Design with POWER Technology Within OpenPOWER**

"Standard POWER Products" – 2014

# Framework to Integrate System IP on Chip

Customizable

#### **Industry IP License Model**

"Custom POWER SoC" - Future

|                       | Sandy<br>Bridge EP<br>E5-x6xx | Ivy Bridge<br>EP<br>E5-26xx v2 | Ivy Bridge<br>EX<br>E7-88xx v2 | Haswell<br>EP<br>E5-26xx v3 | POWER 7+<br>Systems | POWER8              |

|-----------------------|-------------------------------|--------------------------------|--------------------------------|-----------------------------|---------------------|---------------------|

| Clock rates<br>(GHz)  | 1.8–3.6                       | 1.7-3.7                        | 1.9-3.4                        | 1.6-3.5                     | 3.1–4.4 GHz         | 3.0-4.1<br>GHz      |

| SMT options           | 1,2*                          | 1, 2*                          | 1, 2*                          | 1, 2*                       | 1, 2, 4             | 1, 2, 4, 8          |

| Max Threads /<br>sock | 16                            | 24                             | 30                             | 36                          | 32                  | 96                  |

| Max L1 Cache          | 32KB                          | 32KB*                          | 32KB*                          | 64 KB                       | 32KB                | 64KB                |

| Max L2 Cache          | 256 KB                        | 256 KB                         | 256 KB                         | 256KB                       | 256 KB              | 512 KB              |

| Max L3 Cache          | 20 MB                         | 30 MB                          | 37.5 MB                        | 45 MB                       | 80 MB               | 96 MB               |

| Max L4 Cache          | 0                             | 0                              | 0                              | 0                           | 0                   | 128 MB              |

| Memory<br>Bandwidth   | 31.4-51.2<br>GB/s             | 42.6-59.7<br>GB/s              | 68-85**<br>GB/s                | 51-68<br>GB/s               | 100 – 180<br>GB/sec | 230 - 410<br>GB/sec |

<sup>1 =</sup> The Micro-architecture features above contributed to premium performance for the POWER8 systems compared to Ivy Bridge systems

<sup>\*</sup> Intel calls this Hyper-Threading Technology (No HT and with HT)

<sup>\*32</sup>KB running in "Non-RAS mode" 16KB results in better RAS

<sup>\*\*85</sup>GB running in "Non-RAS mode" and dual-device error NOT supported

|                       | Sandy<br>Bridge EP<br>E5-x6xx | Ivy Bridge<br>EP<br>E5-26xx v2 | Ivy Bridge<br>EX<br>E7-88xx v2 | Haswell<br>EP<br>E5-26xx v3 | POWER 7+<br>Systems | POWER8              |

|-----------------------|-------------------------------|--------------------------------|--------------------------------|-----------------------------|---------------------|---------------------|

| Clock rates<br>(GHz)  | 1.8-3.6                       | 1.7-3.7                        | 1.9-3.4                        | 1.6-3.5                     | 3.1-4.4 GHz         | 3.0-4.1<br>GHz      |

| SMT options           | 1,2*                          | 1, 2*                          | 1, 2*                          | 1, 2*                       | 1, 2, 4             | 1, 2, 4, 8          |

| Max Threads /<br>sock | 16                            | 24                             | 20                             |                             | 32                  | 96                  |

| Max L1 Cache          | 32KB                          | 32                             |                                |                             | 32KB                | 64KB                |

| Max L2 Cache          | 256 KB                        | How                            | v fast the                     | engine                      | 256 KB              | 512 KB              |

| Max L3 Cache          | 20 MB                         | 1100                           | v iast tric                    | Crigiric                    | 80 MB               | 96 MB               |

| Max L4 Cache          | 0                             |                                |                                |                             | 0                   | 128 MB              |

| Memory<br>Bandwidth   | 31.4-51.2<br>GB/s             | 42.6-59.7<br>GB/s              | GB/s                           | -1-68<br>GB/s               | 100 – 180<br>GB/sec | 230 - 410<br>GB/sec |

<sup>1 =</sup> The Micro-architecture features above contributed to premium performance for the POWER8 systems compared to Ivy Bridge systems

<sup>\*</sup> Intel calls this Hyper-Threading Technology (No HT and with HT)

<sup>\*32</sup>KB running in "Non-RAS mode" 16KB results in better RAS

<sup>\*\*85</sup>GB running in "Non-RAS mode" and dual-device error NOT supported

|                       | Sandy<br>Bridge EP<br>E5-x6xx | Ivy Bridge<br>EP<br>E5-26xx v2 | Ivy Bridge<br>EX<br>E7-88xx v2 | Haswell<br>EP<br>E5-26xx v3 | POWER 7+<br>Systems | POWER8              |

|-----------------------|-------------------------------|--------------------------------|--------------------------------|-----------------------------|---------------------|---------------------|

| Clock rates<br>(GHz)  | 1.8-3.6                       | 1.7-3.7                        | 1.9-3.4                        | 1.6-3.5                     | 3.1-4.4 GHz         | 3.0-4.1<br>GHz      |

| SMT options           | 1,2*                          | 1, 2*                          | 1, 2*                          | 1, 2*                       | 1, 2, 4             | 1, 2, 4, 8          |

| Max Threads /<br>sock | 16                            | 24                             | 20                             | 36                          | 3Z                  | 96                  |

| Max L1 Cache          | 32KB                          | 32                             |                                | •                           | 32KB                | 64KB                |

| Max L2 Cache          | 256 KB                        | Hov                            | w large the                    | a team                      | 256 KB              | 512 KB              |

| Max L3 Cache          | 20 MB                         | 1100                           | w large tric                   | ctcam                       | 80 MB               | 96 MB               |

| Max L4 Cache          | 0                             |                                |                                |                             | 0                   | 128 MB              |

| Memory<br>Bandwidth   | 31.4-51.2<br>GB/s             | 42.6-59.7<br>GB/s              | GB/s                           | -1-68<br>GB/s               | 100 – 180<br>GB/sec | 230 - 410<br>GB/sec |

<sup>1 =</sup> The Micro-architecture features above contributed to premium performance for the POWER8 systems compared to Ivy Bridge systems

<sup>\*</sup> Intel calls this Hyper-Threading Technology (No HT and with HT)

\*32KB running in "Non-RAS mode" 16KB results in better RAS

<sup>\*\*85</sup>GB running in "Non-RAS mode" and dual-device error NOT supported

|                       | Sand<br>Bri       |                   | Pridge          | Haswell<br>EP<br>E5-26xx v3 | POWER 7+<br>Systems | POWER8              |

|-----------------------|-------------------|-------------------|-----------------|-----------------------------|---------------------|---------------------|

| Clock rates<br>(GHz)  | How a             | bundant t         | the food        | 1.6-3.5                     | 3.1-4.4 GHz         | 3.0-4.1<br>GHz      |

| SMT options           |                   |                   | <               | 1, 2*                       | 1, 2, 4             | 1, 2, 4, 8          |

| Max Threads /<br>sock | 16                |                   |                 | 36                          | 32                  | 96                  |

| Max L1 Cache          | 32KB              | 32KB*             | 32KB*           | 64 KB                       | 32KB                | 64KB                |

| Max L2 Cache          | 256 KB            | 256 KB            | 256 KB          | 256KB                       | 256 KB              | 512 KB              |

| Max L3 Cache          | 20 MB             | 30 MB             | 37.5 MB         | 45 MB                       | 80 MB               | 96 MB               |

| Max L4 Cache          | 0                 | 0                 | 0               | 0                           | 0                   | 128 MB              |

| Memory<br>Bandwidth   | 31.4-51.2<br>GB/s | 42.6-59.7<br>GB/s | 68-85**<br>GB/s | 51-68<br>GB/s               | 100 – 180<br>GB/sec | 230 - 410<br>GB/sec |

<sup>1 =</sup> The Micro-architecture features above contributed to premium performance for the POWER8 systems compared to Ivy Bridge systems

<sup>\*</sup> Intel calls this Hyper-Threading Technology (No HT and with HT)

<sup>\*32</sup>KB running in "Non-RAS mode" 16KB results in better RAS

<sup>\*\*85</sup>GB running in "Non-RAS mode" and dual-device error NOT supported

|                       | Sandy<br>Bridge EP<br>E5-x6xx | Ivy Bridge<br>EP<br>E5-26xx v2 | Ivy Bridge<br>EX<br>E7-88xx v2 | Haswell<br>EP<br>E5-26xx v3 | POWER 7+<br>Systems | POWER8              |

|-----------------------|-------------------------------|--------------------------------|--------------------------------|-----------------------------|---------------------|---------------------|

| Clock rates<br>(GHz)  | 1.8–3.6                       | 1.7-3.7                        | 1.9-3.4                        | 1.6-3.5                     | 3.1-4.4 GHz         | 3.0-4.1<br>GHz      |

| SMT options           | 1,2*                          |                                | 1, 2*                          | 1, 2*                       | 1, 2, 4             | 1, 2, 4, 8          |

| Max Threads /<br>sock |                               |                                |                                | 36                          | 32                  | 96                  |

| Max L1 Cache          | Hov                           | w fast the                     | data                           | 64 KB                       | 32KB                | 64KB                |

| Max L2 Cache          | 1100                          | v rast tric                    | data                           | 256KB                       | 256 KB              | 512 KB              |

| Max L3 Cache          | <b>2</b> 6                    |                                |                                | 45 MB                       | 80 MB               | 96 MB               |

| Max L4 Cache          | 0                             |                                | 0                              |                             | 0                   | 128 MB              |

| Memory<br>Bandwidth   | 31.4-51.2<br>GB/s             | 42.6-59.7<br>GB/s              | 68-85**<br>GB/s                | 51-68<br>GB/s               | 100 – 180<br>GB/sec | 230 - 410<br>GB/sec |

<sup>1 =</sup> The Micro-architecture features above contributed to premium performance for the POWER8 systems compared to Ivy Bridge systems

<sup>\*</sup> Intel calls this Hyper-Threading Technology (No HT and with HT)

<sup>\*32</sup>KB running in "Non-RAS mode" 16KB results in better RAS

<sup>\*\*85</sup>GB running in "Non-RAS mode" and dual-device error NOT supported

# In a nutshell

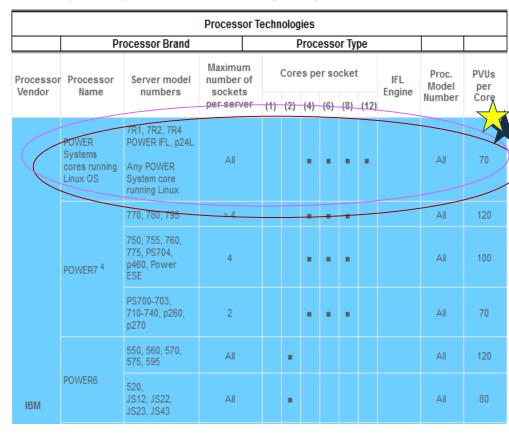

# IBM SWG: 70 PVU on all POWER systems running Linux

- Applies to SWG PVU licensed software products for ALL Power cores running Linux

- 70 PVU pricing previously only available for 1-2 socket servers

- PowerLinux 7R1/7R2, p260/p270 and Power 710/720/730/740

- Intel SandyBridge/IvyBridge servers

- 70 PVU pricing includes:

- Power IFLs

- Power S8xx

- Power E8xx

- Flex System

- Applies to POWER8 and POWER7

#### PVU Table per Core (section 1 of 2 - RISC and System z)

PVU Table link: <a href="http://www-01.ibm.com/software/lotus/passportadvantage/pvu\_licensing\_for\_customers.html">http://www-01.ibm.com/software/lotus/passportadvantage/pvu\_licensing\_for\_customers.html</a>

15

## What's in it for me?

## Consider a mix of workloads requiring 250 cores on x86:

- Scale out approach (2-socket):

- Scale out approach (2-socket):

70 PVU X 250 =

17.500

70 PVU X 100 =

7.000

## What's in it for me?

## Consider a mix of workloads requiring 250 cores on x86:

- Scale out approach (2-socket):

- Scale out approach (2-socket):

7.000

- Optimized scale out (4-socket) :

- Optimized scale out (4-socket) :

## What's in it for me?

## Consider a mix of workloads requiring 250 cores on x86:

- Scale out approach (2-socket):

- Scale out approach (2-socket):

- Optimized scale out (4-socket) :

120 PVU X 250 =

## POWER8 combined with business accelerators

Altera FPGA acceleration and IBM CAPI

Monte Carlo 250x faster than POWER8 core alone, reduced C code 40x over non-CAPI FPGA

AUTRA. IEM

Data Engine for NoSQL 24:1 server

consolidation, 3x lower cost per user, 40TB CAPI-attached flash

CAPI dev kit with FPGA card from Nallatech

US Dept of Energy \$325M super computing contract awarded to IBM, Mellanox, and NVIDIA

DoE systems for science and stockpile stewardship

Sierra and Summit systems to be >100 PF, 2 GB/core main memory, local NVRAM, and science performance 4x-8x Titan or Sequoia

NVIDIA acceleration built into IBM Power S824L

8x faster than x86 lvy Bridge on pattern extraction

82x faster for Cognos Bland DB2 BLU

Tvan OpenPOWER Customer Reference System

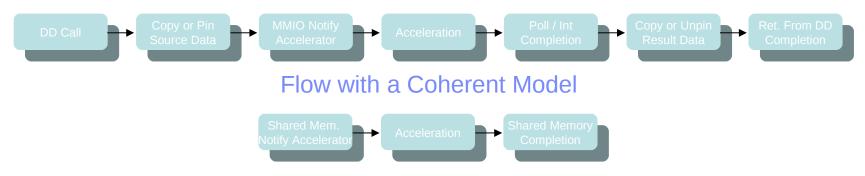

## Coherent attachment of accelerator cards

### Typical I/O Model Flow

Faster application development Faster application execution (40 to 1)

## IBM Power 822L pricing comparison (\$US) -Scale-Out Cloud with KVM

### Comparable TCA

Linux on Intel Ivy Bridge + VMware Vs.

Linux on POWER8

+ with PowerVM

Dell PowerEdge R720 \$28,366 S redha (intel

HP ProLiant DL380 G8 \$29,829 🍛 redhat intel **vm**ware Ivy Bridge

IBM Power 822L \$29,264 Power VM POWFR8

Server list price\* -3-year warranty, on-site

\$12,605

**vm**ware

\$14,068

\$14,895

Virtualization OTC + 3yr. 9x5 SWMA

\$10.064 VMware vSphere Enterprise 5.1

Ivy Bridge

\$9,880 PowerVM for IBM PowerLinux

Linux OS list price - RHEL, 2 sockets, unlimited guests, 9x5, 3 yr. sub./ supp.

\$5,697 Red Hat subscription and Red Hat subport

\$28,366

\$4,489

Total list price: (Total cost of acquisition)

\$5,697 Red Hat subscription and Red Hat support

\$29,829

\$ 10,064

VMware vSphere Enterprise 5.1

Red Hat subscription and IBM support

\$29,264

Server model

HP Proliant DL380p G8 Dell R720

IBM Power 822L

Processor / cores

Two 2.7 GHz, E5-2697, Ivy Bridge, 12-core processors

Two 3.4 GHz POWER8, 10-core

64 GB memory, 2 x 300GB 15k HDD, 10 Gb two port Configuration

Same memory, HDD, NIC \* Based on US pricing for Power S822L announcing on April 28, 2014 matching configuration table above. Source: hp.com, dell.com, vmware.com

## New POWER economical model

## Linux support for POWER

#### RHEL 7

- POWER8 (native mode) and POWER 7/7+

- Available June 2014

#### RHEL 6

- POWER8 supported with U5 (P7-compatibility mode)

- Full support of POWER6 and POWER7 (native mode)

#### · Fedora

- Fedora 16 was first release to re-launch POWER

- Fedora 20 has POWER8 support

- Supported add-ons

- JBoss

- High Performance Network Add-on

Built from the same source as x86

Delivered on the same schedule as x86

Supported at the same time as x86

#### SLES 12

- Anticipated to support POWER8 (native mode) and POWER 7/7+

- Available October 2014

#### SLES 11

- POWER8 with SP3 (P7compatibility mode)

- POWER7+ encryption,

RNG accelerators with

SP3

- Full support of POWER7 (native mode)

#### openSUSE

- openSUSE 12.2 relaunched for IBM POWER

- openSUSE 13.2 includes

POWER8 support

#### Supported add-ons

SUSE Linux Enterprise

High Availability

Extension

#### Ubuntu 14.10

- Continued support for POWER8

- Anticipate 4Q14 availability

#### Ubuntu 14.04

- POWER8 enabled (native mode)

- No official support for POWER7+ and older systems

- No support for 32-bit applications. 64-bit only.

- Supported in KVM only at this time

- LTS

#### Supported add-ons

- JuJu Charms

- MaaS (Metal as a Service)

- Landscape

#### Debian

Debian community now supports Power as of

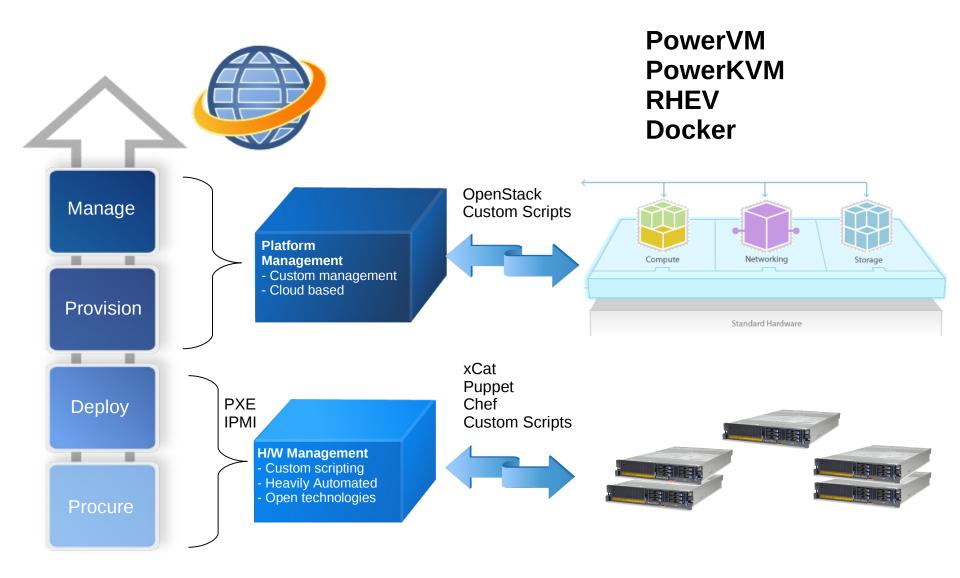

# Integrating POWER into the datacenter

24 © 2015 IBM Corporation

## Hot off the press – OVH MSP to offer POWER8 platform

"OVH has become the first commercial partner outside of IBM to formally announce the deployment of POWER8 servers inside their data centre. These will deployed as bare metal servers for customers who have big data and analytics problems and want the most powerful solution that they can get access to. As part of this announcement, OVH will become an OpenPOWER Foundation member."

- OVH announcement

- Google announcement

- Softlayer announcement

- Rackspace announcement

## **Linux momentum is growing on Power Systems**

An open ecosystem, using the POWER Architecture, to share expertise, investments, and server-class intellectual property to serve customers' evolving needs.

Linux Centers. Offering access to hardware technical support, porting assistance, demos, toolkits, hands-on labs

Beijing | Austin | New York | Montpellier | Tokyo

#### **Global Linux ISV Development**

**NEW. Power Development Cloud** gives Linux developers who want to prototype applications access to Power

**NEW**. **50,000 new developers** from Ubuntu development community

#### **Regional Ecosystem Initiative**

Recruiting key solutions: Open Source Tools Middleware Industry Solutions

in new Linux and open source technologies for IBM Power Systems.

© 2014 IBM Corporation

## OpenPOWER drives industry innovation

The goal of the OpenPOWER Foundation is to create an open ecosystem, using the POWER Architecture to share expertise, investment, and server-class intellectual property to serve the evolving needs of customers.

http://openpowerfoundation.org/

## Where to find more information?

## Power Systems Linux Portal

(Product Information)

## The OpenPOWER Foundation

The Linux on Power Community

franz\_bourlet@be.ibm.com