This presentation will discuss control blocks and pointers.

The goal of this presentation is to expose the hazards and solutions to maintaining consistent control block mappings without spending a lot of time managing duplicate code. This presentation will cover language considerations, some of which should be familiar and then introduce the concept of 'modeless pointers' or "mptrs" for short.

This section will discuss PLX and C structures.

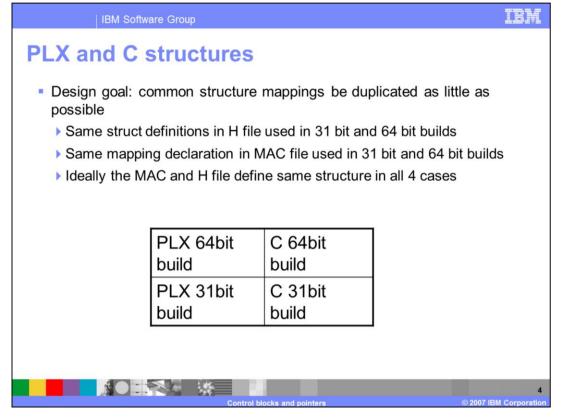

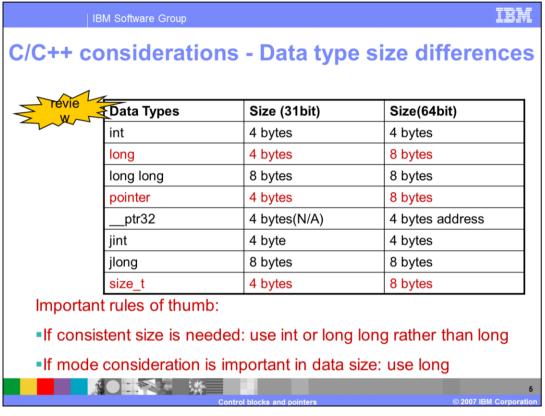

64-bit support poses certain problems when dealing with mapping macros for control blocks. Ideally you should be able to map these control blocks without having several versions of code and these mappings would be consistent. The above table shows the area of support that has been addressed. There are control blocks shared between C and PLX that need to be consistent between 64-bit and 31-bit builds and be consistent across the two languages.

An interesting angle is that the PLX code is built almost exclusively in 31-bit mode. So the mapping it has for any given common control block has to match the C header file that maps it in 64-bit mode in the same driver build.

A quick review – remember that certain things in C change size between 31 and 64bit mode. These differences become problematic in control blocks.

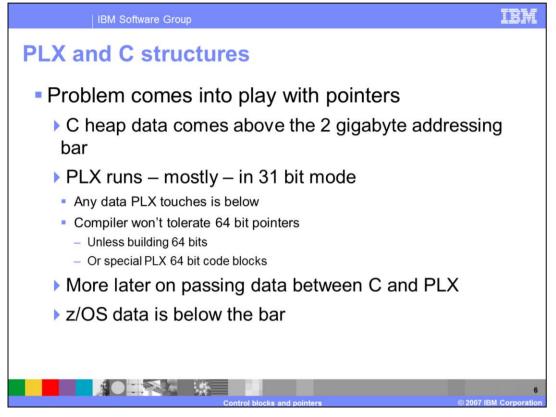

The problem surrounds the use of pointers. Having a control block without pointers the mapping is easier because the control block is the same between the two compile modes. An easier scenario would be to have all 64bit mode systems because there would be no question: all pointers would have to be 8 bytes whether the address is above the bar or below. However, since not all environments are 64-bit, this is impractical. Most, practically all, of the PLX code runs in 31-bit mode. It is fine to make every pointer 8 bytes but the PLX compiler is a bit strict in how it handles the code. It will not compile a ptr(64) in 31-bit mode.

Most of the system data on z/OS is also below the bar, which means more often than not four byte pointers are what get passed back and forth. It is impossible to dictate that all pointers be 8 bytes.

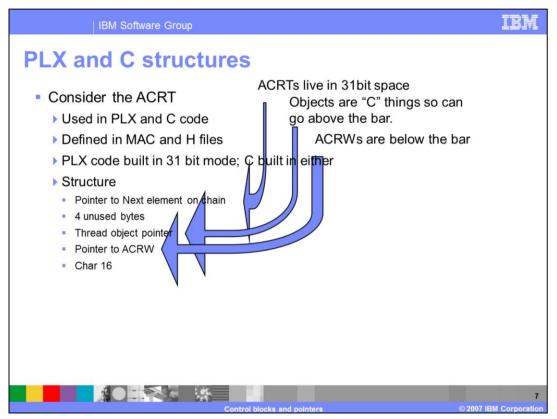

Here is an example of a control block that illustrates the compatibility situation. The ACRT is used in both C and PLX code. It is defined in both an H file and a MAC file. The PLX code is built in 31-bit mode, which is fine, but the C code is built in both. Left to it's own desires, the C compiler will end up generating two versions of offsets for fields in the same control block. One, because of 4 byte pointers and the other because the pointers are 8 bytes.

Let's look at some of the features of the ACRT.

It is used by PLX code which is mostly 31-bit mode so the ACRT has to live below the bar. That means the chaining pointer has to be a 4 byte pointer. 8 byte pointers will not work because the 31-bit code will look at offset zero for four bytes and find a zero. The C mapping is interesting because it will make an 8 byte pointer in 64-bit compile unless ones intentions are asserted. Another important point is that the ACRT has to be allocated below the bar.

The ACRT Points to C objects. They come from the C heap, which is above the bar. Things that could go above the bar have been allocated above the bar whenever possible. The ACRT pointer needs to be 8 bytes and the PLX code can not try to access it. Since it is a pointer to a C object, it is unlikely the PLX code will access it. Notice that problems may arise if this field is a four byte field in 31-bit mode and 8 bytes in the other.

There is a pointer to ACRWs. The pointer lives below the bar and likewise this pointer needs to be four bytes and stay four bytes.

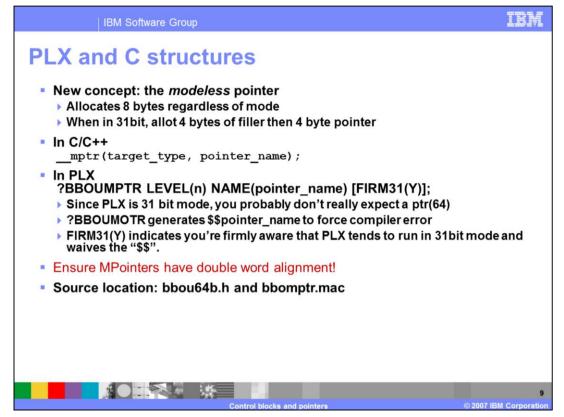

This section will discuss a new time saving construct: the modeless pointer.

The problem with pointers is not that they change sizes, it is that the offset of everything in the structure that follows will get thrown about depending on the length of the pointer. So the mptr was created to maintain steady field offsets.

An mptr always takes up 8 bytes even though the pointer itself might be only 4 bytes. The advantage is that the pointer itself accommodates the amode of the code that is accessing it but within the structure mapping, the overall field width is consistently 8 bytes.

The chart shows how mptrs are declared in both C and PLX. These code macros expand into 8 byte pointers for 64-bit compiles. In 31-bit compiles, a mptr expands into a four byte filler and a four byte pointer. That is how the overall 8 byte width stays consistent in the structure. An important note is that 64-bit pointers must be on a doubleword boundary so be careful not to let the PLX compiler stick in slack bytes to ensure a proper alignment.

Among the oddities of the PLX declaration is the optional keyword FIRM31 which has one useful parameter: "Y". Consider that PLX code tends to run only in 31-bit mode so if you are declaring an mptr that is shared between C and PLX, it had better be a four byte pointer. But if the pointer exists in this control block but is not actually referenced in PLX you are fine. If the pointer is referenced in PLX it could be problematic for C to stick an 8 byte address into a field of which 31-bit mode PLX will use only the lower word. So to head off problems, the macro renames the PLX pointer filed and if it is referenced somewhere in PLX code you will get a compiler error. The FIRM31(Y) prevents the renaming of the

pointer because you are telling the macro you are confident that the pointer will work fine in 31-bit PLX.

MPtrs are defined using macros in bbou64b.h in C and bboumptr.mac for PLX.

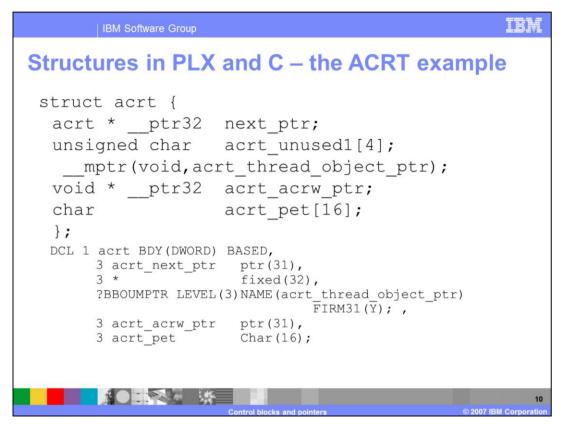

Here is the ACRT example shown in C and PLX declarations.

-The ACRT lives below the bar so its chain pointer needs to be four bytes in both compile modes. An important note is the \_\_ptr32 in the C.

-The thread object pointer must be able to point to storage above the bar when the C code is running in 64bit mode so an mptr construct is used. The PLX code uses the FIRM31(Y) but that is probably unnecessary. Note that the mptr is on a DW boundary.

-Finally, the ACRW lives below the bar so the pointer to it gets a \_\_\_ptr32 in C.

## Trademarks, copyrights, and disclaimers

The following terms are trademarks or registered trademarks of International Business Machines Corporation in the United States, other countries, or both:

IBM

Product data has been reviewed for accuracy as of the date of initial publication. Product data is subject to change without notice. This document could include technical inaccuracies or typographical errors. IBM may make improvements or changes in the products or programs described herein at any time without notice. Any statements regarding IBM's future direction and intent are subject to change or withdrawal without notice, and represent goals and objectives only. References in fits document to IBM products, programs, or services does not imply that IBM intends to make such products, programs or services available in all countries in which IBM operates or does business. Any reference to an IBM Program Product in this document is not intended to state or imply that program product may be used. Any functionally equivalent program, that does not infringe IBM's intellectual property rights, may be used instead.

Information is provided "AS IS" without warranty of any kind. THE INFORMATION PROVIDED IN THIS DOCUMENT IS DISTRIBUTED "AS IS" WITHOUT ANY WARRANTY, EITHER EXPRESS OR IMPLIED. IBM EXPRESSLY DISCLAIMS ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT. IBM shall have no responsibility to update this information. IBM products are warranted, if at all, according to the terms and conditions of the agreements (for example, IBM Customer Agreement, Statement of Limited Warranty, International Program License Agreement, etc.) under which they are provided. Information concerning non-IBM products may be appliers of those products, their published announcements or other publicly available sources. IBM has not tested those products in connection with this publication and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products.

IBM makes no representations or warranties, express or implied, regarding non-IBM products and services.

The provision of the information contained herein is not intended to, and does not, grant any right or license under any IBM patents or copyrights. Inquiries regarding patent or copyright licenses should be made, in writing, to:

IBM Director of Licensing IBM Corporation North Castle Drive Armonk, NY 10504-1785 U S A.

Performance is based on measurements and projections using standard IBM benchmarks in a controlled environment. All customer examples described are presented as illustrations of how those customers have used IBM products and the results they may have achieved. The actual throughput or performance that any user will experience will vary depending upon considerations such as the amount of multiprogramming in the user's job stream, the I/O configuration, and the workload processed. Therefore, no assurance can be given that an individual user will achieve throughput or performance improvements equivalent to the ratios stated here.

© Copyright International Business Machines Corporation 2007. All rights reserved.

Note to U.S. Government Users - Documentation related to restricted rights-Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract and IBM Corp.