**Dave Williams**

# pSeries 630 Models 6C4 and 6E4 Technical Overview and Introduction

ibm.com/redbooks sbv@us.ibm.com

#### International Technical Support Organization

## pSeries 630 Models 6C4 and 6E4 Technical Overview and Introduction

August 2002

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

### **Contents**

| Notices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Trademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V                                         |

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vi                                        |

| The team that wrote this Whitepaper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |

| Comments welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| Confinence welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VII                                       |

| Chapter 1. General description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                         |

| 1.1 Minimum and optional features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                         |

| 1.2 Model types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                         |

| 1.2.1 Model 6C4 rack-mounted server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                         |

| 1.2.2 Model 6E4 deskside/desktop server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

| 1.3 System racks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 1.3.1 IBM RS/6000 7014 Model T00 Enterprise Rack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 1.3.2 IBM RS/6000 7014 Model T42 Enterprise Rack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 1.3.3 OEM racks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |

| 1.3.4 Rack-mounting rules for Model 6C4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

| 1.3.5 Flat panel display options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 1.3.6 VGA switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

| 1.4 Statement of Direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                           |

| 1.4.1 Cluster 1600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           |

| 1.4.2 LPAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |

| 1.4.3 Remote I/O Drawer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |

| 1.4.4 NEBS Level 3 and -48 Volts DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |

| 1.4.4 NEDO Level o and -40 voito DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |

| Chapter 2. Architecture and technical overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                         |

| Chapter 2. Architecture and technical overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                        |

| 2.1 Processor and cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10<br>11                                  |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10<br>11<br>11                            |

| 2.1 Processor and cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10<br>11<br>11                            |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10<br>11<br>11<br>12                      |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10<br>11<br>11<br>12                      |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory.                                                                                                                                                                                                                                                                                                                                                                                                                       | 10<br>11<br>11<br>12<br>12                |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options                                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>11<br>11<br>12<br>12<br>12          |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR                                                                                                                                                                                                                                                                                                                                                                | 10 11 11 12 12 12 13                      |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity                                                                                                                                                                                                                                                                                                      | 10 11 11 12 12 12 13 13                   |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses                                                                                                                                                                                                                                                                                    | 10 11 11 12 12 12 13 13 14                |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses  2.3.1 GX bus and fabric bus                                                                                                                                                                                                                                                       | 10 11 11 12 12 13 13 14 14                |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses  2.3.1 GX bus and fabric bus  2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters                                                                                                                                                                                      | 10 11 11 12 12 13 13 14 14 14             |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses  2.3.1 GX bus and fabric bus  2.3.2 PCI host bridge and PCI bus                                                                                                                                                                                                                    | 10 11 11 12 12 13 14 14 14                |

| 2.1 Processor and cache 2.1.1 L1, L2, and L3 cache 2.1.2 PowerPC™ architecture 2.1.3 Copper and CMOS technology 2.1.4 Processor clock rate  2.2 Memory 2.2.1 Memory options 2.2.2 Memory guidelines for LPAR 2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses 2.3.1 GX bus and fabric bus 2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters 2.4.1 64-bit and 32-bit adapters 2.4.2 Internal Ultra3 SCSI controllers.                                                                                                                      | 10 11 11 12 12 13 14 14 14 14             |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses  2.3.1 GX bus and fabric bus  2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters  2.4.1 64-bit and 32-bit adapters  2.4.2 Internal Ultra3 SCSI controllers.  2.4.3 LAN adapters                                                                                       | 10 11 11 12 12 13 14 14 14 14 15          |

| 2.1 Processor and cache  2.1.1 L1, L2, and L3 cache  2.1.2 PowerPC™ architecture  2.1.3 Copper and CMOS technology  2.1.4 Processor clock rate  2.2 Memory  2.2.1 Memory options  2.2.2 Memory guidelines for LPAR  2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses  2.3.1 GX bus and fabric bus  2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters  2.4.1 64-bit and 32-bit adapters  2.4.2 Internal Ultra3 SCSI controllers.  2.4.3 LAN adapters  2.4.4 Graphics adapters                                                              | 10 11 11 12 12 13 14 14 14 14 15 15       |

| 2.1 Processor and cache 2.1.1 L1, L2, and L3 cache 2.1.2 PowerPC™ architecture 2.1.3 Copper and CMOS technology 2.1.4 Processor clock rate  2.2 Memory 2.2.1 Memory options 2.2.2 Memory guidelines for LPAR 2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses 2.3.1 GX bus and fabric bus 2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters 2.4.1 64-bit and 32-bit adapters 2.4.2 Internal Ultra3 SCSI controllers. 2.4.3 LAN adapters 2.4.4 Graphics adapters. 2.5 Internal storage.                                                    | 10 11 11 12 12 13 14 14 14 15 15          |

| 2.1 Processor and cache 2.1.1 L1, L2, and L3 cache 2.1.2 PowerPC™ architecture 2.1.3 Copper and CMOS technology 2.1.4 Processor clock rate  2.2 Memory 2.2.1 Memory options 2.2.2 Memory guidelines for LPAR 2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses 2.3.1 GX bus and fabric bus 2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters 2.4.1 64-bit and 32-bit adapters 2.4.2 Internal Ultra3 SCSI controllers. 2.4.3 LAN adapters 2.4.4 Graphics adapters 2.4.4 Graphics adapters. 2.5 Internal storage 2.5.1 Internal media        | 10 11 11 12 12 13 14 14 14 15 15 15       |

| 2.1 Processor and cache 2.1.1 L1, L2, and L3 cache 2.1.2 PowerPC™ architecture 2.1.3 Copper and CMOS technology 2.1.4 Processor clock rate  2.2 Memory 2.2.1 Memory options 2.2.2 Memory guidelines for LPAR 2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses 2.3.1 GX bus and fabric bus 2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters 2.4.1 64-bit and 32-bit adapters 2.4.2 Internal Ultra3 SCSI controllers 2.4.3 LAN adapters 2.4.4 Graphics adapters 2.5.1 Internal storage 2.5.1 Internal media 2.5.2 Hot-swappable SCSI disks | 10 11 12 12 13 14 14 14 15 15 15          |

| 2.1 Processor and cache 2.1.1 L1, L2, and L3 cache 2.1.2 PowerPC™ architecture 2.1.3 Copper and CMOS technology 2.1.4 Processor clock rate  2.2 Memory 2.2.1 Memory options 2.2.2 Memory guidelines for LPAR 2.2.3 Memory reliability, fault tolerance, and integrity  2.3 System buses 2.3.1 GX bus and fabric bus 2.3.2 PCI host bridge and PCI bus  2.4 PCI-X slots and adapters 2.4.1 64-bit and 32-bit adapters 2.4.2 Internal Ultra3 SCSI controllers. 2.4.3 LAN adapters 2.4.4 Graphics adapters 2.4.4 Graphics adapters. 2.5 Internal storage 2.5.1 Internal media        | 10 11 11 12 12 13 14 14 14 14 15 15 16 16 |

| 2.6 Security 2.7 Operating system requirements 2.7.1 AIX 5L 2.7.2 Linux      | 18<br>18 |

|------------------------------------------------------------------------------|----------|

| Chapter 3. Availability, investment protection, expansion, and accessibility |          |

| 3.1 High availability solution                                               | 21       |

| 3.2 Reliability, availability, and serviceability (RAS) features             | 22       |

| 3.2.1 First failure data capture, diagnostics, and recovery                  | 23       |

| 3.2.2 Dynamic or persistent deallocation                                     | 23       |

| 3.2.3 Power and cooling                                                      |          |

| 3.2.4 Service processor                                                      |          |

| 3.2.5 Service Agent and Inventory Scout                                      |          |

| 3.2.6 Project eLiza                                                          |          |

| Related publications                                                         | 29       |

| BM Redbooks                                                                  |          |

| Other resources                                                              |          |

| Referenced Web sites                                                         |          |

| How to get IBM Redbooks                                                      |          |

| IBM Redbooks collections                                                     |          |

#### **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

AIX 5L™ IBMLink™ Redbooks(logo)™

AIX® Perform™ Redbooks™

Chipkill™ PowerPC® RS/6000®

Enterprise Storage Server™ POWER4™ SP™

IBM® pSeries™

The following terms are trademarks of International Business Machines Corporation and Lotus Development Corporation in the United States, other countries, or both:

Lotus® Word Pro®

The @server brand consists of the established IBM e-business logo followed by the descriptive term "server".

The following terms are trademarks of other companies:

Linux is a registered trademark of Linus Torvalds in the United States, other countries, or both.

ActionMedia, LANDesk, MMX, Pentium and ProShare are trademarks of Intel Corporation in the United States, other countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

C-bus is a trademark of Corollary, Inc. in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

SET, SET Secure Electronic Transaction, and the SET Logo are trademarks owned by SET Secure Electronic Transaction LLC.

Other company, product, and service names may be trademarks or service marks of others.

#### **Preface**

This document provides a comprehensive single-source guide covering IBM @server pSeries™ 630 Models 6C4 and 6E4 entry servers. Major hardware offerings are introduced and their prominent functions discussed.

Professionals wishing to acquire a better understanding of IBM @server pSeries products may consider reading this document. The intended audience includes:

- Customers

- Sales and marketing professionals

- ► Technical support professionals

- IBM Business Partners

This document expands the current set of IBM @server pSeries documentation by providing a desktop reference that offers a detailed technical description about the pSeries 630 Models 6C4 and 6E4.

This publication does not replace the latest pSeries marketing materials and tools. It is intended as an additional source of information that, together with existing sources, may be used to enhance your knowledge of IBM UNIX® server solutions.

#### The team that wrote this Whitepaper

This Whitepaper was produced by a team of specialists from around the world working at the International Technical Support Organization, Austin Center.

**Derrick Daines** is the pSeries specialist for the Bedfont office in the UK. He has 13 years of experience working on pSeries products. He has worked at IBM for 34 years on products including the pSeries 690. He provides support to other engineers within his own branch, other branches within the region, and also provides country support during weekends.

**Wolfgang Seiwald** is a presales technical support specialist at the IBM office in Salzburg, Austria. He has worked at IBM for three years. He holds a Diplomingenieur degree in Telematik from the Technical University of Graz. The main focus of his work lies in the area of the IBM @server systems and the IBM AIX® operating system.

**Dave Williams** is a consulting IT specialist in the U.K. Advanced Technical Support group based in Bedfont. He has 25 years of experience in IBM, the last 18 of them being with IBM AIX products. His areas of expertise include pSeries 690 and e-business solutions.

Thanks to the following people for their outstanding contributions to this project:

#### IBM U.S.A.

Doug Bossen, Brad Frey, Ghadir Gholami, John Hilburn, Tenley Jackson, Jim McGaughan, Bill Mihaltse, Jan Palmer, Jim Reidy, Alan Standridge, Ven Tenjarla, and Sterling Weaver

#### **IBM Germany**

Volker Haug and Gregor Linzmeier

#### IBM U.K.

Nigel Griffiths

#### **Comments welcome**

Your comments are important to us.

We want our papers to be as helpful as possible. Send us your comments about this Whitepaper in one of the following ways:

► Send your comments in an Internet note to:

sbv@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization ATTN: Scott Vetter Dept. JN9B Building 003 Internal Zip 2834 11400 Burnet Road Austin, Texas 78758-3493, USA

# 1

## **General description**

The IBM @server pSeries 630 Models 6C4 and 6E4 (referred to hereafter as the Model 6C4 and Model 6E4) are designed for customers looking for a cost-effective, high-performance 1- to 4-way server. These servers make use of IBM technology, first used in the high-end pSeries 690, delivered in a compact package. These systems use the 64-bit, copper/SOI-based, POWER4™ microprocessors, packaged as 1- and 2-way cards.

The Models 6C4 and 6E4 are members of the 64-bit family of symmetric multiprocessing (SMP) UNIX servers from IBM. They offer excellent price/performance in small packages with high-end reliability features for managing e-business, greater application flexibility, and innovative technology, all designed to help capitalize on the e-business revolution.

The Model 6C4 (product number 7028-6C4) is a 4 EIA<sup>1</sup> (4U) 19-inch rack-mounted server, while the Model 6E4 (product number 7028-6E4) is a deskside/desktop server. With a maximum of two processor cards, the Models 6C4 and 6E4 can be configured into 1-, 2-, or 4-way systems. Each processor card is packaged together with up to 8 GB of memory per card into a processor book - a sealed unit that protects the components in a rigid structure designed for higher reliability. Total system memory can range from 1 GB up to 32 GB on a 4-way system based on the currently available memory DIMMs.

The Models 6C4 and 6E4 include four, front-accessible disk bays supporting hot-swappable disks. These disk bays can accommodate up to 293.6 GB of disk storage using 73.4 GB Ultra3 SCSI disk drives. Two media bays are used for a CD-ROM, DVD-RAM, or another optional media device, such as a tape or diskette drive.

Additional reliability and availability features include optionally redundant hot-plug cooling fans and power supplies. Along with these hot-plug components, these systems are designed to provide an extensive set of behaviors that include improved fault isolation, recovery from errors without stopping the system, avoidance of recurring failures, and predictive failure analysis. See Section 3.2, "Reliability, availability, and serviceability (RAS) features" on page 22 for more information on RAS features.

The pSeries 630 Model 6C4 is an ideal replacement for the pSeries 640 Model B80 and the pSeries 630 Model 6E4 for the RS/6000 Model 270.

<sup>&</sup>lt;sup>1</sup> One EIA (Electronic Industries Association Unit) is 44.45mm (1.75 inch)

#### 1.1 Minimum and optional features

The Models 6C4 and 6E4 deliver a cost-efficient growth path for the future through such capabilities as:

- ▶ 1-, 2-, and 4-way SMP system

- 1- and 2-way processor books with 1.0 GHz POWER4 microprocessors. Only a single

1-way card is allowed per server at a time. A 3-way configuration is unavailable.

- A 1-way (FC 5131) to a 2-way (FC 5132) upgrade is by feature conversion.

- 32 MB shared L3 cache per processor card.

- ▶ 1 GB to 32 GB ECC DDR SDRAM memory (based on the available memory DIMMs at time of publication)

- Memory DIMMs plug into the processor book (8 DIMM slots per card).

- DIMMs must be populated in quads (four DIMMs). A memory feature consists of a quad. Additional quads may consist of any memory feature code (memory size).

- A system with a single processor card (1- or 2-way) may have a maximum of 16 GB of memory based on the maximum memory feature available (FC 4454 4x2048 MB).

- ► Four hot-swapable disk drive bays

- 18.2 GB to 293.6 GB of disk storage.

- 18.2 GB Ultra3 10K RPM (FC 3157), 36.4 GB Ultra3 10K RPM (FC 3158),

73.4 GB Ultra3 10K RPM (FC 3159) disks are available at the time of writing.

- ► Two media bays (one CD-ROM or DVD-RAM must be configured on an initial order)

- Media bay 1 can accommodate an IDE CD-ROM (FC 2633), or a SCSI DVD-RAM (FC 2623). The DVD-RAM will read CD-ROM installation media.

- Media bay 2 can accommodate a DVD-RAM (FC 2623), diskette drive (FC 2605), or tape drive (4 mm FC 6158 or 8 mm FC 6156; contact your IBM representative to check the availability of 8 mm tape drives).

- FC 6203 with FC 4260 is required for the additional SCSI devices (DVD-RAM or tape drive) installed.

- A maximum of one DVD-RAM is orderable per system.

- ► Four hot-plug PCI-X slots, 64-bit, 133 MHz, 3.3 volt

- For more information on PCI-X, see Section 2.4, "PCI-X slots and adapters" on page 14.

- Integrated ports

- Two 10/100 Ethernet (IEEE 802.3 compliant).

- Two Ultra3 SCSI (one external Ultra3 SCSI (with VHDCI<sup>2</sup> mini 68-pin port), and one internal Ultra3 SCSI disk drive backplane). VHDCI requires a mini 68-pin connector or FC 2118 mini 68-pin to 68-pin 0.3 meter cable as an additional feature.

- Three serial. Serial port 1 (S1) has two physical connectors, one RJ-48 in front and a

9-pin D-shell in the rear. The use of the front port disables the rear S1 port.

- One parallel.

- Keyboard and mouse.

- Optional hot-plug redundant power supplies (requires the addition of redundant cooling)

- ► Optional redundant hot-plug cooling fans

- ► Integrated service processor

- ► AIX® 5L™ license included

- ► Support for 32-bit and 64-bit applications

<sup>&</sup>lt;sup>2</sup> Very High Density Cable Interconnect (VHDCI)

**Note:** Before completing an order, you need to determine whether a diskette drive, mouse, national keyboard, graphics adapter, monitor, or additional features are required.

#### 1.2 Model types

Figure 1-1 shows the package layout for the Models 6C4 and 6E4. The Models 6E4 and 6C4 comply with the FCC limitations for a Class A digital device, and meet IBM's acoustic guidelines for a general business environment.

Figure 1-1 Models 6C4 (shown left) and 6E4 (shown right) physical packaging

#### 1.2.1 Model 6C4 rack-mounted server

The Model 6C4 is a 4U rack-mounted server and is intended to be installed in a 19-inch rack thereby enabling efficient use of computer room floor space. If the IBM 7014 T42 rack is used to mount the Model 6C4, then it is possible to place up to ten systems in an area of 644 mm (25.5 inches) x 1147 mm (45.2 inches).

Each system is delivered pre-configured as ordered. Included with the Model 6C4 rack-mounted server packaging will be all of the components and instructions necessary to enable installation in a 19-inch rack using suitable tools. This system was designated as a customer setup and requires three persons (due to weight and safety issues) to be present to install the unit into the rack.

All system MES upgrades can be performed by the customer with the single exception of the 2-way processor card FC 5132, which requires that a service call be placed.

Each Model 6C4 is shipped with a template which helps each server be mounted into the desired position in the rack. The Model 6C4 is shipped with a cable management arm. The cable management arm provides support and routing for all cables, both power and signal, to prevent damage during movement of the system into the service position. Cables are secured to the arm using cable ties supplied.

#### Physical specifications

The following are the key statistics of the Model 6C4:

- Width: 444.4 mm (17.5 inches)

- ► Depth: 609.6 mm (24.0 inches)

- ► Height: 172.8 mm (6.8 inches)

- ▶ Weight in minimum configuration: 32.0 kg (70.4 pounds)

- Weight in maximum configuration with rails: 47.3 kg (104.0 pounds)

#### 1.2.2 Model 6E4 deskside/desktop server

The Model 6E4 is a deskside/desktop server, ideal for environments requiring the user to have local access to the machine. A typical example of this would be applications requiring a native graphics display.

Each system will be delivered pre-configured as ordered. The system is designed to be set up by the customer and in most cases, will not require the use of any tools. Full setup instructions are included with the server.

All system MES upgrades can be performed by the customer with the single exception of the 2-way processor card FC 5132, which requires that a service call be placed.

#### Physical specifications

The following are the key statistics of the Model 6E4:

- ▶ Width: 300.0 mm (11.8 inches)

- ► Depth: 725.0 mm (28.5 inches)

- ► Height: 530.0 mm (20.9 inches)

- ► Weight in minimum configuration: 36.0 kg (79.2 pounds)

- ► Weight in maximum configuration: 51.0 kg (112.2 pounds)

#### 1.3 System racks

The following description provides an overview of racks available from IBM in which the Model 6C4 can be mounted. There is no feature available to convert a deskside/desktop model to a rack-mounted model.

The Enterprise Rack Models T00 and T42 are 19-inch wide racks for general use with pSeries and RS/6000 rack-based or rack drawer-based systems. The rack provides increased capacity, greater flexibility, and improved floor space utilization.

If a pSeries or RS/6000 system is to be installed in a non-IBM rack or cabinet, you should ensure that the rack to be used conforms to the EIA standard EIA-310-D.

It is the customer's responsibility to ensure that the installation of the drawer in the preferred rack or cabinet results in a configuration that is stable, serviceable, safe, and compatible with the drawer requirements for power, cooling, cable management, weight, and rail security.

#### 1.3.1 IBM RS/6000 7014 Model T00 Enterprise Rack

The 1.8 meter (71 inches) Model T00 is compatible with past and present pSeries and RS/6000 racks, and is designed for use in all situations that have previously used the older rack Models R00 and S00. The T00 rack has the following features:

- ➤ 36 EIA units (36U) of usable space.

- Optional removable side panels.

- Optional classic or sculptured front door.

- Optional side-to-side mounting hardware for joining multiple racks.

- Increased power distribution and weight capacity.

- Standard black or optional white color in OEM format.

- ► Optional reinforced (ruggedized) rack feature provides added earthquake protection with modular rear brace, concrete floor bolt-down hardware, and bolt-in steel front filler panels.

- Support of both AC and DC configurations.

- ▶ Up to 6 AC power distribution units (PDUs) provide a total of 36 power connections. Each PDU will require a separate AC supply. Four PDUs should be adequate for most configurations, and any subsequent PDUs require 1U of rack space.

- ▶ DC rack height is increased to 1926 mm (75.8 inches) due to the presence of the power distribution panel fixed to top of rack.

- Weight:

- T00 base empty rack: 244 kg (535 pounds)

- T00 full rack: 816 kg (1795 pounds)

#### 1.3.2 IBM RS/6000 7014 Model T42 Enterprise Rack

The 2.0 meter (79.3 inches) Model T42 is the rack that will address the special requirements of customers who want a tall enclosure to house the maximum amount of equipment in the smallest possible floor space. The features that differ in the Model T42 rack from the Model T00 include the following:

- ▶ 42 EIA units (42U) of usable space.

- AC power support only.

- Up to 7 PDUs provide a total of 42 power connections. Each PDU will require a separate AC supply. Four PDUs should be adequate for most configurations, and any subsequent PDUs require 1U of rack space.

- ► Weight:

- T42 base empty rack: 261 kg (575 pounds)

- T42 full rack: 930 kg (2045 pounds)

#### 1.3.3 OEM racks

The Model 6C4 can be installed in a suitable OEM rack, provided that the rack conforms to the EIA-310-D standard. This standard is published by the Electrical Industries Alliance, and a summary of this standard is available in the publication *Site and Hardware Planning Information*, SA38-0508. An online copy of this document can be found at:

http://www.ibm.com/servers/eserver/pseries/library/hardware docs

Key points mentioned in this standard are as follows:

- ► Any rack used must be capable of supporting 15.9 kg (35 pounds) per EIA unit (44.5 mm (1.75 inch) of rack height).

- ► To ensure proper rail alignment, the rack must have mounting flanges that are at least 494 mm (19.45 inches) across the width of the rack and 719 mm (28.3 inches) between the front and rear rack flanges.

- It may be necessary to supply additional hardware, such as fasteners, for use in some manufacturers' racks.

#### 1.3.4 Rack-mounting rules for Model 6C4

There are rules that should be followed when mounting drawers into a rack. The primary rules are as follows:

- ► The Model 6C4 is designed to be placed at any location in the rack. For rack stability reasons, it is advisable to start filling a rack from the bottom.

- Any remaining space in the rack can be used to install other systems or peripherals provided that the maximum permissible weight of the rack is not exceeded.

- ▶ Before placing a Model 6C4 into the service position, it is essential to ensure that the rack manufacturer's safety instructions have been followed regarding rack stability.

- ► A Model 6C4 is 4U in height, so a maximum of nine Model 6C4s fit in a T00 rack, or ten Model 6C4s in a T42 rack.

#### 1.3.5 Flat panel display options

For rack-mounted systems, the IBM 7316-TF2 Flat Panel Console Kit may be installed in the system rack. This 1U (EIA) console uses a 15-inch thin film transistor (TFT) LCD with a viewable area of 304.1 mm x 228.1 mm and a 1024 x 768 resolution. The 7316-TF2 Flat Panel Console Kit has the following attributes:

- ► Flat Panel Color Monitor

- Rack tray for keyboard, monitor, and optional VGA switch with mounting brackets

- ▶ IBM Space Saver 2 14.5-inch Keyboard that mounts in the Rack Keyboard Tray and is available as a feature in sixteen language configurations (the track point mouse is integral to keyboard)

Order the T210 Flat-Panel Monitor (FC 3635) if you are looking for a desk-top flat panel display option. The T210 is a 21-inch TFT LCD digital screen with a viewable image size of 528 mm (20.8 inches) measured diagonally, incorporating a 0.207 mm pixel pitch/type for bright, high-definition images.

**Note:** It is recommended that the 7316-TF2 be installed between EIA 20 to 25 of the rack for ease of use. The 7316-TF2 and T210 (or any other graphics monitor) require a GXT135P Graphics Adapter (FC 2848) to be installed in the server.

#### 1.3.6 VGA switch

The VGA switch for the IBM 7316-TF2 allows for the connection of up to eight servers to a single keyboard, display, and mouse.

To help minimize cable clutter, multi-connector cables in lengths of 7, 12, and 20 feet are available. These cables can be used to connect the graphics adapter (required in each attached system), keyboard port, and mouse port of the attached servers to the switch or to connect between multiple switches in a tiered configuration. Using a two-level cascade arrangement, as many as 64 systems can be controlled from a single point.

This dual-user switch allows attachment of one or two consoles, one of which must be an IBM 7316-TF2. An easy to use graphical interface and support for six languages (English, French, Spanish, German, Italian, or Brazilian Portuguese) allows fast switching between systems.

The VGA switch is only 1 EIA unit (1U) high and can be mounted in the same tray as the IBM 7316-TF2, thus conserving valuable rack space. It supports a maximum video resolution of 1600 x 1280, which facilitates the use of graphics-intensive applications and large monitors.

#### 1.4 Statement of Direction

The following are statements of direction. All statements regarding IBM's future, direction, and intent, and are subject to change or withdrawal without notice, and represent goals and objectives only.

#### 1.4.1 Cluster 1600

The Model 6C4, at the time of announcement, is planned to be supported as a cluster building block by the IBM @server Cluster 1600. It will be supported by PSSP 3.4 and can optionally be attached to the SP Switch2. This facility is planned for introduction in the fourth quarter of 2002.

#### 1.4.2 LPAR

IBM is planning to enable the pSeries 630 servers with LPAR to dynamically redefine the resources that make up a logical partition. This means that partitions can be changed while applications continue to run. No re-boot of affected partitions will be required after this planned feature is installed. Processors, memory, and adapters can be logically added or removed from active partitions without disruption to applications. The LPAR requires the use of a Hardware Management Console (HMC). This capability is planned for introduction on the pSeries 630 in the fourth quarter of 2002 and will be supported by a new release of AIX 5L.

AIX 5L Version 5.1 will not support static LPAR on the pSeries 630 servers until fourth quarter of 2002.

#### 1.4.3 Remote I/O Drawer

To enhance expandability of pSeries 630, IBM plans to introduce a 4U high rack-mount remote I/O expansion drawer with seven PCI-X slots and two six-packs of hot-swappable disk bays. This capability is expected to be introduced in the fourth quarter of 2002.

#### 1.4.4 NEBS Level 3 and -48 Volts DC

IBM is planning to provide NEBS<sup>3</sup> Level 3 compliance for the pSeries 630 Model 6C4 and -48V DC power in the first quarter of 2003.

<sup>&</sup>lt;sup>3</sup> Network Equipment Building System

# Architecture and technical overview

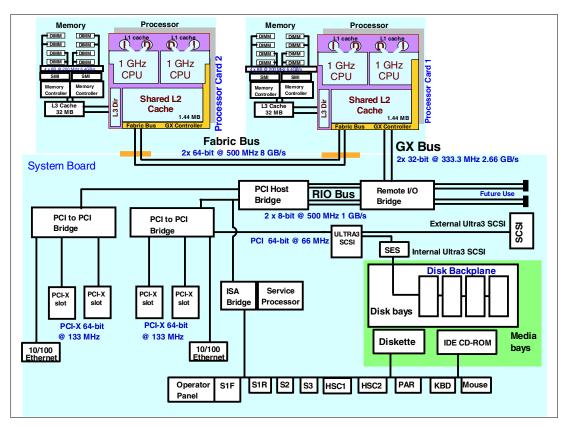

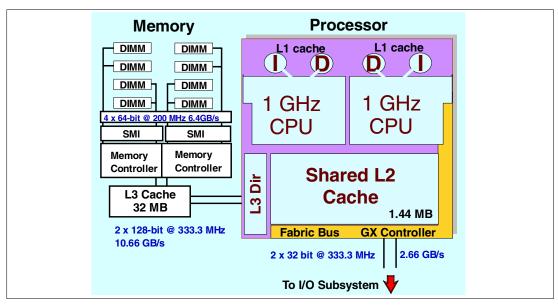

This chapter discusses the overall system architecture represented by Figure 2-1. The major components of this diagram will be described in the following sections. The bandwidths provided throughout this section are theoretical maximums provided for reference. It is always recommended to obtain real-world performance using production workloads.

Figure 2-1 Conceptual diagram of the Models 6C4 and 6E4 system architecture

#### 2.1 Processor and cache

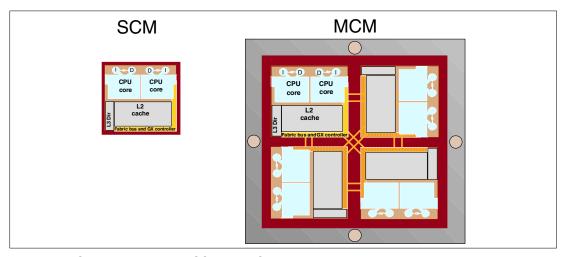

The Models 6C4 and 6E4 processor subsystem consists of POWER4 processors running at 1.0 GHz. These are the same processor chips used in the IBM @server pSeries 690. However, unlike the Multi-Chip Module (MCM) packaging used in the Model 690, these systems use a Single Chip Module (SCM) containing either one or two processor cores (CPUs), with each SCM permanently mounted on to a processor card. Models 6C4 and 6E4 can contain one or two processor cards, giving the option of one, two, or four CPUs per system.

One key difference is that the Chip-to-Chip fabric (which was used between chips on the same MCM in the Model 690) is no longer relevant in the SCM. A logical diagram of the pSeries 630 SCM and the pSeries 690 MCM is shown in Figure 2-2 for comparison.

Figure 2-2 Comparison between SCM and MCM

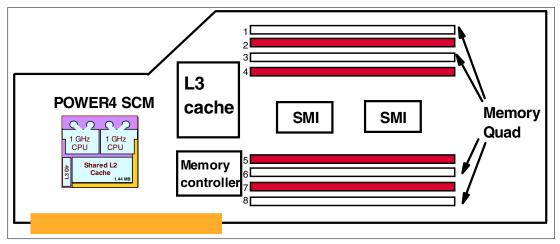

Each SCM is a Ceramic Column Grid Array (CCGA) package where the chip carrier is raised slightly from it's board mounting by small metal solder columns that provide the required connections and improved thermal resilience characteristics. As well as the SCM, each processor card also contains the L3 cache and the memory DIMMs, as shown in Figure 2-3. The processor card is mounted in a rugged metal enclosure named a *book* that protects (both in and out of the server) and secures the card, and helps manage airflow used for cooling.

Figure 2-3 Processor card layout

Memory access is through the on-chip Level 2 cache (L2) and Level 3 (L3) cache directory controller to the off-chip L3 cache and finally through the memory controller and synchronous memory interface (SMI) to the memory DIMMs, as represented in Figure 2-4.

Figure 2-4 Conceptual diagram of processor and memory subsystem

#### 2.1.1 L1, L2, and L3 cache

The POWER4 storage subsystem consists of three levels of cache and the memory subsystem. The first two levels of cache are onboard the POWER4 chip. The first level is 64 KB of Instruction (I) and 32 KB of Data (D) cache per processor core. The second level is 1.44 MB of L2 cache. A 2-way processor shares the L2 cache. All cache has either full ECC<sup>1</sup> or parity protection on the data arrays, and L1 cache has the ability to re-fetch data from L2 cache in the event of soft errors detected by parity checking.

The Level 3 (L3) cache consists of two components: the L3 cache controller/directory and the L3 data array. The L3 controller and cache directory are on the POWER4 chip, and the data array itself consists of two 16 MB embedded DRAM (eDRAM) chips on a separate module, mounted on the processor card.

#### 2.1.2 PowerPC™ architecture

The Models 6C4 and 6E4 systems comply with the RS/6000 platform architecture which is an evolution of the PowerPC Common Hardware Reference Platform (CHRP) specifications.

#### 2.1.3 Copper and CMOS technology

The POWER4 processor chip takes advantage of IBM's leadership technology. It is made using IBM 0.18- $\mu$ m-lithography CMOS² fabrication with seven levels of copper interconnect wiring. POWER4 also uses Silicon-on-Insulator (SOI) technology to allow a higher operating frequency for improved performance, yet with lower power consumption and improved reliability.

<sup>&</sup>lt;sup>1</sup> ECC single error correct, double error detect

<sup>&</sup>lt;sup>2</sup> Complementary Metal Oxide Semiconductor

#### 2.1.4 Processor clock rate

The Models 6C4 and 6E4 operate with a processor clock rate of 1.0 GHz.

To determine the processor characteristics on a running system, use one of the following commands.

**1sattr -E1 proc** *X* Where *X* is the number of the processor, for example, proc0 is the first

processor in the system. The output from the command<sup>3</sup> would be similar to the following (False, as used in this output, signifies the value cannot be changed through an AIX command interface):

state enable Processor state False type powerPC\_POWER4 Processor type False frequency 100000000 Processor Speed false

pmcycles -m This command uses the Performance Monitor cycle counter and the

processor real-time clock to measure the actual processor clock

speed in MHz.

**Note:** The pmcycles command is part of the bos.pmapi fileset. First check if that component is installed using the lslpp -l bos.pmapi command.

#### 2.2 Memory

The conceptual diagram of the memory subsystem of the Models 6C4 and 6E4 is shown in Figure 2-4 on page 11. As shown, there are four 64-bit data paths to memory with an aggregated bandwidth of 6.4 GB/s on each processor card. Each processor card can hold up to eight double data rate (DDR) synchronous DRAM (SDRAM) DIMM memory cards, which must be populated in guads (see Figure 2-4 on page 11).

DDR memory can theoretically double memory throughput at a given clock speed by providing output on both the rising- and falling-edges of the clock signal (rather than just on the rising edge).

Memory must be balanced across the two-processor cards (4-way) for best performance, therefore a 1 GB 4-way configuration is not recommended.

#### 2.2.1 Memory options

The following memory features for the Models 6C4 and 6E4 are available at the time of writing:

FC 4451 1024 MB (4X256 MB) 208 pin 8 ns DDR SDRAM DIMMs FC 4452 2048 MB (4X512 MB) 208 pin 8 ns DDR SDRAM DIMMs

FC 4453 4096 MB (4X1024 MB) 208 pin 8 ns stacked DDR SDRAM DIMMs

FC 4454 8192 MB (4X2048 MB) 208 pin 8 ns stacked DDR SDRAM DIMMs

Each memory feature consists of four DIMMs, or quad.

$<sup>^3</sup>$  The output of the 1sattr command has been expanded with AIX 5L to include the processor clock rate.

#### 2.2.2 Memory guidelines for LPAR

Planning for logical partitioning (see Section 1.4, "Statement of Direction" on page 7) involves the following considerations regarding memory.

- ▶ pSeries 630s must have at least 1 GB to support LPAR. The first 256 MB of memory will be allocated to the hypervisor, the last 256 MB to translation control entries (TCEs) and to hypervisor per partition page tables. This minimum configuration will allow one 512 MB partition or two 256 MB partitions (given a hypervisor memory allocation unit of 256 MB). TCE memory is used to translate the I/O addresses to system memory addresses. Without LPAR, this memory is part of the memory AIX allocates. In LPAR mode, where a system can have many AIX LPAR images, the TCE memory is allocated once for the set of images rather than once for each LPAR image.

- ► The memory installed on processor card 1 should match the size of the memory installed on processor card 2.

- ► With AIX 5L Version 5.1, pSeries 630s can never support a partition with a memory size 16 GB or greater even if more than 16 GB of physical memory is installed.

#### 2.2.3 Memory reliability, fault tolerance, and integrity

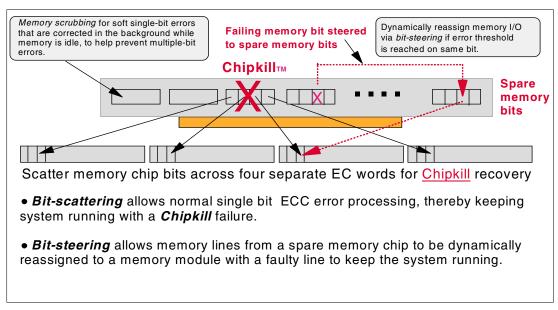

The Models 6C4 and 6E4 use Error Checking and Correcting (ECC) circuitry for system memory to correct single-bit and to detect double-bit memory failures. Detection of double-bit memory failures helps maintain data integrity. Furthermore, the memory chips are organized such that the failure of any specific memory module only affects a single bit within a four bit ECC word (bit scattering), thus allowing for error correction and continued operation in the presence of a complete chip failure (Chipkill<sup>TM</sup> recovery). The memory DIMMs also utilize memory scrubbing and thresholding to determine when spare memory modules within each bank of memory should be used to replace ones that have exceeded their threshold of error count (dynamic bit steering). Memory scrubbing is the process of reading the contents of memory during idle time and checking and correcting any single-bit errors that have accumulated by passing the data through the ECC logic. This function is a hardware function on the memory controller chip and does not influence normal system memory performance.

Figure 2-5 Main storage ECC and extensions

#### 2.3 System buses

The system bus from the processors to the memory subsystem is 2 x 128 bits at 1/3 CPU clock speed (or 333.3 MHz) for an aggregate data rate of 10.66 GB/s. For a system with two processor cards, the fabric bus connects between POWER4 chips on each card. All traffic to and from the I/O subsystem is through the GX bus on the first processor card. All system, I/O, and PCI buses support parity error detection.

#### 2.3.1 GX bus and fabric bus

The GX controller - embedded in the POWER4 chip - is responsible for controlling the flow data through the GX bus. The GX bus is a high frequency, single ended, unidirectional, point to point bus. Both data and address information are multiplexed onto the bus, and for each path there is an identical bus for the return path. The GX bus has dual 32-bit paths at 333.3 MHz to give an aggregate data rate of 2.66 GB/s.

The first processor card connects to the GX bus through its GX controller. The GX bus is connected to a Remote I/O (RIO) bus on the system board through a RIO bridge chip. Each RIO bus provides 8 bits at 500 MHz in each direction, or 1 GB/s bidirectionally.

The second processor card has access to the GX bus using a Fabric bus, which connects it to the first processor card. The Fabric bus is similar in nature to the GX bus, but has dual 64-bit paths operating at 500 MHz to provide an aggregate data rate of 8 GB/s.

#### 2.3.2 PCI host bridge and PCI bus

Two RIO ports connect to the PCI Host Bridge (PHB). The PHB chip acts as a bridge between the RIO bus and two PCI to PCI bridges, which fan out to the separate PCI buses.

In the current implementation, the PCI to PCI bridge supports four PCI-X slots and two Ultra3 SCSI controllers on the system board, which are further described in the following section.

#### 2.4 PCI-X slots and adapters

PCI-X is the latest version of PCI bus technology, using a higher clock speed (133 MHz) to deliver a bandwidth of up to 1 GB/s. The PCI-X slots in the Model 6C4 and 6E4 systems support hot-plug and Extended Error Handling (EEH). EEH-capable adapters respond to a specially generated data packet from a PCI slot with a problem. This packet is analyzed by the system firmware which then allows the device driver to reset the adapter or slot, isolating the error and reducing the need for the system reboot.

In general, PCI-X slots also support existing 3.3 volt PCI adapters. For a full list of the adapters that are supported on the Model 6C4 and 6E4 systems, and for important information regarding adapter placement, see the *RS/6000 and pSeries PCI Adapter Placement Reference*, SA38-0538 for additional information. You can find this publication at:

http://www.ibm.com/servers/eserver/pseries/library/hardware\_docs/pci\_adp\_pl.html

#### 2.4.1 64-bit and 32-bit adapters

In general, PCI-X slots also support existing 3.3 volt PCI adapters, which include both 64-bit and 32-bit adapters.

Choosing between 32-bit and 64-bit adapters influences slot placement and affects performance. Higher-speed adapters use 64-bit slots because they can transfer 64 bits of data for each data transfer phase. 32-bit adapters can typically function in 64-bit PCI slots; however, 32-bit adapters still operate in 32-bit mode and achieve no performance advantage in a 64-bit slot.

#### 2.4.2 Internal Ultra3 SCSI controllers

The internal Ultra3 SCSI controllers provide one external Ultra3 SCSI VHDCI port and one internal SCSI to support the disk drive backplane and associated internal disk subsystem. Ultra3 SCSI supports single-ended or low-voltage differential (LVD) devices at up to 160 MB/s<sup>4</sup>.

A SCSI Enclosure Services (SES) device supports the disk bay hot-swappable features. The SES processor is the SCSI hot-swap manager; it provides the control mechanism for the device hot-swap options such as identify/replace/remove.

For the attachment of any other internal devices (for example CD-ROM, DVD-RAM, or tape), an additional SCSI card and appropriate cables are required.

#### 2.4.3 LAN adapters

Since the Models 6C4 and 6E4 are considered to be servers, they usually are connected to a local area network (LAN). The two internal 10/100 Mbps Ethernet integrated adapters, situated on the system board, can be used to accomplish that.

**Tip:** In conjunction with certain network switches, one can use the Cisco Systems' Etherchannel feature of AIX to build up one virtual Ethernet interface with double bandwidth using two Ethernet interfaces (adapters, or integrated).

Other LAN connection options include: Gigabit Ethernet, 4-port Ethernet, token-ring, and ATM. IBM supports an installation with NIM using Ethernet and token-ring adapters (use chrp as the platform type).

#### 2.4.4 Graphics adapters

The Models 6C4 and 6E4 are servers and are not intended to serve as a workstation. Therefore, the GXT135P is the only graphics adapter available. This adapter offers 2D function for business graphics, Internet applications, or for those applications that require a graphics display for installation and management.

#### 2.5 Internal storage

The internal storage on the Models 6C4 and 6E4 are similar in all respects and so will be discussed together.

The storage contained within the Models 6C4 and 6E4 consists of both SCSI and IDE devices, with the IDE devices being CD-ROM drives and the SCSI devices being internal disks, tape, and DVD-RAM, some of which will require a SCSI adapter to be placed in one of the PCI slots, as discussed in the next section.

<sup>&</sup>lt;sup>4</sup> SCSI T10 Technical Committee, http://www.t10.org

#### 2.5.1 Internal media

The Models 6C4 and 6E4 have two internal media bays. These bays can be populated by the devices listed in Table 2-1.

Table 2-1 List of internal media options

| Feature<br>Code                                      | Description                      | Comments                                                                                                                                                                                              |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2633                                                 | 650 MB IDE 48x<br>CD-ROM Drive   | This drive requires cable FC 4261 to connect the drive to the system board.                                                                                                                           |

| 2605                                                 | Diskette Drive                   | This diskette drive, when fitted, occupies a full media bay.                                                                                                                                          |

| 2623                                                 | DVD-RAM Drive<br>4.7 GB capacity | This feature is a SCSI device and will require one of the following additional feature codes: 6203 with 4260. Either one of these adapters will necessitate the use of a PCI slot within the machine. |

| Tape Drive additional feature codes: 6203 with 4260. |                                  | This feature is a SCSI device and will require one of the following additional feature codes: 6203 with 4260. Either one of these adapters will necessitate the use of a PCI slot within the machine. |

**Note:** A single SCSI adapter, FC 6203 with FC 4260 (2-drop connector cable) is sufficient for supporting SCSI devices in both the internal media bays.

#### 2.5.2 Hot-swappable SCSI disks

The Models 6C4 and 6E4 can have up to four hot-swappable drives in the front hot-swappable disk bay. The hot-swap process is controlled by the SCSI enclosure services, ses0, which is located on the PCI riser card rather than on the SCSI backplane. The PCI riser card has an integrated Ultra3 SCSI adapter. This adapter has two separate controllers: one feeding the hot-swappable bay and the other using an internal cable to supply the external VHDCI mini 68-pin SCSI connector. The hot-swappable bays can use the devices listed in Table 2-2.

Table 2-2 Hot-swappable disk options

| Feature Code | Description                                             |

|--------------|---------------------------------------------------------|

| 3157         | 18.2 GB 10,000 RPM Ultra3 SCSI hot-swappable disk drive |

| 3158         | 36.4 GB 10,000 RPM Ultra3 SCSI hot-swappable disk drive |

| 3159         | 73.4 GB 10,000 RPM Ultra3 SCSI hot-swappable disk drive |

Disk drive fault tracking of transient errors can alert the system administrator of an impending disk failure before it impacts system operation.

#### 2.5.3 Other hot-plug options

The Models 6C4 and 6E4 also give you the ability to concurrently change or add PCI adapters and the disks within the system.

The addition, removal, or changing of a PCI adapter can be accomplished by using a system management tool, such as Manage PCI Hot Plug Slots (using the Web-based System Manager) or PCI Hot Plug Manager (using SMIT). The PCI hot plug tasks can be accomplished also by using the Hot Plug Task of the on-line diagnostics task selection menu (using the diag command). Each of these tools provide a method by which a PCI slot can be identified first, powered off to enable removal or insertion of an adapter, and then powered back on to enable the device to be configured.

Prior to the hot-swap of a disk in the hot-swap bay, all necessary operating system actions must be undertaken to ensure that the disk is capable of being deconfigured.

Once the disk drive has been deconfigured, the SCSI enclosure device will power off the slot, enabling safe removal of the disk. You should ensure that the appropriate planning has been given to any operating system related disk layout, such as the AIX Logical Volume Manager, when using disk hot-swap capabilities. For more information, see *Problem Solving and Troubleshooting in AIX 5L*, SG24-5496.

#### 2.5.4 Boot options

Both Models 6C4 and 6E4 handle the boot process in a similar way to other RS/6000 and pSeries servers.

The initial stage of the boot process is to establish that the machine has powered up correctly and the memory and CPUs are functioning correctly. This sequence of events is performed by the service processor of the Models 6C4 and 6E4. Once the machine reaches the System Management Services (SMS) menus, all the necessary tests have been performed and the machine is scanning the bus for a boot source. At this point, there are a number of possibilities:

CD-ROM or DVD-RAM These devices can be used to boot the system so that a

system can be loaded, system maintenance performed,

or stand-alone diagnostics performed.

Internal or external tape drives

The media bay tape drive or any externally attached tape

drive can be used to boot the system using a mksysb, for

example.

SCSI disk The more common method of booting the system is to

use a disk situated in one of the hot swap bays in the front of the machine. However, any external non RAID

SCSI attached disk could be used if required.

SSA disk The Models 6C4 and 6E4 support booting from an SSA

disk either as an AIX system disk or as a RAID LUN. FC 6230 serial RAID adapters can be used to provide the boot support from a RAID configured disk provided that the firmware level of the adapter is 7000 and above.

For more information on SSA boot, see the SSA frequently asked questions located on the Web<sup>5</sup>.

Note: Fastwrite must not be enabled on the boot

resource SSA adapter.

SAN boot It is possible to boot these systems from a SAN using

FC 6228 with microcode 3.22A1 or later. The IBM 2105 Enterprise Storage Server (ESS) is an example of a SAN

attached device that can provide a boot medium.

**LAN boot** Network boot and NIM installs can be used if required.

An example of this would be in the ISP environment, where a high density of machines are installed in racks

and it is impractical to use CD media.