# Signals & Variables

| Copyright (c) 2012 Young W. Lim.                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using OpenOffice and Octave.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

#### Sequential Statement

- Wait Statement

- Assertion Statement

- Report Statement

- Generate Statement

- Signal Assignment

- Variable Assignment

- Procedure Call

- If

- Case

- Loop

- Next

- Exit

- Return

- Null

- Case Statement

- If Statement

- Loop Statement

- Process Statement

- Subprogram Body

- Sequential Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

#### **Concurrent Statement**

- Block Statement

- Process Statement

- Component Statement

- Generate Statement

- Concurrent Signal Assignment

- Concurrent Assertion

- Concurrent Procedure Call

- Architecture Body

- Block Statement

- Generate Statement

- Conditional Signal Assignment

- Selected Signal Assignemnt

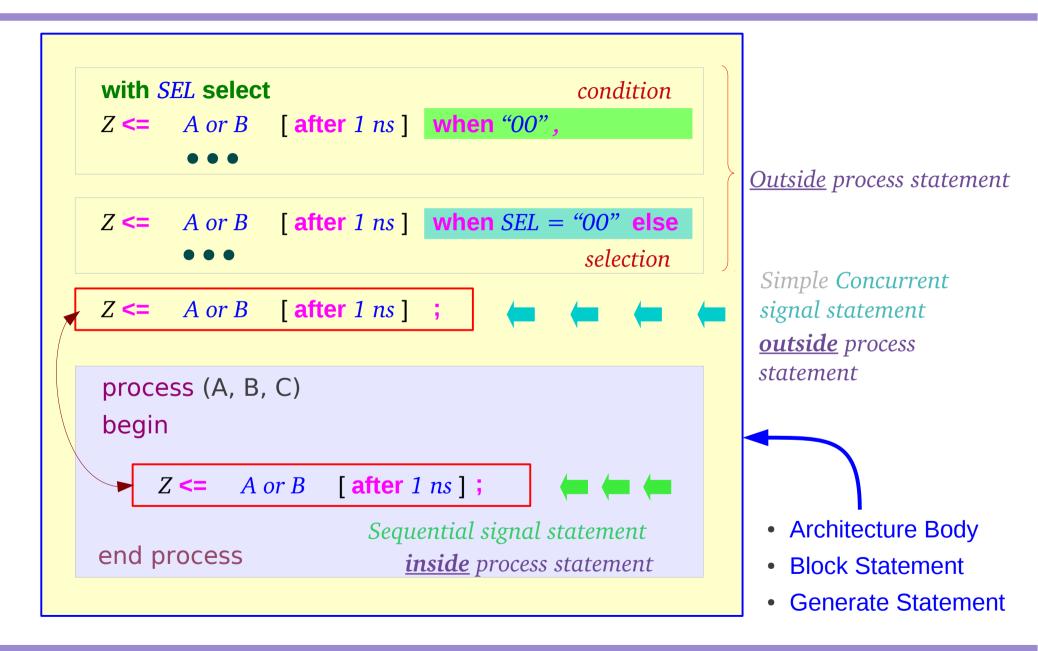

### Conditional Signal Assignment

```

[ after 1 ns ] when S0 = '1' else

Z \leq A \text{ or } B

[ after 2 ns ]

when S1 = '1' else

A or C

A or D [ after 3 \text{ ns} ]

when S0 = '1' else

Z \leftarrow A \text{ or } B \quad [\text{after 1 } ns]

A or C

[ after 2 ns ] ;

[ after 1 ns ] when SO = '1';

Z <=

A or B

7. <=

A or B

[ after 1 ns ]

simple concurrent statement

```

- Concurrent Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

#### Selected Signal Assignment

Conditional Signal Assignment

```

Z \leftarrow A \text{ or } B [after 1 ns] when SEL = "00" else

A or C [after 2 ns] when SEL = "01" else

A or D [after 2 ns] when SEL = "10" else

A or E [after 3 ns] when SEL = "11" else

A or F [after 4 ns];

```

Selected Signal Assignment

```

with SEL select

Z <= A or B  [after 1 ns]  when "00",

A or C  [after 2 ns]  when "01",

A or D  [after 3 ns]  when "10",

A or E  [after 4 ns]  when "11",

A or F  [after 5 ns]  when others;</pre>

selection

```

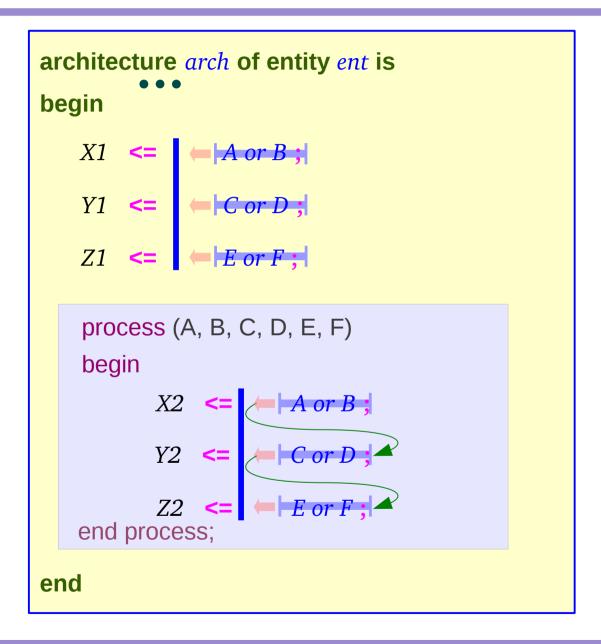

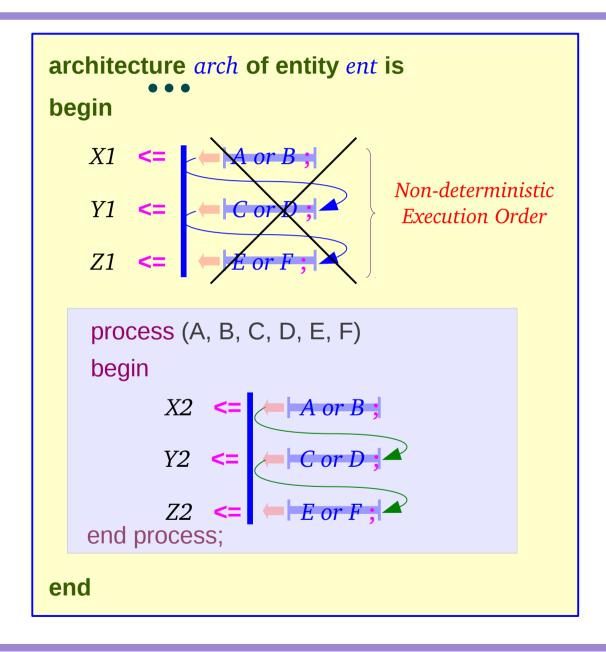

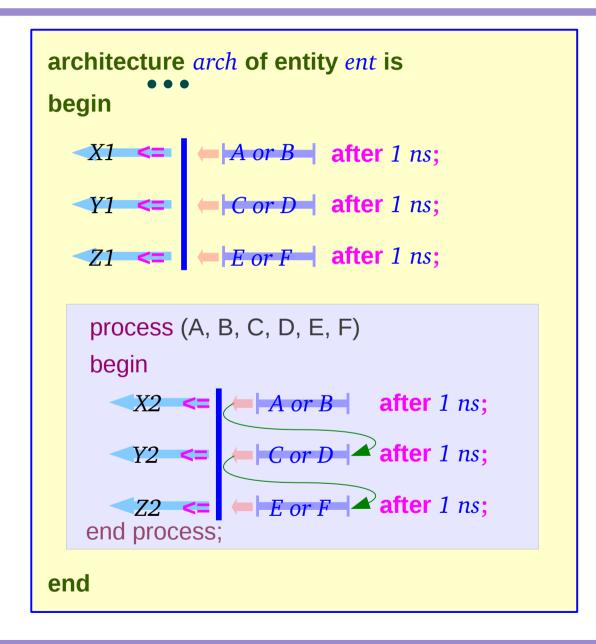

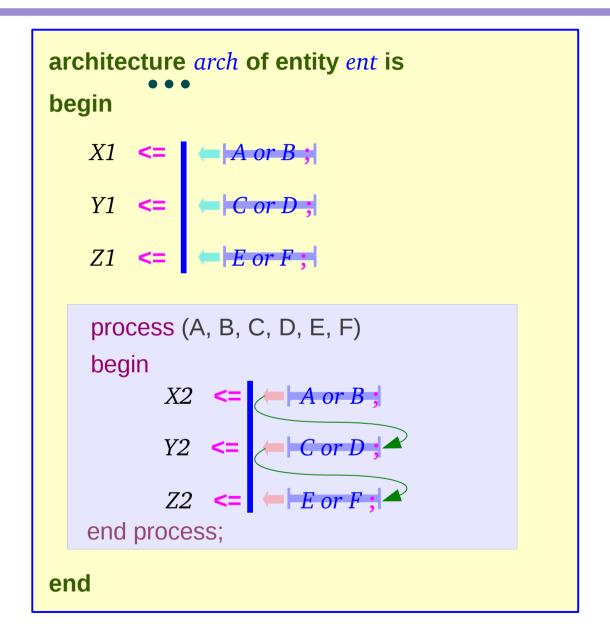

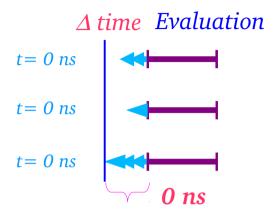

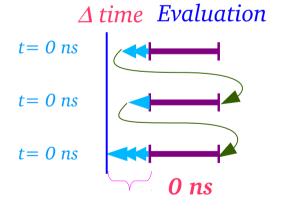

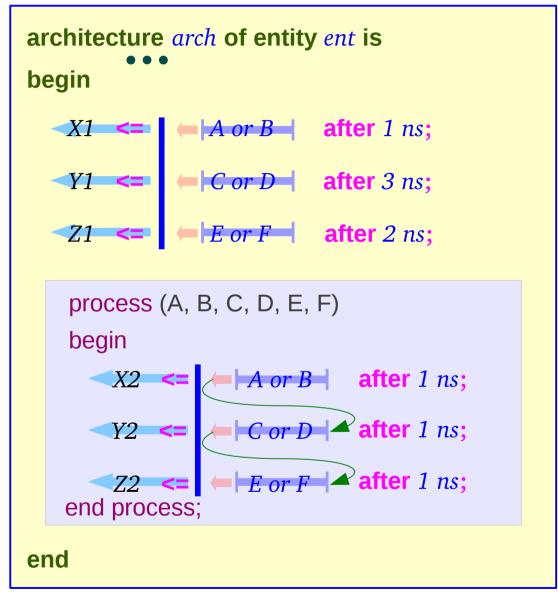

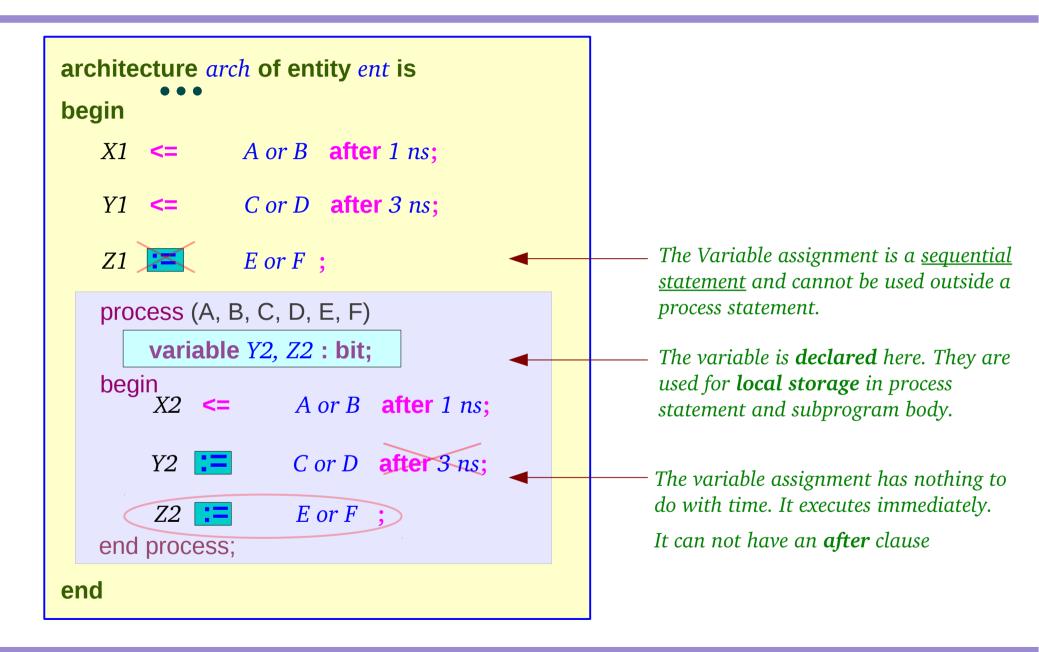

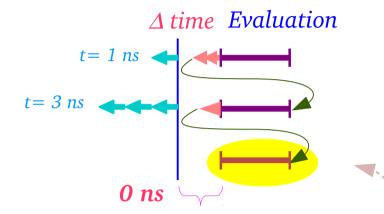

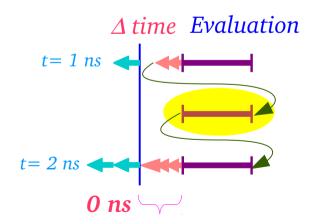

### Concurrent vs Sequential

#### Order of Execution (1)

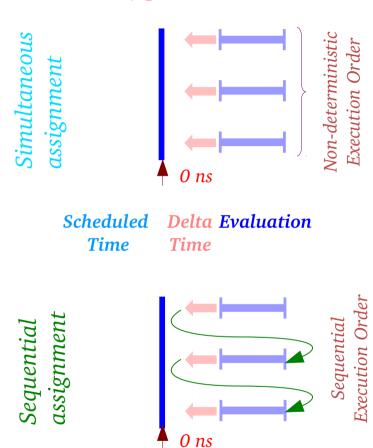

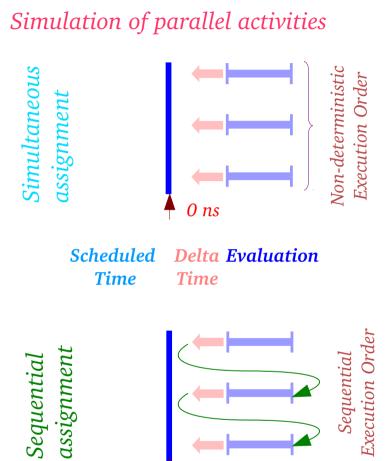

#### Simulation of parallel activities

The order of statements is important

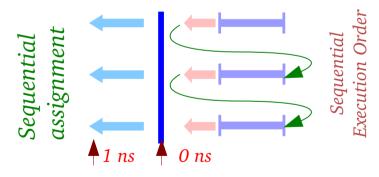

### Order of Execution (2)

The order of statements is important

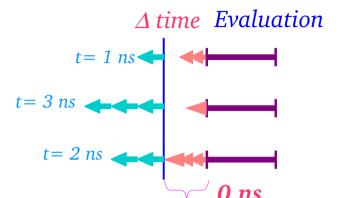

0 ns

### Order of Execution (3)

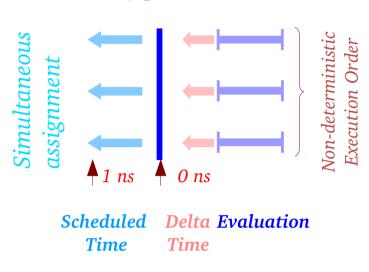

#### Simulation of parallel activities

The order of statements is important Non-blocking Assignment

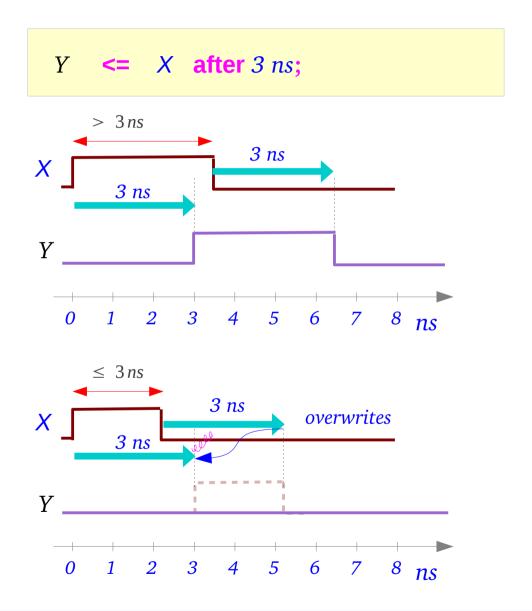

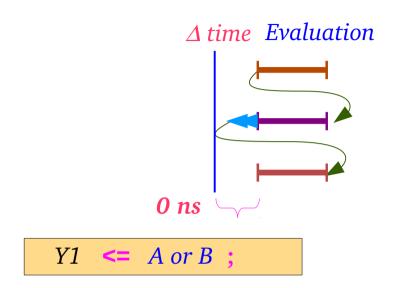

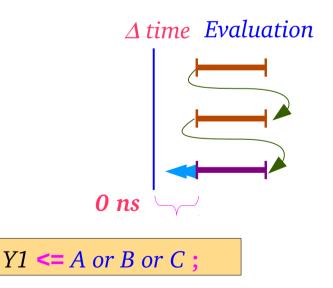

#### Simulation Time

#### **Evaluation**

Simulation Time

is assumed to take no time

Unit: ms, ns, ps, ... Unitless Delta  $\Delta$

Real Delay

- used for a simulator to mimic parallel activities simulator

$1 \, ms = 1000 \, ns$

$1 ps \neq n \cdot \Delta$

$1 \, ns = 1000 \, ps$

no integer n that make n delta equal to 1 ps.

$n \cdot \Delta = \mathbf{0} \, ps = \mathbf{0} \, ns \cdots$

Zero Delay

Zero Delay Assignment

$X1 \leftarrow A \text{ or } B$ ;

$X1 \leq A \text{ or } B \text{ after } 0 \text{ ns};$

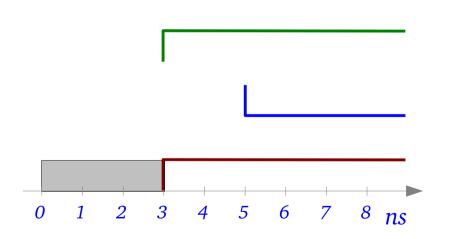

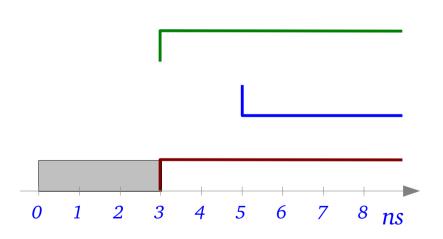

### Zero Delay Assignment

The exact no of delta is determined by the simulator and the context

*Updated values*

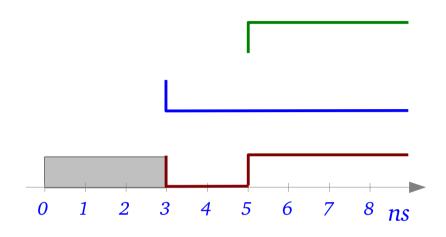

### Non-Zero Delay Assignment

The exact no of delta is determined by the simulator and the context

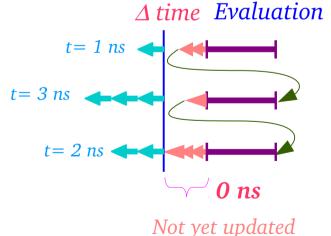

#### Inertial Delay & Transport Delay

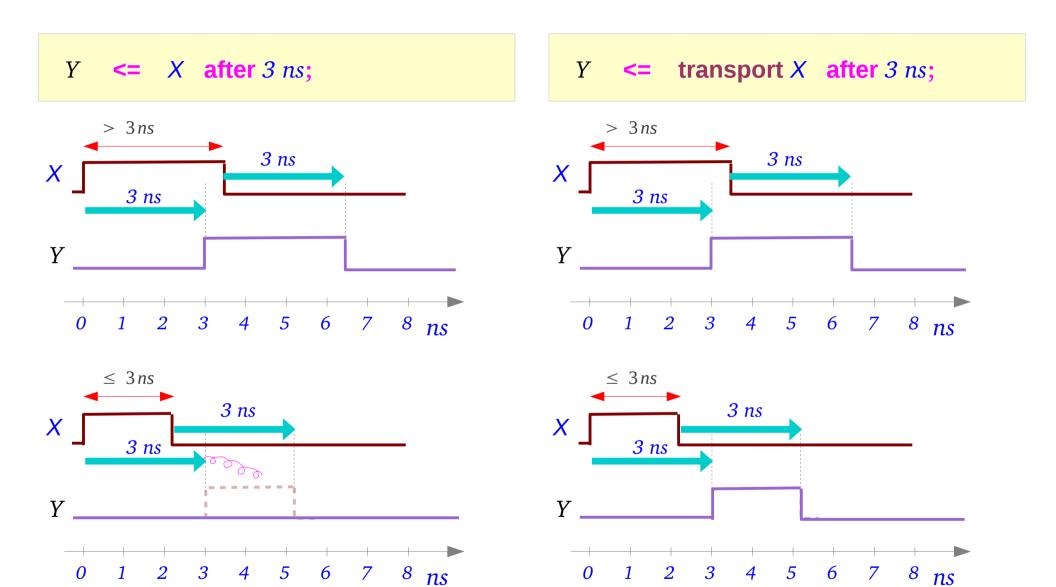

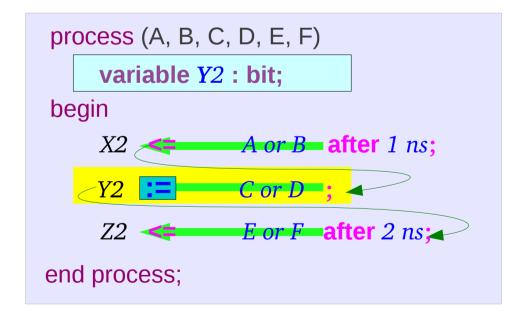

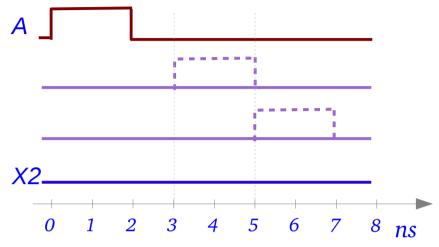

# Variable Assignment (1)

### Variable Assignment (2)

```

process (A, B, C, D, E, F)

variable Z2: bit;

begin

X2 \leftarrow A \text{ or } B \text{ after } 1 \text{ ns};

Y2 \leftarrow C \text{ or } D \text{ after } 3 \text{ ns};

Z2 \leftarrow E \text{ or } F;

end process;

```

The variable assignment has nothing to do with time. It executes immediately.

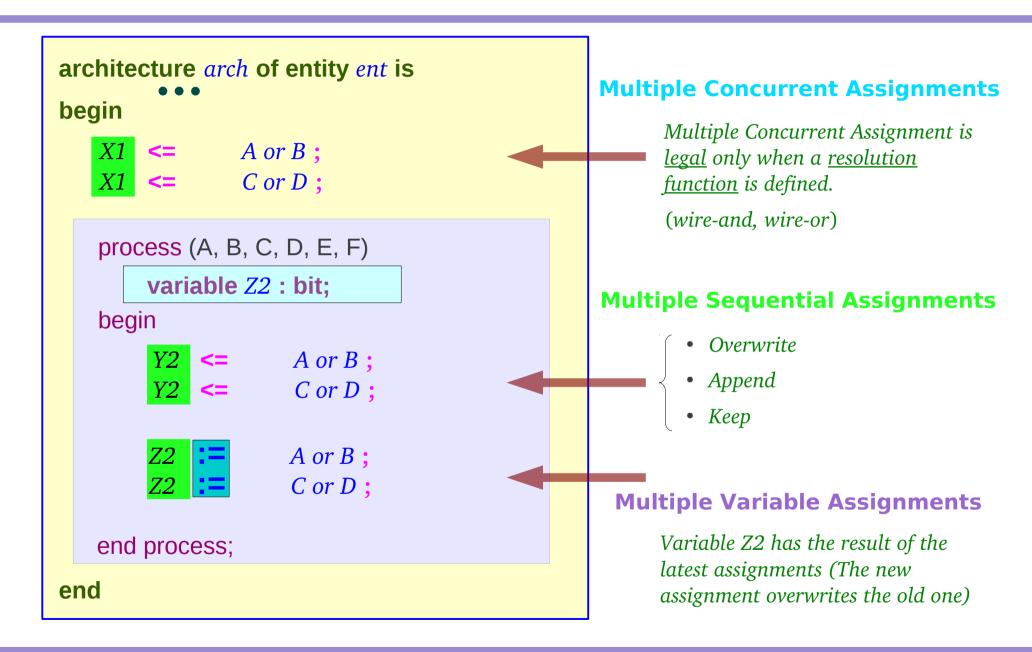

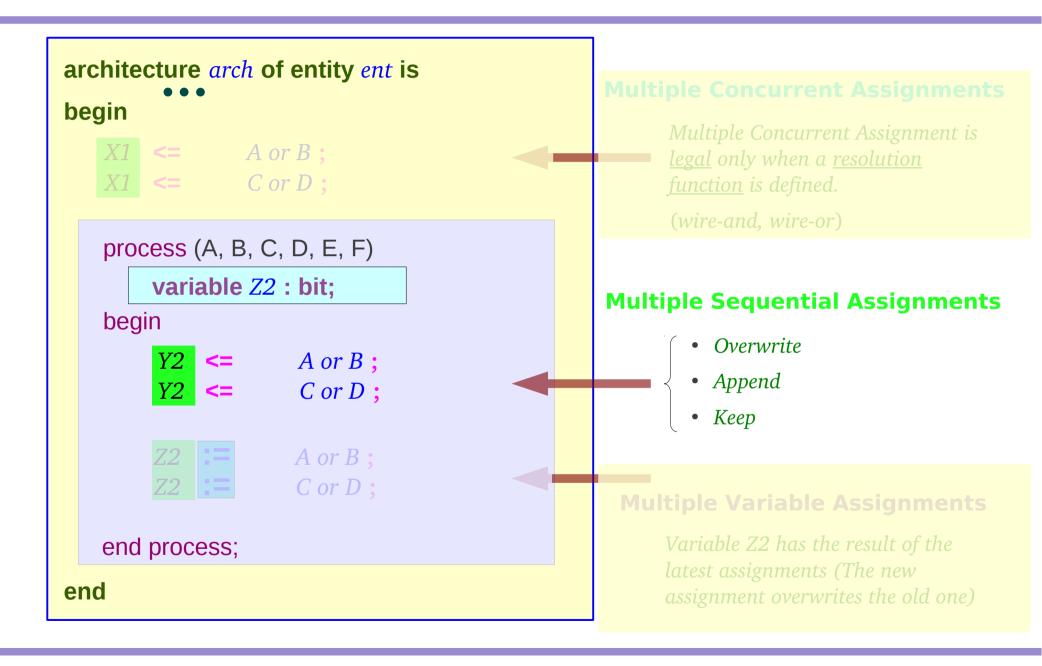

### Multiple Assignments to the Same Target

# Inertial Delay (1)

```

process (...)

begin

X2 \leftarrow 1' after 5 ns;

X2 \leftarrow 0' after 3 ns;

end process;

```

```

process (...)

begin

X2 \leftarrow 1' after 3 ns;

X2 \leftarrow 0' after 5 ns;

end process;

```

# Inertial Delay (2)

```

process (...)

begin

X2 \iff '1' \text{ after } 5 \text{ ns};

X2 \iff '1' \text{ after } 3 \text{ ns};

end process;

```

```

process (...)

begin

X2 \leftarrow 0' \text{ after } 3 \text{ ns};

X2 \leftarrow 0' \text{ after } 5 \text{ ns};

end process;

```

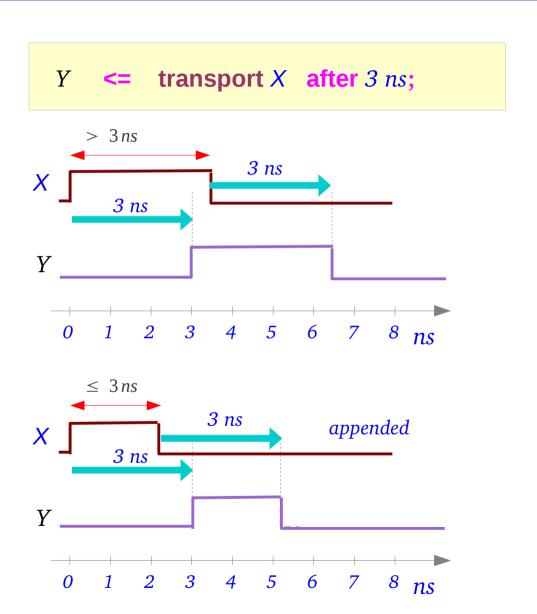

### Transport Delay (1)

```

process (...)

begin

X2 <= transport '1' after 5 ns;

X2 <= transport '0' after 3 ns;

end process;

```

```

process (...)

begin

X2 <= transport '1' after 3 ns;

X2 <= transport '0' after 5 ns;

end process;

```

### Transport Delay (2)

```

process (...)

begin

X2 <= transport '1' after 5 ns;

X2 <= transport '1' after 3 ns;

end process;

```

```

New stat overwrites

1 2 3 4 5 6 7 8 ns

```

```

process (...)

begin

X2 <= transport '0' after 3 ns;

X2 <= transport '0' after 5 ns;

end process;

```

### **Inertial Delay**

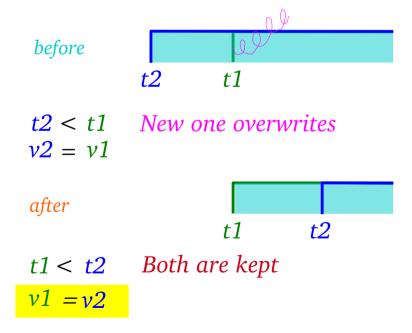

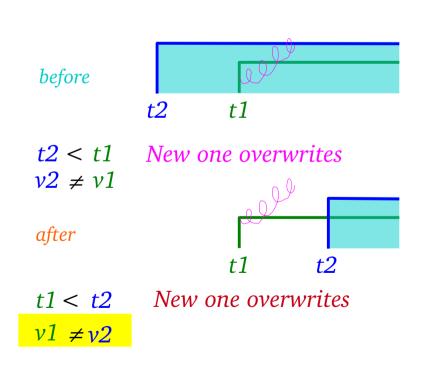

#### **Multiple Sequential Assignments - Inertial Delay**

```

process (...)

begin

X2 \leftarrow v1 \text{ after } t1 \text{ ns};

X2 \leftarrow v2 \text{ after } t2 \text{ ns};

end process;

```

$$t2 < t1$$

$v2 = v1$  New one overwrites

$v2 \neq v1$  New one overwrites

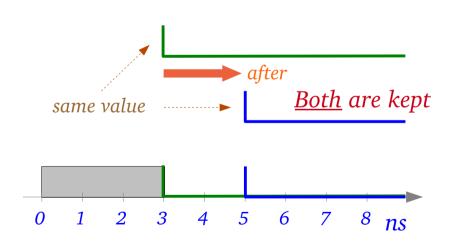

$t1 < t2$   $v1 = v2$  Both are kept

$v1 \neq v2$  New one overwrites

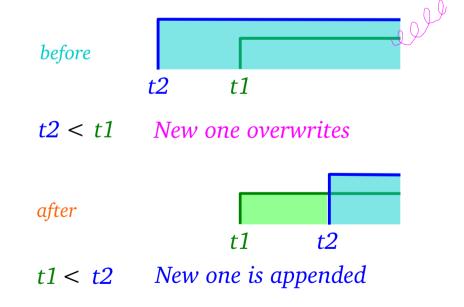

### **Transport Delay**

#### **Multiple Sequential Assignments - Transport Delay**

```

process (...)

begin

X2 <= transport v1 after t1 ns;

X2 <= transport v2 after t2 ns;

end process;

```

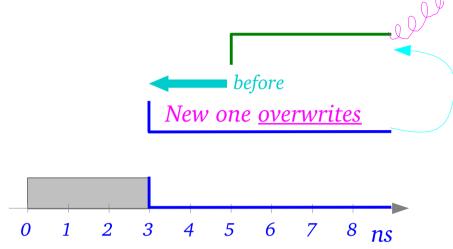

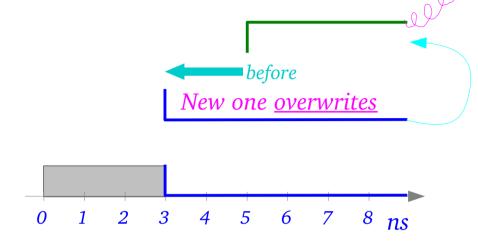

*t2* < *t1* New stat <u>overwrites</u>

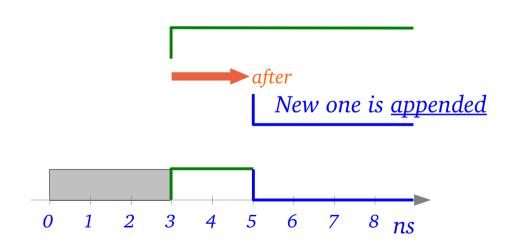

t1 < t2 New stat is appended

# Inertial & Transport Delay Model (1)

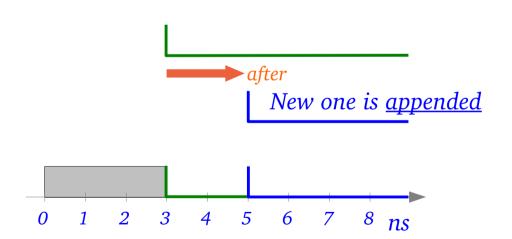

#### **Inertial Delay**

#### The simulation time of a new event

**Before** the time of an old one

New one <u>overwrites</u>

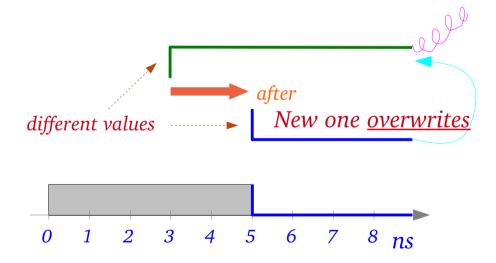

**After** the time of an old one

For the **same** value

Both are kept

For **different** values

New one overwrites

$$t2 < t1$$

$v2 = v1$  New one overwrites

$v2 \neq v1$  New one overwrites

$t1 < t2$   $v1 = v2$  Both are kept

$v1 \neq v2$  New one overwrites

#### **Transport Delay**

The simulation time of a new event

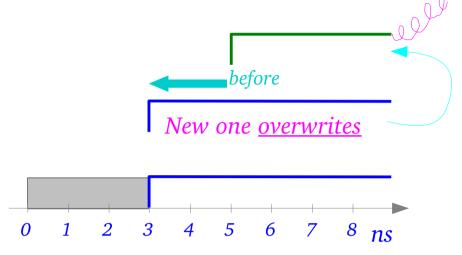

**Before** the time of an old one

New one <u>overwrites</u>

**After** the time of an old one

New stat is <u>appended</u>

*t2* < *t1* New stat <u>overwrites</u>

t1 < t2 New stat is appended

### Inertial & Transport Delay Model (2)

#### **Inertial Delay**

The simulation time of a new event

Before the time of an old one

New one overwrites

After the time of an old one

For the same value

Both are kept

For different values

New one overwrites

$$t2 < t1$$

$v2 = v1$  New one overwrites

$v2 \neq v1$  New one overwrites

$t1 < t2$   $v1 = v2$  Both are kept

$v1 \neq v2$  New one overwrites

### Inertial & Transport Delay Model (3)

#### **Transport Delay**

The simulation time of a new event

Before the time of an old one

New one overwrites

After the time of an old one

New stat is appended

t2 < t1 New stat overwrites

t1 < t2 New stat is appended

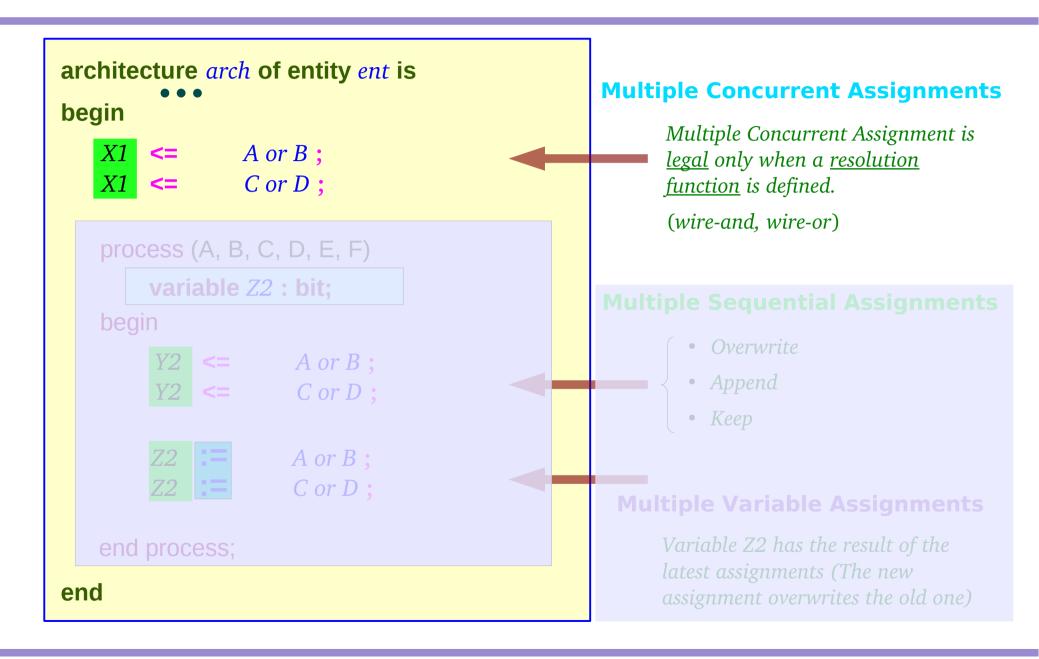

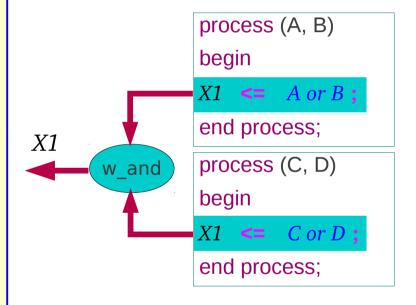

#### **Resolution Function**

```

architecture arch of entity ent is

FUNCTION w and (drivers : bit vector) RETURN bit is

BEGIN

END w and;

SIGNAL X1: w_and bit;

begin

\leftarrow A or B;

\leftarrow C or D;

process (A, B, C, D, E, F)

begin

end process;

end

```

Multiple Concurrent Assignment is <u>legal</u> only when a <u>resolution</u> function is defined.

(wire-and, wire-or)

```

X1 \leftarrow w_and(A \text{ or } B, C \text{ or } D);

```

# **Inertial Delay**

```

X2 <= '1' after 5 ns; Wire-or resolution function

process (...)

begin

end process;

```

```

X2 <= '1' after 3 ns; Wire-or resolution function

process (...)

begin

end process;

```

#### **Transport Delay**

```

X2 <= transport '1' after 5 ns;

X2 <= transport '0' after 3 ns;

process (...)

Wire-or

begin resolution

function

end process;

```

```

X2 <= transport '1' after 3 ns;

X2 <= transport '0' after 5 ns;

process (...)

begin

end process;

Wire-or

resolution

function

```

# **Inertial Delay**

```

X2 \leftarrow A after 5 ns; Wire-or X2 \leftarrow A after 3 ns; resolution process (...) function begin end process;

```

```

X2 <= A after 3 ns; Wire-or resolution function begin end process;

```

### **Transport Delay**

```

X2 <= A after 5 ns; Wire-or resolution process (...) function begin end process;

```

```

X2 <= A after 3 ns; Wire-or resolution process (...) begin function function end process;

```

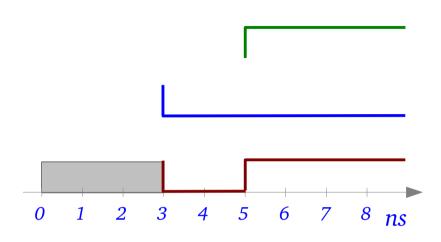

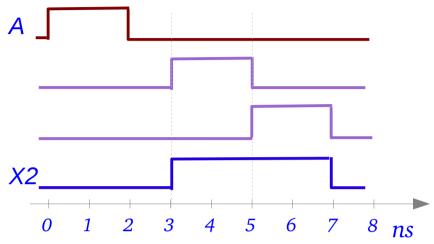

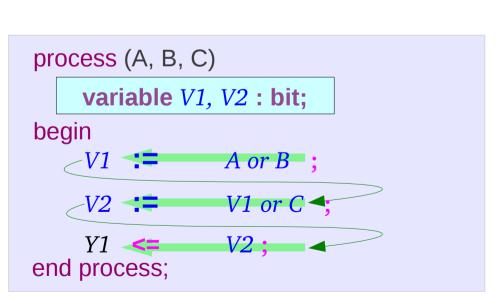

# Signals & Variable Assignment Example 1

```

process (A, B, C)

variable V1, V2 : bit;

begin

V1  A or B;

Y1  V2;

end process;

```

#### References

- [1] http://en.wikipedia.org/

- [2] J. V. Spiegel, VHDL Tutorial, http://www.seas.upenn.edu/~ese171/vhdl/vhdl\_primer.html

- [3] J. R. Armstrong, F. G. Gray, Structured Logic Design with VHDL

- [4] Z. Navabi, VHDL Analysis and Modeling of Digital Systems

- [5] D. Smith, HDL Chip Design

- [6] http://www.csee.umbc.edu/portal/help/VHDL/stdpkg.html

- [7] VHDL Tutorial VHDL onlinewww.vhdl-online.de/tutorial/